# Measuring the Phase Variation of a DOCSIS 3.1 Full Duplex Channel

A Thesis Submitted

to the College of Graduate and Postdoctoral Studies

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

$\label{eq:by-sean-wilson}$  Sean M. Wilson

Saskatoon, Saskatchewan, Canada

© Copyright Sean M. Wilson, August, 2018. All rights reserved.

## Permission to Use

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, it is agreed that the Libraries of this University may make it freely available for inspection. Permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professors who supervised this thesis work or, in their absence, by the Head of the Department of Electrical and Computer Engineering or the Dean of the College of Graduate Studies and Research at the University of Saskatchewan. Any copying, publication, or use of this thesis, or parts thereof, for financial gain without the written permission of the author is strictly prohibited. Proper recognition shall be given to the author and to the University of Saskatchewan in any scholarly use which may be made of any material in this thesis.

Request for permission to copy or to make any other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan, S7N 5A9, Canada

OR

Dean

College of Graduate and Postdoctoral Studies University of Saskatchewan 116 Thorvaldson Building, 110 Science Place Saskatoon, Saskatchewan, S7N 5C9, Canada

## Abstract

Including a Full Duplex option into DOCSIS introduces several problems. One of the more troublesome issues is the presence of a strong self interference signal that leaks from the transmit side to the receive side of a cable node. This self interference is caused by echoes in the channel that translate the forward travelling transmit signals into a reverse travelling signal, as well as, by leakage from the hybrid coupler used to couple the upstream and downstream signals. To suppress this self interference an echo canceller is implemented to remove the unwanted interference from the received signal. Unfortunately with the high rates of data transmission used in modern day CATV networks the echo canceller needs tremendous precision.

A major concern in the implementation of Full Duplex into DOCSIS is if the channels used are even very slightly time varying. The echos in such channels change with time and can be difficult for the echo canceller to track. Changes in the response of the channel cause the echo profile of the network to shift and the echo canceler to re-adapt to the new channel response. The issue with this changing response is that it is possible for the channel to change faster than the echo canceller can adapt, resulting in the interference becoming unacceptably high. Since the channel is a physical network of coaxial cables often exposed to the environment, its propagation properties can be affected by wind swaying pole mounted cables, or by rapid heating from the sun, or sudden shifts in the load of the network. With information on how the physical properties of the cable changes, the engineers designing the echo canceller can know how fast the canceller must adapt to changes and also have a better measure of how reliable its echo cancellation will be.

In this thesis the stability of the echo profile of the channel is measured. It is shown that the property of the channel with the greatest potential to rapidly change and cause noise after echo cancellation is the phase response of the channel. Due to this, the approach of this thesis is to measure the fluctuations in the phase of the channel response of a CATV network constructed in the lab. To measure the fluctuations in the phase response of the

channel, a PLL (Phase Locked Loop) based circuit is designed and built on an FPGA (Field Programmable Gate Array) and connected to a model of a simple CATV network. The PLL circuit used to measure the phase fluctuations of the channel is designed to be able to measure changes occurring faster than 0.1 Hz and with a power higher than  $10^{-7} V^2$ . The circuit is able to capture data from the channel over a period of 90 seconds.

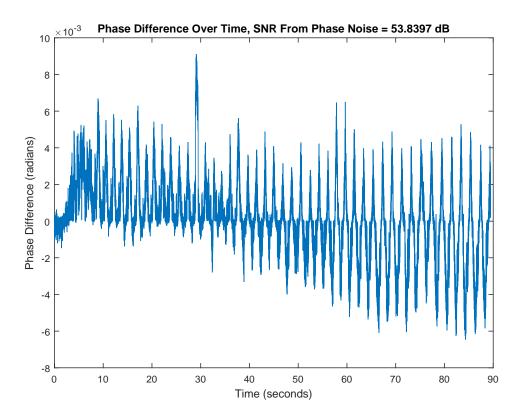

Using this phase variation measurement circuit a series of experiments were performed on a model CATV DOCSIS network. It was found that many physical disturbances to the network had the effect of rapidly shifting the phase response of the network. Heating the cables in the network was found to shift the phase response upwards of 20000  $\mu$ radians. Flexing the cables in the network was found to have a peak phase variation of 8000  $\mu$ radians with similar effects found from walking over cables. Overall, it was clear that physical effects on the network had the propensity to rapidly shift the network response. Any echo canceller that is designed in the future will have to consider these effects when reporting the cancellation that it is able to achieve.

# Acknowledgments

I would like to thank my supervisor Dr. Eric Salt for all of his help and guidance throughout the project. I would also like to thank Dr. Brian Berscheid for his expertise and assistance with many parts of my project. I would like to thank Vecima Networks for providing the opportunity to research some practical topics as well as their support throughout my research.

I greatly appreciate my parents putting up with me and giving me somewhere to live through out my master's degree. I would also like to thank my grandparents for always giving me support and motivation to succeed.

Finally I would like to thank my colleagues, Lance Pitka and Quang Nguyen, for helping me stay sane during the writing of this thesis.

# Table of Contents

| P            | ermis    | ssion to Use                              | 1     |

|--------------|----------|-------------------------------------------|-------|

| $\mathbf{A}$ | Abstract |                                           |       |

| $\mathbf{A}$ | ckno     | wledgments                                | iv    |

| Ta           | able (   | of Contents                               | v     |

| Li           | ist of   | Tables                                    | ix    |

| Li           | ist of   | Figures                                   | X     |

| Li           | ist of   | Abbreviations                             | XV    |

| Li           | ist of   | Symbols                                   | xviii |

| 1            | Intr     | roduction                                 | 1     |

|              | 1.1      | History of Cable Systems                  | 1     |

|              | 1.2      | Modern Cable Systems                      | 2     |

|              | 1.3      | Future Cable Systems                      | 4     |

|              |          | 1.3.1 Remote Phy                          | 5     |

|              |          | 1.3.2 Full Duplex                         | 6     |

|              | 1.4      | Obstacles in Full Duplex                  | 7     |

|              | 1.5      | Statement of the Problem                  | 10    |

|              | 1.6      | Thesis Outline                            | 11    |

| 2            | Crit     | tical Components of a Full Duplex Network | 13    |

|   | 2.1  | Architecture of a Full Duplex Cable System          | 13 |

|---|------|-----------------------------------------------------|----|

|   | 2.2  | Functional Operation of Critical System Components  | 15 |

|   |      | 2.2.1 Downstream PHY Layer                          | 15 |

|   |      | 2.2.2 Converting a Complex Baseband to a Real RF    | 16 |

|   |      | 2.2.3 Digital to Analog Conversion                  | 19 |

|   |      | 2.2.4 Analog to Digital Conversion                  | 27 |

|   |      | 2.2.5 Hybrid Couplers                               | 29 |

|   |      | 2.2.6 Coaxial Cable                                 | 30 |

|   | 2.3  | System Analysis of a Full Duplex Network            | 36 |

| 3 | Self | Interference Suppresion and Phase Instability       | 42 |

|   | 3.1  | Concept and Roll of Self Interference Suppression   | 42 |

|   | 3.2  | Channel Coherence Time                              | 46 |

|   | 3.3  | Phase Noise and its Limitation on Echo Suppression  | 47 |

|   | 3.4  | Phase Measurement Requirements                      | 51 |

| 4 | Pha  | se Fluctuation Measurement With a Phase Locked Loop | 55 |

|   | 4.1  | Phase Locked Looped Quadrature Method               | 55 |

|   | 4.2  | Output of a Phase Locked Loop                       | 60 |

|   | 4.3  | Transfer Function Analysis of a Phase Locked Loop   | 61 |

|   |      | 4.3.1 Analysis of a Type 1 PLL                      | 61 |

|   |      | 4.3.2 Analysis of a Type 2 PLL                      |    |

| 5 | Imp | olemen   | tation of a Phase Locked Loop Circuit on an FPGA | 68  |

|---|-----|----------|--------------------------------------------------|-----|

|   | 5.1 | Param    | neter Selection in a Type 2 Phase Locked Looped  | 68  |

|   |     | 5.1.1    | Gain Control Circuit                             | 71  |

|   |     | 5.1.2    | Notch Filter                                     | 73  |

|   | 5.2 | Noise    | Sources in the Phase Locked Loop                 | 76  |

|   |     | 5.2.1    | Effect of Amplitude Noise on Phase Error Output  | 76  |

|   |     | 5.2.2    | Quantization Noise                               | 77  |

| 6 | Ver | ificatio | on of Phase Locked Loop Measurement Circuit      | 91  |

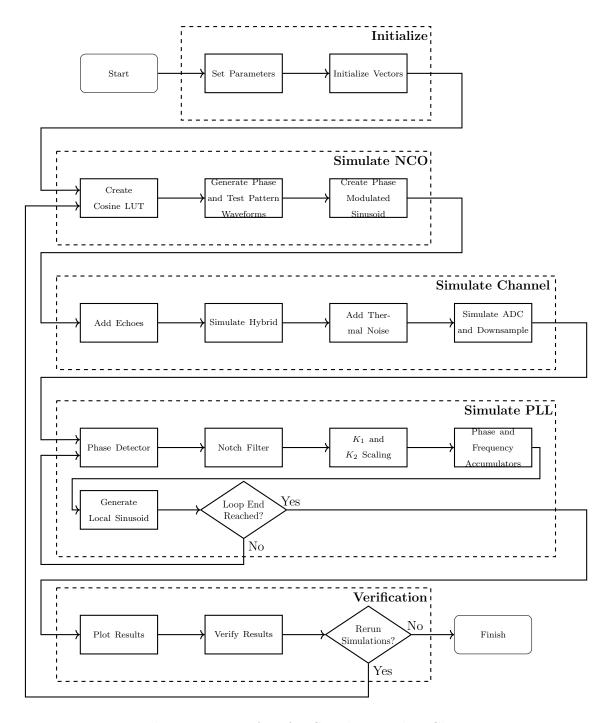

|   | 6.1 | MATI     | AB Verification                                  | 91  |

|   |     | 6.1.1    | Program Flow Overview                            | 91  |

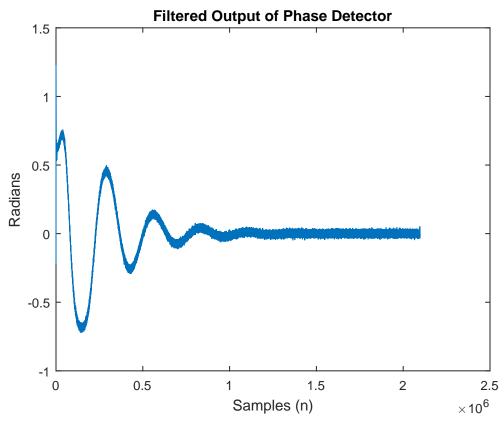

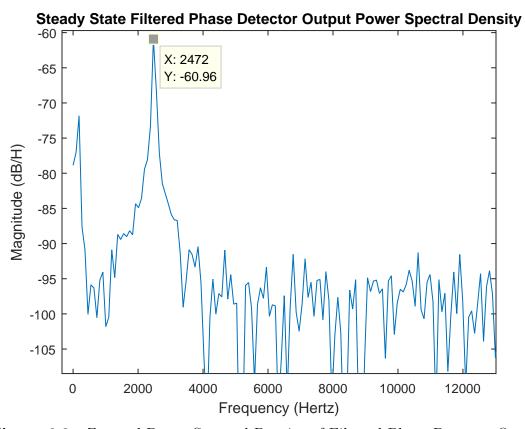

|   |     | 6.1.2    | MATLAB Simulation Results                        | 93  |

|   | 6.2 | Verific  | eation of FPGA Implementation                    | 97  |

|   |     | 6.2.1    | Transmit Circuitry                               | 97  |

|   |     | 6.2.2    | Receive Circuitry                                | 101 |

| 7 | Lab | Meas     | urements                                         | 109 |

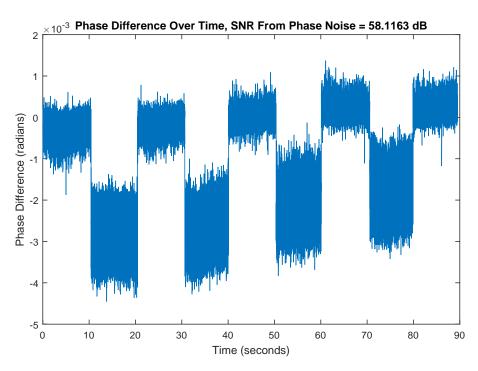

|   | 7.1 | Effects  | s of Physical Disturbances to Coaxial Cables     | 111 |

|   | 7.2 | Effect   | of Heated Cables                                 | 115 |

|   | 7.3 | Effect   | of Sudden Load Changes                           | 117 |

| 8 | Sun | nmary    | and Future Work                                  | 122 |

|   | 8 1 | Contri   | ibutions and Results                             | 122 |

| 8.2                                                  | Future | e Work                               | :4 |

|------------------------------------------------------|--------|--------------------------------------|----|

| Appendix Full Duplex Remaining System Components 125 |        |                                      |    |

| A.1                                                  | MAC    | Layer                                | 25 |

| A.2                                                  | DOCS   | SIS PHY Layer Components             | 26 |

|                                                      | A.2.1  | Convergence Layer                    | 26 |

|                                                      | A.2.2  | Forward Error Correction             | 26 |

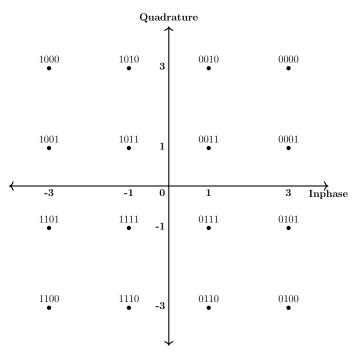

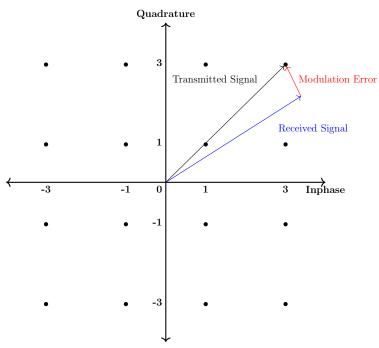

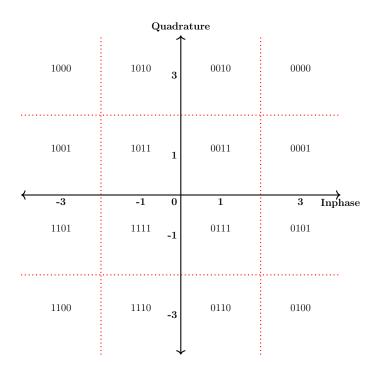

|                                                      | A.2.3  | Constellation Mapper                 | 26 |

|                                                      | A.2.4  | Inverse Fourier Transform            | 29 |

|                                                      | A.2.5  | Cyclic Prefix and Roll Off Insertion | 1  |

|                                                      | A.2.6  | Upstream PHY Layer                   | 2  |

|                                                      |        | FFT                                  | 3  |

|                                                      |        | QAM Slicer                           | 4  |

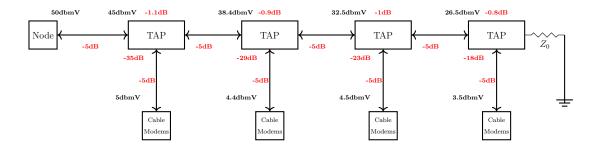

| A.3                                                  | Taps   |                                      | 4  |

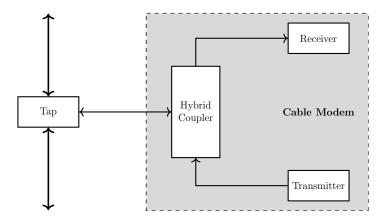

| A.4                                                  | Cable  | Modems                               | 7  |

| References 139                                       |        |                                      |    |

# List of Tables

| 1.1 | DOCSIS Standard Progression                          | 4  |

|-----|------------------------------------------------------|----|

| 2.1 | Minimum CNR for DOCSIS QAM Constellations            | 41 |

| 5.1 | Statistical Properties of Quantization Noise Sources | 89 |

# List of Figures

| 1.1  | Remote Phy CATV System                                            | 5  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Half Duplex Spectrum                                              | 6  |

| 1.3  | Full Duplex Spectrum                                              | 7  |

| 1.4  | Block Diagram of a Full Duplex Node Without an Echo Canceller     | 7  |

| 1.5  | Echo Paths Inside the Node                                        | 8  |

| 1.6  | Received Spectrum                                                 | 9  |

| 1.7  | Node Diagram With Echo Canceller                                  | 10 |

| 1.8  | Coaxial Cable Network                                             | 10 |

| 2.1  | Full Duplex DOCSIS Network Architecture                           | 14 |

| 2.2  | Simplified Downstream PHY Processing                              | 17 |

| 2.3  | Frequency Up Converter                                            | 17 |

| 2.4  | Input and Output for a DAC                                        | 20 |

| 2.5  | Equivalent System of Sample and Hold Dac                          | 21 |

| 2.6  | Sampling Distortion Caused by Timing Jitter                       | 22 |

| 2.7  | Clock Jitter to Additive Noise Model                              | 23 |

| 2.8  | ADC Sampling Showing Error From Clock Jitter                      | 28 |

| 2.9  | Diplexer Block Diagram                                            | 30 |

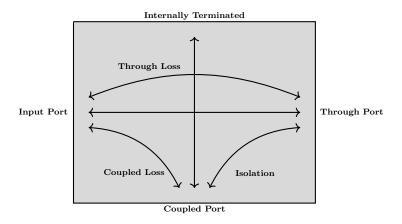

| 2.10 | Hybrid Block Diagram Showing Typical Isolation and Insertion Loss | 31 |

| 2.11 | Generic 2-Port Network Showing S-parameter Usage                                 | 35 |

|------|----------------------------------------------------------------------------------|----|

| 2.12 | System Diagram of a Full Duplex Network                                          | 37 |

| 3.1  | Adaptive Filtering                                                               | 43 |

| 3.2  | Adaptive Filter Structure                                                        | 44 |

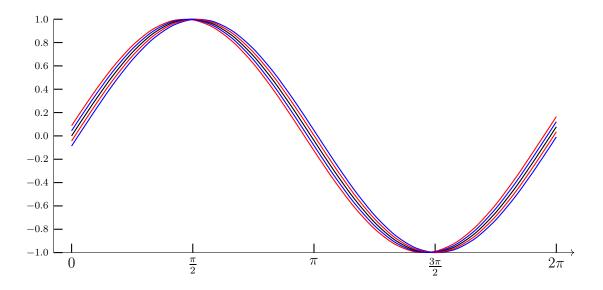

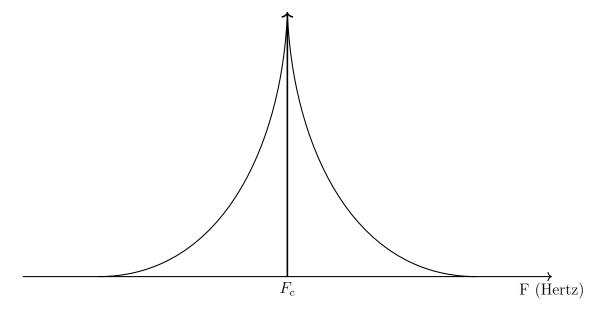

| 3.3  | Sinusoidal Signal with Phase Noise                                               | 48 |

| 3.4  | Spreading of a Tone's Spectrum Caused by Phase Noise                             | 49 |

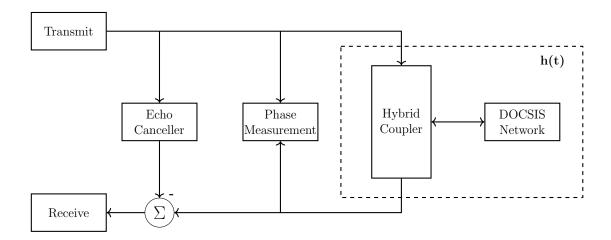

| 3.5  | Phase Stability Measurement                                                      | 52 |

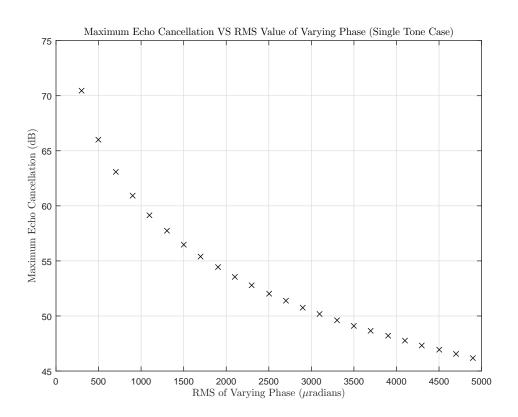

| 3.6  | RMS of Phase Fluctuations Effect on SNR                                          | 53 |

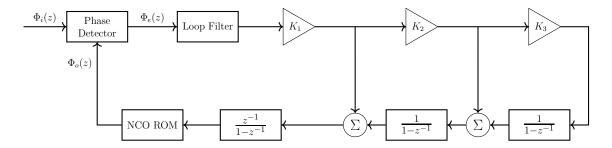

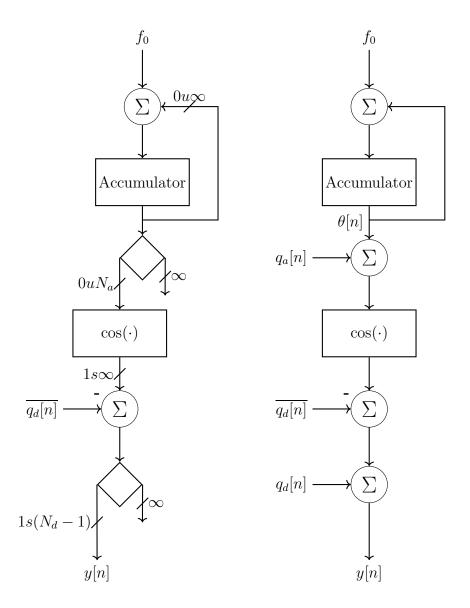

| 4.1  | Generic Digital Phase Locked Loop Circuit                                        | 56 |

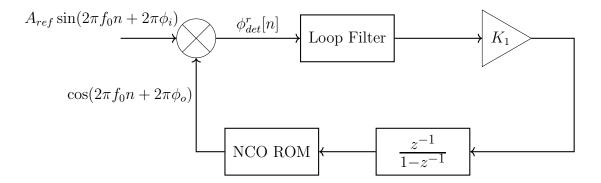

| 4.2  | Type 1 Phase Locked Loop with Multiplier Phase Detector                          | 57 |

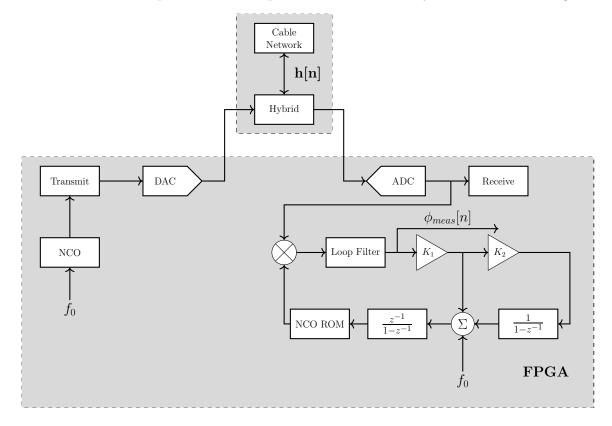

| 4.3  | Hardware Setup for a Phase Locked Loop Based Measurement System                  | 59 |

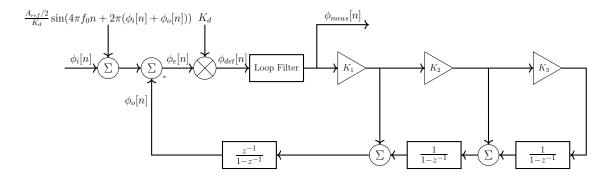

| 4.4  | Equivalent Model of a Type 3 Phase Locked Loop                                   | 60 |

| 4.5  | Type 1 Phase Locked Loop                                                         | 62 |

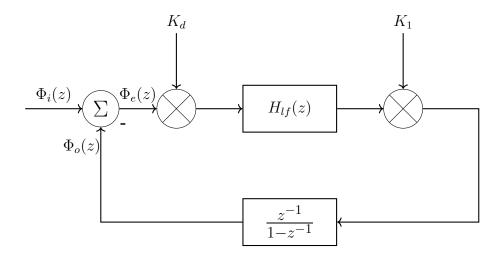

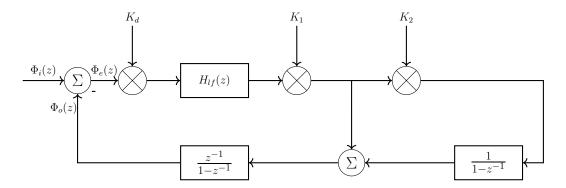

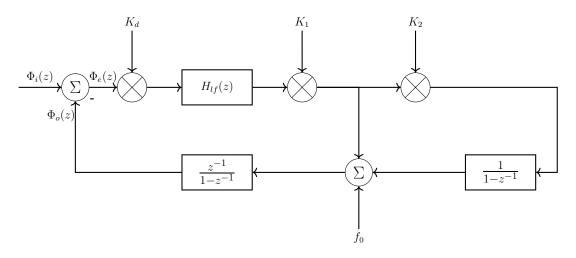

| 4.6  | Type 2 Phase Locked Loop                                                         | 64 |

| 4.7  | Type 2 Phase Locked Loop with Frequency Inputted                                 | 67 |

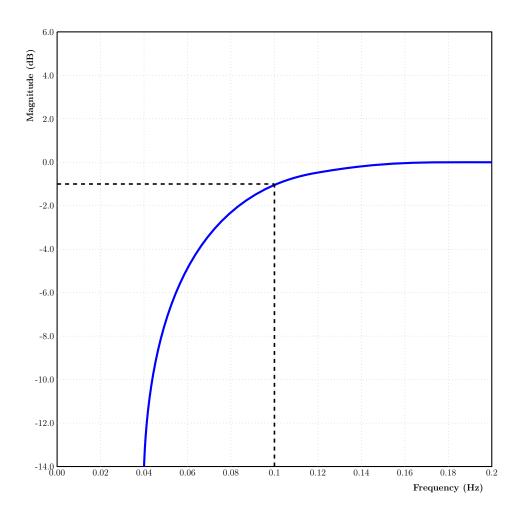

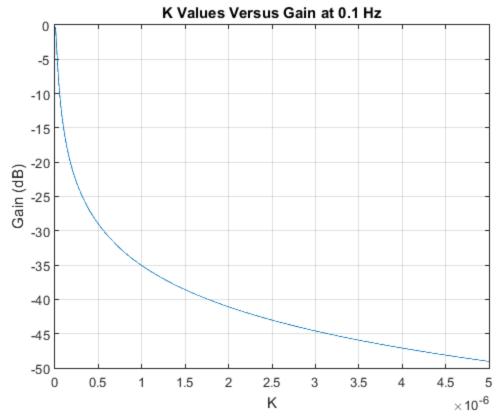

| 5.1  | Magnitude Response of $E_2(z)$ Showing a Gain of -1 dB at a Stop Frequency       |    |

|      | of 0.1 Hz                                                                        | 70 |

| 5.2  | Gain at 0.1 Hz for Different Values of K $\dots \dots \dots \dots \dots \dots$ . | 71 |

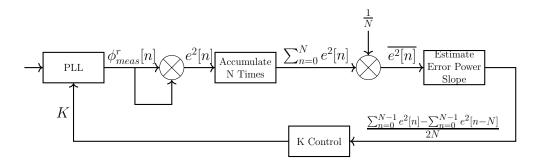

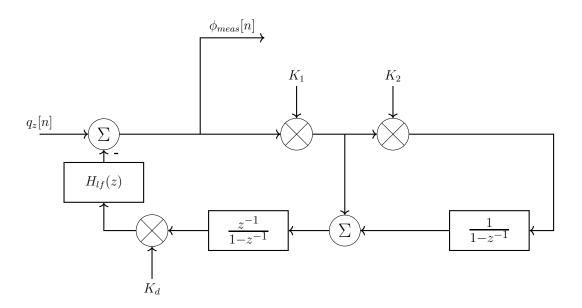

| 5.3  | Hardware Implementation of the PLL Gain Control Algorithm                        | 73 |

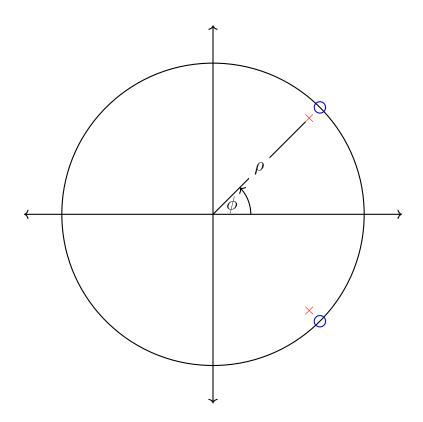

| 5 /  | Pole Zero Plot of a Notch Filter                                                 | 7/ |

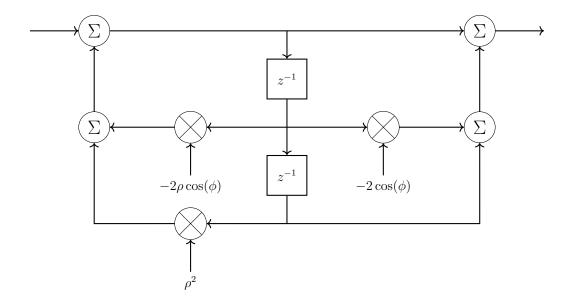

| 5.5  | Circuit Diagram of a Notch Filter                                                              | 75  |

|------|------------------------------------------------------------------------------------------------|-----|

| 5.6  | Notch Filter Coefficient Calculation                                                           | 76  |

| 5.7  | Quantized vs Unquantized                                                                       | 78  |

| 5.8  | Probability Density Function of Quantization Error                                             | 79  |

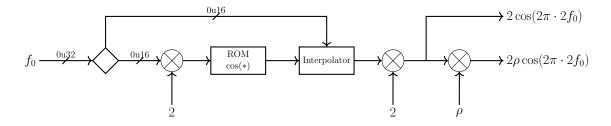

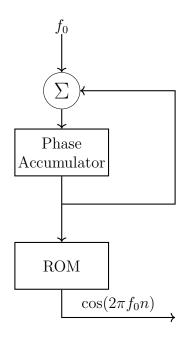

| 5.9  | Block Diagram of a NCO                                                                         | 80  |

| 5.10 | Truncated NCO Showing Bit Widths and Additive Noise                                            | 81  |

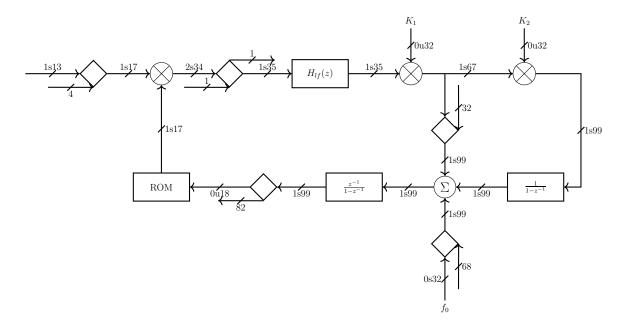

| 5.11 | PLL Circuit Diagram Showing Word Formats                                                       | 85  |

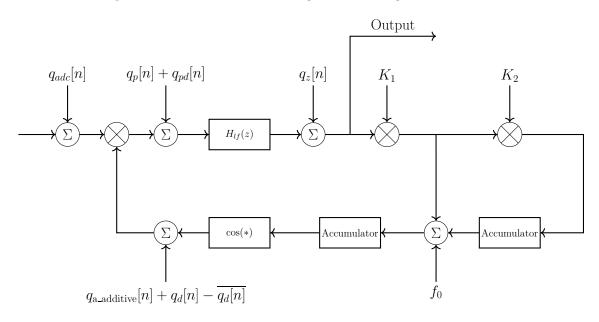

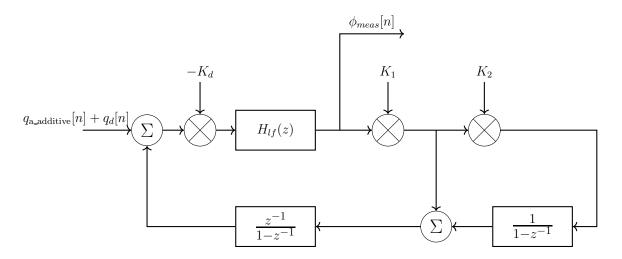

| 5.12 | PLL Circuit with Additive Quantization Noise Sources Shown                                     | 85  |

| 5.13 | Equivalent Circuit for Quantization Noise from Phase Detector and Pole Section of Notch Filter | 86  |

| 5.14 | Equivalent Circuit for Quantization Noise from NCO                                             | 87  |

| 5.15 | Equivalent Circuit for Quantization Noise from Zero Section of Notch Filter                    | 88  |

| 6.1  | MATLAB Simulation Flow Chart                                                                   | 94  |

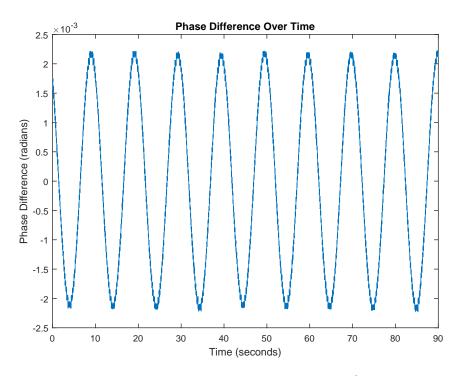

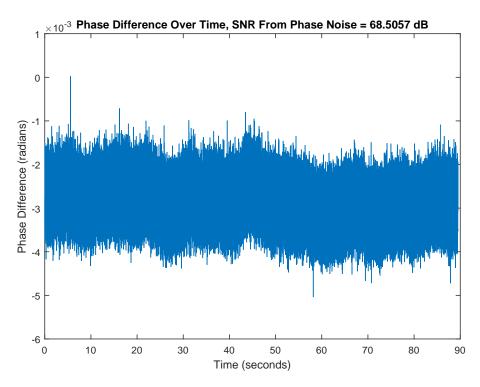

| 6.2  | Filtered Output of Phase Detector                                                              | 95  |

| 6.3  | Zoomed Power Spectral Density of Filtered Phase Detector Output                                | 96  |

| 6.4  | FPGA and DAC/ADC Test Boards Used for the Measurement Circuit                                  | 97  |

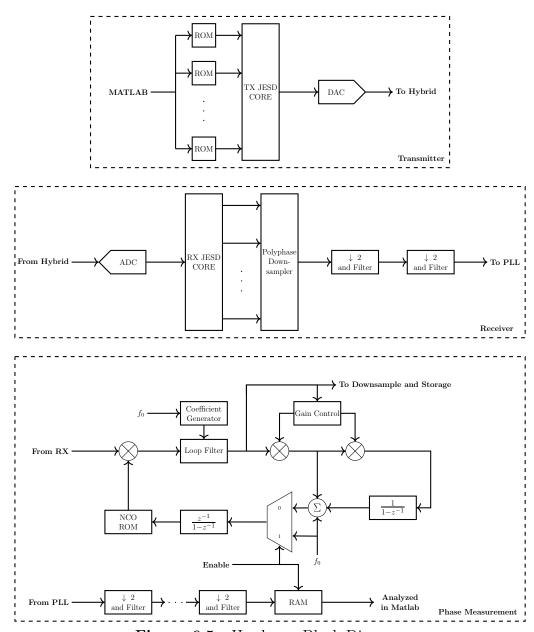

| 6.5  | Hardware Block Diagram                                                                         | 98  |

| 6.6  | Transmitted Signal Order                                                                       | 99  |

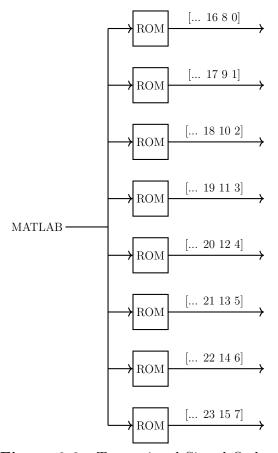

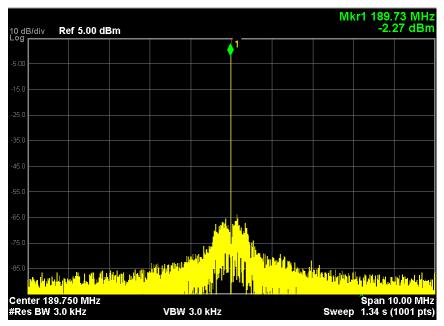

| 6.7  | Dac Output                                                                                     | 100 |

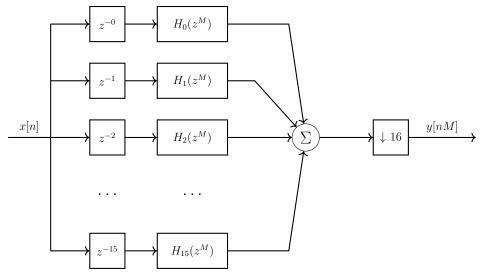

| 6.8  | Noble Identity                                                                                 | 101 |

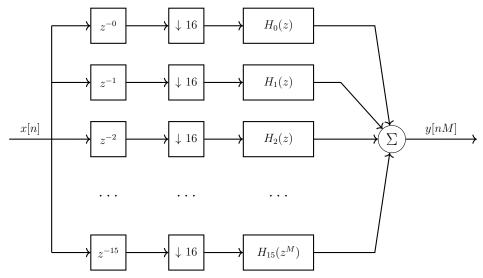

| 6.9  | Polyphase Partition of a Low Pass Anti Aliasing Filter                          | 103 |

|------|---------------------------------------------------------------------------------|-----|

| 6.10 | Polyphase Partition of a Low Pass Anti Aliasing Filter With Input Down Sampling | 103 |

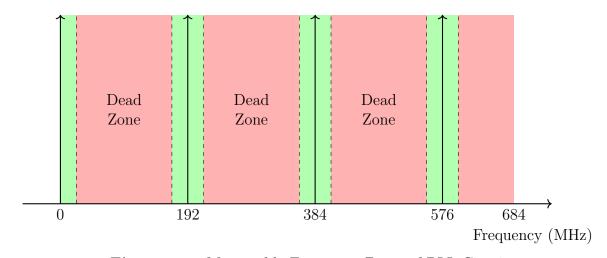

| 6.11 | Measurable Frequency Zones of PLL Circuit                                       | 104 |

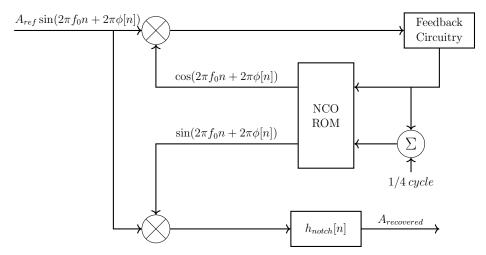

| 6.12 | Amplitude Recovery Circuit                                                      | 106 |

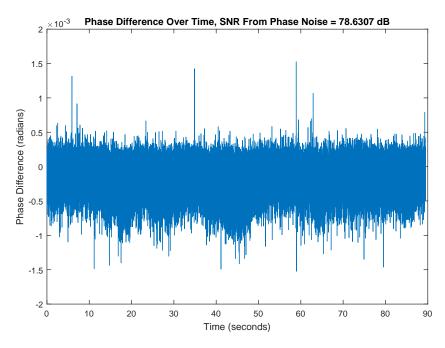

| 6.13 | Baseline Noise at Output of Phase Measurement Circuit                           | 107 |

| 6.14 | Hardware Phase Detector Output                                                  | 107 |

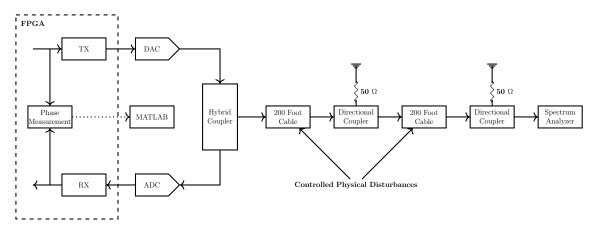

| 7.1  | Lab Measurement Apparatus                                                       | 109 |

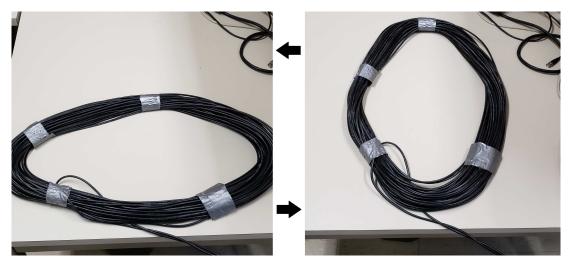

| 7.2  | Coaxial Cables Hung From Utility Poles                                          | 112 |

| 7.3  | Experiment on Flexing Cable in a Model Network                                  | 113 |

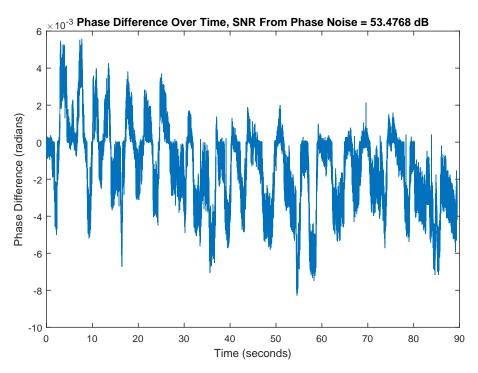

| 7.4  | Phase Fluctuations from Flexed Cables                                           | 113 |

| 7.5  | Hung Cable for Experiment on Lightly Shaking                                    | 114 |

| 7.6  | Phase Fluctuations from Shaken Cables                                           | 115 |

| 7.7  | Walked Over Cable Experiment                                                    | 116 |

| 7.8  | Phase Fluctuations from Walked Over Cables                                      | 117 |

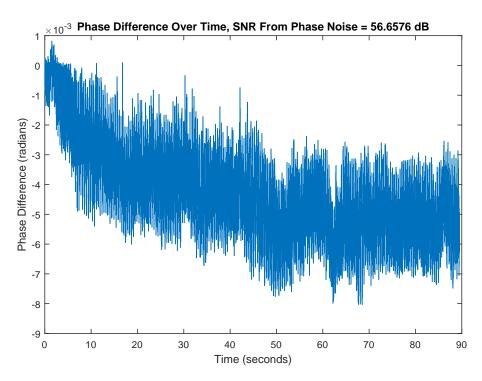

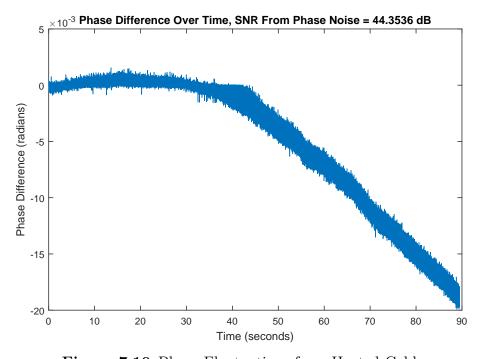

| 7.9  | Heated Cable Experiment                                                         | 118 |

| 7.10 | Phase Fluctuations from Heated Cables                                           | 118 |

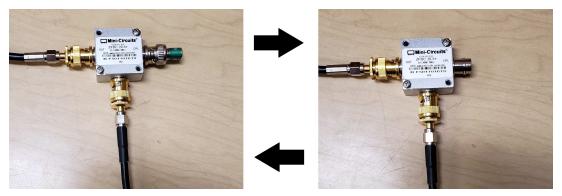

| 7.11 | Terminated and Unterminated Tap Experiment                                      | 119 |

| 7.12 | Phase Fluctuations from an Unterminated 20 dB Tap                               | 120 |

| 7.13 | Phase Fluctuations from a Alternately Terminated and Unterminated 20 dB         |     |

|      | Tap                                                                             | 121 |

| A.1  | Example Gray Coded 16-QAM Constellation for 4 Example Bits $(y_1, y_2, y_3, y_4)$ | 127 |

|------|-----------------------------------------------------------------------------------|-----|

| A.2  | Modulation Error                                                                  | 128 |

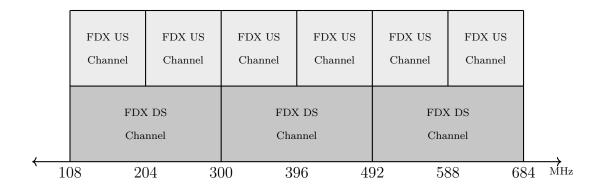

| A.3  | Full Duplex Band Allocation                                                       | 131 |

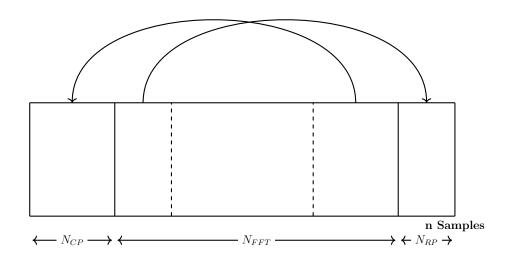

| A.4  | OFDM Cyclic Prefix and Window Algorithm                                           | 131 |

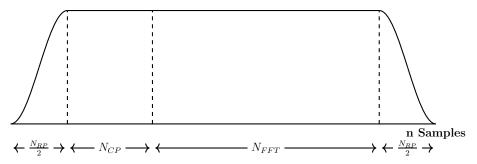

| A.5  | Cyclic Prefix and Roll Off Insertion                                              | 132 |

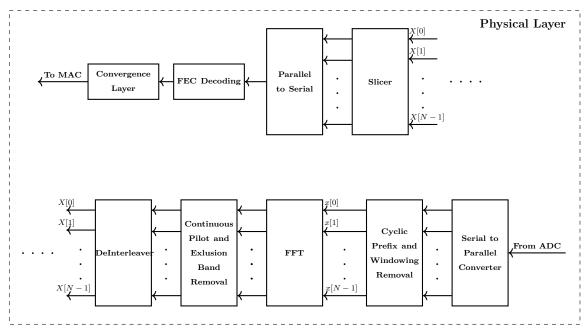

| A.6  | Simplified Upstream PHY Processing                                                | 133 |

| A.7  | 16-QAM Slicer                                                                     | 135 |

| A.8  | Power Flow Through a Directional Coupler                                          | 136 |

| A.9  | Example Losses Through a Typical Coaxial Cable Network, Losses Are Shown          |     |

|      | in Red and Signal Levels in Black                                                 | 137 |

| A.10 | Cable Modem Simplified Block Diagram                                              | 137 |

#### List of Abbreviations

ADC Analog Digital Converter

AM Amplitude Modulation

AWGN Additive White Gaussian Noise

BCH-LDPC Bose-Chaudhuri-Hocquemghemv Low Density Parity

Check

BER Bit Error Rate

BW Bandwidth

CATV Community Antenna TeleVision

CM Cable Modem

CMTS Cable Modem Termination System

CNR Carrier Noise Ratio

CP Cyclic Prefix

DAC Digital Analog Converter

DFT Discrete Fourier Transform

DS Down Stream

DOCSIS Data Over Cable System Interface Specification

DSL Digital Subscriber Line

ENOB Effective Number Of Bits

FDX Full Duplex

FEC Forward Error Correction

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

HDX Half Duplex

HFC Hybrid Fibre Coaxial

I Inphase

IDFT Inverse Discrete Fourier Transform

IFFT Inverse Fast Fourier Transform

ISI Inter-Symbol Interference

LMS Least Mean Squared

LPF Low Pass Filter

MAX Media Access Control

MER Modulation Error Ratio

NCO Numerically Controlled Oscillator

OFDM Orthogonal Frequency Division Multiplexing

OFDMA Orthogonal Frequency Division Multiple Access

PA Power Amplifier

PAPR Peak to Average Power Ratio

PDF Probability Density Function

PHY Physical Layer

PLC Phy Link Layer

PLL Phase Locked Loop

PSD Power Spectral Density

Q Quadrature

QAM Quadrature Amplitude Modulation

QoS Quality of Service

RAM Random Access Memory

RLS Recursive Least Squared

RMS Root Mean Squared

ROM Read Only Memory

RP Roll-Off Period

RX Receiver

SNR Signal to Noise Ratio

SOI Signal Of Interest

TX Transmitter

US Up Stream

VNA Vector Network Analyzer

# List of Symbols

| $A_{ref}$                   | Amplitude of sinusoid being input to the PLL              |

|-----------------------------|-----------------------------------------------------------|

| $oldsymbol{a}(t)$           | Time varying amplitude of a sinusoid                      |

| $\alpha_r$                  | Attenuation constant associated with an echo at point $r$ |

| $\delta[n]$                 | Discrete impulse sequence                                 |

| $\delta(t)$                 | Continuous impulse signal                                 |

| $\Delta oldsymbol{t}[n]$    | Sequence of time jitter samples in seconds                |

| $\Delta oldsymbol{\phi}[n]$ | Sequence of time jitter samples in radians                |

| e[n]                        | Difference signal of an adaptive filter                   |

| f                           | Digital frequency in cycles/sample                        |

| F                           | Analog frequency in hertz                                 |

| $F_s$                       | Sampling frequency in hertz                               |

| $F_{PLL}$                   | Sampling rate of the PLL                                  |

| $\mathcal{F}\{x[n]\}$       | DOCSIS FFT of $x[n]$                                      |

| $\mathcal{F}^{-1}\{X[k]\}$  | DOCSIS IFFT of $X[k]$                                     |

| G(z)                        | Open loop PLL transfer function                           |

| h[n]                        | Discrete system impulse response                          |

| h(t)                        | Time domain channel response                              |

| $h_{ij}(t)$                 | Response between points $i$ and $j$                       |

| $H(\Omega)$                 | Analog frequency domain response                          |

| H(z)                        | Closed loop PLL transfer function                         |

| $H_{lf}(z)$                 | Transfer function of PLL loop filter                      |

| $H_{notch}(z)$              | Tranfer function of a notch filter                        |

| $K_x$                       | Gain of scaling factor "x" in a PLL                       |

| $K_d$                       | Phase detector gain                                       |

| n                           | Sample number                                             |

| n(t)                        | Time domain thermal noise                                 |

$N_{FFT}$ FFT/DFT size  $N_{CP}$ Cyclic Prefix size  $N_{RP}$ Roll off Period size  $N_r$ Number of bits used to represent the frequency in an NCO  $N_a$ Number of bits used to represent the phase in an NCO  $N_d$ Number of bits used to represent output sinusoid in an NCO  $\phi[n]$ Discrete time varying phase in cycles  $\phi^r[n]$ Discrete time varying phase in radians  $\phi_i[n]$ PLL input phase in cycles  $\phi_o[n]$ PLL output phase in cycles  $\phi_e[n]$ PLL phase difference in cycles  $\phi_{det}[n]$ Output of phase detector in a PLL in cycles  $\phi(t)$ Continuous time varying phase in radians Digital power of signal x in  $V^2$  $P_x$  $q_x[n]$ Quantization noise sequence introduced by x Magnitude of a pole on the unit circle ρ  $\widetilde{r}(t)$ Complex passband signal received at the receive side of the hybrid including distortions introduced by network  $R_1(z)$ PLL scaling factor =  $K_d \cdot H_{lf}(z) \cdot K_1$  $\sigma_x^2$ Variance of x Step size of a discrete signal  $S_{xx}(2\pi F)$ Analog power spectral density of x  $S_{xx}(e^{j2\pi f})$ Digital power spectral density of x  $t_r$ Time a echo at point r takes to propagate to the received side of the hybrid  $T_c$ Coherence time of the channel in seconds  $T_d$ Dwell time of an echo canceller in seconds

Mean of x

$\mu_x$

| V                          | Unit for a digital signal relating electric potential of the input of ADCs and   |

|----------------------------|----------------------------------------------------------------------------------|

|                            | output of DACs to the digital signal level                                       |

| $V^2$ samples              | Digital energy, samples are analogous to seconds in the digital domain so the    |

|                            | energy is the sum of the squares of digital samples                              |

| $V^2$                      | Digital power, average power in a sequence of digital samples is the digital     |

|                            | energy divided by the number of samples averaged by                              |

| $\frac{V^2}{cycle/sample}$ | Digital power spectral density. $V^2$ per digital cycle related to sampling fre- |

|                            | quency.                                                                          |

| w[n]                       | Taps of a digital filter                                                         |

| $\omega$                   | Digital frequency in radians                                                     |

| Ω                          | Analog frequency in radians                                                      |

| $\overline{x^2[n]}$        | Mean squared of $x[n]$                                                           |

| $\widetilde{x}[n]$         | Real passband version of complex baseband $x[n]$                                 |

| $\widetilde{x_1}(t)$       | Complex passband signal transmitted by the node                                  |

| $\widetilde{x_2}(t)$       | Complexx passband signal transmitted by the cable modems                         |

| y[n]                       | Output of a discrete time system                                                 |

| z                          | Result of Z transform = $e^{jw}$                                                 |

#### 1. Introduction

#### 1.1 History of Cable Systems

The history of CATV (Common Antenna Television) or cable networks probably began in the late 1940's when a radio operator named L.E. "Ed" Parsons responded to a challenge from his wife who wanted pictures with her radio [1]. Ed went to the tallest nearby building and constructed an antenna able to pick up a weak television signal which he was able to connect to his television. Before long, much of his town wanted to be connected to this antenna to receive a television signal and the CATV boom had started. When Ed was able to pick up the television signal, he was responding to a need felt through much of rural America. These Americans were too distant from most commercial stations to pick up a television signal with a regular antenna. In other parts of America, CATV was simultaneously developing and consumers soon clamored to be connected to a cable network [1]. This quickly resulted in CATV becoming large business and the technology slowly began to develop into what we see today.

In the next few decades several technological improvements began to make their way into the traditional CATV networks. The improvements mainly consisted of increasing the number of channels that the cable network was able to support. An important technological innovation was the introduction of a upstream path in CATV networks. The upstream path would allow cable subscribers to communicate back to the head end of the CATV network and thus two-way communications was achievable. The upstream communication technology was originally developed for military applications, but was quickly integrated

into commercial CATV which led to the birth of early cable modems [2].

The rapid growth of CATV networks continued up until the late 1980's with the advent of the internet. It was around this time that cable providers switched from a traditional analog distribution to a digital system. A key part of this switch was to divide the existing network into HFC (Hybrid Fibre Coaxial) networks which allowed for faster data transmission. By making these changes cable networks were able to compete with phone companies which had begun to offer services such as DSL (Digital Subscriber Line), which offered much faster data transmission than cable was initially able to provide [3].

The CATV network became digital and consumers modern demands were now able to be met. CATV subscribers wanted modern services such as pay TV, point-to-point services such as teleconferencing and high-speed data exchange, and eventually the internet. The main drive for this advancement was pay television such as Home Box-Office (HBO). The cable provider's cable modems that they had located in the subscribers homes slowly transformed into devices that were able to provide all of these services.

Early on the electronics for cable networks was proprietary equipment from a single manufacturer [4]. While there was more then one equipment manufacturer, a cable network had to commit to one, which meant that manufactures had a monopoly on any expansion to the network. In order to create competition among manufacturers, service providers formed a not-for-profit organization in 1988. The purpose of this organization, which was called CableLabs, is to create standards that would allow interoperability of equipment supplied by different manufactures [5]. CableLabs introduced its first interoperable standard, referred to as Data Over Cable Service Interface Specification (DOCSIS), in 1997 [6].

# 1.2 Modern Cable Systems

The first version of the North American data over cable standard, known as DOCSIS 1.0, was released by Cable Labs in 1997. In this initial version of DOCSIS, the DOCSIS network was described as many Cable Modems (CMs) located in subscriber households connected

to a Cable Modem Termination System (CMTS) via a HFC network [6]. In the upstream direction (from the households to the head end,) the CMs were described as transmitters and the CMTS as a receiver. In the downstream direction (from the head end to the household), the CMs were treated as receivers and the CMTS as the transmitter. After the release of DOCSIS 1.0, the standard continued to evolve to meet the demands of modern consumers. The demand for more bandwidth, particularly in the upstream direction, was a source of major upgrades to DOCSIS.

Following the releasal of DOCSIS 1.0 in 1997 DOCSIS 1.1, which added VOIP (Voice Over IP) service, was released. DOCSIS 1.0 and DOCSIS 1.1 are collectively referred to as DOCSIS 1.x. Following DOCSIS 1.x was DOCSIS 2.0, which released December 31, 2001 and offer a 3X increase in upstream speeds. DOCSIS 3.0 was released August 4, 2006. This release offered much higher speeds in both directions. Finally DOCSIS 3.1 was released on October 29, 2013 which again offered greatly increased speeds and higher efficiency. The next iteration, known as Full Duplex (FDX) DOCSIS 3.1, was released on October 26, 2017. It promises symmetric gigabit service greatly increasing the upstream capacity of DOCSIS 3.1 [7].

Table 1.1 [7] summarizes the capability of the sequence of DOCSIS standards. It shows the steady increase of data throughput and services available through the standard. The improvements in DOCSIS were mainly due to higher Quadrature Amplitude Modulation (QAM) orders on the upstream and downstream paths, as well as increased support for channel bonding and Internet Protocol Version 6 (IPv6). The increase in the modulation order of the QAM allowed for more throughput over the same bandwidth. With DOCSIS 3.1 the modulation scheme was augmented to include Orthogonal Frequency Division Multiple Access (OFDMA) to further increase data throughput and spectral efficiency. The demand for more bandwidth seems to be ever increasing, which will continue to pressure cable providers to innovate and adapt.

**Table 1.1** DOCSIS Standard Progression

|             | Highlights    | Downstream | Upstream               | Release |

|-------------|---------------|------------|------------------------|---------|

|             |               | Capacity   | Capacity               | Date    |

|             | Initial Cable |            |                        |         |

| DOCSIS 1.0  | Broadband     | 40 Mbps    | 10 Mbps                | 1997    |

|             | Technology    |            |                        |         |

| DOCSIS 1.1  | Added VOIP    | 40 Mbps    | 10 Mbps                | 2001    |

|             | Service       |            |                        |         |

|             | Higher        |            |                        |         |

| DOCSIS 2.0  | Upstream      | 40 Mbps    | 30 Mbps                | 2002    |

|             | Speed         |            |                        |         |

|             | Greatly       |            |                        |         |

| DOCSIS 3.0  | Enhanced      | 1 Gbps     | $100 \; \mathrm{Mbps}$ | 2006    |

|             | Capacity      |            |                        |         |

|             | Capacity and  |            |                        |         |

| DOCSIS 3.1  | Efficiency    | 10 Gbps    | 1-2 Gbps               | 2013    |

|             | Progression   |            |                        |         |

|             | Symmetrical   |            |                        |         |

| Full Duplex | Streaming     | 10 Chng    | 10 Chas                | 2017    |

| DOCSIS 3.1  | and Increased | 10 Gbps    | 10 Gbps                | 2017    |

|             | Upload Speeds |            |                        |         |

#### 1.3 Future Cable Systems

The demand for high speed internet service has continued to grow and will continue to grow into the foreseeable future. It is currently at a point where it has begun to be economical for telephone companies to plow fibre directly to the homes of subscribers to meet the demand. Cable service providers believe that they can compete with this fibre to the home service without having to completely replace their expensive coaxial cable plants with optical fibres. As described in the previous section the cable service providers have been incrementally increasing the throughput of their cable plants through a series of technological changes. Two proposed changes of particular interest to the cable providers are decentralizing the CMTS by remoting the physical layer, referred to as Remote Phy, and introducing new technology that supports Full Duplex, which allows for simultaneous upstream and downstream communication in the same spectrum.

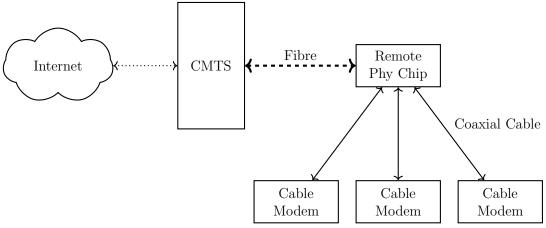

Figure 1.1 Remote Phy CATV System

#### 1.3.1 Remote Phy

For sending information up and down fibre there are at least two fundamental methods in the context of HFC plants: Linear HFC and Digital HFC. Up until recently Linear HFC was most widely used in the cable market due to its relative inexpensiveness and ease of use. However, Linear HFC has some clear disadvantages. Linear HFC is limited in the distance it can send data, it requires significant upkeep, and it introduces noise that can not be removed. Increasingly the industry is moving towards Digital HFC as it can travel long distances, support more wavelengths, has lower fixed and operating costs, scales well, and the noise inherent to the signal can be removed [8]. Digital HFC has the disadvantage of being more complicated than Linear HFC. Changing DOCSIS to Digital HFC can be accomplished by using DOCISIS Remote Phy technology. DOCSIS currently uses a centralized CMTS (Cable Modem Termination System) located at the cable providers head end. This CMTS has a phy chip that modulates data into a signal appropriate for transmission on a coaxial cable network. The basic premise of Remote Phy is to take this phy chip and locate it closer to the subscriber. The CMTS would be connected to the phy chip through fibre lines using Digital HFC.

#### 1.3.2 Full Duplex

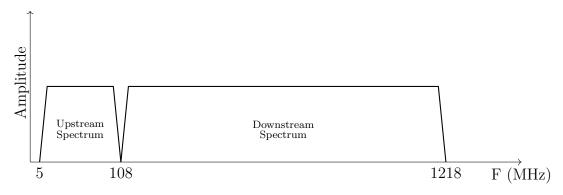

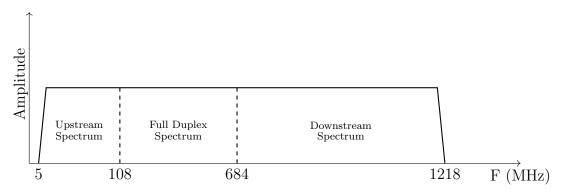

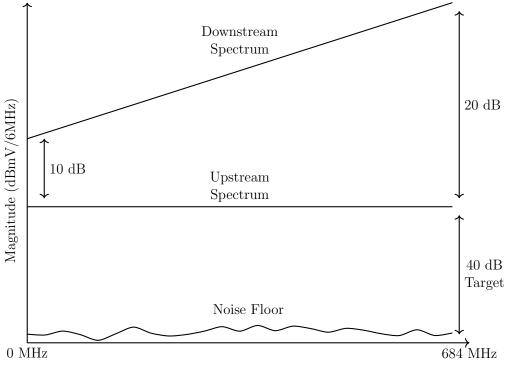

A hot topic currently for cable providers is the switch to full duplex, which promises great increases in the upstream communication speeds that can be offered. Historically bandwidth was used for communication in one direction only, and as a result the spectrum is allocated in such a way that the downstream has a much larger slice than the upstream. Today, there is more demand for upstream traffic and more upstream bandwidth must be allocated in order to support the increased bit rates needed for such things as cloud services, uploading pictures, and online games. However, the amount of spectrum available is finite and an increase in upstream capacity cannot come at the cost of reduced downstream. In the old frequency division duplex system (or half duplex), the spectrum was split between the upstream and the downstream with the upstream occupying the lower frequency band and the downstream occupying the upper as shown in Figure 1.2. The next logical step in the evolution of cable systems is to use a full duplex system in which upstream and downstream spectra occupy the same portion of bandwidth at the same time. Switching to full duplex will vastly increases the upstream bandwidth without sacrificing downstream, as shown in Figure 1.3. Moving to a full duplex system would increase the data throughput in the upstream direction and allow the coaxial cable networks to remain competitive with fibre to the home networks for years to come.

Figure 1.2 Half Duplex Spectrum

Figure 1.3 Full Duplex Spectrum

## 1.4 Obstacles in Full Duplex

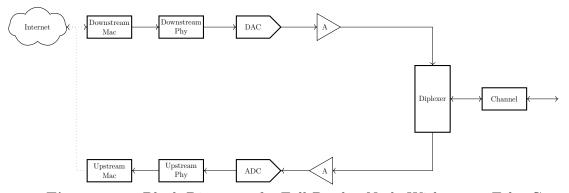

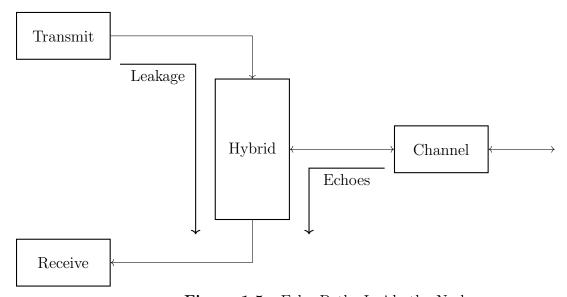

Changing a network from one that supports frequency division duplex to one that supports a mix of full duplex and frequency division duplex requires a number of changes to the hardware in the system. Perhaps the most significant of which is modifying the diplexer, which is essential to frequency division duplex, to allow two way communication. Modifying the diplexer means replacing it with a specialized directional coupler as shown in Figure 1.4 as a "Hybrid".

Figure 1.4 Block Diagram of a Full Duplex Node Without an Echo Canceller

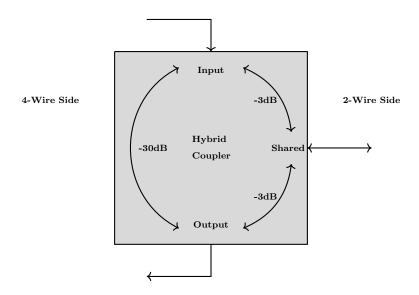

A diplexer separates the upstream spectrum from the downstream spectrum using strategically placed low pass and high pass filters. However, the full duplex portion of the system supports two way communication over part of the bandwidth, so simply filtering to separate a signal is no longer viable. Accommodating the full duplex portion of the spectrum involves the diplexer being replaced by a directional coupler. This directional couple can have at most approximately 30dB of isolation between the upstream and the downstream direction in the full duplex band. The relatively low isolation in the directional coupler means that some of the downstream signal will leak into the upstream received signal. This leakage is especially problematic as the downstream signal has a much higher signal level than the upstream signal at the CMTS, which has been greatly attenuated in traversing the cable system from CM to CMTS. The echo paths and leakage through the hybrid are illustrated in Figure 1.5.

Figure 1.5 Echo Paths Inside the Node

The hybrid also has greater loss than the diplexer, which means that any power amplifiers in the processing chain must be driven higher. Driving the power amplifier higher causes it to become nonlinear by approaching its compression point, which adds more distortion into the higher amplitude portions of the signal. Due to this factor and a number of other noise sources on the upstream data such as noise from the PAs (Power Amplifiers), noise from the ADCs and DACs, and oscillator phase noise, the SNR on the upstream data is likely to be very low if not negative. A rough sketch of the spectrum is shown in Figure 1.6.

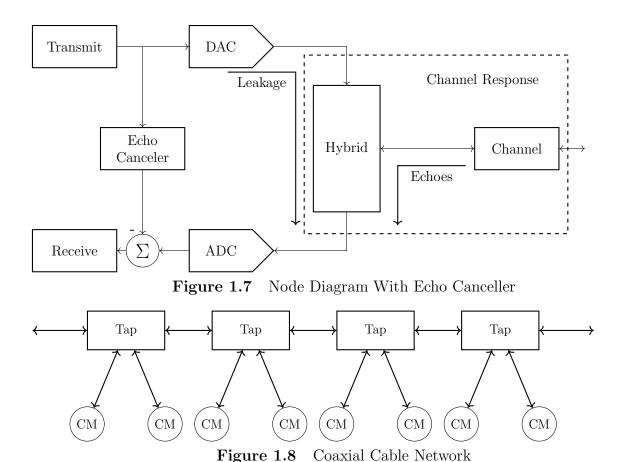

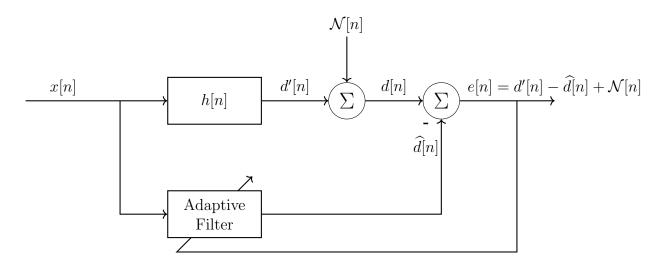

If the upstream signal is to be recovered the self interference from the downstream signal needs to be removed along with any echoes that the coaxial cable network introduces. It is for these reasons that an echo canceller is needed to restore the upstream signal. In

Figure 1.6 Received Spectrum

Figure 1.7, the location of the echo canceller in the node is shown. The function of the echo canceller is to exactly mimic the "echo transfer function" of the system so that the echo can be subtracted from the received signal. It is very difficult to measure the "echo transfer function" while receiving the upstream signal as the upstream signal will bury the echo. The echo canceller can also be thought of as a self interference canceller, as it also has the job of removing the portion of the transmitted downstream signal that "leaks" through the hybrid into the received upstream signal.

The echoes are introduced by the taps and CMs in the coaxial cable network, as well as any tiny imperfections present in the coaxial cables. As can be seen in Figure 1.8, the cable network is made up of lengths of coaxial cable connected to a series of taps (directional couplers), which take some of the signal and couple it to the attached cable modems (CM in the diagram), which would be located inside the users home. The coaxial cable itself is lossy, meaning that the signal will become increasingly attenuated as it moves through the network. To help make up for this loss, as well as for the power that is lost from the taps,

the fraction of the power being diverted in each tap depends on the location of the tap in the network. The taps are arranged so that each cable modem gets the same amount of power. Unfortunately, these taps are not perfect by nature and generate reflections that show up at the CMTS as echoes. As the downstream signal hits each of the taps an impedance mismatch means that the tap cannot absorb all of the incoming power and thus some is reflected.

#### 1.5 Statement of the Problem

The cable industry has planned for full duplex to be the next step in the evolution of DOCSIS. The DOCSIS 3.1 full duplex standard was released in October 2017, its feasibility was based entirely on theory and simulation and also under the perhaps shaky assumption that advanced hardware could be developed that supports it. This being the case, there are still a few unresolved issues around implementing a full duplex system in hardware. These

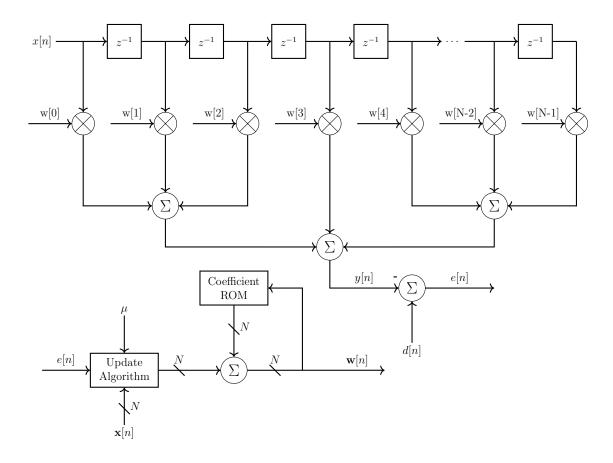

issues mostly center on the echo canceller. The echo canceller needs a significant time to determine the echo response of the channel. If the echo response of the channel changes with time as it is certain to do, the rate of change may be too fast to be considered constant over a defined "dwell time". This results in an improperly canceled signal and a unacceptably high noise interference. The main objective of this research is to determine the rate of change of the channel and the effect this rate of change has on the echo cancellation. To accomplish this a system will be designed and implemented on an FPGA that measures the characteristics of the channel as a function of time and determines the residual effects after echo cancellation.

In order to determine the characteristics of the channel that are most susceptible to rapid change, a model of a full duplex cable network is developed. Mathematical descriptions of the significant components in a full duplex cable network must be developed in order to properly model transmission in the system. These mathematical descriptions outline noise sources inherent to the system, so that their effect on echo cancellation can be accounted for. Once a detailed model of the system is developed it will be clear what signals the echo canceller needs to remove. The effect of the channel changing with time should be clear and the parameters associated with the change should be revealed. The measurement system can then be designed to find to these parameters.

#### 1.6 Thesis Outline

The remainder of the thesis is organized as follows. Chapter 2 goes into detail on the full duplex DOCSIS network and provides mathematical description and analysis of the critical components that make it up. At the end of Chapter 2, analysis is done on the received upstream signal in the full duplex node to highlight the noise corrupting it. The result of this analysis is an equation showing the different impairments on the received signal. Chapter 3 uses this equation to show the need for self interference (echo) cancellation in the Full Duplex Node. Chapter 3 also provides analysis on echo cancellation and shows that it is limited by phase instability. The limitation that phase shifts imposes on echo cancellation is then

expanded into showing the need for a stable channel response for successful echo cancellation. Finally, Chapter 3 parameterizes the channel and provides a solution for characterizing the channel.

Chapter 4 analyzes a Phase Locked Loop based method selected to measure the channel parameters of importance outlined in 3. Chapter 5 goes through the issues of a high performance PLL circuit that is needed to measure the parameters of interest. Chapter 5 discusses the hardware implementation of the PLL as well as design procedures for selecting the parameters of the loop. Special care is given to the selection of the word lengths used in the PLL implementation on an FPGA.

The objective of Chapter 6 is to verify the design from Chapter 5. The chapter verifies that the Chapter 5 design meets all the goals outlined in Chapter 3 by simulating both the network and the PLL in MATLAB. Once the design is verified in MATLAB, it is built on an FPGA and further verified. The FPGA implementation shows that the design is able to meet the design goals. A series of measurements are explained, performed, and analyzed in Chapter 7. The measurements performed further show the success of the system as well as providing insight into the research goals of this thesis. Finally, the results of the research are summarized in Chapter 8. Chapter 8 concludes the work done in the thesis as well as outlining future work that can be performed in this area of research.

# 2. Critical Components of a Full Duplex Network

In this chapter the operation and limitations of a full duplex DOCSIS network is explored to provide the necessary background for the subsequent chapters. Chapter 3 will frame a clear statement of the problem using concepts explored in this chapter as a reference. This chapter begins by showing the architecture of the full duplex system specified in version 3.1 of DOCSIS. The system architecture and the mathematical models of its components are developed to give the research a firm theoretical basis. The mathematical descriptions of the components reveal some of the limitations of the full duplex DOCSIS network. After the relevant components are described the system is analyzed and the major issues explored.

## 2.1 Architecture of a Full Duplex Cable System

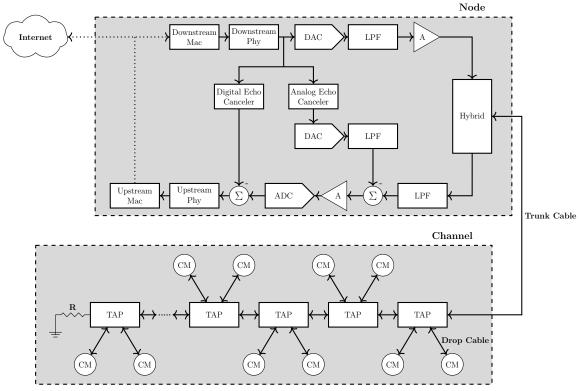

The architecture of a FDX DOCSIS network is shown in Figure 2.1. The node connects to and receives data from the internet. It maps the data into symbols and uses these mapped symbols to modulate a carrier. The down stream bound modulated carrier is transmitted over coaxial cable to Cable Modems (CMs) in subscriber households. In the opposite direction, the CMs in subscriber households generate data which modulates a carrier that is sent over the cable network to the CMTS. The network connects CMs in subscriber households to a node in the head end. The signals entering the network from the CMs to the node are considered to be in the upstream direction, and the signals sent from the node to network are considered to be in the downstream direction.

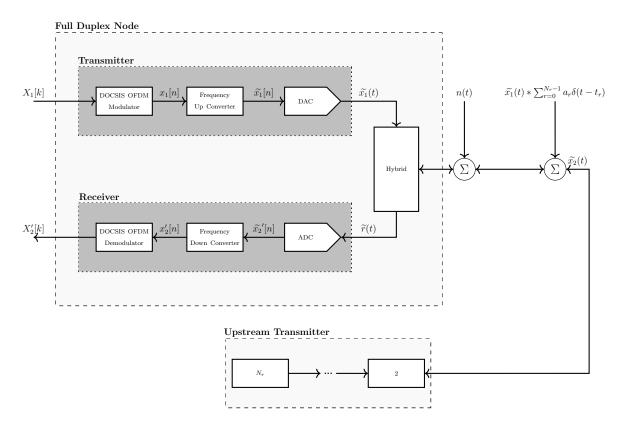

Inside the node section of Figure 2.1 there are a number of components. The data coming from the internet is first sent to the Media Access Control (MAC) layer of the downstream

Figure 2.1 Full Duplex DOCSIS Network Architecture

path in the node. This MAC layer controls transmission of DOCSIS signals through a variety of algorithms which are summarized in Appendix 8.2. After the MAC layer, the data is passed into the Physical (PHY) layer. The function of this PHY layer is to convert the data into OFDM symbols. The PHY layer is also responsible for adding Forward Error Correction (FEC) to the incoming packets from the MAC layer [7]. After the data has been transformed into OFDM symbols, it is converted to an analog waveform in a Digital Analog Converter (DAC). This analog waveform is filtered to remove images and amplified to give it the power profile specified in the DOCSIS 3.1 standard. The signal is then sent through a directional coupler (Hybrid) and into the trunk cable.

In the upstream direction the processing in the node is in the reverse order. The upstream analog waveform is first band limited with a filter, passed through a low noise amplifier, and then converted to digital samples by an Analog to Digital Converter (ADC). The samples are filtered digitally and organized into OFDM symbols. These OFDM symbols are then

demodulated in the upstream PHY layer. The recovered data is then sent to the upstream MAC layer and from there onto the internet.

The transmitted signals are translated in frequency and placed into channels by various combinations of filtering, up conversion, and down conversion. A channel is the bandwidth allocated for one full duplex OFMDA spectrum. After the analog waveform has been organized into channels it is transmitted into a trunk cable. This cable then connects to a series of multi-port directional couplers, referred to as taps, with specific coupling strengths [9]. Cable modems located in the subscriber households are connected to the taps via drop cables. Figure 2.1 shows only two CMs attached to each tap, but the number of taps in a "tap" varies and depends on the density of subscribers. The end of the trunk is terminated to prevent impedance mismatches that generate interference in the form of echoes. Impedance mismatches will be discussed in detail later in this chapter.

#### 2.2 Functional Operation of Critical System Components

This section of the chapter will describe the components mentioned in the previous section. Mathematical and functional descriptions of the components will shed light on the issues faced in the full duplex DOCSIS network. Only the blocks that directly relate to the measurements of interest done in this thesis are described, descriptions of the MAC layer, DOCSIS PHY layer components, taps, and cable modems can be found in Appendix 8.2.

For the purposes of this research, the transmit signal will be a single cosine tone at some arbitrary frequency within the FDX band. The analysis determined in the subsequent sections are done in the general case. The results of these analysis are later used to apply to the single test tone operation.

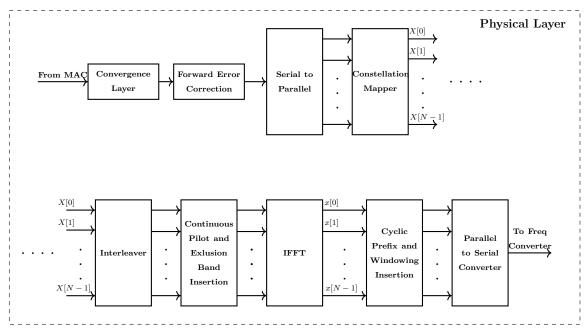

# 2.2.1 Downstream PHY Layer

The physical layer of the DOCSIS 3.1 node is mainly responsible for converting the incoming binary data into OFDM symbols. The physical layer also maps packets received

from the MAC layer into FEC codewords [7]. A simplified block diagram of the DOCSIS 3.1 PHY layer is illustrated in Figure 2.2. Figure 2.2 omits a few details of the actual processing path, mainly the PLC (Phy Link Layer), of the DOCSIS 3.1 PHY layer but the essentials for modulation are all present. Descriptions of the significant components shown in this diagram can be found in Appendix 8.2. Readers unfamiliar with DOCSIS cable networks may need to read this appendix to fully understand the remainder of this chapter.

The word "symbol" is widely used in the literature but it is used to refer to different things, before continuing it is of worth to define exactly what is meant by a "symbol" as it will be used in this thesis. From Figure 2.2 [7] it is seen that the IFFT block takes in parallel streams of  $N_{FFT}$  complex amplitudes generated by the constellation mapper. This group of  $N_{FFT}$  parallel complex amplitudes going into the IFFT block are collectively referred to as a frequency domain OFDM symbol. The output of the OFDM modulator after the parallel to serial converter is a set of  $N_{FFT} + N_{CP} + N_{RP}$  complex samples. The core of which is the  $N_{FFT}$  samples generated by the IFFT block. A cyclic prefix of  $N_{CP}$  is prepended to the core as well as a role off period of  $N_{RP}$  samples. This entire set of  $N_{FFT} + N_{CP} + N_{RP}$  complex samples are referred to as an OFDM symbol. Every frequency domain OFDM symbol is translated to an OFDM symbol that is sent to the frequency up converter.

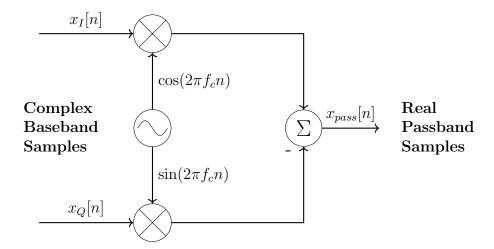

# 2.2.2 Converting a Complex Baseband to a Real RF

A crucial step in the formation of the DOCSIS spectrum is not shown in Figure 2.2. The processing path shown in Figure 2.2 outputs complex baseband OFDM symbols, this means that there is a real and imaginary component (also referred to as the Inphase and Quadrature components) and the spectrum of the signal only occupies the band from 0 to 192 MHz. However, in Figure 1.3 the region from 5 to 1218 MHz is shown as occupied. The broader spectrum is filled by parking a number of different complex baseband OFDM spectrums in different segments of the overall spectrum using a process called frequency up conversion. Each full duplex DOCSIS node produces a number of complex baseband OFDM spectrums that are up converted to different bands. This conversion is accomplished with

Figure 2.2 Simplified Downstream PHY Processing

the circuit shown in Figure 2.3. A frequency up converter separates the complex baseband signals into real and imaginary parts, multiplies them by quadrature sinusoids, then sums them to get a real bandpass signal.

Figure 2.3 Frequency Up Converter

The output of the frequency up converter as shown in Figure 2.3 is given by the following equations.

$$x_{pass}[n] = Re\{(x_I[n] + jx_Q[n])e^{j2\pi f_c n}\}$$

$$= x_I[n]\cos(2\pi f_c n) - x_Q[n]\sin(2\pi f_c n)$$

(2.1)

The output of the frequency up converter is a real version of the input with its frequency now centered at  $F_c$  Hz.

The local oscillator in (2.1) is shown to output pure noise free sinusoids. In practice the local oscillator will be corrupted in both amplitude and phase. The output of the quadrature local oscillator will take the form [10]:

$$\alpha_{TX}[n] = (1 + a_{TX}[n])e^{(j2\pi f_c n + \phi_{TX}[n])}, \tag{2.2}$$

where  $\phi_{TX}[n]$  is the phase noise of the carrier used to mix the incoming signal and  $a_{TX}[n]$  is the amplitude noise. The phase noise in the local oscillator, which is constructed digitally using a circuit known as an NCO (Numerically Controlled Oscillator), is due to truncation in the phase accumulator and the amplitude noise is due to truncation in the output tone. It is clear from (2.2) and (2.1) that frequency up conversion introduces phase noise to the signal and is therefore an imperfect process. It is important that this oscillator has as little phase noise as possible, as phase noise introduces inter carrier interference which will decrease the MER of the signal. More phase noise is introduced in the frequency down conversion process. The down converted signal takes on the following form:

$$x_{downconverted}[n] = x_{pass}[n] * h[n](1 + a_{RX}[n])e^{(-j2\pi f_c n + \phi_{RX}[n])}$$

$$(2.3)$$

where h[n],  $\phi_{RX}[n]$ , and  $a_{RX}[n]$ ] are the network response, the receiver oscillator phase noise, and the receiver oscillator amplitude noise respectively. Since the receive and transmit oscillators are locked to each other,  $Re\{x_{downconverted}\}$  becomes the inphase (real) received symbols and  $Im\{x_{downconverted}\}$  the quadrature (imaginary) received symbols. The phase noise terms introduced in the frequency down conversion will also contribute to inter carrier

interference and degrade the MER of the signal. This analysis shows that a significant amount of noise can be introduced in the frequency up conversion step of the DOCSIS processing chain.

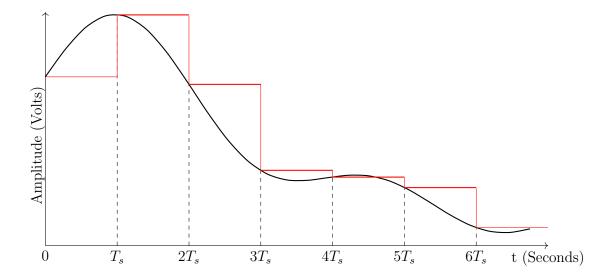

## 2.2.3 Digital to Analog Conversion

A crucial component in the DOCSIS processing path is the Digital to Analog Converter (DAC). A DAC converts a digital signal to an analog signal, but the process is unfortunately not without error. There are two types of error introduced by a DAC: amplitude error and phase error. This subsection explains the conversion process from digital to analog in sufficient detail to provide a footing for the sources of noise introduced by the DAC and the effect that they have on the echo cancellation process.

#### Principle of Operation

A DAC can be thought of as having a sample and hold like function, although this is not truly the case. A DAC converts a value held in a digital register to a analog voltage level and holds that analog voltage level until the value in the digital register is updated. The process can be viewed as the DAC sampling the digital value and holding it until the digital value is updated, normally over a time period equal to the sampling period. In doing this, a DAC takes a discrete time sequence and converts it to an analog signal.

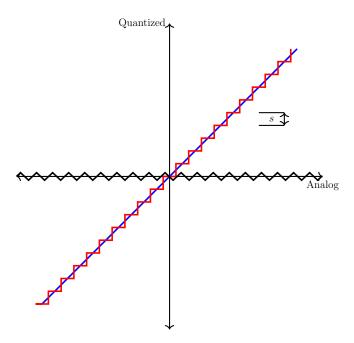

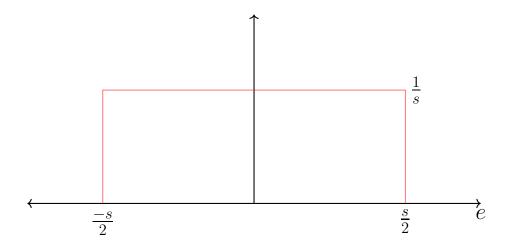

The resolution of the signal that is generated from the DAC depends on the number of bits used in the digital representation of the signal of interest and the sampling time,  $T_s$ , of the DAC. The more bits and the shorter the sample time the closer the output of the DAC will resemble the equivalent analog waveform. For example, a DAC that can output voltages between  $\pm 5V$  and has a 3-bit register could only output 8 different voltages between  $\pm 5V$ . A DAC with a 14-bit register could output  $2^{14} = 16384$  different voltages between  $\pm 5V$ . Having a finite number of output levels gives rise to quantization noise, which is discussed in further detail in Chapter 5. Figure 2.4 shows the DAC output (red) for an ideal signal (black) that was sampled at time  $nT_s$  and sent to the DAC.

Figure 2.4 Input and Output for a DAC

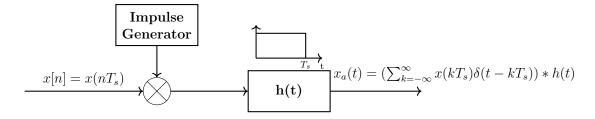

The sample and hold like function of the DAC can be approximated with a purely theoretical circuit that operates as if the the digital signal was multiplied by a series of impulses centered at the sampling times  $0, T_s, 2T_s, 3T_s, ...$  and then passed through a filter with an impulse response that is constant for one sample time and zero otherwise. In mathematical terms the impulse response of this constant response filter is defined as:

$$h(t) = \begin{cases} 1, & 0 \le t \le T_s \\ 0, & \text{Otherwise} \end{cases}$$

(2.4)

The frequency response of this filter is obtained by taking the Fourier transform of h(t) and is given by

$$H(\Omega) = T_s e^{-j\Omega \frac{T_s}{2}} \left( \frac{\sin(\frac{\Omega T_s}{2})}{\frac{\Omega T_s}{2}} \right)$$

(2.5)

where:

$T_s =$ Sampling Time of the DAC in seconds

$\Omega = \text{Analog Frequency in radians/second}, = 2\pi F$

Figure 2.5 Equivalent System of Sample and Hold Dac

The equivalent system of the DAC is shown in Figure 2.5. The effect of impulse sampling places an infinite number of spectral copies of the original signal at integer multiples of the sampling rate. Therefore, the output of the impulse sampler in the frequency domain is the infinite sum of spectral copies,  $\sum F_s X(\Omega - k\Omega)$ . The filter with the impulse sampler reduces, but does not annihilate, these spectral copies. The spectral copies are removed by a low pass filter referred to as a reconstruction filter that is placed after the DAC. This reconstruction filter is shown as LPF in Figure 2.1 on page 14. The output of the system in Figure 2.5, which is the output of the DAC, has Fourier Transform

$$X_a(\Omega) = \sum_{k=-\infty}^{\infty} e^{\frac{-j\Omega T_s}{2}} \frac{\sin(\frac{\Omega T_s}{2})}{\frac{\Omega T_s}{2}} X(\Omega - 2\pi k F_s)$$

(2.6)

If the quantization noise of the signal is so fine it can be ignored and the reconstruction filter is perfect, which will never happen in practice, the output of the reconstruction filter is equal to the digital waveform sampled by the DAC. In which case the Fourier Transform of the output is

$$X_a(\Omega) = e^{\frac{-j\Omega T_s}{2}} \frac{\sin(\frac{\Omega T_s}{2})}{\frac{\Omega T_s}{2}} X(\Omega)$$

(2.7)

#### **Clock Jitter Noise**

The analysis for the output of the DAC was done for an ideal clock source where the sampling time is always at exact integer multiples of  $T_s$ . In reality the clock will have some jitter associated with it. This jitter in the edges of the clock introduces distortion to the

output of the DAC that cannot be removed. The time deviation between sample time  $nT_s$  and the corresponding rising edge of the clock is symbolized

$$\Delta \mathbf{t}[n] = \frac{\Delta \phi[n]}{2\pi F_0} \tag{2.8}$$

where:

$\Delta \mathbf{t}[n]$  = Sequence of Random Variables in Units Seconds

n = Sample Number

$\Delta \pmb{\phi}[n] = \text{Phase Deviation in Radians at Sample } n$

$F_0$  = Clock Rate in Hertz

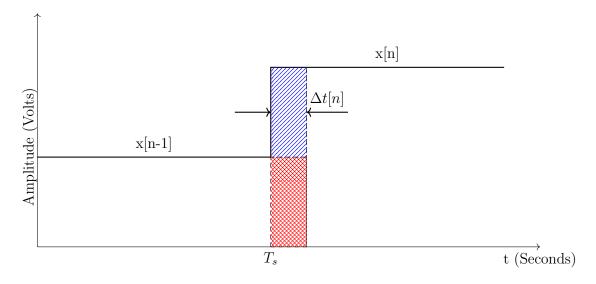

The phase deviation of the clock is usually specified in terms of its rms jitter in seconds, i.e in terms of  $\sqrt{\Delta \mathbf{t}^2[n]}$ . This jitter causes the time of the positive edge of the clock to change, which changes the length of the "hold" of the sample and hold of the DAC. This is made clear in Figure 2.6, where the jitter delays the clock edge that clocks x[n] into the register. In the case of Figure 2.6, the jitter causes x[n-1] to remain in the register by  $\Delta \mathbf{t}[n]$  too long.

Figure 2.6 Sampling Distortion Caused by Timing Jitter

Figure 2.7 Clock Jitter to Additive Noise Model

The error at sample time  $nT_s$  is illustrated in Figure 2.6 by the rectangle of width  $\Delta t[n]$  and height x[n] - x[n-1] that is shaded with blue diagonal hatching. The practical DAC output is that of the ideal DAC output less the error, i.e. minus the diagonal blue hatched pulse.

Since  $\Delta \mathbf{t}[n]$  is certain to be much smaller than  $T_s$ , the blue diagonal hatched pulse can be modeled as a delta function with area  $(x[n] - x[n-1])\Delta t[n]$  and located at  $t = nT_s$ . That is, the error introduced by the jitter at  $nT_s$  can be modelled by  $(x[n]-x[n-1])\Delta t(nT_s)\delta(t-nT_s)$ , that being the case, the error sequence is given by the following sum

$$x_{dac\_error}(nT_s) = \sum_{n=-\infty}^{\infty} (x[n] - x[n-1])\Delta t(nT_s)\delta(t - nT_s)$$

(2.9)

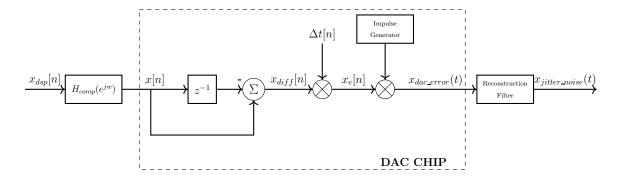

The model that converts clock jitter,  $\Delta \mathbf{t}[n]$ , into additive noise is presented as a block diagram in Figure 2.7. The circuit enclosed in the dashed rectangle is an implementation of (2.9), which is a model for the DAC with x[n] being the digital input to the DAC and  $x_{dac\_error}(t)$  being the additive noise corrupting the output of the DAC. The block before and the block after the DAC are an integral part of the digital to analog conversion, but are not built on the actual DAC chip.

The block that precedes the "DAC CHIP" is a compensation filter. The purpose of the compensation filter is to correct for the in-band distortion that the DAC introduces to the signal of interest. The in-band distortion appears as a  $\frac{\sin(\pi F/F_s)}{\pi F/F_s}$  roll off, which attenuates

higher frequencies. The compensation filter that corrects for this roll off is a linear phase filter with frequency response

$$H_{comp}(e^{jw}) = \begin{cases} \frac{2\pi F/F_s}{1 - e^{j2\pi F/F_s}}; \ 0 \le F \le \frac{F_s}{2} \\ 0; \text{Otherwise} \end{cases}$$

(2.10)

The magnitude response of this filter is  $\frac{\pi F/F_s}{\sin(\pi F/F_s)}$ , which is the multiplicative inverse of the DAC roll off.

It is of interest to determine the power spectral density of the jitter noise  $x_{jitter\_noise}(t)$ , which is the noise caused by jitter that will be added to the output of the DAC. Since the reconstruction filter is a low pass filter with a flat pass band its output has the same power spectral density as its input over its pass band and is 0 for frequencies in the stop band, assuming an ideal filter. Figure 2.7 shows the input to the reconstruction filter to be  $x_{dac\_error}(t)$ . Therefore the PSD of  $x_{jitter\_noise}(t)$  is that of  $x_{dac\_error}(t)$  over the band 0 to  $F_s/2$  and 0 otherwise.

Figure 2.7 shows that  $x_{dac\_error}(t)$  is a train of impulses multiplied by the digital signal  $x_e[n]$ . Since multiplication in the time domain is convolution in the frequency domain and the Fourier Transform of the train of time domain impulse is the set of frequency domain impulses  $\frac{1}{T_s}\delta(F-nF_s)$  for n=...,-1,0,1,..., the PSD of  $x_{dac\_error}(t)$  is an infinite set of frequency shifted versions of the PSD of  $x_e[n]$  with each being scaled by  $\frac{1}{T_s^2}$ . Therefore, the PSD of  $x_{jitter\_noise}(t)$  is that of  $x_e[n]$  scaled by  $\frac{1}{T_s^2}$ .

$$S_{x\_jitterx\_jitter}(2\pi F) = \frac{S_{xexe}(e^{j2\pi F/F_s})}{T_s^2}$$

(2.11)

The problem of finding the PSD for  $x_{jitter\_noise}(t)$  is reduced to finding the PSD of  $x_e[n]$ . Continuing to work back in Figure 2.7 has  $x_e[n] = x_{diff}[n]\Delta t[n]$ . Under conditions where  $\Delta t[n]$  is independent of  $x_{diff}[n]$ , which it always will be, it can be shown that the power spectral density of  $x_e[n]$  is the convolution of the PSDs of  $x_{diff}[n]$  and  $\Delta t[n]$ . From this we

get the following equation for the power spectral density

$$S_{xexe}(2\pi f) = \int_{-\infty}^{\infty} S_{xdiffxdiff}(e^{j(2\pi f - 2\pi\lambda)}) S_{\Delta t \Delta t}(e^{j2\pi\lambda}) d\lambda$$

(2.12)

where  $f = \frac{F}{F_s}$  and  $\lambda$  have units of cycles/sample,  $S_{xexe}(e^{j2\pi f})$  is the PSD of  $x_e[n]$ ,  $S_{xdiffxdiff}(e^{j2\pi f})$  is the PSD of  $x_{diff}[n]$ , and  $S_{\Delta t\Delta t}(e^{j2\pi f})$  is the PSD of  $\Delta t[n]$ .

Continuing to work back to  $x_{dsp}[n]$  shows  $x_{diff}[n]$  is linked to  $x_{dsp}[n]$  by the system function  $H(z) = H_{comp}(z)(1-z^{-1})$

$$H_{diff}(e^{j2\pi f}) = H_{comp}(e^{j2\pi f})(1 - e^{-j2\pi f})$$

$$= \frac{2\pi f}{1 - e^{-j2\pi f}}(1 - e^{-j2\pi f})$$

$$= 2\pi f$$

(2.13)

Since,  $S_{xdiffxdiff}(e^{j2\pi f}) = |X_{diff}(e^{j2\pi f})|^2$ ,

$$S_{xdiffxdiff}(e^{j2\pi f}) = |H_{diff}(e^{j2\pi f})|^2 |X_{dsp}(e^{j2\pi f})|^2$$

$$= |H_{diff}(e^{j2\pi f})|^2 S_{xdspxdsp}(e^{j2\pi f})$$

$$= 4\pi^2 f^2 S_{xdspxdsp}(e^{j2\pi f})$$

(2.14)

An expression for the PSD of  $x_{jitter\_noise}(t)$  is found by a series of back substitutions. First  $S_{xdspxdsp}(e^{j2\pi f})$  is used to get  $S_{xdiffxdiff}(e^{j2\pi f})$  and then  $S_{xdiffxdiff}(e^{j2\pi f})$  is back substituted to get the PSD for  $x_{jitter\_noise}(t)$ . After the chain of substitutions are made the equation becomes,

$$S_{xjitterxjitter}(e^{j2\pi f}) = \frac{1}{T_s^2} \int_0^{0.5} (2\pi\lambda)^2 S_{xdspxdsp}(e^{j2\pi\lambda}) S_{\Delta t\Delta t}(e^{j2\pi f - 2\pi\lambda}) d\lambda$$

(2.15)

A special case of great importance to this thesis is  $x_{dsp}[n] = \cos(2\pi f_0 n) = \cos(2\pi F_0/F_s n)$ . In this case  $S_{xdspxdsp}(2\pi F) = \frac{1}{2}\delta(F/F_s - F_0/F_s)$  or  $\pi\delta(2\pi F/F_s - 2\pi F_0/F_s)$  and  $S_{xjitterxjitter}(2\pi F) = \frac{1}{2}\delta(F/F_s - F_0/F_s)$   $\frac{(2\pi F_0/F_s)^2}{2}S_{\Delta t\Delta t}(e^{j2\pi(F-F_0)/F_s})$ , which is simply  $S_{\Delta t\Delta t}(e^{j2\pi F/F_s})$  shifted in frequency by  $F_0$  and scaled by  $\frac{1}{2}(2\pi F_0/F_s)^2$ .

The equation for the PSD of  $x_{jitter\_noise}(t)$  can be verified through use of Parseval's Theorem [11], by using a time domain analysis to get the total power in  $x_{jitter\_noise}(t)$ . Since  $H_{diff}(e^{j2\pi f}) = 2\pi f$ ,  $x_e[n]$  has a particular relationship to  $x_{dsp}[n]$ . A system with a transfer function of  $2\pi f$  is known as a differentiator. Therefore  $x_e[n]$  can be obtained by sampling the analog signal  $\frac{d}{dt}x_{dsp}(t)$ , which is the derivative of the analog equivalent of  $x_{dsp}[n]$ . From this the following is obtained

$$x_{diff}[n] = x'_{dsp}(t)|_{t=nT_s} = x'_{dsp}[n]$$

(2.16)

Since  $x_e[n] = x_{diff}[n]\Delta \mathbf{t}[n]$ , the power in  $x_e[n]$  is

$$\overline{x_e^2[n]} = \overline{x_{dsp}'[n]^2 \Delta \mathbf{t}[n]^2}$$

(2.17)

and since  $\Delta \mathbf{t}[n]$  is independent noise

$$\overline{x_e^2[n]} = \overline{x_{dsp}'[n]^2} \cdot \overline{\Delta \mathbf{t}[n]^2}$$

(2.18)

expressing the powers of  $x'_{dsp}[n]$  and  $\Delta \mathbf{t}[n]$  in terms of their PSD has

$$\overline{x_e^2[n]} = \int_0^{1/2} (2\pi f)^2 S_{xdspxdsp}(e^{j2\pi f}) df \cdot \int_0^{1/2} S_{\Delta t \Delta t}(e^{j2\pi f}) df$$

(2.19)

In the special case where  $S_{xdspxdsp}(e^{j2\pi f}) = \frac{1}{2}\delta(f - f_0),$

$$\overline{x_{jitter\_noise}^2(t)} = \overline{x_e^2[n]} = \frac{1}{2} (2\pi f_0)^2 \int_0^{1/2} S_{\Delta t \Delta t}(e^{j(2\pi f - 2\pi f_0)}) df$$

(2.20)

Which is the same total power obtained before. The term  $x_e[n]$  appears as additive noise on the output of the DAC such that the expression at the output is

$$x_a(t) = x_{dsp}[nT_s] + x_e[nT_s]$$

(2.21)

These results now characterize the noise that is introduced to the transmitted signal by clock jitter noise in the DAC. This clock jitter noise will always be present, and is a source of noise that the echo canceller cannot compensate for.

## 2.2.4 Analog to Digital Conversion

The full duplex node both transmits the downstream signal and receives the upstream signal. An Analog to Digital Converter (ADC) is required to receive the upstream signal and demodulate it back into digital packets. An ADC samples an analog voltage and converts it into a digital word. The more bits used in the digital representation of the sample, the less error in the quantized sample. An ADC will always introduce some quantization noise into the digital sample. The noise introduced by the ADC is assumed to be zero mean, white, and Gaussian, with a variance that characterizes the ADC's Effective Number of Bits (ENOB). The variance of the error, which is its average AC power, is found as follows

$$\sigma^2 = \frac{1}{3} \cdot \frac{1}{2}^{2 \cdot \text{ENOB}} \cdot \left(1 - \frac{1}{4}^{\text{ADC BITS-ENOB}}\right) V^2$$

(2.22)

where:

$\sigma^2$  = Variance of Gaussian Noise and Quantization Noise Added by ADC

ADC BITS = ADC Resolution in Bits

ENOB = ADC Effective Resolution in Bits

The expression in (2.22) is found from the quantization error introduced from converting an infinite precision signal to a finite precision signal. The ENOB is essentially how many of the ADCs rated bits are actually usable information and how many are entirely consumed by the noise. The ENOB is normally given by the manufacturer of the ADC in the device's data sheet.

The dynamic range of an ADC is the range between the noise floor of the device and the maximum level it can output. The dynamic range is essentially the range of voltage levels that the ADC can resolve into digital words. An ADC with a dynamic range of 40dB can resolve voltages from x volts to 100x volts. The range of the ADC is important because in the full duplex DOCSIS network the range of signal strengths can vary greatly. The ADC receiving the upstream signal will likely need a very high dynamic range as the power leaking from the downstream through the hybrid will be very large and the upstream signal from the CMs very small.

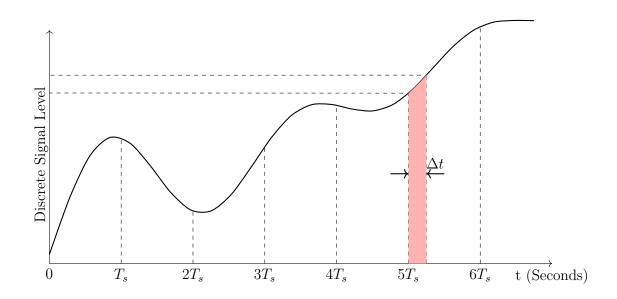

Figure 2.8 ADC Sampling Showing Error From Clock Jitter

#### Error Due to Clock Jitter

A second source of error is due to the error in sampling times. If the quantization noise is ignored the relation between the analog input of a ADC and the digital output is as follows

$$x[n] = x_a(t)|_{t=nT_s + \Delta t[n]}$$

(2.23)

where the  $\Delta \mathbf{t}[n]$  is clock jitter, which was explained in the DAC section of this chapter. This

random clock jitter again causes error in our sampled signal. This error arises from irregular sampling as can be seen in Figure 2.8. If the error in sampling time,  $nT_s$ , is small the output of the ADC can be expressed with a first order Taylor series as follows

$$x[n] = x_a(t) + x'_a(t)\Delta t[n]\Big|_{t=nT_c}$$

(2.24)

The error term in this signal is  $x'_a(t)\Delta t[n]\big|_{t=nT_s}$  which, surprisingly, is the exact same error term found for the DAC output given in Equation 2.21. This means that the error power in this signal is the same as that found in the DAC section in Equation 2.17 and thus further analysis is omitted.

If the same oscillator is used to clock both the ADC and the DAC, and the propagation time between the DAC and ADC is  $<< T_s$ , then only the DAC error affects the signal. If the propagation delay is  $>> T_s$  or different clocks are used for the DAC and ADC the error will add on a power basis. If different oscillators are used for the ADC and the DAC then the error terms will be independent of each other and add on a power basis [10]. The reasoning for this is because the timing jitter for oscillators is due to internal thermal noise and imperfections in the crystals which will be unique to each crystal resulting in independent noise sources.

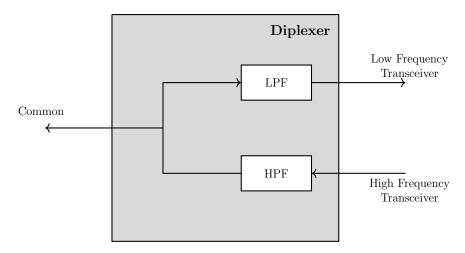

# 2.2.5 Hybrid Couplers

A major difference in the construction of an FDX node from the old HDX node is the replacement of a diplexer with a hybrid coupler. When the spectrum was divided as explained in Chapter 1, it was simple to separate the upstream signal from the downstream signal using low pass and high pass filters. The diplexer shown in Figure 2.9 cannot be used to isolate the upstream signals from the downstream signals when they both occupy the same bandwidth. A hybrid coupler is required to separate the upstream signals from the downstream signals when they occupy the same bandwidth.