# STUDY OF RADIATION TOLERANT STORAGE CELLS FOR DIGITAL SYSTEMS

A Thesis Submitted to the

College of Graduate and Postdoctoral Studies

In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon

By

## ZONGRU LI

© Copyright Zongru Li, June, 2023. All rights reserved.

Unless otherwise noted, copyright of the material in this thesis belongs to the author

#### **Permission to Use**

In presenting this thesis/dissertation in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis/dissertation in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis/dissertation work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis/dissertation or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis/dissertation.

Requests for permission to copy or to make other uses of materials in this thesis/dissertation in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan S7N 5A9 Canada

OR

Dean

College of Graduate and Postdoctoral Studies University of Saskatchewan 116 Thorvaldson Building, 110 Science Place Saskatoon, Saskatchewan S7N 5C9 Canada

#### **Abstract**

Single event upsets (SEUs) are a significant reliability issue in semiconductor devices. Fully Depleted Silicon-on-Insulator (FDSOI) technologies have been shown to exhibit better SEU performance compared to bulk technologies. This is attributed to the thin Silicon (Si) layer on top of a Buried Oxide (BOX) layer, which allows each transistor to function as an insulated Si island, thus reducing the threat of charge-sharing. Moreover, the small volume of the Si in FDSOI devices results in a reduction of the amount of charge induced by an ion strike.

The effects of Total Ionizing Dose (TID) on integrated circuits (ICs) can lead to changes in gate propagation delays, leakage currents, and device functionality. When IC circuits are exposed to ionizing radiation, positive charges accumulate in the gate oxide and field oxide layers, which results in reduced gate control and increased leakage current. TID effects in bulk technologies are usually simpler due to the presence of only one gate oxide layer, but FDSOI technologies have a more complex response to TID effects because of the additional BOX layer.

In this research, we aim to address the challenges of developing cost-effective electronics for space applications by bridging the gap between expensive space-qualified components and high-performance commercial technologies. Key research questions involve exploring various radiation-hardening-by-design (RHBD) techniques and their trade-offs, as well as investigating the feasibility of radiation-hardened microcontrollers.

The effectiveness of RHBD techniques in mitigating soft errors is well-established. In our study, a test chip was designed using the 22-nm FDSOI process, incorporating multiple RHBD Flip-Flop (FF) chains alongside a conventional FF chain. Three distinct types of ring oscillators (ROs) and a 256 kbit SRAM was also fabricated in the test chip. To evaluate the SEU and TID performance of these designs, we conducted multiple irradiation experiments with alpha particles, heavy ions, and gamma-rays. Alpha particle irradiation tests were carried out at the University of Saskatchewan using an Americium-241 alpha source. Heavy ion experiments were performed at the Texas A&M University Cyclotron Institute, utilizing Ne, Ar, Cu, and Ag in a 15 MeV/amu cocktail. Lastly, TID experiments were conducted using a Gammacell 220 Co-60 chamber at the University of Saskatchewan. By evaluating the performance of these designs under various

irradiation conditions, we strive to advance the development of cost-effective, high-performance electronics suitable for space applications, ultimately demonstrating the significance of this project.

When exposed to heavy ions, radiation-hardened FFs demonstrated varying levels of improvement in SEU performance, albeit with added power and timing penalties compared to conventional designs. Stacked-transistor DFF designs showed significant enhancement, while charge-cancelling and interleaving techniques further reduced upsets. Guard-gate (GG) based FF designs provided additional SEU protection, with the DFR-FF and GG-DICE FF designs showing zero upsets under all test conditions. Schmitt-trigger-based DFF designs exhibited improved SEU performance, making them attractive choices for hardening applications. The 22-nm FDSOI process proved more resilient to TID effects than the 28-nm process; however, TID effects remained prominent, with increased leakage current and SRAM block degradation at high doses. These findings offer valuable insights for designers aiming to meet performance and SER specifications for circuits in radiation environments, emphasizing the need for additional attention during the design phase for complex radiation-hardened circuits.

## Acknowledgements

First, I would like to express my deepest gratitude and love to my biggest supporter in life, whose unwavering love, encouragement, and belief in me have been the cornerstone of my success. Your understanding and patience during challenging times have been truly inspiring, and your constant motivation has pushed me to work harder.

My sincerest appreciation goes to Dr. Li Chen, my thesis advisor, for his unwavering support, guidance, and mentorship throughout my academic journey. Your expertise and dedication have shaped this thesis and inspired me to strive for excellence. I am deeply grateful for the time, effort, and passion you have invested in me and my research.

I would also like to thank Chen, Chris, Jaime, Jiesi, Peiman, Dr. Shi, and Zhi Wu for your invaluable contributions to my thesis. Your expertise, knowledge, and insights have been instrumental in shaping my research and ensuring its success. Your support, encouragement, and constructive criticism have motivated me to work harder and aim for excellence.

Lastly, I would like to acknowledge any financial assistance received to carry out this project and express my gratitude for any extraordinary assistance provided during data collection, analysis, or other aspects of this research.

Thank you all for being part of this journey.

# **Table of Contents**

| Permission   | to Usei                            |

|--------------|------------------------------------|

| Abstract     | ii                                 |

| Acknowled    | gementsiv                          |

| Table of Co  | ontentsv                           |

| List of Figu | iresix                             |

| List of Tab  | lesxiii                            |

| List of Abb  | reviationsxiv                      |

| 1 Introd     | uction1                            |

| 1.1 Int      | roduction1                         |

| 1.2 Mo       | otivation                          |

| 1.3 Ob       | jectives4                          |

| 1.4 Th       | esis Overview5                     |

| Refe         | rences                             |

| 2 Backgi     | ound9                              |

| 2.1 Sir      | ngle Event Effects9                |

| 2.1.1        | Single Event Transient             |

| 2.1.2        | Single Event Upset                 |

| 2.1.3        | Single Event Latchup               |

| 2.1.4        | Single Event Functional Interrupts |

| 2.1.5        | Single Event Gate Ruptures         |

| 2.2 To       | tal Dose Effects                   |

| 2.3 Irra     | adiation Sources                   |

| 2.3.1        | Heavy Ion Irradiation Source       |

| 2.    | .3.2    | Alpha Particle Irradiation Source                                   | 15    |

|-------|---------|---------------------------------------------------------------------|-------|

| 2.    | .3.3    | Co-60 Irradiation Source                                            | 16    |

| 2.    | .3.4    | Proton Irradiation Source                                           | 17    |

| 2.    | .3.5    | Laser Irradiation Source                                            | 18    |

| 2.4   | EC      | C and Hamming Code                                                  | 19    |

|       | Refer   | ences                                                               | 21    |

| 3 E   | fficacy | of Transistor Stacking on Flip-Flop SEU Performance at 22-nm Fl     | DSOI  |

| Node. | •••••   |                                                                     | 26    |

| 3.1   | Intr    | oduction                                                            | 28    |

| 3.2   | Sta     | cked-transistor Structure and Latch Designs                         | 31    |

| 3.    | .2.1    | DFF                                                                 | 31    |

| 3.    | .2.2    | Stacked-Transistor DFF                                              | 32    |

| 3.    | .2.3    | Charge-cancelling-stacked DFF                                       | 33    |

| 3.    | .2.4    | Stacked-Transistor DFF with Interleaving.                           | 34    |

| 3.3   | Tes     | t Chip Design                                                       | 34    |

| 3.4   | Exp     | perimental Results                                                  | 36    |

| 3.    | .4.1    | Alpha Particle Experiments                                          | 36    |

| 3.    | .4.2    | Heavy Ion Experiments                                               | 36    |

| 3.5   | Dis     | cussions                                                            | 40    |

| 3.6   | Cor     | nclusions                                                           | 41    |

|       | Refer   | ences                                                               | 43    |

| 4 S   | EU Pe   | rformance of RHBD Flip-Flops Using Guard-Gates at 22-nm FDSOI Techn | ology |

| Node. | •••••   |                                                                     | 46    |

| 4.1   | Intr    | oduction                                                            | 48    |

| 4.2   | GG      | Structure and FF Designs                                            | 50    |

| 4     | 2 1     | Conventional FF                                                     | 52    |

| 4.2                                                         | 2.2                                           | GG FF                                                                                                                                                                                                              | 52                      |

|-------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 4.2                                                         | 2.3                                           | DFR FF                                                                                                                                                                                                             | 53                      |

| 4.2                                                         | 2.4                                           | GG-DICE FF                                                                                                                                                                                                         | 54                      |

| 4.3                                                         | Tes                                           | t Chip Design                                                                                                                                                                                                      | 55                      |

| 4.4                                                         | Exp                                           | perimental Details and Results                                                                                                                                                                                     | 57                      |

| 4.4                                                         | 4.1                                           | Alpha Particle Experiments                                                                                                                                                                                         | 57                      |

| 4.4                                                         | 4.2                                           | Heavy Ion Experiments                                                                                                                                                                                              | 57                      |

| 4.5                                                         | Disc                                          | cussions                                                                                                                                                                                                           | 60                      |

| 4.5                                                         | 5.1                                           | SEU Cross-Section Discussions                                                                                                                                                                                      | 60                      |

| 4.5                                                         | 5.2                                           | Comparing SEU Performance of GG-FF Designs across the Latest Technology                                                                                                                                            | gies 64                 |

| 4.6                                                         | Cor                                           | nclusion                                                                                                                                                                                                           | 65                      |

|                                                             | Refere                                        | ences                                                                                                                                                                                                              | 66                      |

| _                                                           |                                               |                                                                                                                                                                                                                    |                         |

| 5 SE                                                        | EU P                                          | erformance of Schmitt-Trigger-based Flip-Flops at the 22-nm FL                                                                                                                                                     | SOI                     |

|                                                             |                                               | erformance of Schmitt-Trigger-based Flip-Flops at the 22-nm FL Node                                                                                                                                                |                         |

|                                                             | ology                                         |                                                                                                                                                                                                                    | 69                      |

| Techno                                                      | ology<br>INT                                  | Node                                                                                                                                                                                                               | <b> 69</b><br>71        |

| Techno                                                      | ology<br>INT<br>Sch                           | NodeTRODUCTION                                                                                                                                                                                                     | <b>69</b><br>71<br>74   |

| 5.1<br>5.2<br>5.2                                           | ology<br>INT<br>Sch                           | Node  TRODUCTION  mitt-Trigger DFF Designs                                                                                                                                                                         | 69<br>71<br>74<br>74    |

| 5.1<br>5.2<br>5.2                                           | ology<br>INT<br>Sch<br>2.1<br>2.2             | Node  TRODUCTION  mitt-Trigger DFF Designs  DFF Design                                                                                                                                                             | 69 71 74 74             |

| 5.1<br>5.2<br>5.2<br>5.2                                    | INT<br>Sch<br>2.1<br>2.2<br>2.3               | Node                                                                                                                                                                                                               | 69 71 74 74 75          |

| 5.1<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2                      | INT<br>Sch<br>2.1<br>2.2<br>2.3               | Node  TRODUCTION  mitt-Trigger DFF Designs  DFF Design  Schmitt-Trigger Designs  ST1 Schmitt-Trigger-Based DFF                                                                                                     | 69 71 74 75 76          |

| 5.1<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2                      | INT<br>Sch<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Node  TRODUCTION  mitt-Trigger DFF Designs  DFF Design  Schmitt-Trigger Designs  ST1 Schmitt-Trigger-Based DFF  ST2 Schmitt-Trigger-Based DFF                                                                      | 69 71 74 75 76 77       |

| 5.1<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2               | INT Sch 2.1 2.2 2.3 2.4 2.5 Tes               | Node  TRODUCTION  mitt-Trigger DFF Designs  DFF Design  Schmitt-Trigger Designs  ST1 Schmitt-Trigger-Based DFF  ST2 Schmitt-Trigger-Based DFF  Schmitt-Trigger-Based DFF                                           | 69 71 74 75 76 77 78    |

| 5.1<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.2<br>5.3 | INT Sch 2.1 2.2 2.3 2.4 2.5 Tes Exp           | Node  TRODUCTION  mitt-Trigger DFF Designs  DFF Design  Schmitt-Trigger Designs  ST1 Schmitt-Trigger-Based DFF  ST2 Schmitt-Trigger-Based DFF  Schmitt-Trigger-Based DFF  Schmitt-Trigger-Based DFF  t Chip Design | 69 71 74 75 76 77 80 82 |

|   | F   | Refer | rences                                                             | 88          |

|---|-----|-------|--------------------------------------------------------------------|-------------|

| 6 | Co  | mpa   | arison of Total Ionizing Dose Effects in 22-nm and 28-nm FD SOI To | echnologies |

|   | 91  |       |                                                                    |             |

|   | 6.1 | Intr  | roduction                                                          | 93          |

|   | 6.2 | Des   | scription of Test Circuits                                         | 95          |

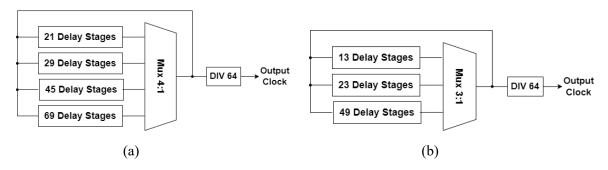

|   | 6.2 | .1    | Ring Oscillators                                                   | 95          |

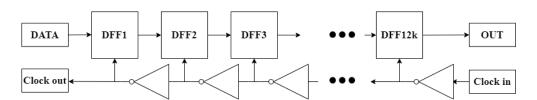

|   | 6.2 | .2    | Flip-Flop Chains                                                   | 97          |

|   | 6.2 | .3    | SRAM Block                                                         | 98          |

|   | 6.3 | Tes   | st Chip Design                                                     | 99          |

|   | 6.4 | TII   | D Experimental Results and Discussions                             | 100         |

|   | 6.5 | Coı   | nclusions                                                          | 106         |

|   | F   | Refer | rences                                                             | 107         |

| 7 | SU  | MM    | ARY, CONTRIBUTIONS AND FUTURE WORK                                 | 110         |

|   | 7.1 | Sur   | mmary                                                              | 110         |

|   | 7.2 | Coı   | ntributions                                                        | 111         |

|   | 7.3 | Cui   | rrent Work                                                         | 112         |

|   | 7.4 | Fut   | ture Work                                                          | 113         |

# **List of Figures**

| Figure 1.1 Cosmic radiation environment in space [4]                                                     |

|----------------------------------------------------------------------------------------------------------|

| Figure 1.2 22-nm FD SOI transistor cross sections for a regular well configuration [8]                   |

| Figure 2.1 D-Latch design.                                                                               |

| Figure 2.2 Heavy-ion facility at TAMU                                                                    |

| Figure 2.3 Alpha particle source on the top of the testing circuit.                                      |

| Figure 2.4 Gammacell 220 Co-60 Irradiator                                                                |

| Figure 2.5 Floorplan of the PIF lab at TRIUMF [43].                                                      |

| Figure 2.6 SPA/TPA Laser System at the University of Saskatchewan                                        |

| Figure 3.1 22-nm FD SOI transistor cross sections for a regular well configuration                       |

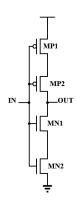

| Figure 3.2 The simplified schematic of the primary-secondary DFF                                         |

| Figure 3.3 Conventional D-Latch design. 31                                                               |

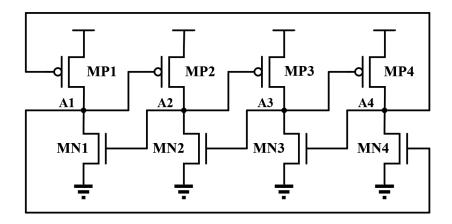

| Figure 3.4 Stacked inverter. 31                                                                          |

| Figure 3.5 D-latch design with stacked inverters                                                         |

| Figure 3.6 Multiple layout designs: (a) Conventional D-latch layout design. (b) Stacked D-latch          |

| layout design. (c) Enhanced charge-cancelling with stacked-transistor D-latch layout design. (d)         |

| Interleaved-stacked D-latch layout design. 33                                                            |

| Figure 3.7 Test chip overall layout. 34                                                                  |

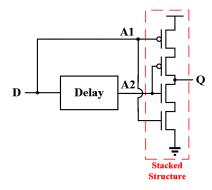

| Figure 3.8 Flip-flop chain and the clock data flow for the shift register design                         |

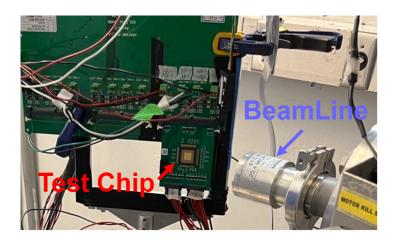

| Figure 3.9 Heavy ion experimental setup at Texas A&M University                                          |

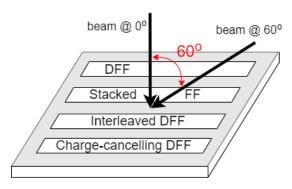

| Figure 3.10 Tilt angle used during testing showing the angle of incidence with respect to power          |

| lines on the IC. Power lines run left-to-right in the IC                                                 |

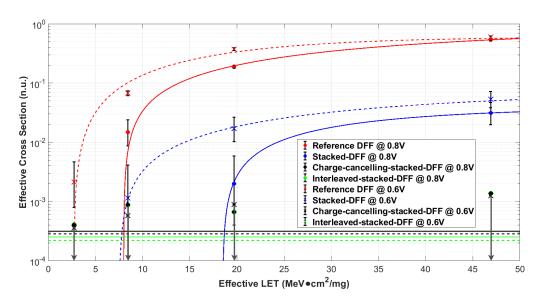

| Figure 3.11 FFs' SEU cross-section as a function of LET and voltage at normal incidence 38               |

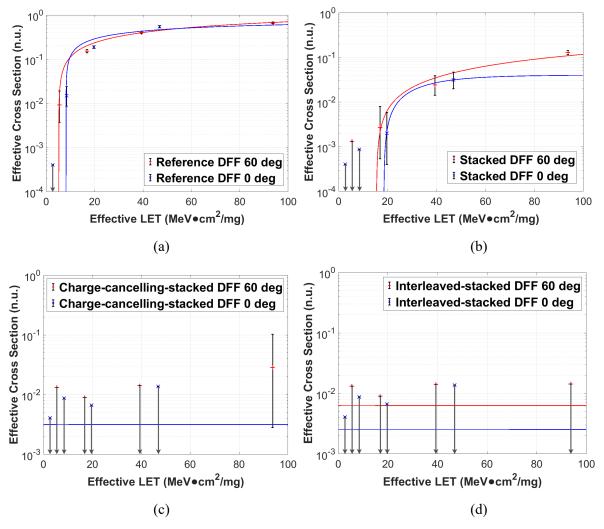

| Figure 3.12 SEU Cross-section at normal and $60^{\circ}$ angle for $0.8~V~VDD$ for (a) conventional DFF, |

| (b) Stacked-transistor DFF, (c) Enhanced-charge-cancelling-stacked DFF, and (d) Interleaved-             |

| stacked DFF                                                                                              |

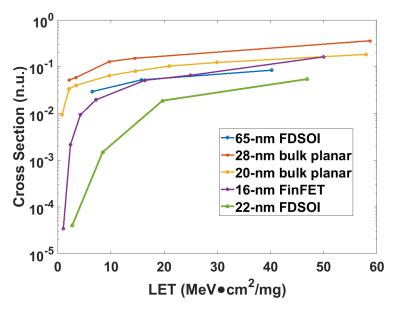

| Figure 3.13 SEU cross section comparison among five different technology nodes (28-nm FDSOI,             |

| 20-nm bulk CMOS, 28-nm bulk CMOS, 16-nm FinFET, 22-nm FDSOI)                                             |

| Figure 4.1 22-nm FDSOI transistor cross sections for a regular well configuration                        |

| Figure 4.2 Stacked inverter.                                                                             |

| Figure 4.3 GG structure with a delay unit                                               | 51          |

|-----------------------------------------------------------------------------------------|-------------|

| Figure 4.4 Conventional FF design.                                                      | 52          |

| Figure 4.5 GG FF design.                                                                | 53          |

| Figure 4.6 DFR FF design.                                                               | 53          |

| Figure 4.7 Conventional DICE latch design.                                              | 54          |

| Figure 4.8 GG based DICE latch design.                                                  | 55          |

| Figure 4.9 Test chip overall layout.                                                    | 55          |

| Figure 4.10 Flip-flop chain and the clock data flow for the shift register design       | 56          |

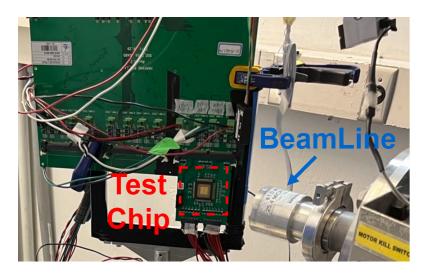

| Figure 4.11 Heavy ion experimental setup at Texas A&M University.                       | 57          |

| Figure 4.12 Tilt angle used during testing showing the angle of incidence with respec   | t to power  |

| lines on the IC. Power lines run left-to-right in the IC.                               | 58          |

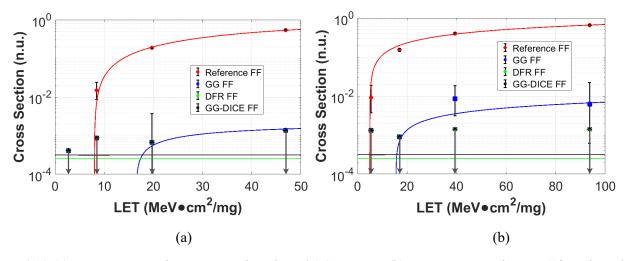

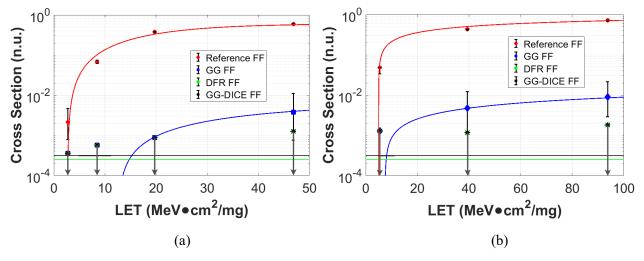

| Figure 4.13 (a) SEU Cross-sections at normal angle and 0.8 V VDD. (b) SEU Cross-        | sections at |

| 60° angle and 0.8 V VDD.                                                                | 59          |

| Figure 4.14 (a) SEU Cross-sections at normal angle and 0.6 V VDD. (b) SEU Cross-        | sections at |

| 60° angle and 0.6 V VDD.                                                                | 60          |

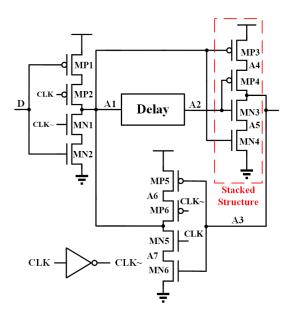

| Figure 4.15 GG latch schematic design.                                                  | 61          |

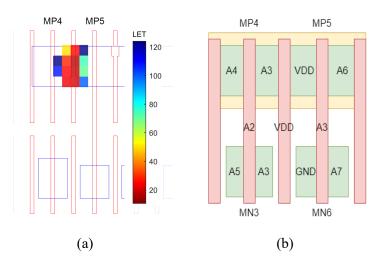

| Figure 4.16 (a) GG design heat map and (b) GG design layout.                            | 62          |

| Figure 4.17 New GG design layout with MP4 and MP5 separated                             | 62          |

| Figure 4.18 Charge collected at the node A3 before and after the modification for a 6   | 4 LET ion   |

| strike                                                                                  | 63          |

| Figure 4.19 SEU cross section comparison of flip flops designed with guard-gate between | ween three  |

| different technology nodes (22-nm FDSOI, 16-nm FinFET and 7-nm FinFET)                  | 64          |

| Figure 5.1 22-nm FD SOI transistor cross-sections for a regular well configuration      | 72          |

| Figure 5.2 The simplified schematic of the primary-secondary DFF                        | 74          |

| Figure 5.3 Conventional D Latch design.                                                 | 74          |

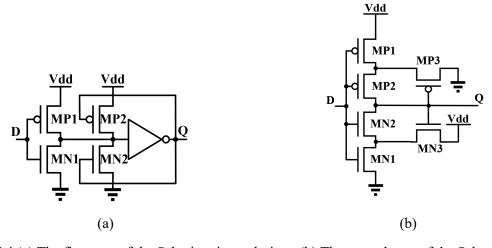

| Figure 5.4 (a) The first type of the Schmitt-trigger design. (b) The second type of th  | e Schmitt-  |

| trigger design.                                                                         | 75          |

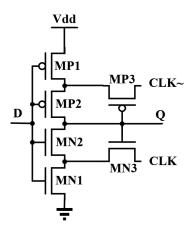

| Figure 5.5 A variation of the second Schmitt-trigger.                                   | 76          |

| Figure 5.6 ST1 DFF schematic based on the first type of the Schmitt-trigger design v    | where only  |

| one inverter is replaced by a Schmitt-trigger.                                          | 77          |

| Figure 5.7 ST2 DFF schematic based on the variation of the second type of the Schmitt-trigger              |

|------------------------------------------------------------------------------------------------------------|

| design                                                                                                     |

| Figure 5.8 Guard-gate-based latch design where an inverter is replaced by a guard-gate along with          |

| the delay circuit                                                                                          |

| Figure 5.9 DFR-FF design. 79                                                                               |

| Figure 5.10 ST-DFR DFF schematic based on the variation of the second type of the Schmitt-                 |

| trigger design and the DFR structure                                                                       |

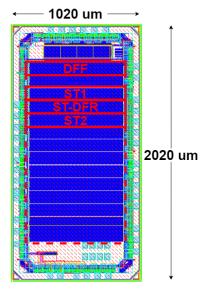

| Figure 5.11 Test chip overall layout (includes some other testing circuits)                                |

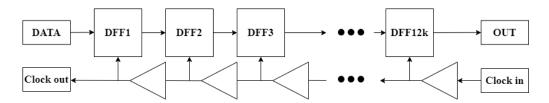

| Figure 5.12 Flip-flop chain and the clock data flow for the shift register design                          |

| Figure 5.13 Heavy ion experimental setup at Texas A&M University                                           |

| Figure 5.14 Tilt angle used during testing showing the angle of incidence with respect to power            |

| lines on the IC. Power lines run left-to-right in the IC                                                   |

| Figure 5.15 (a) SEU Cross-section at normal angle and 0.8 V $V_{\text{DD}}$ for the conventional DFF, ST1, |

| ST2 and ST-DFR. (b) SEU Cross-section at 60° angle and 0.8 V VDD for the conventional DFF,                 |

| ST1, ST2 and ST-DFR84                                                                                      |

| Figure 5.16 (a) SEU Cross-section at normal angle and 0.6 V $V_{\text{DD}}$ for the conventional DFF, ST2  |

| and ST-DFR. (b) SEU Cross-section at 60° angle and 0.6 V VDD for the conventional DFF, ST2                 |

| and ST-DFR85                                                                                               |

| Figure 5.17 SEU cross-section comparison between two different technology nodes (22-nm                     |

| FDSOI and 16-nm FinFET)                                                                                    |

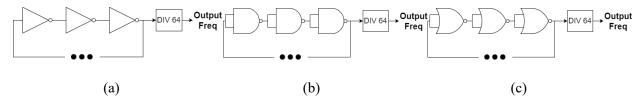

| Figure 6.1 Three different RO designs: (a) Inverter-based RO design; (b) NAND2-based RO                    |

| design; (c) NOR2-based RO design96                                                                         |

| Figure 6.2 Schematic designs of different gate-based ROs: (a) Inverter-based RO schematic design           |

| (b) NAND2 or NOR2-gate-based RO schematic design                                                           |

| Figure 6.3 Flip-flop chain and the clock data flow for the shift register design                           |

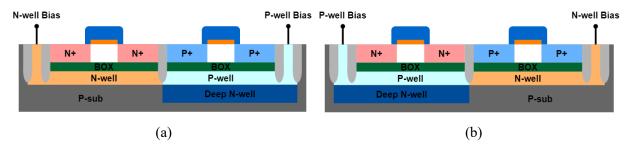

| Figure 6.4 (a) Flipped well configuration (FBB); (b) regular well configuration (RBB)                      |

| Figure 6.5 Test chip overall layout. 99                                                                    |

| Figure 6.6 Gammacell 220 Co-60 Irradiator                                                                  |

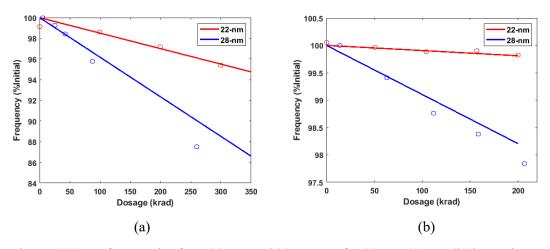

| Figure 6.7 RO frequencies vs. total absorbed dose during Co-60 test: (a) Inverter-based ROs; (b)           |

| NAND2-based ROs; (c) NOR2-based ROs. 101                                                                   |

| Figure 6.8 RO frequencies vs. total absorbed dose during heavy ion test                                    |

| Figure 6.9 Schematic of the 28-nm RO design.                                                 | 103 |

|----------------------------------------------------------------------------------------------|-----|

| Figure 6.10 RO frequencies from 22-nm and 28-nm test for (a) Co-60 test; (b) heavy ion test. | 104 |

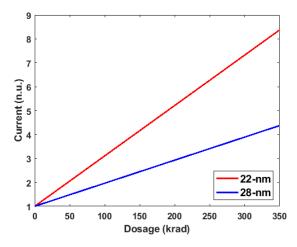

| Figure 6.11 Current from 22-nm and 28-nm tests during Co-60 test.                            | 105 |

# **List of Tables**

| Table 3.1 Electrical Performance Characteristics for the FF Chains                         | 35      |

|--------------------------------------------------------------------------------------------|---------|

| Table 3.2 Ions Used in Heavy Ion Experiments                                               | 37      |

| Table 4.1 Electrical Performance Characteristics for the FF Chains                         | 56      |

| Table 4.2 Ions Used in Heavy Ion Experiments                                               | 58      |

| Table 5.1 Electrical Performance Characteristics for the FF Chains                         | 81      |

| Table 5.2 Ions Used in Heavy Ion Experiments                                               | 83      |

| Table 6.1 Inverter-based programmable RO simulation results.                               | 96      |

| Table 6.2 NAND-based programmable RO simulation results.                                   | 96      |

| Table 6.3 NOR-based programmable RO simulation results.                                    | 97      |

| Table 6.4 RO frequency differences from 0 krad(Si) of exposure to 300 krad(Si) during Co-6 | o test. |

|                                                                                            | 101     |

## **List of Abbreviations**

ADC Analog-to-Digital Converters

ASIC Microprocessors and Application-Specific Integrated Circuit

BOX Buried Oxide

CHB Checkerboard

CMOS Complementary Metal-Oxide-Semiconductor

CNRX Continuous Active Diffusion

CO-59 Cobalt-59

CO-60 Cobalt-60

CRC Cyclic Redundancy Check

DAC Digital-to-Analog Converter

DFR Dual-Feedback-Recovery

DICE Dual Interlocked Storage Cell

DSET Digital Single Event Transient

DUT Device Under Test

ECC Error Correction Code

FBB Forward Body Bias

FDSOI Fully Depleted Silicon-on-Insulator

FF Flip-Flop

GG Guard Gate

HI Heavy Ion

IC Integrated Circuit

IGBT Insulated Gate Bipolar Transistors

LEAP Layout Error-Aware Transistor Positioning

LET Linear Energy Transfer

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistors

NI-60 Nickel-60

NSREC Nuclear Science and Space Radiation Effects Conference

PDK Process Design Kit

PLL Phase-Locked Loop

PIF Proton Irradiation Facility

RBB Reverse Body Bias

RHBD Radiation Hardened by Design

RO Ring Oscillator

SE Soft Error

SEB Single Event Burnout

SEE Single Event Effect

SEFI Single Event Functional Interrupt

SEGR Single Event Gate Rupture

SEL Single Event Latchup

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SI Silicon

SIA Semiconductor Industry Association

SOI Silicon on Insulator

SRAM Static Random-Access Memory

ST Schmitt Trigger

STI Shallow Trench Isolation

TAMU Texas A & M University

TCAD Technology Computer Aided Design

TID Total Ionizing Dose

VLSI Very Large-Scale Integration

#### 1 Introduction

## 1.1 Introduction

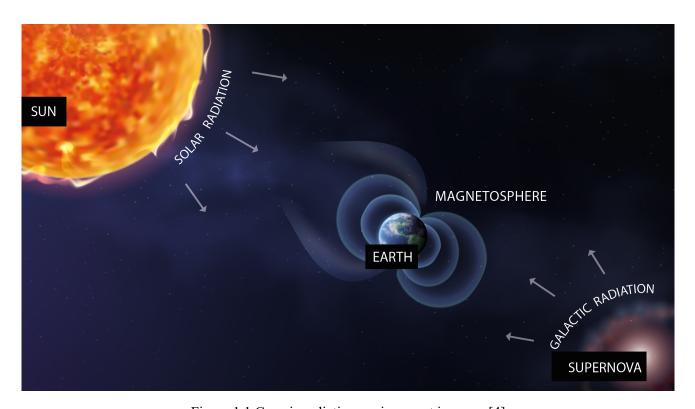

In recent years, advanced semiconductor technologies have gained increasing importance in space systems and high-performance computing, with the aim of enhancing performance, reducing power consumption, and minimizing system size and weight. However, the harsh radiation environment in space, as well as on Earth, poses significant challenges to the reliable operation of electronic systems. Single-event upsets (SEUs) and total ionizing dose (TID) effects are two critical factors that can lead to malfunctions or even permanent damage to electronic systems in these settings [1-3]. Consequently, radiation-hardening-by-design (RHBD) techniques

Figure 1.1 Cosmic radiation environment in space [4].

are essential for developing robust designs that can withstand ionizing radiation and maintain reliable performance in extreme environments.

SEUs, caused by radiation particles interacting with nanoscale technologies, are a major reliability issue for modern micro-electronic systems [5]. These events can affect various storage components, such as memory cell arrays, flip-flops (FFs), and Static Random-Access Memories (SRAMs), leading to bit flips and functionality issues. To address this, designers often implement RHBD techniques through layout, schematic, or system-level architectural manipulations, improving SEU resilience for components like FFs [6-8]. Additionally, error correction and detection methods are employed to further safeguard systems against radiation-induced errors.

On the other hand, TID effects in integrated circuits (ICs) can result in changes to gate propagation delays, leakage currents, and even loss of device functionality [9,10]. These effects are particularly concerning in long-term space missions, where devices can be exposed to constant sources of radiation for years. ICs in bulk technologies and Fully Depleted Silicon-on-Insulator (FDSOI) technologies exhibit different responses to TID effects, necessitating tailored radiation-hardening approaches [10,11]. Designers must carefully choose the appropriate technology and design techniques to achieve optimal radiation tolerance while balancing other factors like power consumption, performance, and cost.

As technology continues to scale down and supply voltage decreases, ensuring the reliability of electronic systems in radiation-rich environments becomes increasingly crucial. By employing RHBD techniques and understanding the impact of SEUs and TID effects on various semiconductor technologies, designers can develop more resilient systems for aerospace and high-performance computing applications. This requires continuous research and development in radiation-hardening techniques, material sciences, and device modeling to stay ahead of the ever-evolving challenges posed by radiation effects on semiconductor technologies. In turn, this will enable more advanced and reliable systems capable of withstanding the harsh conditions found in space, nuclear facilities, and other radiation-prone environments, ultimately contributing to the success and safety of missions and operations in these demanding contexts.

#### 1.2 Motivation

As previously noted, the sensitivity of integrated circuits (ICs) to individual ions, such as alpha particles from packaging material, increases significantly as their feature size decreases. FDSOI technology nodes exhibit promising radiation-hardness characteristics compared to bulk technology nodes. However, as feature sizes reach the nanometer scale, single event upsets (SEUs) remain a concern, necessitating the development of innovative hardening techniques to ensure reliable electronic device performance in space. Additionally, understanding the comparative total ionizing dose (TID) resilience between different nodes is essential when choosing the most suitable technology for various space applications.

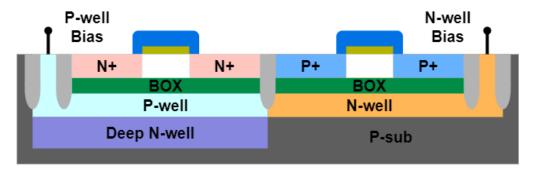

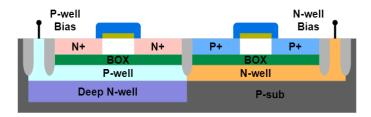

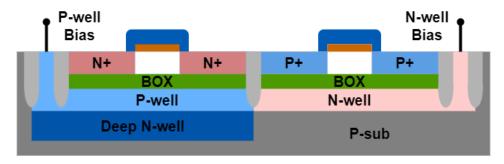

FDSOI technologies are attractive due to features such as high speed and low power consumption, making them good candidates for space applications. Unlike bulk technologies, FDSOI technologies utilize a thin Silicon (Si) layer on top of a Buried Oxide (BOX), providing superior gate control in the channel region and reduced nodal capacitances, as illustrated in Figure 1.2 [8,12,13]. The thin Si layer also limits charge collection after ion strikes due to the reduced active-Si volume [14]. FDSOI technologies largely avoid the charge-sharing issues experienced by bulk technologies, which occur when multiple transistors that are in close proximity to an impacted transistor collect simultaneous charges.

Figure 1.2 22-nm FD SOI transistor cross sections for a regular well configuration [8].

In addressing residual single event challenges, researchers often focus on circuit-level approaches that do not necessitate modifications at the process or technology level [6,7]. These methods involve alterations to the schematics or layouts of the target design. Due to the infeasibility of changing fabrication processes to enhance single-event (SE) performance, designers typically opt for RHBD techniques [6]. Some of the challenges in this research area

include the introduction of cost-effective mitigation solutions and the management of trade-offs between SEU performance, power, area, and other factors. Implementing SEU mitigation techniques often involves modifying layout, schematic, or system-level architectures, and striking the right balance among these parameters can be difficult [6,7]. By addressing these challenges, this study aims to contribute valuable insights to the development of radiation-hardened electronics for various applications.

In FDSOI technologies, TID effects are more complex compared to bulk devices due to the presence of an additional parasitic structure introduced by the Buried Oxide (BOX) layer [8,15 - 19]. This layer leads to a two-dimensional coupling effect between the front and back interfaces of the channel, significantly impacting the ionizing dose response of FDSOI devices. As a result, FDSOI technologies exhibit greater sensitivity to TID than bulk counterparts [10,20,21]. Despite their inherent resistance to particle-induced single event effects (SEEs) making FDSOI technologies appealing for space missions [6,10,11], previous research on the 28-nm FDSOI technology node [3,6] demonstrated substantial increases in TID-induced gate delay and leakage currents. These challenges present difficulties for space applications requiring high total absorbed dose tolerance, making it essential to investigate TID effects in the 22-nm FDSOI technology node as well.

## 1.3 Objectives

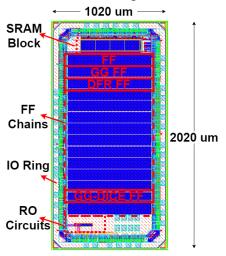

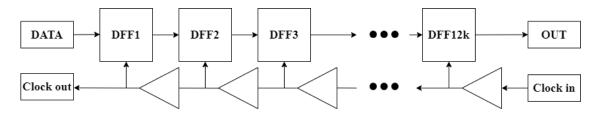

The overall goal of this thesis is to study the SEU and TID performance at the 22-nm FDSOI technology node, and develop cost-effective electronics for various space applications. To achieve this, a test chip was designed and fabricated using the 22-nm FDSOI process, incorporating multiple RHBD FF chains alongside a conventional FF chain, three distinct types of ROs, and a 256 kbit SRAM. Multiple irradiation experiments were conducted to assess the SEU and TID performance of these designs. The thesis is structured around three specific objectives:

Investigate the SEU performance of different RHBD FFs based on three fundamental hardening techniques: transistor-stacking, guard-gating, and Schmitt-triggers. This objective involves the development, testing, and analysis of various FF designs making use of these techniques, such as stacked FF, charge-canceling stacked FF, interleaved-stacked FF, GG FF, DFR

FF, GG-DICE FF, ST1 FF, ST2 FF, and ST-DFR FF. All design were fabricated using the same 22-nm FDSOI process. The designs were subjected to alpha particle and heavy ion irradiation for SEU characterization, and their SEU performance is thoroughly evaluated.

Compare the total ionizing dose effects in 22-nm and 28-nm FDSOI technologies using SRAM and ring oscillator designs. This objective aims to assess the TID performance of the 22-nm FDSOI technology by utilizing SRAM and various RO designs, such as inverter ROs, NAND ROs, and NOR ROs. The results are compared to those of the 28-nm FDSOI node to identify differences in radiation tolerance between the two technology nodes. The findings will highlight the necessity for careful consideration when designing complex circuits for radiation-hardened applications.

#### 1.4 Thesis Overview

This thesis comprises the author's manuscripts published or currently under review during their master's studies. It focuses on the examination of single event effects on digital systems through simulation and experimental results. Each chapter begins with a concise summary, highlighting the connection between the current chapter and the preceding one, followed by a brief conclusion. The organization and primary content of this thesis are summarized below.

Chapter 1 offers a brief introduction to radiation effects and fundamental background information, as well as the motivation and objectives of this research.

Chapter 2 delves into more detailed background information, covering the radiation effects investigated in this research, radiation particles, experimental facilities, and radiation-hardening techniques used in the project.

Chapter 3 examines the design and experimental results of stacked-transistor-based hardened flip-flop designs in comparison to conventional designs at the 22-nm FDSOI node. It presents three stacked-transistor-based DFF designs and evaluates their SEU performance after exposure to alpha particle and heavy ion irradiation.

Chapter 4 explores multiple RHBD flip-flop designs using guard-gate circuits at the 22-nm FDSOI node and presents their irradiation results. The chapter evaluates the SEU performance

of several guard-gate (GG) structure-based FF designs after exposure to alpha particle and heavy ion irradiation and assesses the impact of the CnRx construct in the GG design.

Chapter 5 evaluates the single-event performance of Schmitt-trigger-based flip-flop designs compared to the conventional DFF design at the 22-nm FDSOI node. The study presents three Schmitt-trigger-based FF designs and assesses their SEU performance after exposure to alpha particle and heavy ion irradiation.

Chapter 6 presents a comparative study of total ionizing dose effects between the 22-nm and 28-nm FDSOI technology nodes, focusing on ring oscillators and memory elements. The study uses ring oscillators (ROs) and a 256 kbit SRAM block to assess the TID sensitivity of these devices, followed by Co-60 radiation tests to evaluate their TID performance.

Finally, Chapter 7 provides conclusions and recommendations for future work.

## References

- [1] P. E. Dodd and L. W. Massengill, "Basic mechanisms and modeling of single-event upset in digital microelectronics," IEEE Transactions on Nuclear Science, vol. 50, no. 3, pp. 583-602, Jun. 2003.

- [2] R. C. Baumann, "Radiation-induced soft errors in advanced semiconductor technologies," IEEE Transactions on Device and Materials Reliability, vol. 5, no. 3, pp. 305-316, Sep. 2005.

- [3] D. Seo, L. D. Trang, J.-W. Han, J. Kim, S. Lee, and I.-J. Chang, "Total ionizing dose effect on ring oscillator frequency in 28-nm FD-SOI technology," IEEE Electron Device Letters, vol. 39, no. 11, pp. 1728-1731, Nov. 2018.

- [4] L. Gil, "Cosmic Radiation: Why We Should not be Worried," International Atomic Energy Agency, 2021. [Online]. Available: <a href="https://www.iaea.org/newscenter/news/cosmic-radiation-why-we-should-not-be-worried">https://www.iaea.org/newscenter/news/cosmic-radiation-why-we-should-not-be-worried</a>.

- [5] E. Normand, "Single event upset at ground level," IEEE Transactions on Nuclear Science, vol. 43, no. 6, pp. 2742-2750, Dec. 1996.

- [6] R. Liu et al., "Single event transient and TID study in 28 nm UTBB FDSOI technology," IEEE Transactions on Nuclear Science, vol. 64, no. 1, pp. 113-118, Jan. 2017.

- [7] M. Nicolaidis, "Design for soft error mitigation," IEEE Transactions on Device and Materials Reliability, vol. 5, no. 3, pp. 405-418, Sep. 2005.

- [8] Z. Li et al., "Efficacy of Transistor Stacking on Flip-Flop SEU Performance at 22-nm FDSOI Node," IEEE Transactions on Nuclear Science, vol. 70, no. 4, pp. 596-602, Apr. 2023.

- [9] H. Zhang et al., "Effects of total-ionizing-dose irradiation on single-event response for flip-flop designs at a 14-/16-nm bulk FinFET technology node," IEEE Transactions on Nuclear Science, vol. 65, no. 8, pp. 1928-1934, Aug. 2018.

- [10] Z. Li et al., "Comparison of total ionizing dose effects in 22-nm and 28-nm FD SOI technologies," Electronics, vol. 11, no. 11, pp. 1757-1767, Jun. 2022.

- [11] Q. Zheng et al., "Total ionizing dose responses of forward body bias ultra-thin body and buried oxide FD-SOI transistors," IEEE Transactions on Nuclear Science, vol. 66, no. 4, pp. 702-709, Apr. 2019.

- [12] C. Cai et al., "Large-tilt heavy ions induced SEU in multiple radiation hardened 22 nm FDSOI SRAMs," in Proceedings of the IEEE International Reliability Physics Symposium, Grapevine, TX, USA, Apr. 2020, pp. 641-645.

- [13] C. J. Elash et al., "Efficacy of transistor interleaving in DICE flip-flops at a 22 nm FD SOI technology node," Applied Science, vol. 12, no. 9, pp. 4229-4238, Apr. 2022.

- [14] E. H. Cannon et al., "Apparatus and method for hardening latches in SOI CMOS devices," U.S. Patent 7,888,959, issued Feb. 15, 2011.

- [15] M. P. King et al., "Analysis of TID process geometry and bias condition dependence in 14-nm FinFETs and implications for RF and SRAM performance," IEEE Transactions on Nuclear Science, vol. 64, no. 1, pp. 285-292, Jan. 2017.

- [16] M. Gaillardin et al., "Total ionizing dose response of multiple-gate nanowire field effect transistors," IEEE Transactions on Nuclear Science, vol. 64, no. 8, pp. 2061-2068, Aug. 2017.

- [17] J. Riffaud et al., "Investigations on the geometry effects and bias configuration on the TID response of nMOS SOI tri-gate nanowire field-effect transistors," IEEE Transactions on Nuclear Science, vol. 65, no. 1, pp. 39-45, Jan. 2018.

- [18] H. Hughes et al., "Total ionizing dose radiation effects on 14 nm FinFET and SOI UTBB technologies," in Proceedings of the IEEE Radiation Effects Data Workshop, Boston, MA, USA, Jul. 2015, pp. 97-102.

- [19] P. Paillet et al., "Total ionizing dose effects on deca-nanometer fully depleted SOI devices," IEEE Transactions on Nuclear Science, vol. 52, no. 6, pp. 2345-2352, Dec. 2005.

- [20] M. Gaillardin et al., "Impact of SOI substrate on the radiation response of ultrathin transistors down to the 20 nm node," IEEE Transactions on Nuclear Science, vol. 60, no. 4, pp. 2583-2589, Aug. 2013.

- [21] A. Javanainen et al., "Heavy-ion induced charge yield in MOSFETs," IEEE Transactions on Nuclear Science, vol. 56, no. 6, pp. 3367-3371, Dec. 2009.

## 2 Background

In this chapter, a comprehensive overview of the key single event effects (SEEs) relevant to electronic systems is provided. The discussion encompasses single event transients (SETs), single event upsets (SEUs), single event latch-ups (SELs), single event functional interrupts (SEFIs), and single event gate ruptures (SEGRs). Additionally, the concept of total ionizing dose (TID) is introduced, along with its implications for device performance and reliability.

Various irradiation sources utilized in this research are examined, including heavy ions, alpha particles, Co-60 gamma rays, protons, and lasers, as well as their impact on electronic components. Furthermore, error correction techniques are presented, such as error correction codes (ECC) and the principles of Hamming codes, which serve to safeguard SRAM blocks in radiation environments.

## 2.1 Single Event Effects

SEEs are radiation-induced phenomena that can lead to functional disruptions, performance degradation, or permanent damage in electronic devices and systems operating in high-energy particle environments, such as those encountered in space or high-altitude aviation applications [1]. These effects originate from the interaction of high-energy particles, including cosmic rays, protons, or heavy ions, with sensitive areas of integrated circuits (ICs) and semiconductor devices, resulting in transient or permanent errors in device operation [2][3].

SEEs encompass a broad spectrum of effects, such as SEUs, SELs, SEGRs, single event burnouts (SEBs), SEFIs, and SETs [4][5]. Each effect poses unique challenges and can significantly impact the reliability and performance of electronic systems in radiation-rich environments.

Numerous mitigation techniques have been developed over the years to address the various types of SEEs. These approaches include radiation-hardened technologies, circuit-level design techniques like redundancy, ECC, and radiation-hardening-by-design (RHBD), as well as system-level strategies such as fault-tolerant computing and radiation-aware software design [6]. Despite these efforts, SEEs continue to pose a significant challenge for modern electronic systems, especially as device scaling persists and technology nodes become smaller, heightening the sensitivity of devices to radiation-induced errors.

## 2.1.1 Single Event Transient

A SET is a single event effect in combinational-logic circuits of digital systems, contrasting with SEUs in sequential cells. SET soft error rates are influenced by factors like clock speed, with higher frequencies increasing the likelihood of capturing SETs and potentially limiting system speed [7].

SETs occur when ions strike a buffer or other combinational cell in a digital circuit, generating a transient pulse that may impact the entire system if captured by a flip-flop. An SET in the system clock tree can cause system failure by producing an extra clock edge and disrupting sequential logic.

Energetic particles, like heavy ions, create SETs by interacting with reverse-biased PN junctions in combinational logic transistors. They generate transient pulses through direct and secondary ionization processes. SETs can be categorized as Analog (ASET) or Digital (DSET) based on their presence in analog or digital circuits.

The focus here is on DSETs, which have become a growing concern due to technology scaling. DSETs can significantly affect the soft error rate (SER) in sub-100nm technologies, with even relatively low-energy alpha particles potentially increasing the SER [8,9]. Therefore, examining DSETs and their impact is vital for developing reliable digital technologies.

## 2.1.2 Single Event Upset

A Single Event Upset is a non-destructive, transient error that occurs in electronic systems due to the interaction of ionizing radiation with the sensitive regions of semiconductor devices [10]. SEUs can lead to the alteration of stored data or change in the logic state of the electronic device, potentially causing a malfunction or system failure [11]. With the increasing demand for high-performance electronics in various fields such as aerospace, defense, medical, and telecommunications, the impact of SEUs on the reliability and overall performance of electronic systems has become a critical concern [12].

The most common manifestation of an SEU is a bit flip, where a binary value (0 or 1) stored in a memory cell, or a flip-flop is changed to the opposite value. This can lead to data corruption, incorrect calculations, or system malfunctions. The susceptibility of electronic systems to SEUs depends on several factors, including device technology, circuit design, operating environment, and shielding techniques [13]. As technology nodes continue to shrink, the sensitivity of semiconductor devices to SEUs has increased due to the reduced charge collection volume, lower operating voltages, and higher integration densities [10]. Moreover, the use of advanced electronic systems in harsh radiation environments, such as space and high-altitude applications, further increases the likelihood of SEUs [14].

SEUs can significantly affect the reliability and performance of electronic systems, causing system crashes, data corruption, or unexpected behavior [15]. In safety-critical systems, such as avionics and nuclear power plant control systems, SEUs can pose severe risks to human life and the environment. Therefore, understanding the mechanisms of SEUs and their impact on electronic systems is essential for designing robust and reliable systems [16].

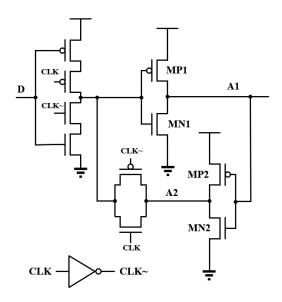

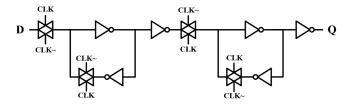

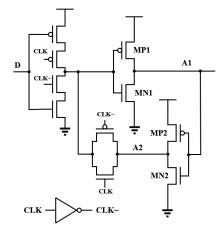

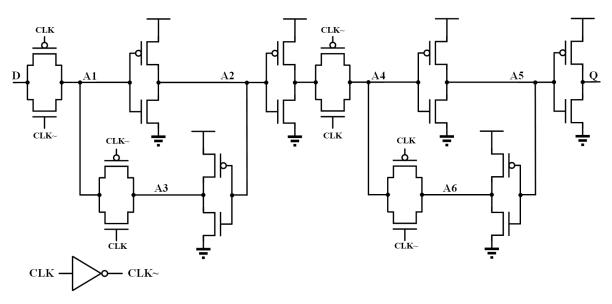

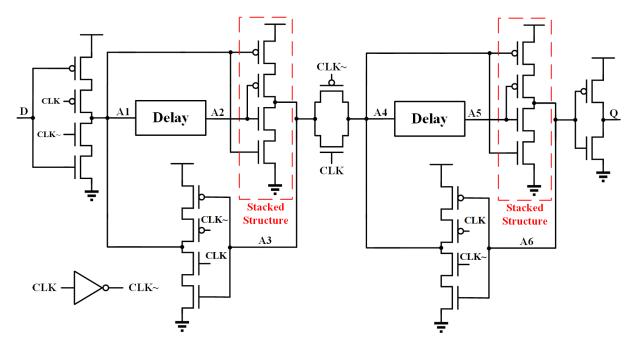

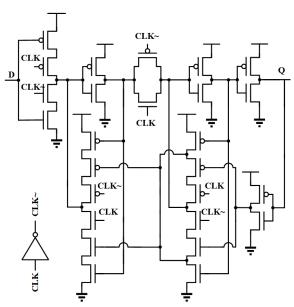

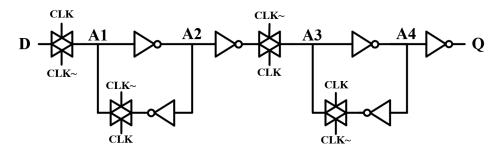

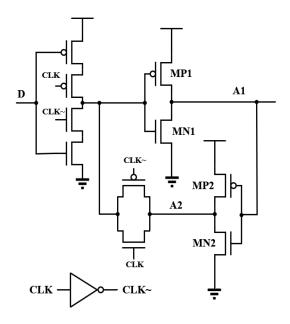

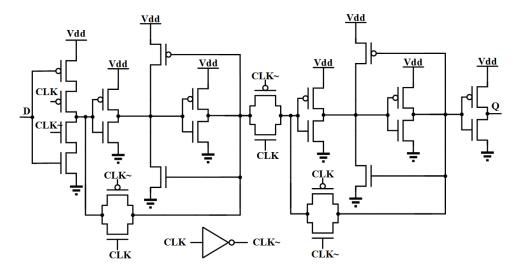

SEUs occur is all types of storage cells, including latch, SRAM cells, DRAM cells, and dynamic logic circuits. Figure 2.1 shows the schematic of a D latch, including two pass gates and a pair of inverters with a positive feedback loop.

Consider Image 2.1. When both CLK and input D are high, the latch enters the hold state. In this situation, the MN1 and the MP2 are turned off, making them sensitive to radiation strikes. If a particle impacts the drain of MN1, the resulting current may be significant enough to surpass

Figure 2.1 D-Latch design.

the restoring current provided by the MP1. This voltage perturbation at the affected node can then propagate to inverter in the feedback loop, potentially causing an unintended state change in the D latch, which is known as the SEU.

## 2.1.3 Single Event Latchup

A SEL is a radiation-induced phenomenon that can have severe consequences for ICs exposed to high-energy particle environments, such as those encountered in space or high-altitude aviation applications. The latch-up effect occurs when high-energy particles, like galactic cosmic rays or heavy ions, strike the sensitive regions of the IC, creating a parasitic thyristor structure that can induce a high current state and potentially result in permanent device damage or failure [17,18].

The SEL was first observed in the early 1970s, coinciding with the increasing integration of bipolar and complementary metal-oxide-semiconductor (CMOS) technologies in microelectronics [19]. Since then, it has emerged as a critical reliability concern for designers of electronic systems operating in radiation-rich environments.

Over the years, a variety of mitigation techniques have been developed to prevent or reduce the risk of SEL in ICs. These methods encompass radiation-hardened technologies and process modifications, as well as circuit-level design techniques and system-level approaches [20,21]. Despite these advancements, SELs remain a significant challenge for modern ICs, particularly as device scaling persists and technology nodes continue to shrink.

## 2.1.4 Single Event Functional Interrupts

SEFIs are radiation-induced events that can cause temporary functional disruptions or malfunctions in ICs operating in high-energy particle environments, such as those found in space or high-altitude aviation applications. SEFIs occur when high-energy particles, like galactic cosmic rays or heavy ions, interact with sensitive regions of the IC, resulting in erroneous outputs, state changes, or unintended operations without causing permanent damage [1,2].

SEFIs have been a topic of concern since the early days of space electronics, as they can significantly impact system reliability and mission success. They are particularly critical for complex digital systems, such as microprocessors and application-specific ICs (ASICs), where even a transient disturbance can have a cascading effect on overall system functionality [22].

Various mitigation techniques have been developed over the years to prevent or reduce the risk of SEFIs in ICs. These methods include radiation-hardened technologies, circuit-level design techniques, such as redundant architectures or ECC, and system-level approaches, like fault-tolerant computing and watchdog timers [5,6]. Despite these efforts, SEFIs remain a significant challenge for modern ICs, especially as device scaling continues and technology nodes shrink.

## 2.1.5 Single Event Gate Ruptures

SEGRs are radiation-induced events that can cause permanent damage or failure in power metal-oxide-semiconductor field-effect transistors (MOSFETs) and insulated gate bipolar transistors (IGBTs) when exposed to high-energy particle environments, such as those encountered in space or high-altitude aviation applications. SEGRs transpire when high-energy particles, like cosmic rays or heavy ions, impact the gate oxide region of the transistor, resulting in a localized increase in the electric field, which can subsequently lead to gate oxide breakdown and device failure [23,24].

SEGRs were initially reported in the 1980s when researchers observed unanticipated failures in power MOSFETs and IGBTs operating in radiation-rich environments [25,26]. Since then, SEGRs have emerged as a critical reliability concern for designers of electronic systems that function in such conditions, particularly for high-voltage and high-power applications.

A variety of mitigation techniques have been developed to prevent or reduce the risk of SEGRs in power devices. These methods encompass radiation-hardened technologies, process modifications to enhance gate oxide robustness, and design techniques such as increasing the gate oxide thickness or incorporating gate field plates [26,27]. Despite these advancements, SEGRs continue to pose a significant challenge for modern power devices, especially as the demand for high-voltage and high-power systems persists.

#### 2.2 Total Dose Effects

The TID effect refers to the degradation of devices caused by prolonged exposure to highenergy particles in radiation environments [28-35]. This degradation occurs when energetic particles generate charged electron-hole pairs in the SiO2 layer, which can become trapped at the Si-SiO2 interface and form an electric field. Over time, this leads to the deterioration of the device's electrical characteristics, increased gate delay, and higher transistor leakage current. In extreme cases, it can cause circuit malfunctions as well.

Modern technologies have reduced gate oxide layers to nanometer scales, effectively mitigating TID effects [36]. However, TID analysis in Silicon-On-Insulator (SOI) technologies is more complex due to the additional Buried Oxide isolation layer between the substrate and body, alongside the gate oxide and Shallow Trench Isolation (STI) [37].

#### 2.3 Irradiation Sources

## 2.3.1 Heavy Ion Irradiation Source

Heavy ion accelerators generate high-energy ion beams with energies up to GeV levels and linear energy transfer (LET) values spanning the full LET range found in space, from less than 1

MeV-cm<sup>2</sup>/mg to around 100 MeV-cm<sup>2</sup>/mg [38]. These accelerators enable efficient evaluation of ICs' SEE performance and data collection for in-orbit error rate calculations. The detection of the first space-related soft error caused by heavy ions led to research on their effects and radiation-tolerant designs for space-based ICs [39].

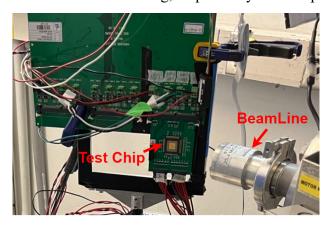

Ground-based accelerators allow researchers to effectively simulate naturally occurring heavy ions, providing a cost-effective and controllable method for replicating the space environment. This technique enables repeated radiation-effect experiments and in-depth studies of radiation-hardened designs. In this study, heavy-ion experiments were carried out at TAMU. Figure 2.2 shows the heavy-ion control room and facility at TAMU.

Figure 2.2 Heavy-ion facility at TAMU.

## 2.3.2 Alpha Particle Irradiation Source

Alpha particles, which are high-velocity helium nuclei with two protons and two neutrons, have a rest mass of 6.64 x 10-27 kg and an electric charge of 3.20 x 10-19 coulomb. Intel reported the first SEE on Earth caused by an alpha particle from radioactive-contaminated packaging material in ICs [40].

Alpha particles, primarily emitted through the decay of materials like Americium 241, have a dominant energy peak at 5.486 MeV, representing 85.2% of the particles. These particles can penetrate the 10-20  $\mu$ m dead layer of ICs and access the sensitive layer due to their 27.9  $\mu$ m range in silicon. The LET of a 5.486 MeV alpha particle is 0.5 MeV-cm<sup>2</sup>/mg [41], though the LET range

Figure 2.3 Alpha particle source on the top of the testing circuit.

of alpha particles exiting from an Am-241 source can range from approximately 0.1 LET to 2.6 LET.

Alpha sources offer the advantage of not requiring an accelerator and having no beam time limitations. The dose rate can be controlled by applying various concentrations of Americium 241 to a copper plate. The alpha source used in this work is shown in Figure 2.3.

#### 2.3.3 Co-60 Irradiation Source

Co-60 is a widely used radioactive isotope in various industrial, medical, and research applications due to its gamma-ray emission properties. It is produced as a result of neutron activation of stable cobalt-59 (Co-59) in a nuclear reactor, which subsequently decays with a half-life of 5.27 years into nickel-60 (Ni-60) while emitting two gamma photons with energies of 1.17 MeV and 1.33 MeV [42].

The Co-60 irradiation source utilized for the TID experiments were conducted using a Gammacell 220 Co-60 chamber (Figure 2.4) at the University of Saskatchewan. This chamber is capable of providing an irradiation rate of 108.2 rad(Si) per minute. The designated container for the Device Under Test (DUT) measures approximately 15.2 cm x 20.6 cm. A cable bundle with a diameter of up to 3.5 cm can be accommodated, allowing for the biasing and readout of the electronics being irradiated using external test equipment. A cable length of approximately 1 meter is required for this setup.

Figure 2.4 Gammacell 220 Co-60 Irradiator.

## 2.3.4 Proton Irradiation Source

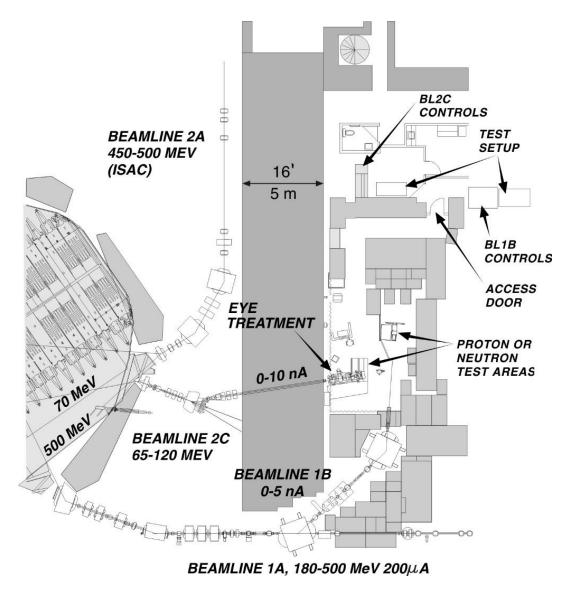

Proton beam irradiation sources are an advanced technology that employ accelerated protons to create a highly focused and precise beam of energy. Proton beams share a similarity with heavy ion beams in that they are both monoenergetic, making it convenient to examine the cross-section in relation to LET or energy [41]. The energy levels of proton beams can range from a few MeV to several hundred MeV, which is considerably lower than the highest energy of protons found in space. Nonetheless, for a majority of ICs, the cross-section reaches saturation at around 100 MeV [41]. In this study, experiments are conducted at TRIUMF's Proton Irradiation Facility (PIF) in Vancouver. A schematic representation of the laboratory can be seen in Figure 2.5.

Figure 2.5 Floorplan of the PIF lab at TRIUMF [43].

## 2.3.5 Laser Irradiation Source

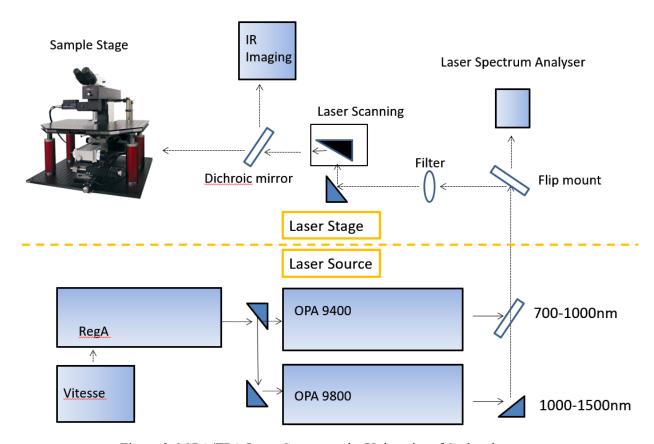

The laser testing mechanism involves the interaction of laser light with silicon, generating electron-hole pairs that produce SET pulses akin to those created by ion impacts. Laser irradiation sources are favored over alternative irradiation methods due to their increased precision and accuracy. They offer detailed spatial and temporal information, allowing for fine control over both time and location. Additionally, laser irradiation sources are a more cost-effective option compared to other methods. Figure 2.6 shows the SPA/TPA Laser System at the University of Saskatchewan.

Figure 2.6 SPA/TPA Laser System at the University of Saskatchewan.

## 2.4 ECC and Hamming Code

ECC plays a crucial role in ensuring the reliable transmission of data through electrical circuits. Researchers have employed various error-detecting methods, such as parity bits and Cyclic Redundancy Checks (CRC) to address electrical error issues in IC design [44-48]. ECC allows for the automatic correction of errors in data transport by adding redundant bits to enhance reliability. Upon receiving the data, the receiver or detection device evaluates it based on the redundant bits. Data stored in memory is highly susceptible to SEEs, making error detection and correction particularly valuable for protecting memory circuits [49].

Hamming code is an error-correcting code that plays a crucial role in the field of digital communication and computer systems, which was introduced by Richard W. Hamming, who was an American mathematician and computer scientist [50]. The Hamming code works on the

principle of parity bits, which are extra bits added to the original data bits to facilitate error detection and correction. In the Hamming code, these parity bits are placed at specific positions, namely the power of 2 (e.g., 1, 2, 4, 8, etc.), within the encoded data [51]. The positioning of the parity bits allows the code to identify and correct single-bit errors that may occur during data transmission or storage [52].

When encoding a data sequence using the Hamming code, the parity bits are calculated based on the data bits in specific groups, which are determined by the position of the parity bit itself. For example, parity bit P1 is responsible for data bits in positions 1, 3, 5, 7, and so on, while parity bit P2 is responsible for data bits in positions 2, 3, 6, 7, and so on [53]. The parity bits are set to either 0 or 1 to ensure an even number of 1's in each group, which is known as even parity.

Upon receiving the encoded data, the receiver evaluates the parity bits for the received data sequence using the same method as the sender. If the calculated parity bits match the received parity bits, the data is assumed to be error-free. However, if there is a mismatch, the receiver can identify the position of the erroneous bit by adding the positions of the incorrect parity bits. Consequently, the receiver can correct the single-bit error and recover the original data.

#### References

- [1] L. Sihver et al., "Radiation environment at aviation altitudes and in space", Radiation Protection Dosimetry, vol. 164, no. 4, pp. 477-483, May 2015.

- [2] P. E. Dodd and L. W. Massengill, "Basic mechanisms and modeling of single-event upset in digital microelectronics," IEEE Transactions on Nuclear Science, vol. 50, no. 3, pp. 583-602, Jun. 2003.

- [3] R. C. Baumann, "Soft errors in advanced semiconductor devices Part I: The three radiation sources," IEEE Transactions on Device and Materials Reliability, vol. 1, no. 1, pp. 17-22, Mar. 2001.

- [4] A.H. Johnston, "Scaling and Technology Issues for Soft Error Rates", in Proceedings of the Fourth Ann. Research Conf. Reliability, Oct. 2000. [Online]. Available: <a href="https://doi.org/2014/16240">https://doi.org/2014/16240</a>

- [5] G. C. Messenger and M. S. Ash, "The effects of radiation on electronic systems," Van Nostrand Reinhold, New York, NY, 1992.

- [6] O. Musseau, "Single-event effects in SOI technologies and devices," IEEE Transactions on Nuclear Science, vol. 43, no. 2, pp. 603-613, Apr. 1996.

- [7] P. E. Dodd, M. R. Shaneyfelt, J. R. Schwank, and J. A. Felix, "Current and future challenges in radiation effects on CMOS electronics," IEEE Transactions on Nuclear Science, vol. 57, pp. 1747-1763, Aug. 2010.

- [8] P. E. Dodd, M. R. Shaneyfelt, J. A. Felix, and J. R. Schwank, "Production and propagation of single-event transients in high-speed digital logic ICs," IEEE Transactions on Nuclear Science, vol. 51, no. 6, pp. 3278-3284, Dec. 2004.

- [9] H. Wang, "Study of single-event effects on digital systems," Ph.D. dissertation, College of Graduate Studies Research, University of Saskatchewan, Saskatoon, Canada, 2015.

- [10] T. C. May and M. H. Woods, "Alpha-Particle-Induced Soft Errors in Dynamic Memories," IEEE Transactions on Electron Devices, vol. 26, no. 1, pp. 2-9, Jan. 1979.

- [11] E. Normand, "Single event upset at ground level," IEEE Transactions on Nuclear Science, vol. 43, no. 6, pp. 2742-2750, Dec. 1996.

- [12] J. F. Ziegler, H. W. Curtis, H. P. Muhlfeld, C. J. Montrose, and B. Chin, "IBM experiments in soft fails in computer electronics (1978-1994)," IBM Journal of Research and Development, vol. 40, no. 1, pp. 3-18, Jan. 1996.

- [13] D. A. Sunderland, J. Lerma and A. L. McKay, "Designing electronic systems for space," in IEEE Bipolar/BiCMOS Circuits and Technology Meeting, Monterey, CA, USA, 2008, pp. 171-177.

- [14] K. W. Gear, A. Sanchez-Macián, and J. A. Maestro, "An analysis of FPGA configuration memory SEU accumulation and a preventative scrubbing technique," Microprocessors and Microsystems, vol. 90, p. 104467, 2022.

- [15] Y. Ko, "Characterizing System-Level Masking Effects against Soft Errors," Electronics, vol. 10, no. 18, pp. 2286, Sep. 2021.

- [16] S. Yang, Q. Shao, and C. Bian, "Reliability analysis of ensemble fault tolerance for soft error mitigation against complex radiation effect," Reliability Engineering & System Safety, vol. 217, p.108092, 2022.

- [17] N. A. Dodds et al., "Effectiveness of SEL hardening strategies and the latchup domino effect", IEEE Transactions on Nuclear Science, vol. 59, no. 6, pp. 2642-2650, Dec. 2012.

- [18] J. M. Hales et al., "Pulsed-laser testing to quantitatively evaluate latchup sensitivity in mixed-signal ASICs", IEEE Transactions on Nuclear Science, vol. 69, no. 3, pp. 429-435, Mar. 2022.

- [19] N. A. Dodds, "Single event latchup: hardening strategies, triggering mechanisms, and testing considerations," Ph.D. thesis, Faculty of the Graduate School, Vanderbilt University, Nashville, TN, USA, 2012.

- [20] M. Nicolaidis, "A low-cost single-event latchup mitigation scheme", in the Proceedings of the IEEE International On-Line Testing Symposium, Lake Como, Italy, Jul. 2006, pp. 111-118.

- [21] R.R. Troutman, "Latchup in CMOS Technology: The Problem and its Cure", Kluwer Publications, Boston, MA, 1986.

- [22] A. Ju et al., "Analysis of Ion-Induced SEFI and SEL Phenomena in 90 nm NOR Flash Memory," IEEE Transactions on Nuclear Science, vol. 68, no. 10, pp. 2508-2515, Oct. 2021.

- [23] S. Kuboyama, E. Mizuta, Y. Nakada and H. Shindou, "Physical Analysis of Damage Sites Introduced by SEGR in Silicon Vertical Power MOSFETs and Implications for Postirradiation Gate-Stress Test," IEEE Transactions on Nuclear Science, vol. 66, no. 7, pp. 1710-1714, Jul. 2019.

- [24] K. Muthuseenu et al., "Analysis of SEGR in Silicon Planar Gate Super-Junction Power MOSFETs," IEEE Transactions on Nuclear Science, vol. 68, no. 5, pp. 611-616, May 2021.

- [25] J.-M. Lauenstein, "Single-Event Gate Rupture in Power MOSFETs: A New Radiation Hardness Assurance Approach," Ph.D. thesis, Faculty of the Graduate School, University of Maryland, College Park, MD, USA, 2011.

- [26] T. A. Fischer, "Heavy-Ion-induced gate-rupture in power MOSFETs", IEEE Transactions on Nuclear Science, vol. NS-34, no. 6, pp. 1786-1791, Dec. 1987.

- [27] Z. Chen et al., "Analysis and Mitigation of Single-Event Gate Rupture in VDMOS With Termination Structure," IEEE Transactions on Nuclear Science, vol. 68, no. 6, pp. 1272-1278, Jun. 2021.

- [28] J. D. Popp, "Developing radiation hardened complex system on chip ASICs in 33 ultradeep submicron CMOS processes," IEEE Nuclear and Space Radiation Effects Conference Short Course, Denver, CO, USA, Jul. 2010.

- [29] E. E. King and R. L. Martin, "Effects of Total Dose Ionizing, Radiation on the 1802 Microprocessor," IEEE Transactions on Nuclear Science, vol. 24, no. 6, pp. 2172-2176, 1977.

- [30] H. L. Hughes, "A Pre-Irradiation Indicator for Total-Dose Ionizing Radiation-Sensitivity," IEEE Transactions on Nuclear Science, vol. 22, no. 5, pp. 2118-2119, 1975.

- [31] D. Neamen, W. Shedd and B. Buchanan, "Radiation induced charge trapping at the silicon sapphire substrate interface," IEEE Transactions on Nuclear Science, vol. 21, no. 6, pp. 211-216, 1974.

- [32] P. Paillet et al., "Total ionizing dose effects on deca-nanometer fully depleted SOI devices," IEEE Transactions on Nuclear Science, vol. 52, no. 6, pp. 2345-2352, 2005.

- [33] G. Cellere et al., "Effect of different total ionizing dose sources on charge loss from programmed floating gate cells," IEEE Transactions on Nuclear Science, vol. 52, no. 6, pp. 2372-2377, Dec. 2005.

- [34] M. J. Campola et al., "Compendium of Total Ionizing Dose and Displacement Damage Results from NASA Goddard Spaceflight Center," in Proceedings of the IEEE Radiation Effects Data Workshop, Portland, OR, USA, Jul. 2016, pp. 10-18.

- [35] R. M. Chen et al., "Effects of Total-Ionizing-Dose Irradiation on SEU- and SET-Induced Soft Errors in Bulk 40-nm Sequential Circuits," IEEE Transactions on Nuclear Science, vol. 64, no. 1, pp. 471-476, Feb. 2017.

- [36] H.-B. Wang et al., "An area efficient stacked latch design tolerant to SEU in 28 nm FDSOI technology," IEEE Transactions on Nuclear Science, vol. 63, no. 6, pp. 3003-3009, Dec. 2016.

- [37] R. Liu, "Study of Radiation Effects on 28nm UTBB FDSOI Technology," Ph.D. dissertation, College of Graduate Studies Research, University of Saskatchewan, Saskatoon, Canada, 2017.

- [38] J. Leray, J. Baggio, V. Ferlet-Cavrois, and O. Flament, "Atmospheric neutron effects in advanced microelectronics, standards and applications," in Proceedings of the IEEE International Conference on Integrated Circuit Design and Technology, Austin, TX, USA, May 2004, pp. 311-321.

- [39] J. C. Pickel and J. T. Blandford, "Cosmic-ray-induced errors in MOS devices," IEEE Transactions on Nuclear Science, vol. 27, no. 2, pp. 1006-1015, Apr. 1980.

- [40] H. Tian, "Study of radiation-tolerant SRAM design," M.S. thesis, College of Graduate Studies Research, University of Saskatchewan, Saskatoon, Canada, 2019.

- [41] S. Shi, "Single Event Evaluation on 28nm Fully Depleted Silicon-On-Insulator SRAM and Commercial Solid-State Drives," M.S. thesis, College of Graduate Studies Research, University of Saskatchewan, Saskatoon, Canada, 2020.

- [42] M. F. L'Annunziata, "Radioactivity: Introduction and History," Elsevier, 2007.

- [43] E. W. Blackmore, "Operation of the TRIUMF (20-500 MeV) proton irradiation facility," in Proceedings of the IEEE Radiation Effects Data Workshop, Reno, NV, USA, Jul. 2000, pp. 1-5.

- [44] T. J. Richardson, M. A. Shokrollahi, and R. L. Urbanke, "Design of capacity-approaching irregular low-density parity-check codes," IEEE Transactions on Information Theory, vol. 47, no. 2, pp. 619-637, Feb. 2001.

- [45] E. J. Wyrwas, "Proton Irradiation of the 16GB Intel Optane SSD," [Online]. Available: https://ntrs.nasa.gov/api/citations/20180000932/downloads/20180000932.pdf. [Accessed: Apr. 22, 2023].

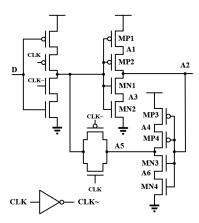

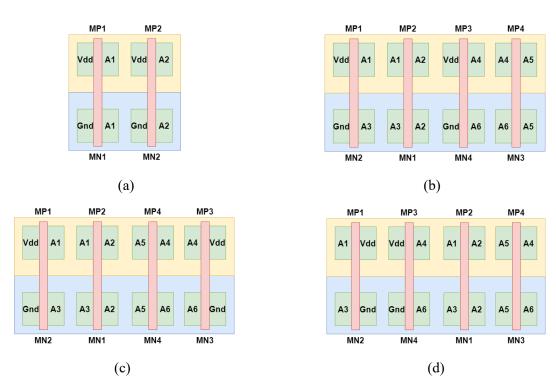

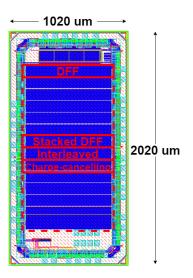

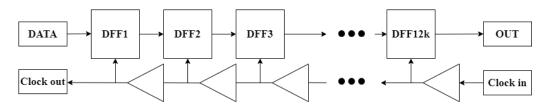

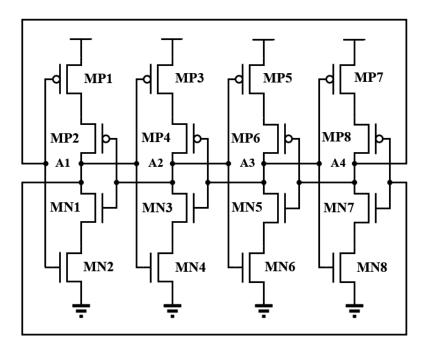

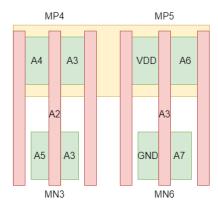

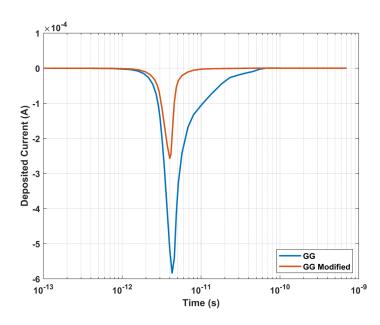

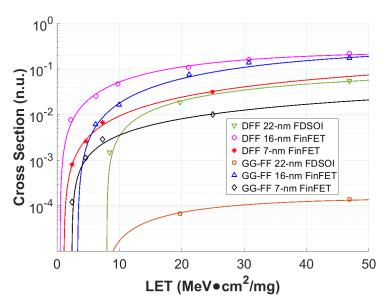

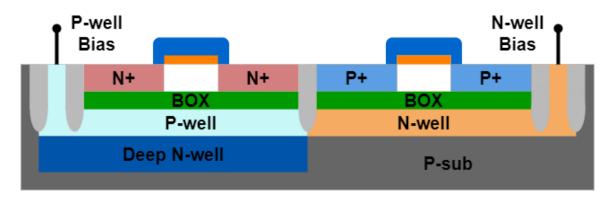

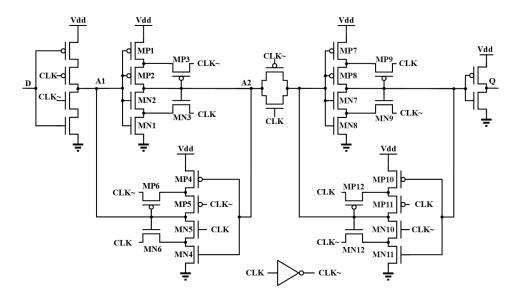

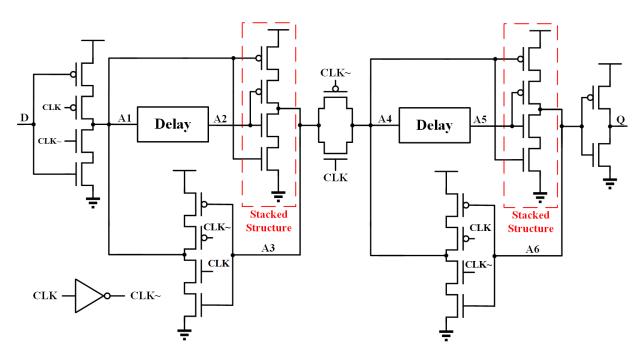

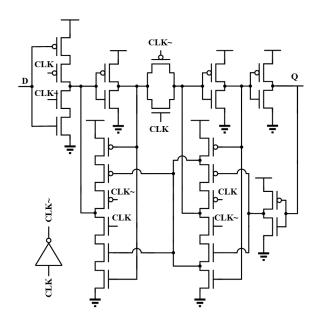

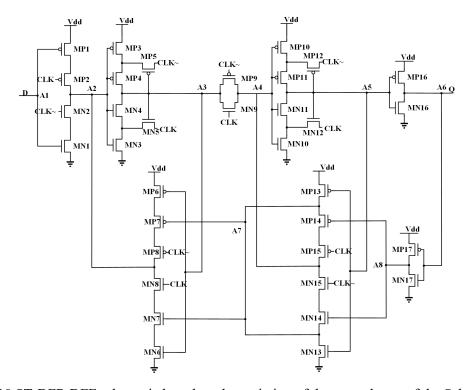

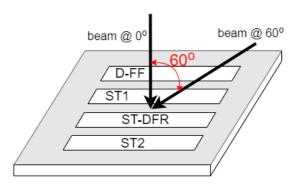

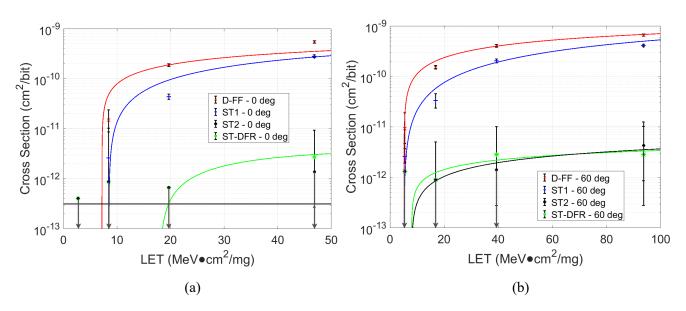

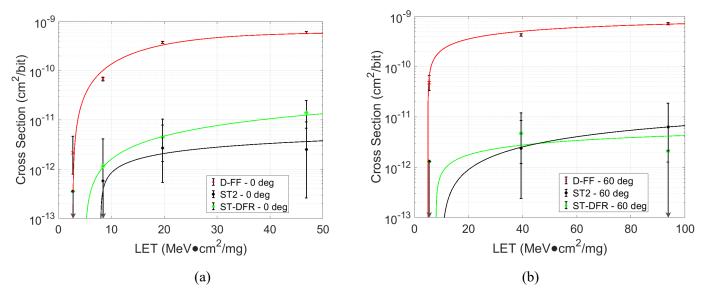

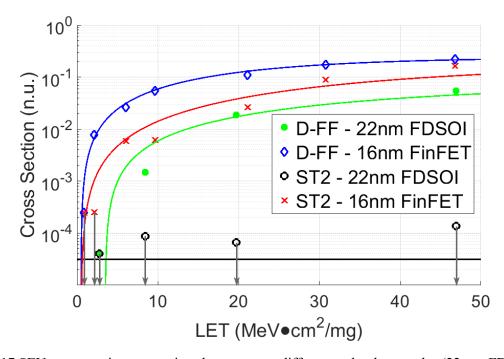

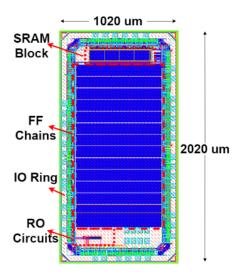

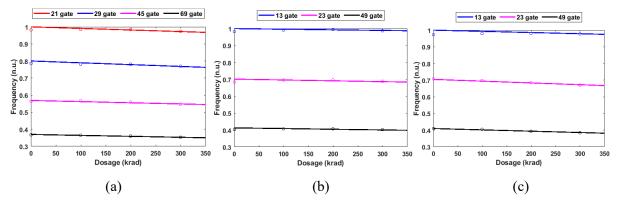

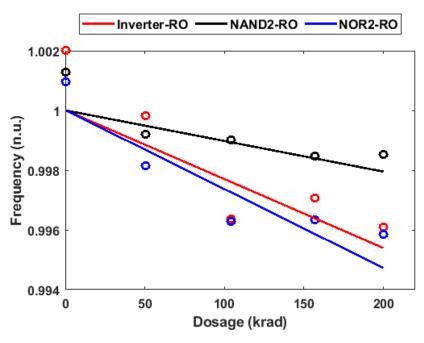

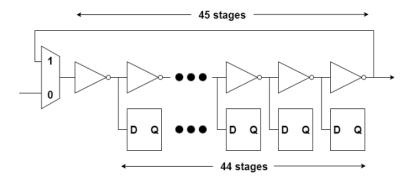

- [46] D. J. C. MacKay, "Good error-correcting codes based on very sparse matrices," IEEE Transactions on Information Theory, vol. 45, no. 2, pp. 399-431, Mar. 1999.