# Single Event Effect Hardening Designs in 65nm CMOS Bulk Technology

A Thesis Submitted to the College of

Graduate and Postdoctoral Studies

In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

By

Mo Chen

PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree

from the University of Saskatchewan, I agree that the Libraries of this University may make it

freely available for inspection. I further agree that permission for copying of this thesis in any

manner, in whole or in part, for scholarly purposes may be granted by the professor or professors

who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of

the College in which my thesis work was done. It is understood that any copying or publication or

use of this thesis or parts thereof for financial gain shall not be allowed without my written

permission. It is also understood that due recognition shall be given to me and to the University of

Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part

should be addressed to:

Head of the Department of Electrical and Computer Engineering

University of Saskatchewan

3B38 Engineering Building

57 Campus Drive

Saskatoon, Saskatchewan

Canada

S7N 5A9

i

#### **ABSTRACT**

Radiation from terrestrial and space environments is a great danger to integrated circuits (ICs). A single particle from a radiation environment strikes semiconductor materials resulting in voltage and current perturbation, where errors are induced. This phenomenon is termed a Single Event Effect (SEE). With the shrinking of transistor size, charge sharing between adjacent devices leads to less effectiveness of current radiation hardening methods. Improving fault-tolerance of storage cells and logic gates in advanced technologies becomes urgent and important.

A new Single Event Upset (SEU) tolerant latch is proposed based on a previous hardened Quatro design. Soft error analysis tools are used and results show that the critical charge of the proposed design is approximately 2 times higher than that of the reference design with negligible penalty in area, delay, and power consumption. A test chip containing the proposed flip-flop chains was designed and exposed to alpha particles as well as heavy ions. Radiation experimental results indicate that the soft error rates of the proposed design are greatly reduced when Linear Energy Transfer (LET) is lower than 4, which makes it a suitable candidate for ground-level high reliability applications.

To improve radiation tolerance of combinational circuits, two combinational logic gates are proposed. One is a layout-based hardening Cascode Voltage Switch Logic (CVSL) and the other is a fault-tolerant differential dynamic logic. Results from a SEE simulation tool indicate that the proposed CVSL has a higher critical charge, less cross section, and shorter Single Event Transient (SET) pulses when compared with reference designs. Simulation results also reveal that the proposed differential dynamic logic significantly reduces the SEU rate compared to traditional dynamic logic, and has a higher critical charge and shorter SET pulses than reference hardened design.

#### **ACKNOWLEDGEMENTS**

I wish to express my sincere gratitude to my supervisor Dr. Li Chen for his continuous support of my study and related research during these two years. Without his patience, motivation, and immense knowledge, I could not have completed my projects and thesis. His guidance helped me have a deeper understanding of digital circuits and radiation effects. Thanks to him I gained valuable experience in Integrated Circuit design and implemented my ideas into real chips. He also took time out from his busy schedule to offer me valuable suggestions and comments on my thesis.

My appreciation also extends to my laboratory colleagues, Haibin Wang and Yuanqing Li. We worked together to finish the test chip from design to sign off and they supported me greatly and gave me a lot of technical suggestions. Thanks also go to Trevor Zintel, who was our support engineer and helped us a lot with license and software problems.

Lastly and most of all, I would like to thank my parents, whose value to me only grows with age. It is their love and encouragement that helped me to survive all the stress from these years; they never let me give up. I am so proud to be their daughter.

# TABLE OF CONTENTS

| PERM   | SSION TO USEi                       |

|--------|-------------------------------------|

| ABST   | ACTii                               |

| ACKN   | WLEDGEMENTSiii                      |

| TABL   | OF CONTENTSiv                       |

| LIST ( | TABLESvii                           |

| LIST ( | F FIGURESix                         |

| LIST ( | F ABBREVIATIONSxiv                  |

| СНАР   | ER 1: INTRODUCTION1                 |

| 1.1    | Background and Motivation1          |

| 1.2    | Objectives4                         |

| 1.3    | Thesis Organization6                |

| СНАР   | ER 2: RADIATION EFFECTS BACKGROUND7 |

| 2.1    | SEE Basic Mechanism                 |

| 2.2    | Sources of Radiation9               |

|        | 2.2.1 Alpha Particles               |

|        | 2.2.2 Heavy Ions                    |

|        | 2.2.3 Neutrons                      |

|        | 2.2.4 Protons                       |

| 2.3    | SEU (Single Event Upset)12          |

| 2.4    | SET (Single Event Transient)16      |

| CHAP | TER 3: ( | CURRENT SEE TOLERANT DESIGNS                               | 18     |

|------|----------|------------------------------------------------------------|--------|

| 3.1  | Basic N  | Mitigation Approaches                                      | 19     |

| 3.2  | Redund   | lancy-based Mitigation Methods                             | 20     |

|      | 3.2.1    | TMR                                                        | 21     |

|      | 3.2.2    | Guard-Gate                                                 | 21     |

|      | 3.2.3    | DICE                                                       | 23     |

|      | 3.2.4    | Quatro                                                     | 24     |

| 3.3  | Layout   | -based Mitigation Methods                                  | 26     |

|      | 3.3.1    | Charge Sharing and Pulse Quenching                         | 27     |

|      | 3.3.2    | Node Separation                                            | 30     |

|      | 3.3.3    | Well Contact and Guard Ring                                | 31     |

|      | 3.3.4    | Layout Design Through Error-Aware Transistor Positioning   | 33     |

| СНАР | TER 4: A | A RADIATION HARDENING DESIGN IN SEQUENTIAL CIRCU           | JITS38 |

| 4.1  | Propose  | ed Fault-tolerant Design and SEU Analysis                  | 38     |

|      | 4.1.1    | Proposed Quatro-based Flip-flop Design and Basic Operation | 38     |

|      | 4.1.2    | SEU Resistance Analysis                                    | 41     |

| 4.2  | Single 1 | Event Simulations                                          | 46     |

|      | 4.2.1    | TFIT Soft Error Simulation Setup                           | 46     |

|      | 4.2.2    | Simulation Results and Analysis                            | 48     |

| 4.3  | Perforn  | nance Comparison                                           | 51     |

| СНАР | TER 5: I | RADIATION HARDENING DESIGNS IN COMBINATION CIRC            | UITS53 |

| 5.1  | Static I | _ogic Hardening                                            | 53     |

|      | 5.1.1                               | Static CMOS Logic and CVSL                    | 53 |

|------|-------------------------------------|-----------------------------------------------|----|

|      | 5.1.2                               | Proposed Layout-based Hardening Design        | 55 |

|      | 5.1.3                               | SET Simulation Results and Analysis           | 58 |

| 5.2  | Dynam                               | ic Logic Hardening                            | 62 |

|      | 5.2.1                               | Single Event Effect Analysis on Dynamic Logic | 62 |

|      | 5.2.2                               | Proposed Design                               | 63 |

|      | 5.2.3                               | TFIT Simulation Results                       | 67 |

| 5.3  | Delay,                              | Power, and Area Comparison                    | 72 |

| СНАР | TER 6: 1                            | TEST CHIP DESIGN AND EXPERIMENTAL RESULTS     | 75 |

| 6.1  | Test Ch                             | nip Design                                    | 75 |

|      | 6.1.1                               | Flip-flop Chains                              | 75 |

|      | 6.1.2                               | Clock Network and Power Grid                  | 76 |

|      | 6.1.3                               | Overall Chip and Verification                 | 79 |

| 6.2  | PCB D                               | esign and Test System Setup                   | 81 |

| 6.3  | Alpha T                             | Test Results and Analysis                     | 83 |

| 6.4  | Heavy-Ion Test Results and Analysis |                                               |    |

| СНАР | TER 7: S                            | SUMMARY AND FUTURE WORK                       | 88 |

| 7.1  | Summa                               | ary                                           | 88 |

| 7.2  | Conclu                              | sions                                         | 89 |

| 7.3  | Future '                            | Work                                          | 90 |

| DEED | DENCES                              |                                               | 01 |

# LIST OF TABLES

| Table 4.1 SEU immunity of four nodes to positive and negative pulses in the Quatro cell              | 41 |

|------------------------------------------------------------------------------------------------------|----|

| Table 4.2 Critical charge of Quatro designs with different transistor sizes                          | 46 |

| Table 4.3 C-to-Q delay of Quatro and Proposed FFs                                                    | 51 |

| Table 4.4 Power dissipation of Quatro and proposed FFs with different data activities                | 52 |

| Table 5.1 Transistor size of CVSL and reference static designs                                       | 57 |

| Table 5.2 Critical charge of static AND gate, regular CVSL, and proposed CVSL design                 | 59 |

| Table 5.3 Cross section (cm <sup>2</sup> ) of three logics with different LET values when input is 0 | 60 |

| Table 5.4 Transistor size of reference and proposed dynamic logic gates                              | 65 |

| Table 5.5 SEU cross section of reference and proposed dynamic logic gates                            | 69 |

| Table 5.6 Critical charge (fC) of three dynamic logic gates                                          | 70 |

| Table 5.7 Rising and falling delay of the six logic gates                                            | 72 |

| Table 5.8 Power consumption of the six logic gates                                                   | 73 |

| Table 5.9 Area of the six logic gates                                                                | 73 |

| Table 6.1 Transistor size of the proposed FF design                                                  | 76 |

| Table 6.2 Post-layout simulation conditions                                                          | 80 |

| Table 6.3 Alpha test results of reference Quatro FF and proposed FF                                  | 84 |

| Table 6.4 Parameters of heavy ions | 85 |

|------------------------------------|----|

|------------------------------------|----|

# LIST OF FIGURES

| Figure 1.1 Percentage of upsets with the shrinking of technology nodes [7]                      |

|-------------------------------------------------------------------------------------------------|

| Figure 2.1 Basic mechanism of a strike in a reverse-biased junction                             |

| Figure 2.2 DFF and SEU analysis                                                                 |

| Figure 2.3 Voltage waves with time of storage nodes A and B in low and high collected charges   |

|                                                                                                 |

| Figure 3.1 Bulk NMOS and SOI NMOS                                                               |

| Figure 3.2 Feedback structure in a back-to-back inverter pair                                   |

| Figure 3.3 Illustration of the TMR principle                                                    |

| Figure 3.4 Schematic of a guard-gate [40]                                                       |

| Figure 3.5 Guard-gate used in a combinational circuit                                           |

| Figure 3.6 Dual Interlocked Storage Cell (DICE) [12]                                            |

| Figure 3.7 DICE latch with 4 guard-gates [42]24                                                 |

| Figure 3.8 Quatro-10T cell [13]                                                                 |

| Figure 3.9 Regular 6T cell                                                                      |

| Figure 3.10 The cross section of CMOS transistors and the illustration of the parasitic bipolar |

| transistors                                                                                     |

| Figure 3.11 Diagram of an active node and passive node affected by charge sharing               | 28    |

|-------------------------------------------------------------------------------------------------|-------|

| Figure 3.12 Illustration of the pulse quenching effect in a chain of inverters                  | 29    |

| Figure 3.13 Interdigitating of transistors                                                      | 31    |

| Figure 3.14 Well contacts in PMOS and NMOS transistors                                          | 32    |

| Figure 3.15 Diagram of a guard ring outside of a transistor [46]                                | 33    |

| Figure 3.16 Charge cancellation when striking both Drains of the PMOS and NMOS in an            |       |

| inverter                                                                                        | 34    |

| Figure 3.17 Layout of an inverter using LEAP principle                                          | 35    |

| Figure 3.18 LEAP-DICE schematic and layout diagram [15]                                         | 36    |

| Figure 4.1 Diagram of the regular Quatro latch [13]                                             | 38    |

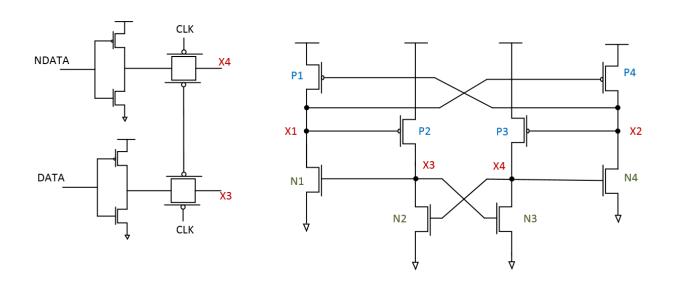

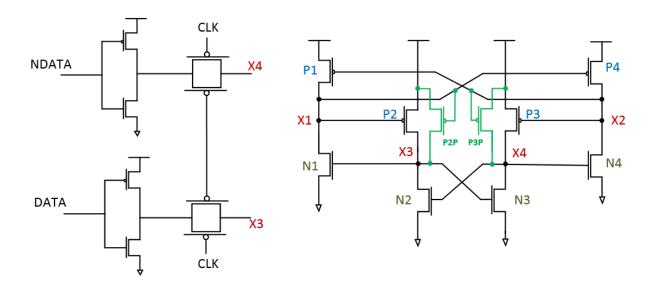

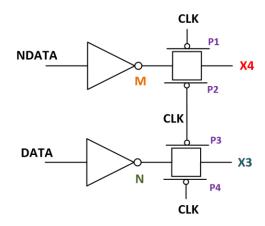

| Figure 4.2 Proposed Quatro-based latch                                                          | 39    |

| Figure 4.3 Schematic diagram of transmission gates                                              | 40    |

| Figure 4.4 Layout sketch of two transmission gates                                              | 40    |

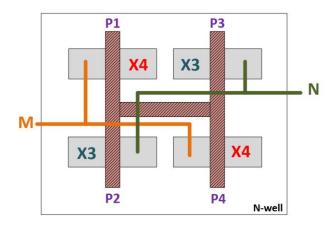

| Figure 4.5 A capacitor controlled by a switch is used to simulate particle injection            | 43    |

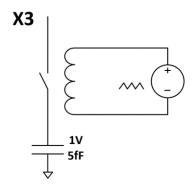

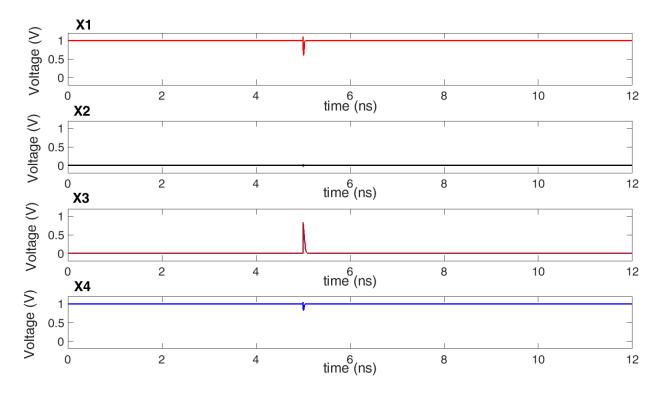

| Figure 4.6 Waveforms of four nodes in the Quatro design: when a 5fC positive charge is injured. | ected |

| into X3, the cell upsets in this case                                                           | 44    |

| Figure 4.7 Waveforms of four nodes in the proposed design: when a 5fC positive charge is                |

|---------------------------------------------------------------------------------------------------------|

| injected into X3, the cell does not upset in this case                                                  |

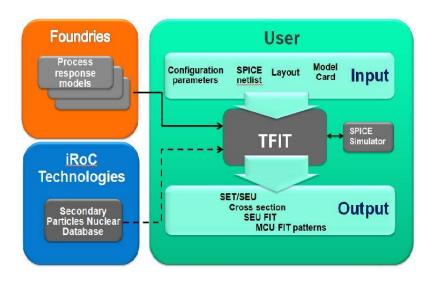

| Figure 4.8 TFIT block diagram and workflow [52]47                                                       |

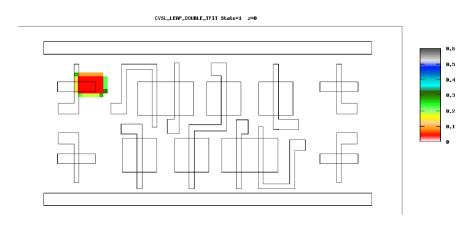

| Figure 4.9 Sensitivity map of Quatro (CLK=0 All-0) when LET is 2 MeV·cm <sup>2</sup> /mg48              |

| Figure 4.10 Sensitivity map of Proposed FF (CLK=0 All-0) when LET is 2 MeV·cm <sup>2</sup> /mg49        |

| Figure 4.11 Sensitivity map of Quatro (CLK=0 All-0) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg49        |

| Figure 4.12 Sensitivity map of Proposed FF (CLK=0 All-0) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg .49 |

| Figure 4.13 Sensitivity map of Quatro (CLK=1 All-0) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg49        |

| Figure 4.14 Sensitivity map of Proposed FF (CLK=1 All-0) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg .49 |

| Figure 4.15 Sensitivity map of Quatro (CLK=0 All-1) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg50        |

| Figure 4.16 Sensitivity map of Proposed FF (CLK=0 All-1) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg .50 |

| Figure 4.17 Sensitivity map of Quatro (CLK=1 All-1) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg50        |

| Figure 4.18 Sensitivity map of Proposed FF (CLK=1 All-1) LET from 1.3 to 30 MeV·cm <sup>2</sup> /mg .50 |

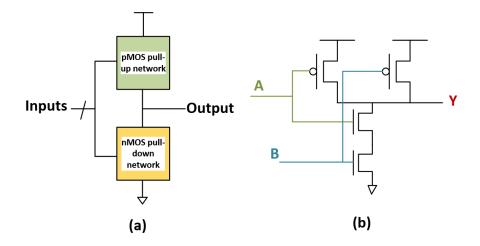

| Figure 5.1 (a) general static CMOS logics; (b) 2-input static NAND gate54                               |

| Figure 5.2 General CVSL gate                                                                            |

| Figure 5.3 Schematic of two-level CVSL AND-NAND gates                                                   |

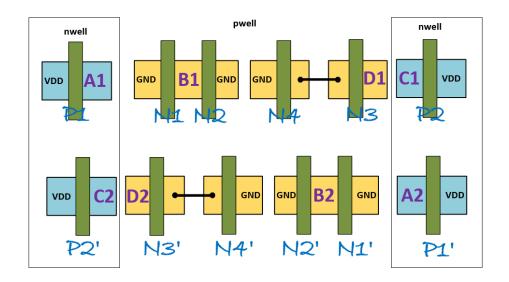

| Figure 5.4 Layout diagram of two-level CVSL gates                                                       |

| Figure 5.5 Schematic of reference static CMOS AND gate                                | 57            |

|---------------------------------------------------------------------------------------|---------------|

| Figure 5.6 Sensitivity map of reference static AND gate when input is 0               | 59            |

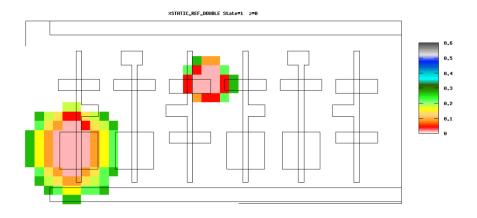

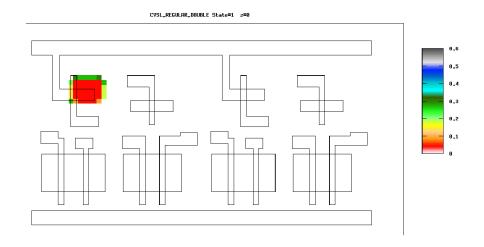

| Figure 5.7 Sensitivity map of regular CVSL when input is 0                            | 60            |

| Figure 5.8 Sensitivity map of proposed CVSL when input is 0                           | 60            |

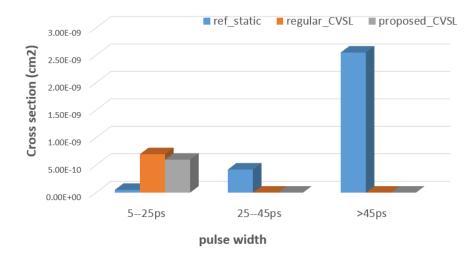

| Figure 5.9 Cross section changes with pulse widths of three static designs when input | t is 0 at 4.4 |

| MeV·cm <sup>2</sup> /mg                                                               | 61            |

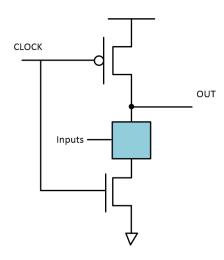

| Figure 5.10 A general dynamic logic gate                                              | 62            |

| Figure 5.11 A regular dynamic AND gate                                                | 62            |

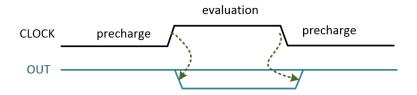

| Figure 5.12 Precharge and evaluation stages of a dynamic logic                        | 63            |

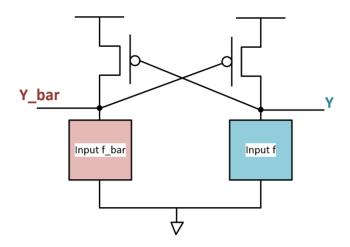

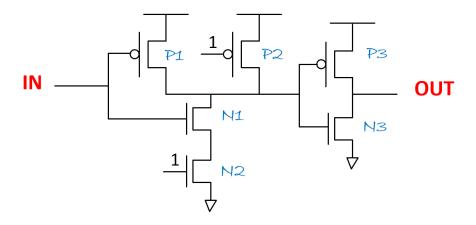

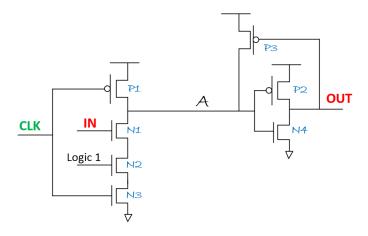

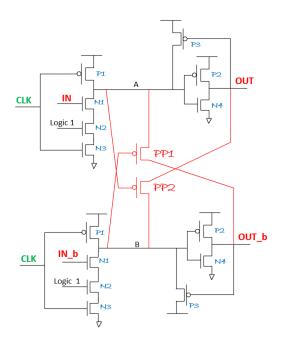

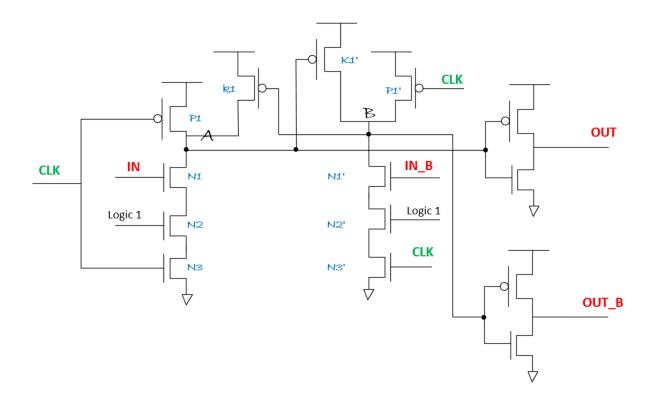

| Figure 5.13 Proposed differential dynamic logic gate                                  | 64            |

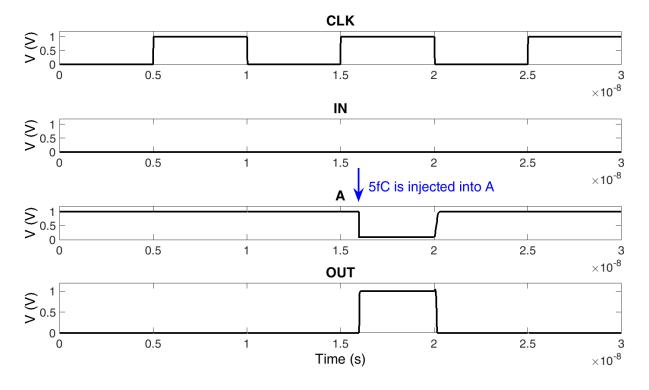

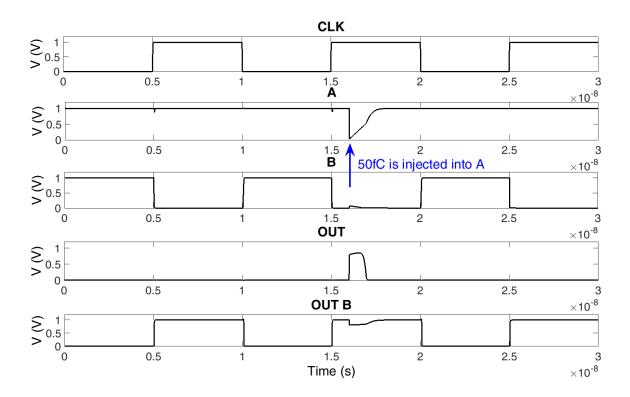

| Figure 5.14 Waveforms of reference design when 5fC charge is injected into node A     | 65            |

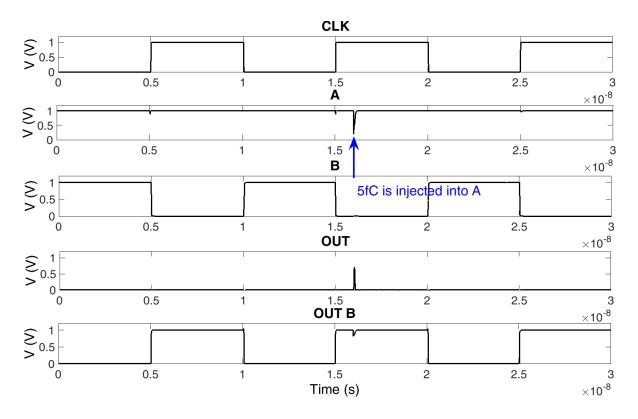

| Figure 5.15 Waveforms of proposed design when 5fC charge is injected into node A      | 66            |

| Figure 5.16 Waveforms of proposed design when 50fC charge is injected into node A     | A67           |

| Figure 5.17 Schematic of the dynamic logic with differential keepers [57]             | 68            |

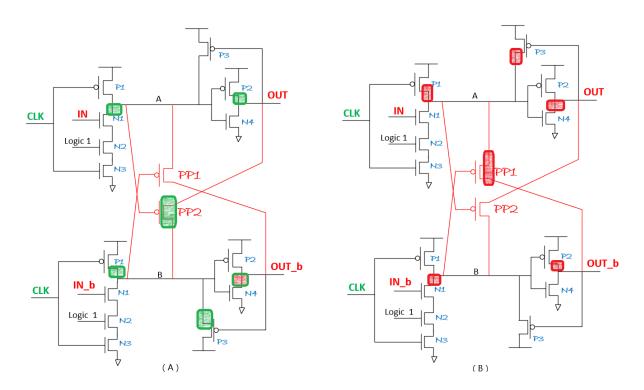

| Figure 5.18 Sensitive Drains of proposed design in evaluation phase when input is 0   | (A) and 1     |

| (B)                                                                                   | 70            |

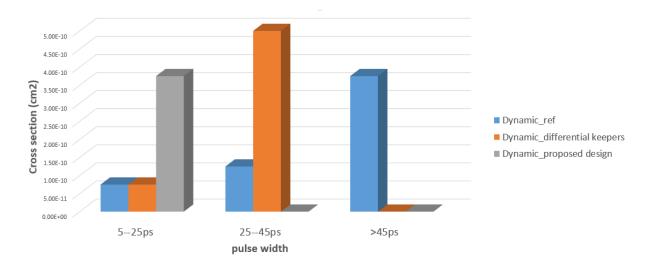

| Figure 5.19 Cross section of pulse width in the three dynamic designs when LET is 1.3 |    |

|---------------------------------------------------------------------------------------|----|

| MeV·cm <sup>2</sup> /mg and input is 1 for evaluation phase                           | 71 |

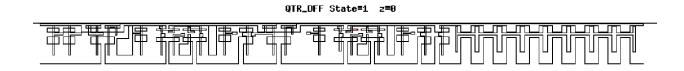

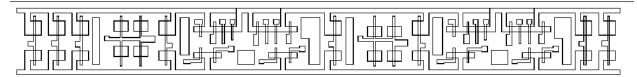

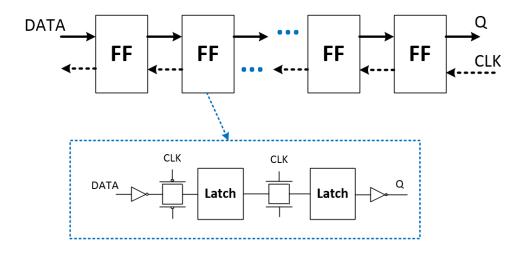

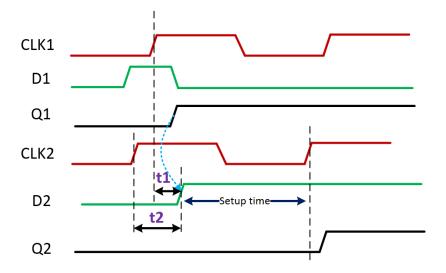

| Figure 6.1 Diagram of a flip-flop chain                                               | 75 |

| Figure 6.2 Diagram of reverse clock                                                   | 76 |

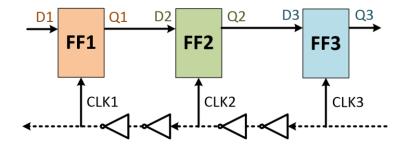

| Figure 6.3 Timing analysis of the reverse clock between two adjacent FF cells         | 77 |

| Figure 6.4 Power grid of the test chip                                                | 78 |

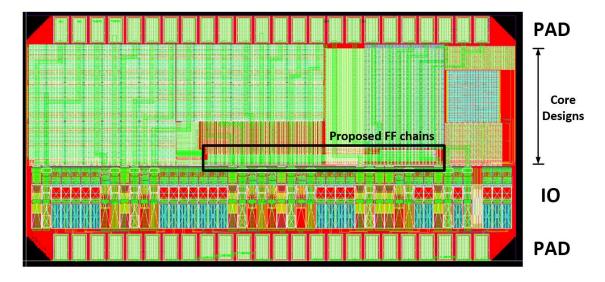

| Figure 6.5 Overall chip design                                                        | 79 |

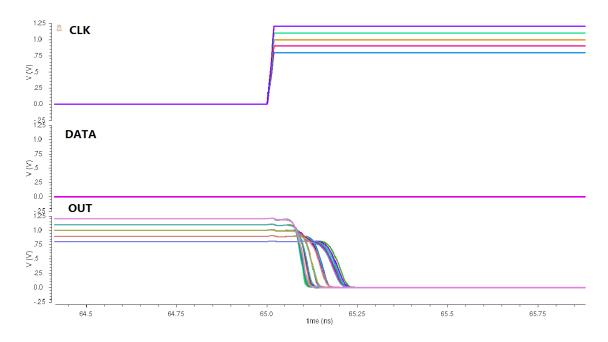

| Figure 6.6 Post-layout simulation waveforms                                           | 80 |

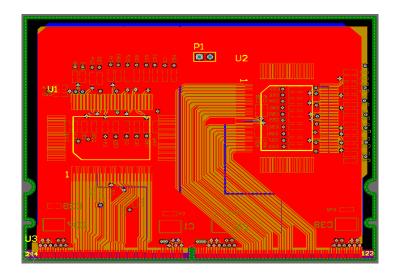

| Figure 6.7 Designed PCB by Altium Designer                                            | 81 |

| Figure 6.8 PCB and test chips                                                         | 81 |

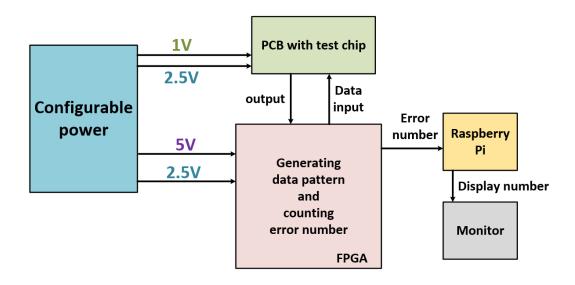

| Figure 6.9 Diagram of the test system                                                 | 82 |

| Figure 6.10 Alpha test setup                                                          | 83 |

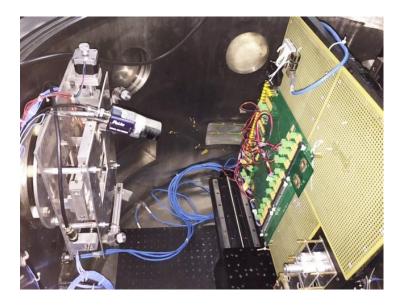

| Figure 6.11 Heavy-ion test setup                                                      | 85 |

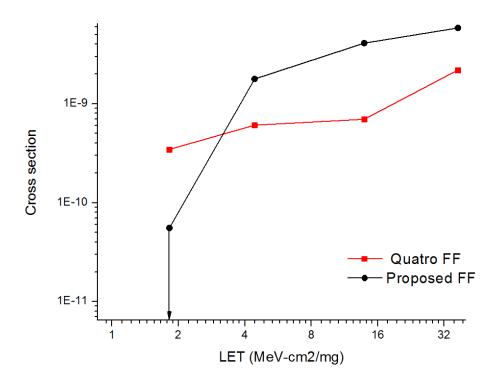

| Figure 6.12 Heavy-ion cross section of the reference and proposed FFs                 | 86 |

### LIST OF ABBREVIATIONS

3D Three-Dimension

BPSG Borophosphosilicate Glass

CIAE China Institute of Atomic Energy

CMOS Complementary Metal-Oxide Semiconductor

CPU Central Processing Unit

CQFP80 80-pin Surface Mount Ceramic Quad Flat Package

CVSL Cascode Voltage Switch Logic

DFF D-type Flip Flop

DICE Dual Interlocked Storage Cell

DIMM Dual In-line Memory Module

DUT Device Under Test

ECC Error Correcting Codes

ESD Electrostatic Discharge

FF Flip-flop

FIT Failure-In-Time

FPGA Field Programmable Gate Array

IBM International Business Machines

IC Integrated Circuit

I/O Input/Output

LEAP Layout Design Through Error-Aware Transistor Positioning

LET Linear Energy Transfer

MCU Multiple Cells Upset

MFF Mega Flip-flops

NMOS Negative-Channel Metal Oxide Semiconductor

PCB Printed Circuit Board

PMOS Positive-Channel Metal Oxide Semiconductor

Quatro Quad-node Ten Transistor Cell

RC Resistor-Capacitor

SBU Single Bit Upset

SE Soft Error

SEE Single Event Effect

SEL Single Event Latch-up

SEMU Single Event Multiple Nodes Upset

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SNM Static Noise Margin

SOI Silicon-On-Insulator

SPICE Simulation Program with Integrated Circuit Emphasis

SRAM Static Random Access Memory

TCAD Technology Computer Aided Design

TMR Triple Modular Redundancy

TSMC Taiwan Semiconductor Manufacturing Company

VDD Voltage Drain Drain

VSS Voltage Source Source

#### **CHAPTER 1: INTRODUCTION**

## 1.1 Background and Motivation

Particles from space and terrestrial radiation environments pose great dangers to integrated circuits (ICs). In the 1970s, Binder et al. were first to report upsets in a communication satellite caused by cosmic rays [1]. Before long, engineers at Intel discovered that alpha particles could cause nonrecurring errors in terrestrial memory devices [2], and they proposed the term "soft errors" for the first time to define random and recoverable faults caused by particle irradiation [3]. When a single energetic particle in a radiation environment strikes a microelectronic device, electron and hole pairs are generated along the path of the particle in semiconductor materials. The charge is collected by reverse-biased p-n junctions or diffusion regions, and causes voltage transients at the associated nodes. If the transient occurs in a combinational logic circuit, it is referred as a Single Event Transient (SET) [4]. If the SET occurs inside or is latched into a storage cell, it is called a Single Event Upset (SEU) [5]. The data errors caused from SETs and SEUs cannot damage the circuit itself, so they are often referred to as soft errors, which are defined as the random errors generated from particle striking. The generated charges may also trigger a parasitic thyristor structure and a direct and short current path between the power and the ground in Complementary Metal-Oxide Semiconductor (CMOS) Bulk technologies, which is referred as a Single Event Latch-up (SEL). A SEL can only be recovered by power recycling, which induces a significant reliability hazard for space instrumentation. These phenomena are generally termed Single Event Effects (SEEs) in microelectronics [6].

Besides charged particles like heavy ions, protons, and alpha particles, non-charged particles such as neutrons can also induce soft errors [5]. Unlike heavy ions and alpha particles which directly ionize semiconductor materials and generate electron-hole pairs, neutrons can cause soft

errors via indirect ionization, meaning that they react with silicon nuclei and generate secondary charged particles [6]. Heavy ions, alphas, protons, and neutrons comprise the major radiation sources. In a space environment, the abundant existence of protons and heavy ions is the main threat to space instrumentation. As to the electronics at ground level, SEEs are caused by alpha particles emitted from packaging materials and neutrons generated from cosmic rays reacting with the upper atmosphere of the earth.

In well-designed ICs, SEEs appear to be the most troublesome in a space environment or in high-altitude terrestrial environments. SEEs have been reported to be found in microprocessors, memories, network switches, routers, configuration bits in Field Programmable Gate Arrays (FPGA), and even in implantable medical devices (e.g., cardiac defibrillators) in terrestrial electronic systems [6]. The error rate can be as much as 50,000 FIT (Failure-In-Time: 1 failure per 109 hours of device operation), while the typical hard failure (e.g., gate oxide breakdown, metal electromigration, latch-up) rates in ICs add up to only 5-200 FIT [2]. For example, in 1999-2000, Sun Systems' flagship servers, which had a selling price of \$500,000 to \$1 million USD dollars, encountered an unacceptably high system failure rate due to SEEs found in the memory cards. It took engineers a year to fully understand and solve the problems. This cost Sun Systems tens of millions of dollars and an enormous number of man-hours in technical debugging and in debriefings with customers. Furthermore, Sun's brand image was damaged and the company was criticized for the poor treatment of their customers.

During the last forty years, scaling of silicon technologies has greatly improved the performance of ICs in terms of power, speed, and integration. However, the continuous scaling means more transistors per unit area, smaller power supply voltage, higher clock frequency, less node capacitance, and more complexity of circuits, all of which make the circuits more vulnerable to SEEs. For example, the strike of a particle usually causes only a Single Bit Upset (SBU) in

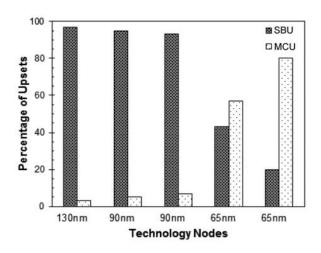

Static Random Access Memories (SRAM) manufactured in less advanced technologies. However, it can cause Multiple Cells Upset (MCU) in advanced technologies. Figure 1.1 shows the trend of SBU and MCU ratios with the scaling of technology nodes in SRAMs [7], illustrating that SEEs can have worse impacts on circuits in modern technologies.

Figure 1.1 Percentage of upsets with the shrinking of technology nodes [7]

Researchers and engineers have been continuously studying the radiation effects in microelectronics and exploring radiation hardening techniques in circuits and systems. Generally, mitigation techniques of SEEs can be classified into three categories: system-level, circuit-level, and fabrication-level [5]. A typical example of system-level approaches is Error-Correcting Codes (ECC), which add extra parity bits to correct erroneous bits in memories [8]. In general, the ECC method is more effective in memory applications. Fabrication-level methods are based on fabrication, which can greatly improve the tolerance of SEEs by changing fabrication processes. Triple-well [9] or quadruple-well structures [10] and Silicon-On-Insulator (SOI) substrates [11] are widely used. Circuit-level designs, which are the focus of this thesis, contain schematic and layout hardening methods. Circuit-level methods have high flexibility and are independent of fabrication processes, since they can be applied to basic cells or blocks, or to whole circuits. Through spatial or temporal redundancy of sensitive nodes or devices, the single event tolerance can be improved

from a schematic perspective. For example, a Dual Interlocked Storage Cell (DICE) was introduced to achieve SEU tolerance by storing two pairs of complementary values instead of one pair [12]. A Quad-node ten transistor cell (Quatro) is another SEU-tolerant storage design, which reduces soft error rate (SER) by 98% compared to its regular counterpart in a 90nm CMOS technology [13]. In the layout-level, node separation and guard rings are broadly used to mitigate SEE [14]. Layout Design Through Error-Aware Transistor Positioning (LEAP) is one of the newest approaches in layout-level, showing 5 times the improvement over the regular layout method in a 180nm CMOS technology [15].

Many methods listed above were proposed to improve the SEU resistance of storage cells in sequential circuits. SET glitches in combinational logic circuits do not necessarily cause failures because of various masking effects [2]. However, studies show that soft errors caused by the SETs in combinational logics can contribute significantly to the overall errors when clock frequencies are in gigahertz range or higher [16]. The traditional methods include, but are not limited to, increasing the transistor size, using guard drains in layout, and using spatial or temporal redundancy. However, the complexity of logic circuits increases the difficulty of finding a universal hardening method. Taking into account the factor of high operating clock frequencies, it is necessary to improve the radiation tolerance of combinational circuits.

## 1.2 Objectives

The overall objective of this thesis is to propose radiation hardening designs at the circuitlevel to reduce soft errors induced by SEEs. Schematic methods and layout methods will be used to improve the radiation tolerance of sequential circuit cells and combinational logic circuits. The approach taken is as follows:

1. Develop a latch that is immune to alpha particles with minimum overhead.

Radiation at ground level may bring soft errors to electronic devices and cannot be ignored. The effectiveness against a particle strike will be evaluated using sophisticated Technology Computer Aided Design (TCAD) simulation tools. A flip-flop chain containing the proposed design will be implemented in a 65nm CMOS Bulk technology test chip. Alpha-particle and heavyion exposures will be performed to verify its capability against ground-level and space-level radiation.

2. Design radiation hardening logic gates based on Cascode Voltage Switch Logic (CVSL) and dynamic logic gates.

Combinational logic circuits are more prone to SETs with high clock frequencies. With the development of high speed processors and devices, reducing or shortening SETs in logic gates is more important than ever. To evaluate the effectiveness of radiation resistance, simulations will be carried out to analyze SET characteristics of reference and proposed designs. The performance of area, power, and delay will also be measured in the 65nm CMOS Bulk technology.

The steps below are followed to accomplish the objectives:

- 1. Study the background of SEEs, including the mechanism of particle radiation, the main sources, and their impacts on sequential and combinational circuits.

- 2. Summarize the current various SEE resilient designs from schematic-level to layout-level.

- 3. Propose a radiation hardening latch and two fault-tolerant logic gates, and analyze their SEE resistance.

- 4. Perform particle incidence simulations by soft error simulators on proposed and previous hardening designs to evaluate their effectiveness of SEU/SET mitigation.

- 5. Build test benches for proposed designs and their counterparts and do simulations using Spectre to compare their area, delay, and power dissipation.

- 6. Design and fabricate a test chip which contains the proposed flip-flop chain. Since charge sharing is more obvious in advanced Bulk technologies, resulting in a lower upset threshold, 65nm Bulk technology is chosen as the fabrication process.

- 7. Implement a test system and carry out alpha and heavy-ion experiments to evaluate the SEU-tolerant performance of the proposed design and its counterpart.

### 1.3 Thesis Organization

Chapter 1 of this study gives the background of radiation and explains the motivation of this thesis. Objectives are also presented in this chapter. Chapter 2 introduces the background of radiation effects and Single Event Effects. Chapter 3 provides a review of the current radiation tolerant designs on sequential and combinational circuits. Chapter 4 presents the proposed hardening latch design and Single Event Upset (SEU) simulations. Chapter 5 introduces the two proposed combinational logic gates and analyzes their radiation hardening performance by using TCAD simulations. Chapter 6 describes the test chip in 65nm CMOS technology and the test system for alpha and heavy-ion experiments. Radiation test results are also analyzed in this chapter. Chapter 7 is the summary and conclusions of the thesis.

#### **CHAPTER 2: RADIATION EFFECTS BACKGROUND**

#### 2.1 SEE Basic Mechanism

As mentioned in chapter 1, Single Event Effects (SEEs) come from an energetic particle strike on an integrated circuit (IC). When striking the semiconductor material, the energetic particle loses energy quickly. Based on Energy Band theory, this energy makes electrons jump from the valence band to the conduction band, so that there are electrons in the conduction band and holes in the valence band. During this process, electron-hole pairs are generated. These generated electrons and holes will be recombined eventually if there is no electric field. However, if this happens in a reverse-biased junction where a high field exists, the depletion layer can help collect carriers through the drift process. Thus, a reverse-biased junction is the most sensitive area of a circuit.

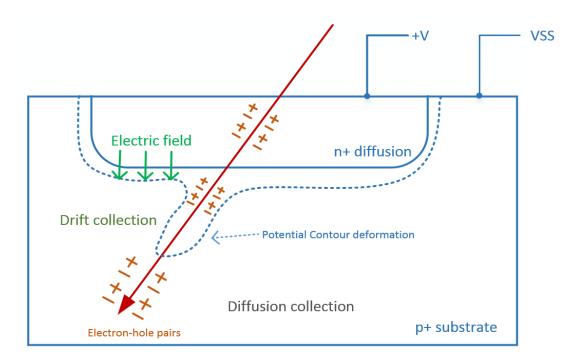

Figure 2.1 Basic mechanism of a strike in a reverse-biased junction

Figure 2.1 details the basic mechanism when a strike happens in a reverse-biased junction[17]. As shown, when the N diffusion connects to Voltage Drain Drain (VDD) and the P substrate connects to Voltage Source (VSS), the reverse-biased junction is formed. The high electric field present in the depletion part is from the N diffusion to the P substrate. According to Baumann's study, at the beginning of the particle striking, a cylindrical trajectory exists whose radius is less than one micron [17]. This cylindrical trajectory is full of electrons and holes. These concentrated electrons and holes neutralize those in the depletion region around the trajectory, and, at the same time, the high electric field helps collect electrons into the N diffusion and holes into the P substrate. Thus, electrostatic potential changes, and potential contour deforms, as shown in Figure 2.1. This funnel-shaped depletion area (termed "field funnel") can also raise the charge collection in return because it extends deeply into the P substrate [18]. After tens of picoseconds, drift collection caused by the electric field is finished, resulting in electrons concentrating in the N diffusion and holes concentrating in the P substrate. From the perspective of the circuit, a current pulse is shown on the node struck. A voltage perturbation can be captured [19], which may change the logic state of this node and cause a soft error. Following the drift process described above, diffusion collection dominates the event. This diffusion process assists the recombination and diffusion of carriers from this area. Nanoseconds after the strike, all carriers are removed and disappear. During the whole process, a current pulse is formed in the struck node.

The incident particle lost its energy when penetrating the silicon material and generating electron-hole pairs. To quantify the damage strength in a semiconductor material from the injection of a charged particle, the terminology LET (Linear Energy Transfer) is used broadly [20]. The definition of LET is the deposited energy per unit length of an incident particle. Due to the differences in injected materials, LET is normalized with the density of the target material. Its unit is MeV·cm<sup>2</sup>/mg.

$$LET = \frac{1}{\rho} \frac{dE}{dL} \tag{2.1}$$

In equation (2.1), E represents Energy with the unit MeV, L is Length with the unit cm<sup>2</sup>, and  $\rho$  is density with the unit mg/cm<sup>3</sup> [21].

In silicon, 3.6eV is needed to generate an electron-hole pair. With the charge of one electron 1.6\*10<sup>-19</sup>C and the density of Si 2.33g/cm<sup>3</sup>, Naseer et al. showed how to transfer the unit MeV·cm<sup>-2</sup>/mg to pC/µm [22], which is also generally used to express the magnitude of LET.

When LET = 1pC/ $\mu$ m, it means that 1pC charge is deposited per unit length ( $\mu$ m), so the deposited electron-hole pairs per  $\mu$ m is  $\frac{1pC/\mu m}{1.6*10^{-19}C}$ . The energy per  $\mu$ m is  $\frac{1pC/\mu m}{1.6*10^{-19}C} \times 3.6eV$ . LET can be obtained after normalized by the density of silicon,  $\frac{1pC/\mu m}{1.6*10^{-19}C} \times 3.6eV \div 2.33g/cm^3$ .

$$\frac{{}^{1}pC}{{}^{\mu}m} \Leftrightarrow \frac{{}^{1}pC}{{}^{\mu}m} \times 3.6eV \div \frac{{}^{2.33}g}{{}^{c}m^3} = 96.57MeV \cdot cm^2/mg \tag{2.2}$$

According to equation (2.2), 97 MeV·cm<sup>2</sup>/mg LET value can be expressed as 1pC/ $\mu$ m. In general, an approximation of 1pC/ $\mu$ m = 100 MeV·cm<sup>2</sup>/mg is used for convenience. From the definition of LET, we know that LET is related to the energy and mass of incident particles, and the materials struck by the particles [6].

#### 2.2 Sources of Radiation

There are three radiation sources for SEE in space: particles in the earth's radiation belts called Van Allen Belts, particles from solar activities, and particles from galactic cosmic rays. On earth, the neutron particles in the atmosphere and alpha particles in packaging materials can also induce soft errors via indirect or direct ionization [23]. Alpha particles, heavy ions, neutrons, and protons will be introduced in the following sections.

#### 2.2.1 Alpha Particles

The first soft errors of SEE discovered on earth were caused by alpha particles in packaging materials of chips. These soft errors had a negative impact on the function of circuits [24].

Alpha is a doubly ionized helium atom (He<sup>2</sup>), which is the product emitted by the emissive decay of radioactive materials. An alpha particle consists of two neutrons and two protons, so that it carries a charge of +2, and its mass is 4 times that of a hydrogen atom. In a package of integrated circuits, there are small amounts of radioactive isotopes, such as uranium and thorium. When they decay, high energetic alpha particles are generated with the energy varying from 3.95 to over 9 MeV [24]. It has already been verified that alpha particles with 5 MeV or less can pass through silicon and cause upsets in dynamic memories. Alpha particles cannot travel far and a piece of paper can stop them easily. For example, polyimide can block alpha particles, so it is often used in fabrication processes.

For this thesis, alpha-particle radiation experiments were carried out at the University of Saskatchewan. An americium-241 5.5MeV alpha source was placed on top of a chip whose top lid was removed before the experiments. This alpha source has 2.5uCi activity and 4.61\*10<sup>7</sup>a/cm<sup>2</sup>/h emissivity.

#### 2.2.2 Heavy Ions

Heavy ions are those charged particles heavier than protons and their atomic numbers are higher than 1, including charged helium, carbon, and neon ions. They have more than one unit of electric charge, for example, carbon-12, neon-22, calcium-45, iron-56, uranium-238, and krypton 84. Through direct ionization, a heavy ion strikes circuit devices, generating abundant electron-hole pairs along with the ionic track. The Linear Energy Transfer of heavy ions is from 1 MeV·cm- $^2$ /mg to 100 MeV·cm $^2$ /mg [25].

The very first observation of soft errors in space was from the radiation of heavy ions [26], opening the door to the study of space radiation effects and radiation hardening technologies for space semiconductors. After that, for convenience, heavy ions were generated by accelerators, which could simulate space radiation environments and be used for radiation experiments on earth. Accelerators allow various types of ions, from Ar to U, to generate different LET beams of heavy ions. These accelerators speed up charged ions to high-level velocity, almost near the speed of light. Using accelerators for radiation experiments on earth helps to control the radiation environment, and to choose the types, energy, and intensity of ions. Repeated experiments and a large number of trials become possible via this method, which advances the study of radiation hardening.

For this thesis, we did heavy-ion experiments at the HI-13 Tandem accelerator, China Institute of Atomic Energy (CIAE), Beijing, China.

#### 2.2.3 Neutrons

Neutrons are the product of nuclear fusion, nuclear fission, radioactive decay, or other reactions. Neutrons and protons, which will be introduced in the next section, constitute the nuclei of atoms. A neutron has the same mass as a proton, but it has no charge. Since they are not blocked by the coulomb barrier, neutrons can react with most nuclei. At sea level, about 95% of cosmic rays are neutrons [27]. Neutrons in the atmosphere are the end-products when the atmosphere interacts with cosmic rays [25]. The intensity varies with altitude, position in the geomagnetic field, and solar magnetic activities [28].

Neutrons cause soft errors in electrical devices through indirect ionization. One type of neutron radiation damage occurs when high-energy neutrons (10MeV-1GeV) in space react with the nuclei of silicon and generate ions, which can then produce electron-hole pairs via direct ionization. Another type is low-energy or thermal neutrons in space which react with boron (<sup>10</sup>B)

in packaging materials, generating a lithium ion and an alpha particle [23]. Boron is presented in doped polysilicon, doped wafers, and borophosphosilicate glass (BPSG). When struck by neutrons, boron becomes unstable and loses energy through fission.

#### 2.2.4 Protons

A proton is a subatomic particle with a positive charge of 1.6\*10<sup>-19</sup>C. There are abundant protons existing in space environments. Protons make up 87% of galactic cosmic rays. The energy of these protons is usually around 1GeV but sometimes is as great as 10<sup>12</sup> MeV. In addition, particles generated during solar activities include many highly energetic protons. The energy of protons trapped in the Van Allen Radiation Belts varies from several keV to several hundreds of MeV [25].

Protons can affect electronic circuits by direct and indirect ionization. When proton energy is lower than 10 MeV, protons can directly ionize the silicon materials, generating electron and hole pairs, in the same manner as alpha particles and heavy ions [29]. When energy is higher than 20 MeV, protons act like neutrons via indirect ionization by generating secondary charged particles to induce soft errors [30].

# 2.3 SEU (Single Event Upset)

Digital logic circuits can be divided into two categories depending on the logic function: sequential circuits and combinational circuits. Sequential circuits have memory, which means that not only current inputs but also previous inputs can affect the current outputs. However, in combinational circuits, outputs at any time depend only on the present inputs. Single Event Effects behave differently in these two kinds of circuits. The main components in sequential logic circuits are storage cells, such as flip-flops (FFs) and latches, which can store the data. If an energetic

charged particle strikes a latch, the sensitive node may collect enough charge and upset its state, causing a SEU to occur. For combinational logic circuits, there are no memory-like structures. The collected charge will cause a transient change of current and voltage in the nodes, which we define as a SET in the circuits.

When a charged particle strikes a sensitive node, a current pulse will be generated and may flip the state of the node. We quantify this behavior using critical charge ( $Q_{crit}$ ). Critical charge is defined as the minimum quantity of charge required to upset a circuit node.

$$Q_{crit} = V_{DD} \times C_{node} \tag{2.3}$$

Equation (2.3) expresses critical charge after first-order approximation. Critical charge depends on the voltage and capacitance of the node. Based on analysis, critical charge is a contributing factor in determining the SER of a circuit. Higher restoring strength and a larger load help increase critical charge and improve radiation resistance [31]. It is easy to conclude that reduced node capacitance and lower power supply voltages in advanced technologies lower the critical charge and introduce more challenges for mitigating the SEEs.

The following is an example showing the mechanism of how a SEU occurs in a D-type Flip Flop (DFF) storage cell.

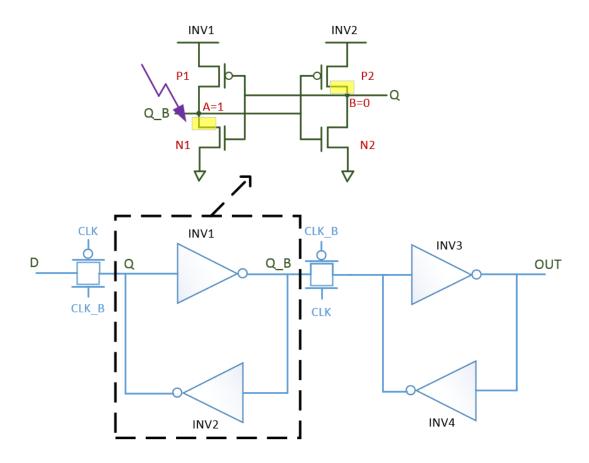

In Figure 2.2, a DFF consists of two transmission gates and two latches. A back-to-back inverter pair (INV1 & INV2 or INV3 & INV4) is the basic storage element of the latch. The transmission gate contains one Positive-Channel Metal Oxide Semiconductor (PMOS) and one Negative-Channel Metal Oxide Semiconductor (NMOS). When the clock is logic low, the first transmission gate opens, and input data is written into the first latch, and stored in the first back-to-back inverter pair. During this time, the second transmission gate is closed, and the second back-to-back inverter pair keeps the previous data. After a short time, the rising edge of the clock triggers the DFF to output the current data. The first transmission gate closes and the second one opens

when the clock changes from logic low to logic high. At this moment, data in the first latch will be passed to the second latch and be available at the node OUT. Consequently, after the rising edge of the clock, the DFF completes a reading cycle and exports data.

Figure 2.2 DFF and SEU analysis

A SEU occurs in a latch at the hold state, when the clock transition is not considered. For example, the first back-to-back inverter pair is analyzed in the state A=1 and B=0. In this state, Q=0 and Q\_B=1, transistors P1 and N2 are open, and P2 and N1 are closed. A reverse-biased P-N junction is the sensitive region for a SEE, so the Drains of N1 and P2 are the most sensitive areas of this latch (marked with yellow). If a strike happens in one of these two Drains (assume the Drain of NMOS), a current pulse will occur. Electrons concentrate in the Drain of N1 and generate a negative pulse in node A. The open transistor P1 drives node A to power VDD by offering a

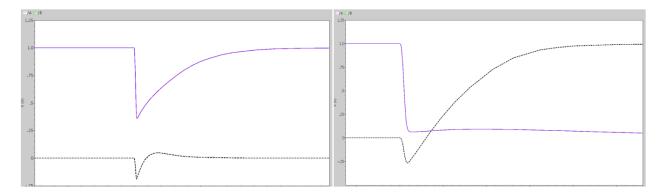

restoring strength. In the left illustration in Figure 2.3, the purple solid line represents the voltage in node A, and the black dashed line shows the voltage in node B. When the restoring transistor (P1) is strong enough, state 1 in node A can be recovered and will not change the data stored in the latch. If the restoring current from P1 fails to balance the current generated by the strike, which means the collected charge exceeds the critical charge of node A, the state of node A will change from 1 to 0 (the right illustration in Figure 2.3). Because of the feedback structure in the latch, logic low in node A will close N2 and open P2, resulting in node B changing from 0 to 1. Thus, an upset happens in this latch. This is the basic mechanism of a SEU in memory cells.

Figure 2.3 Voltage waves with time of storage nodes A and B in low and high collected charges

In general, the possibility for SEUs in memories is called "cross section." The cross section is the result of the total error numbers of a circuit divided by the fluence of incident ions. Fluence is the total particle numbers passing through a unit area. Cross section also refers to a sensitive area and is expressed in cm<sup>2</sup>. Thus, in many papers, the cross section versus LET curve depicts the device's failure rate at various radiation conditions. Another term, Failure-In-Time (FIT), is used to show the failure rate of devices, which is the number of errors per one billion hours.

### 2.4 SET (Single Event Transient)

Unlike sequential circuits, there are no feedback structures in combinational circuits. The current pulse caused by charge collection can generate a voltage glitch and propagate along the critical path in a combinational circuit. Only when the glitch is captured by a storage element, such as a register, can a SET generate a soft error, which is a SEU in this case.

In fact, a SET in a circuit will not necessarily cause a failure because of various masking mechanisms, namely logical masking, temporal masking, and electrical masking [2].

Logical masking happens when there is no existing path for the SET to spread, and the fault will be masked. We can take a two-input NOR gate in a combinational path as an example, where if the two inputs are all logic high, the output will be logic low. When a particle strikes one of the inputs changing its value from high to low, the output of this NOR gate will remain logic low, which means that the SET is eliminated by logic masking. Only when particles strike both inputs simultaneously and change their values to logic low, will the output change from logic low to high.

Temporal masking means that a SET in a combinational path will not induce a functional fault to the whole circuit, if the register following this path does not sample this SET. For a positive-edge-triggered flip-flop, data must be stable for some time before the rising edge of the clock. This time is called setup time. If the input changes during the setup time, incorrect data will be captured and cause a setup violation. The time after the rising edge of the clock during which data must remain unchanged is called hold time. A hold violation happens when incorrect data is latched during this time. If a SET propagates along a combinational path and reaches a register during the setup time, or a SET happens in logics inside registers, this SET will cause a SEU [32]. In deep sub-micron processes, the SET pulse width in digital logics can be hundreds of picoseconds, while the clock speed rises steadily from megahertz to gigahertz. Thus, it is relatively easier for SET pulses to be captured by registers.

If a SET pulse in an input is shorter than the delay of the logic gate, it will be masked and cannot cause any soft error. This occurrence is called electrical masking. The allowable noise voltage on the input of a gate is determined by noise margin. A higher noise margin means larger noise is allowed by the logic gate, and thus, the logic gate has better noise resistance. For example, if the output of the first level of a combinational logic path is struck by an energetic charged particle, voltage perturbation caused by charge collection will appear, and this voltage perturbation is the input of the second level of this logic path. Next, consider the output of the second-level gate. If the voltage perturbation is lower than its noise margin, the SET will be masked through an electrical masking mechanism. With CMOS technology scaling, gate delay becomes shorter, so narrower SETs can propagate through combinational paths, which poses a challenge in mitigating soft errors in advanced technologies. In addition, Massengill et al. report that SETs in combinational chains can result in pulse broadening, depending on specific circuit configurations and technologies [33]. The research on SETs in combinational circuits attracts much attention due to the challenging factors.

This chapter details the basic mechanism of SEEs when a charged particle strikes semiconductor materials. A brief introduction of radiation sources is included. Following that, SEUs in sequential circuits and SETs in combinational circuits are explained using typical examples. In the next chapter, SEE mitigation techniques will be reviewed and some typical radiation hardening designs will be presented.

#### **CHAPTER 3: CURRENT SEE TOLERANT DESIGNS**

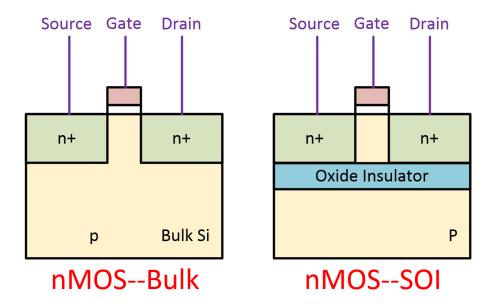

Currently Bulk and SOI are the two main silicon CMOS technologies. Figure 3.1 is a simplified diagram showing the difference between Bulk NMOS and SOI NMOS transistors. Silicon-On-Insulator (SOI) adds a layer of insulation oxide under the transistor's Source and Drain regions. Through reducing the sensitive volume, SOI technologies can effectively reduce the charge collection, and hence, has higher radiation resistance than Bulk technologies [5][11]. In addition, SOI technologies have reduced parasitic node capacitances, which shortens parasitic delay and lowers dynamic power consumption. Most importantly, transistors with SOI technologies are free from latch-up due to the complete isolation from device to device. All these advantages make SOI technologies an attractive option for the silicon industry to reduce SERs in electronic circuits.

Figure 3.1 Bulk NMOS and SOI NMOS

With the continuing study of radiation effect mechanisms in Bulk and SOI technologies, mitigation methods have been developed not only at the circuit-level but also at the layout-level.

Section 3.1 provides a brief introduction of basic SEE-tolerant designs. Section 3.2 details the current circuit-based hardening designs, including Triple Modular Redundancy (TMR), Guard-Gate, DICE, and Quatro. Section 3.3 discusses layout-based mitigation theories (e.g., charge sharing and pulse quenching) and corresponding radiation hardening layout designs.

### 3.1 Basic Mitigation Approaches

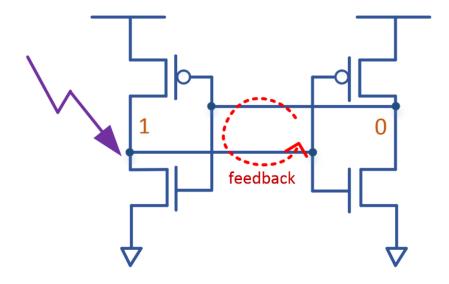

Initially, researchers focused on SEU-tolerant designs for storage cells because clock frequencies were not very fast and SETs in combinational circuits were not significant with lower operating frequency. Generally, two back-to-back inverters are the storage elements in most of the storage cells, as shown in Figure 3.2. The occurrence of a SEU depends on two factors: the recovery time of the struck node voltage and the propagation time for the SET pulse to propagate through the feedback loop. For example, if a strike happens in the Drain of an "OFF" NMOS, there will be a current transient in the struck node, which will cause a negative voltage pulse. The "ON" PMOS of this node will eventually balance the voltage pulse and drive the node back to logic 1. At the same time, the voltage pulse will propagate to the other node through the feedback structure and upset the state if the pulse width is long enough. The time of this propagation is called cell feedback time. In cross-coupled inverters, cell feedback time can be simplified as Resistor-Capacitor (RC) delay. The competition between a SET's recovery time and cell feedback time determines whether a SEU happens [5]. The shorter RC delay a memory cell has, the more susceptible to SEUs it will be.

Figure 3.2 Feedback structure in a back-to-back inverter pair

Early mitigation methods focused on these two parameters by either decreasing the SET recovery time or increasing the cell feedback time. Decreasing the SET recovery time can be realized by increasing the size of transistors in the inverters, where larger transistors can provide a larger driving current to recover the struck node. However, using this method causes extra area and power consumption. To increase the cell feedback time, resistance or capacitance can be added into the feedback loop, as shown in Figure 3.2 [34]. Adding capacitance at critical nodes can also increase the critical charge. Resistors, diodes, transistors, or capacitors are used in different places of the feedback path to increase SEU resistance[35][36][37]. The cell feedback time method reduces SEUs in memory cells at the price of larger area, more power consumption, and slower operating speed. With the need for high speed circuits, new approaches and elegant designs are required.

## 3.2 Redundancy-based Mitigation Methods

More complex mitigation methods involve the redundancy of information instead of simply increasing the critical charge of storage nodes. For example, reproducing data spatially or

temporally can help reduce the probability of SEEs. Multiple copies of inputs or outputs and differential inputs or outputs are also used to implement this concept. The next three sections will introduce four advanced designs which fully take advantage of this concept.

#### 3.2.1 TMR

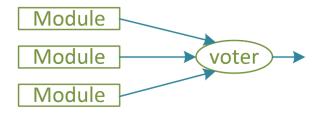

Triple Modular Redundancy (TMR) has a straightforward structure and is widely used in commercial and space applications. Lyons et al. were first to apply the TMR method in radiation hardened equipment [38]. Figure 3.3 shows the basic form of the TMR method, where a majority voter is added to vote on the outputs from three identical modules.

Figure 3.3 Illustration of the TMR principle

In sequential circuits, the module can be an unhardened latch or a regular DFF. All latches or flip-flops share the same clock and input data. If a strike hits one of the latches or flip-flops and causes a SEU, the majority voter can filter this SEU and output the correct data from the other two unaffected modules. The majority voter can be built by using combinational logics, so TMR is SEU-free and susceptible to SETs. The disadvantages of the TMR approach are the large area and power consumption, which can be  $3\sim4$  times greater than a single module.

#### 3.2.2 Guard-Gate

A guard-gate is also called a Muller C-element. Figure 3.4 shows the basic structure of a guard-gate. When input A equals input B, the guard-gate behaves the same as an inverter. When

input A differs from input B, the output of the guard-gate is in a high impedance state and maintains its previous value [39].

Figure 3.4 Schematic of a guard-gate [40]

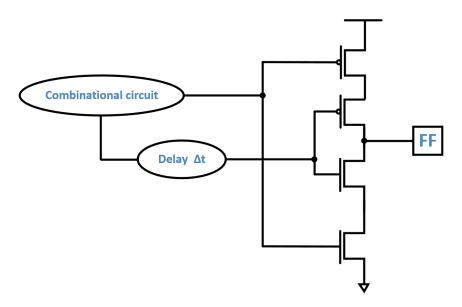

The application of guard-gates in combinational circuits is illustrated in Figure 3.5. With inputs A and B replaced by the normal and delayed outputs of a combinational circuit, the guard-gate can remove the SET pulses in this combinational circuit if the SET pulse width is shorter than the delay unit, and output correct data to the following flip-flop. In other words, the guard-gate can mask the SET pulses whose width is shorter than  $\Delta t$  delay [40].

Figure 3.5 Guard-gate used in a combinational circuit

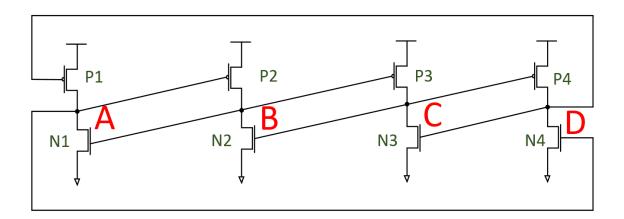

#### 3.2.3 DICE

A Dual Interlocked Storage Cell (DICE) is a spatial redundant design, which has been used broadly since it was first proposed in 1996 [12]. Figure 3.6 shows the structure of a DICE cell. It has 4 storage nodes (A, B, C, and D) instead of 2 for redundancy purposes. In these four nodes, B and D have the complementary value of A and C. For example, assume nodes A and C are logic low (0), and B and D are logic high (1). Then, transistors N1, P2, N3, and P4 are "ON," whereas P1, N2, P3, and N4 are "OFF." The Drain of the P1 transistor is sensitive to a SET. If a particle strikes node A, a positive voltage pulse will occur at this node. The "ON" transistor N1 will drive node A to suppress this positive pulse, which may turn off P2 and turn on N4. Node B will be floating and retain its value when P2 and N2 are OFF. If N4 is ON, there will be a competition between P4 and N4 to determine the voltage level on node D. Even if N4 dominates, which drives the voltage on node D from high to low and turns N3 off, node C will retain its value and be floating in this worst case. Finally, once the positive SET pulse disappears, all the storage nodes in the DICE cell will restore their values. In conclusion, the DICE structure is immune to a SEU if only a single node is affected.

Figure 3.6 Dual Interlocked Storage Cell (DICE) [12]

In order to write into the DICE, at least two nodes need to be accessed simultaneously to achieve a successful write operation. Compared to the TMR structure, a DICE has smaller area and power dissipation. It has no static current path between power and ground during static mode. Another advantage of the DICE is that the transistors do not have to be specifically sized. Based on these benefits, the DICE structure is commonly used as a SEU-tolerant storage element. However, there are also some drawbacks for this design. The most obvious disadvantage is the occurrence of a SEU when two of the nodes are struck simultaneously. Researchers have made efforts to solve this problem. One example is the combination of the DICE structure and the guardgate, as shown in Figure 3.7, which is also called a 4-TAG latch. Radiation experiments have shown that no error occurred even at 175 MeV·cm²/mg LET value in the AMI 0.5μm process [41].

Figure 3.7 DICE latch with 4 guard-gates [41]

## 3.2.4 Quatro

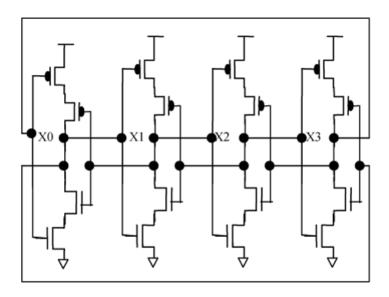

The Quad-node ten transistor cell (Quatro or Quatro-10T) is another popular SEU-tolerant storage cell design [13]. This Quatro-10T cell was proposed firstly as a hardened memory cell of

SRAM. It can also be used as a latch cell in sequential circuits. Figure 3.8 shows the structure of a Quatro-10T cell.

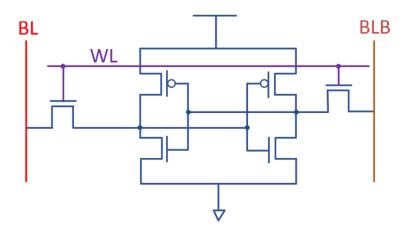

Figure 3.8 Quatro-10T cell [13]

With the symmetrical structure, the Quatro cell stores differential data in 4 nodes (X1, X2, X3, and X4). X1 and X4 have the same value, as do X2 and X3. This Quatro-10T cell is immune to a positive pulse in node X1 or X2, and immune to a negative pulse in node X3 or X4. For example, assume X1 is logic low (0) and X2 is logic high (1). If a positive pulse occurs in X1, the "ON" transistors P2 and P4 will be turned off, resulting in nodes X3 and X2 floating and unchanged. If node X3 has a negative SET pulse, the "ON" transistors N1 and N3 will be turned "OFF," resulting in X1 and X4 floating and maintaining their values. However, a negative pulse in node X1 or X2 and a positive pulse in node X3 or X4 may cause SEUs. For example, the negative SET pulse in node X2 will turn on both P1 and P3, causing competitions in nodes X1 and X4. If the SET pulse is large enough, the competitions will flip the Quatro cell and a SEU will occur. Appropriate size of transistors can reduce the competitions and help the Quatro cell improve its robustness.

It is reported that the Quatro-10T cell has a larger noise margin and lower leakage current than a DICE cell, and the SER of a Quatro-10T cell SRAM is reduced by 98% compared to the unhardened standard 6T cell, as shown in Figure 3.9 [13].

Figure 3.9 Regular 6T cell

## 3.3 Layout-based Mitigation Methods

With technologies scaling, shrinking of transistors results in a higher probability of Single Event Multiple Nodes Upset (SEMU). A SEMU caused by a single particle strike was observed firstly in SRAMs [42]. Charge sharing theory is proposed to explain this phenomenon. Researchers have made great efforts to reduce charge sharing, and hence, SEMUs as well as SERs. However, it becomes more challenging in the most advanced technologies, such as 40nm and 28nm technologies. On the other hand, some researchers started to use the mechanism of charge sharing to mitigate the single event effects, which led to layout-based hardening design techniques in addition to circuit-based mitigation approaches. In the next section, the mechanisms of charge sharing and pulse quenching will be detailed first, and then, several layout-based mitigation methods will be introduced, including node separation, guard rings, and Layout Design Through Error-Aware Transistor Positioning (LEAP).

#### 3.3.1 Charge Sharing and Pulse Ouenching

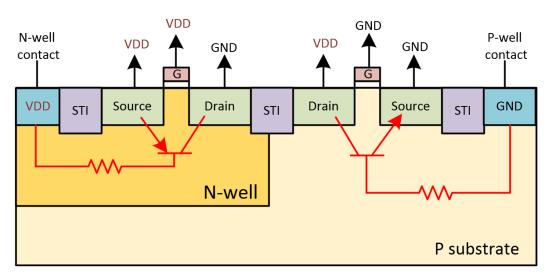

Besides diffusion and drift process, parasitic bipolar effect plays a significant role during charge collection. Figure 3.10 shows the cross section of both PMOS and NMOS transistors. If an energetic charged particle strikes the n-well when the Source of the PMOS is logic high and the Drain is logic low, electron-hole pairs will be generated, and electrons will be concentrated around the n-well because of the electric field between the n-well and p substrate. These collected electrons will decrease the potential of the n-well. The P-N junction between the Source and the n-well will be forward biased, and the P-N junction between the Drain and the n-well will be reverse biased. The lateral parasitic bipolar in the n-well will be turned on. For this bipolar transistor, the Drain is acting as the Collector, the n-well is the Base, and the Source is the Emitter. The amplification of this bipolar transistor will increase the Drain voltage, resulting in a positive pulse. In the NMOS device, the mechanism is the same as in the PMOS device. However, because the voltage perturbation of the P substrate is not so obvious as that of the n-well, the parasitic bipolar effect in the NMOS is not as significant as in the PMOS. With the shrinking of the feature size of transistors, the shorter the gate length, the larger the bipolar current gain [43].

Figure 3.10 The cross section of CMOS transistors and the illustration of the parasitic bipolar transistors

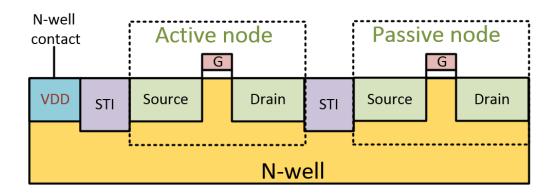

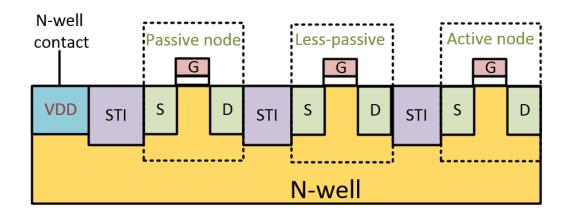

When the distance between a hit device and neighbouring devices is large, such as in the less advanced technologies, generated carriers only concentrate on the vicinity of the hit device. However, technologies scaling results in less charge needed to represent a logic state, and generated carriers can affect adjacent devices due to the diffusion process. Amusan et al. studied the charge sharing between an active node and the passive node of adjacent MOS devices in the same well, as shown in Figure 3.11 [14].

Figure 3.11 Diagram of an active node and passive node affected by charge sharing

Because of the diffusion process and parasitic bipolar mechanism in the n-well caused by a charged particle, the parasitic bipolar transistor of the passive PMOS can be turned on. In PMOS devices, the parasitic bipolar effect in the passive node is dominant over the diffusion process. The existence of the bipolar transistor will increase the total collected charge in both the active and passive nodes. If there is only a single node collecting these carriers, some generated carriers will be recombined in the end. However, because of the absence of a well-like structure and relatively stable voltage of the p substrate, diffusion is still the main mechanism of charge sharing in NMOS devices. In both PMOS and NMOS transistors, increasing the distance between the active and passive nodes can help to reduce charge sharing and the effect on adjacent transistors. Transistors in separated n-wells have a lower possibility of charge sharing [14]. The existence of the electric

field between an n-well and a p substrate can isolate them, and thus, charge sharing is not prominent in the separated wells.

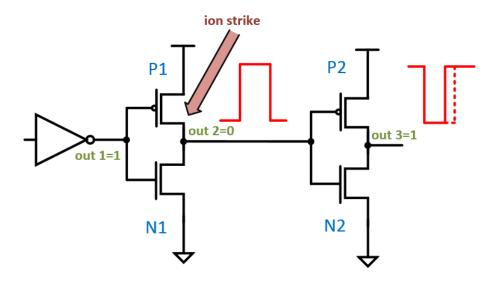

As to SETs in combinational circuits, pulse quenching is referred to as the effect of charge sharing on SET pulse width. The pulse quenching effect was introduced to describe the phenomenon that SET pulse widths become shortened in certain cases at high LET values [44].

Figure 3.12 Illustration of the pulse quenching effect in a chain of inverters

In Figure 3.12, there is an inverter chain including three inverters. Assume that out1 is logic high, out2 is low, and out3 is high. Transistors P1 and N2 are "OFF," whereas N1 and P2 are "ON." Because of the reverse-biased junction in the Drain of P1, this node is sensitive to SETs. When an ion strikes the Drain of P1, there will be a positive voltage pulse in out2. This pulse will propagate downstream and generate a negative pulse in node out3. Ahlbin et al. observed the interesting phenomenon that the pulse width at out3 is shorter than that at out2 [44]. Through simulations, they found that it is caused by the charge sharing between P1 and P2. At the node out3, there are two voltage transitions. One is a high to low transition from the propagation of the SET at out2. The other is a low to high transition due to charge sharing. When the positive SET pulse generated at out2 propagates to out3, it will turn off transistor P2 and turn on N2. Then the "OFF" transistor

P2 is prone to charge collection. Especially when P1 and P2 are placed closely, the generated charge will be shared between transistors P1 and P2. Carriers diffuse from P1 to P2 and cause a low to high transition at the node out3. This low to high transition reduces the pulse width from out2 to out3 and pulse quenching occurs. Two requirements determine the occurrence of pulse quenching. The first one is the possibility of charge sharing. In less advanced technologies, the distance between transistors is relatively large, so pulse quenching is not as significant as that in advanced technologies. The second one is that the time of charge sharing from the hit device to the adjacent device must be close to the time of a SET propagating from the previous gate to the current gate. If the propagation delay of a SET from one gate to another is much larger than the charge sharing period, pulse quenching will not occur. In conclusion, it is "delayed charge sharing collection" that causes the quenched SETs.

Based on the mechanism of charge sharing and the description of the pulse quenching mechanism, the following layout-based mitigation methods are introduced to reduce charge collection and to improve the radiation tolerance of circuits.

## 3.3.2 Node Separation

To reduce the SER of circuits, the most direct method at the layout-level is increasing the node distance between two sensitive transistors, which can decrease the possibility of charge sharing. However, this method becomes less attractive with the scaling of transistors because of the large area overhead. A study using a 90nm Bulk CMOS technology shows that charge sharing may occur among multiple PMOS transistors by an angular particle strike because of the n-well potential variation, which means that node separation to 2µm is not enough to suppress SEMU and to decrease SER [45].

An alternative of node separation is interdigitating transistors, which is to place the less-affected nodes between two sensitive nodes [14]. As shown in Figure 3.13, the less-passive transistor is located between an active node and a passive node, so the distance between the active node and passive node can be enlarged. Since the less-passive node is not that sensitive to collected carriers, this node has less chance to experience upset. This method can diminish the SER without using too much area. It is more effective for NMOS transistors than PMOS transistors, because charge sharing caused by the parasitic bipolar effect is not obvious in NMOS transistors, and interdigitation enlarges the distance resulting in mitigation of the diffusion effect.

Figure 3.13 Interdigitating of transistors

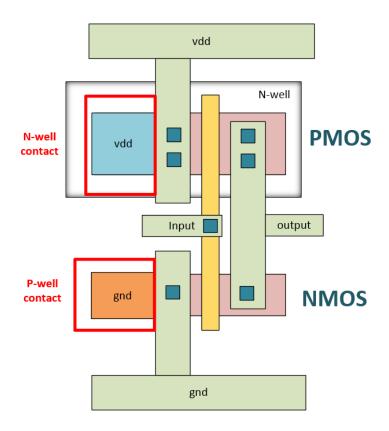

#### 3.3.3 Well Contact and Guard Ring

As discussed above, in PMOS devices, the main mechanism of charge sharing is the parasitic bipolar effect. Maintaining the voltage of the n-well is an effective method to reduce charge sharing and soft errors. Figure 3.14 is the layout diagram of an inverter with well contacts. A well contact is a high doping diffusion area that maintains well potential. Reducing the distance of a well contact and the struck node can diminish the resistance of the parasitic bipolar transistor, resulting in decreasing the time of potential drop and speeding up the recovery of the well voltage. A guard band is another type of well contact located among PMOS devices to extend horizontal well

contacts. It can also prevent potential perturbation. Simulations in a 130nm technology proved that guard bands could reduce soft errors by 97% in PMOS transistors and by 35% in NMOS transistors at a LET of 40 MeV·cm²/mg [14]. The mitigation effect is different in PMOS and NMOS transistors because the well contacts and guard bands are used to decrease the contribution of the parasitic bipolar effect, which is not dominant in NMOS devices. Heavy-ion experiment results show that guard bands and high-density well contacts can remove 70% of SETs which are longer than 1ns [46].

Figure 3.14 Well contacts in PMOS and NMOS transistors

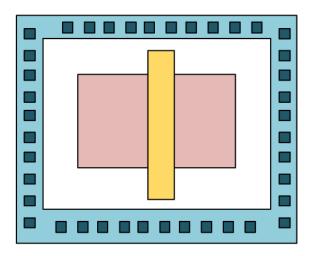

Another design more effective than a guard band is a guard ring. Figure 3.15 shows a transistor surrounded by a guard ring. Besides preventing well potential from collapse, a guard ring can prevent a Single Event Latch-up (SEL). A SEL can enable a direct current path between power and ground rails due to a particle strike. Heavy ion experiment results indicated that the guard ring

structure did not show any improvement over SEUs in DICE circuits, but it was more effective in decreasing the collected charge in passive PMOS transistors than in NMOS transistors with normal and 60° strikes [45]. Compared to redundancy methods, area overhead for guard rings or guard bands is not too high. Well contacts and guard rings are still effective methods to improve radiation tolerance, especially for PMOS devices.

Figure 3.15 Diagram of a guard ring outside of a transistor [45]

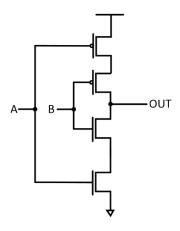

## 3.3.4 Layout Design Through Error-Aware Transistor Positioning

Kelin et al. proposed Layout Design Through Error-Aware Transistor Positioning (LEAP) in 2010 [15]. It is a creative layout-based radiation hardening design, differing from traditional layout mitigation technologies, such as guard bands or guard rings. The basic principle of LEAP is charge cancellation via the layout method to reduce the possibility of multiple node upsets.

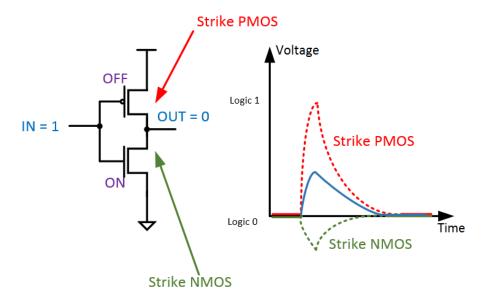

Figure 3.16 Charge cancellation when striking both Drains of the PMOS and NMOS in an inverter

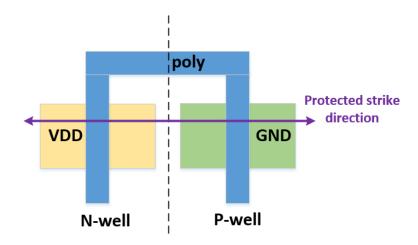

Take a CMOS inverter as the example in Figure 3.16. Because of the existence of an electric field at a P-N junction, electrons will concentrate in N diffusion if an ion hits the Drain of the NMOS, resulting in a voltage drop. Holes will concentrate in the P diffusion if an ion hits the Drain of the PMOS, resulting in a voltage rise. When the input of this inverter is logic high, the output will be logic low. The red dashed line shows that there is a positive voltage pulse in node OUT when an ion strikes the PMOS. The green dashed line indicates that there is a negative voltage pulse in the node OUT when an ion strikes the NMOS. Because the Drain of the PMOS is reverse-biased and the Drain of the NMOS is forward-biased, this PMOS is more sensitive for a particle strike than the NMOS. Thus, the amplitude of the positive voltage pulse is larger than that of the negative pulse. If a particle strikes both the PMOS and NMOS simultaneously, these positive and negative pulses can cancel each other and reduce the pulse at the node OUT (the blue solid line). The principle of the LEAP layout design is to place the Drains of the PMOS and NMOS close to each other, which have opposite effects for a particle strike, as shown in Figure 3.17. The purple

line indicates the horizon which is the protected strike direction, because striking both Drains of the PMOS and NMOS can reduce the SET pulse magnitude of the node.

Figure 3.17 Layout of an inverter using LEAP principle

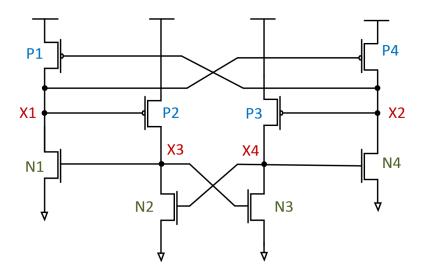

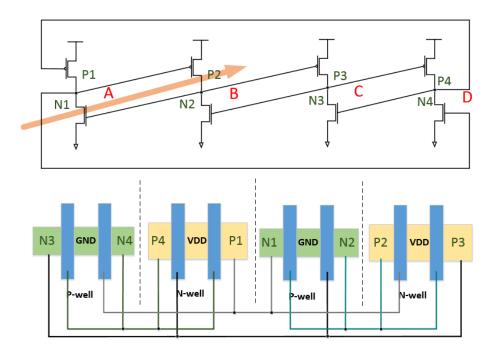

Kelin et al. chose the DICE cell to implement the LEAP technique because the DICE is a reliable design for SEUs but is vulnerable to SEMUs [15]. Figure 3.18 shows the schematic and layout diagram of a DICE cell using the LEAP layout hardening technology. If the states of A, B, C, D are 1, 0, 1, 0, respectively, P1, N2, P3, N4 are "ON," and N1, P2, N3, P4 are "OFF." Node A will drop if an ion strikes the Drain of N1. This negative pulse will turn off N4 and turn on P2, resulting in contention between P2 and N2. This contention will reduce the current of P3, leaving node C weakly driven by P3. Node D will be floating. After a short time, node A will recover because of P1's driving and the recombination of carriers. Thus, the DICE cell is immune to a SEU. However, if the ion strikes in the direction of the orange line, N1 and P2 will be hit simultaneously. In addition, the voltage of node B will change from low to high instead of the intermediate competition state caused by an N1 hit. The state change of both nodes A and B can cause this DICE cell to upset.

Figure 3.18 LEAP-DICE schematic and layout diagram [15]

Since the DICE cell is not immune to multiple node upsets, a LEAP layout design is proposed to solve this problem. In Figure 3.18, all 8 transistors in a DICE cell are aligned horizontally. For example, placing N2 between N1 and P2 separates these nodes from each other, and cancels the total effect of multiple node upsets. If N2 and P2 are hit simultaneously, the magnitude of the voltage pulse at node B is reduced, which is the same result shown in the inverter, as described in Figure 3.16. Different from the mechanism of N2 and P2, which is called "direct SET suppression," "indirect SET suppression" occurs when N1 and N2 are struck together [15]. The negative pulse created in node A by a particle strike can turn on P2, and then, cause a contention in node B, which may increase the voltage of B. At the same time, striking N2 can generate a negative pulse in node B. This negative pulse will suppress the increasing voltage above and drive B back to its original state. In this way, striking N1 and N2 together is beneficial for the DICE because of charge cancellation. For that reason, N2 is placed between N1 and P2. The other transistors are placed in

a similar way to reduce the overall effect of a SEMU. Besides the horizontal direction, all the other angled directions can be protected from a SEMU. In addition, the structure of P-N-P-N wells is better than P-P-N-N wells because the former structure provides additional isolation to reduce charge sharing. By using the LEAP layout design, the DICE cell is not only immune to SEUs, but also has a lower probability of single event multiple node upsets.