# STUDY OF SINGLE EVENT TRANSIENT ERROR MITIGATION

A Thesis Submitted to the

College of Graduate and Postdoctoral Studies

in Partial Fulfillment of the Requirements

for the degree of Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon

By

Hao Xie

©Hao Xie, July/2017. All rights reserved.

# PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering University of Saskatchewan 57 Campus Drive, Saskatoon, Saskatchewan Canada, S7N 5A9

## ABSTRACT

Single Event Transient (SET) errors in ground-level electronic devices are a growing concern in the radiation hardening field. However, effective SET mitigation technologies which satisfy ground-level demands such as generic, flexible, efficient, and fast, are limited. The classic Triple Modular Redundancy (TMR) method is the most well-known and popular technique in space and nuclear environment. But it leads to more than 200% area and power overheads, which is too costly to implement in ground-level applications. Meanwhile, the coding technique is extensively utilized to inhibit upset errors in storage cells, but the irregularity of combinatorial logics limits its use in SET mitigation. Therefore, SET mitigation techniques suitable for ground-level applications need to be addressed.

Aware of the demands for SET mitigation techniques in ground-level applications, this thesis proposes two novel approaches based on the redundant wire and approximate logic techniques.

The Redundant Wire is a SET mitigation technique. By selectively adding redundant wire connections, the technique can prohibit targeted transient faults from propagating on the fly. This thesis proposes a set of signature-based evaluation equations to efficiently estimate the protecting effect provided by each redundant wire candidates. Based on the estimated results, a greedy algorithm is used to insert the best candidate repeatedly. Simulation results substantiate that the evaluation equations can achieve up to 98% accuracy on average. Regarding protecting effects, the technique can mask 18.4% of the faults with a 4.3% area, 4.4% power, and 5.4% delay overhead on average. Overall, the quality of protecting results obtained are 2.8 times better than the previous work. Additionally, the impact of synthesis constraints and signature length are discussed.

Approximate Logic is a partial TMR technique offering a trade-off between fault coverage and area overheads. The approximate logic consists of an under-approximate logic and an overapproximate logic. The under-approximate logic is a subset of the original min-terms and the overapproximate logic is a subset of the original max-terms. This thesis proposes a new algorithm for generating the two approximate logics. Through the generating process, the algorithm considers the intrinsic failure probabilities of each gate and utilizes a confidence interval estimate equation to minimize required computations. The technique is applied to two fault models, Stuck-at and SET, and the separate results are compared and discussed. The results show that the technique can reduce the error 75% with an area penalty of 46% on some circuits. The delay overheads of this technique are always two additional layers of logic.

The two proposed SET mitigation techniques are both applicable to generic combinatorial logics and with high flexibility. The simulation shows promising SET mitigation ability. The proposed mitigation techniques provide designers more choices in developing reliable combinatorial logic in ground-level applications.

### ACKNOWLEDGEMENTS

First, I would like to thank my supervisor, Dr. Chen. Without his valuable instruction and inspiration, this thesis would not have been completed. Also, I am grateful for his helpful guidance on how to become a real academic and how to think critically. His encouragement and patience helped me overcome numerous difficulties through my Master's program.

Dr. Adrian Evans gave me a great deal of technical and academic advice. His passion about research deeply inspired me. His profound knowledge of radiation hardening greatly benefited my research project.

I would also like to acknowledge my committee members Professor Gokaraju, Professor Yang and Professor Bui for the constructive feedback and suggestions which made my thesis better in many ways.

Finally, all my success would be impossible without the unconditional love and support from my family.

# CONTENTS

| Pe | rmiss                    | on to Use                                                                                                                                                                                                                                                                                        | i                                                                        |

|----|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Ał | ostrac                   |                                                                                                                                                                                                                                                                                                  | ii                                                                       |

| Ac | know                     | edgements                                                                                                                                                                                                                                                                                        | iv                                                                       |

| Co | onten                    |                                                                                                                                                                                                                                                                                                  | v                                                                        |

| Li | st of [                  | ables                                                                                                                                                                                                                                                                                            | vii                                                                      |

| Li | st of l                  | gures                                                                                                                                                                                                                                                                                            | iii                                                                      |

| Li | st of A                  | bbreviations                                                                                                                                                                                                                                                                                     | ix                                                                       |

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | view of SET Mitigation Techniques       1         Package and Chip Level       1         Core and Module Levels       1         Cell and Process Levels       1         Block Level       1         2.4.1       Coding Techniques       1         2.4.2       Redundant Logic Techniques       1 | <b>1</b><br>1<br>6<br>8<br>10<br><b>12</b><br>13<br>14<br>15<br>16<br>17 |

| 3  | Low<br>3.1<br>3.2        | Signature Based Method to Estimate Controllability and Observability       1         3.1.1 Signature       1         3.1.2 Controllability       1         3.1.3 Observability       1         Redundant Wires       1         3.2.1 Logic Implications       1                                  | <b>19</b><br>19<br>21<br>22<br>24<br>24<br>24                            |

|   |                                                 | 3.2.3 Circuit Modification                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |  |  |  |

|---|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

|   | 3.3                                             | Algorithm for Evaluating and Selecting Logic Implications                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                 |  |  |  |

|   |                                                 | 3.3.1 Identification                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                 |  |  |  |

|   |                                                 | 3.3.2 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                 |  |  |  |

|   |                                                 | 3.3.2.1 Evaluation of Zone A                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                 |  |  |  |

|   |                                                 | 3.3.2.2 Evaluation of Zone B                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                 |  |  |  |

|   |                                                 | 3.3.2.3 Evaluation of Zone C                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                 |  |  |  |

|   |                                                 | 3.3.2.4 Evaluation of Overlap Between Implications                                                                                                                                                                                                                                                                                                                                                                                                             | )                                 |  |  |  |

|   |                                                 | 3.3.3 Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                 |  |  |  |

|   |                                                 | 3.3.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                 |  |  |  |

|   | 3.4                                             | Simulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                 |  |  |  |

|   |                                                 | 3.4.1 Implication Identification                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                 |  |  |  |

|   |                                                 | 3.4.2 Protective Effect Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                 |  |  |  |

|   |                                                 | 3.4.3 Protection Results                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                 |  |  |  |

|   |                                                 | 3.4.4 Impact of Synthesis Constraints                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                 |  |  |  |

|   |                                                 | 3.4.5 Impact of Signature Length                                                                                                                                                                                                                                                                                                                                                                                                                               | )                                 |  |  |  |

|   |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                 |  |  |  |

|   | 3.5                                             | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I                                 |  |  |  |

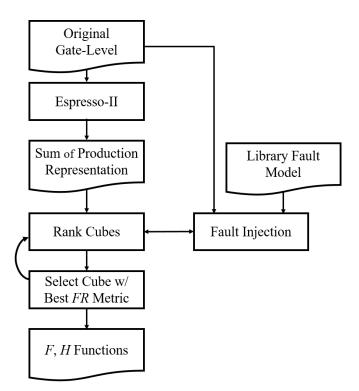

| 4 | New                                             | Approximate Logic based Approaches for Synthesis of Redundant Combina-       53         al Logic for Selective Fault Tolerance       53         Fault Model and Evaluation Method       54         Proposed Algorithm       55         Simulation Results       59                                                                                                                                                                                             | <b>3</b><br>4<br>5<br>9           |  |  |  |

| 4 | <b>New</b><br>toria<br>4.1<br>4.2               | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model60                                                                                                                                                                                                                     | <b>3</b><br>4<br>5<br>9<br>0      |  |  |  |

| 4 | <b>New</b><br>toria<br>4.1<br>4.2               | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model604.3.2Simulation Results with SET Fault Model60                                                                                                                                                                       | <b>3</b><br>4<br>5<br>9<br>0      |  |  |  |

| 4 | <b>New</b><br>toria<br>4.1<br>4.2               | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model604.3.2Simulation Results between Fault Models60                                                                                                                                                                       | <b>3</b><br>4<br>5<br>9<br>0<br>0 |  |  |  |

| 4 | <b>New</b><br>toria<br>4.1<br>4.2               | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model604.3.2Simulation Results with SET Fault Model604.3.3Comparing Results between Fault Models604.3.4Effect of Logic Sharing on Fault Tolerance62                                                                         | <b>3</b> 4 5 9 0 0 2              |  |  |  |

| 4 | <b>New</b><br>toria<br>4.1<br>4.2               | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model604.3.2Simulation Results between Fault Models60                                                                                                                                                                       | 34590024                          |  |  |  |

| 4 | New<br>toria<br>4.1<br>4.2<br>4.3<br>4.4<br>5um | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model604.3.2Simulation Results with SET Fault Model604.3.3Comparing Results between Fault Models604.3.4Effect of Logic Sharing on Fault Tolerance624.3.5Results Prediction64Conclusions65mary, Conclusion and Future Work66 | 3459002456                        |  |  |  |

|   | New<br>toria<br>4.1<br>4.2<br>4.3               | Approximate Logic based Approaches for Synthesis of Redundant Combina-<br>al Logic for Selective Fault Tolerance53Fault Model and Evaluation Method54Proposed Algorithm55Simulation Results554.3.1Simulation Results with SA Fault Model604.3.2Simulation Results with SET Fault Model604.3.3Comparing Results between Fault Models604.3.4Effect of Logic Sharing on Fault Tolerance624.3.5Results Prediction64Conclusions64                                   | 34590024566                       |  |  |  |

# LIST OF TABLES

| 3.1 | Observability of Nodes in Example Circuit                                | 23 |

|-----|--------------------------------------------------------------------------|----|

| 3.2 | Implication Lookup Table                                                 | 31 |

| 3.3 | Results of Identification Algorithm                                      | 45 |

| 3.4 | Results of Evaluation Algorithm                                          | 47 |

| 3.5 | Protection Results                                                       | 50 |

| 3.6 | Impact of Synthesis Constraints                                          | 51 |

| 3.7 | Impact of Vector Size on Quality of Results                              | 52 |

| 4.1 | Logic Cubes for Example Circuit                                          | 56 |

| 4.2 | Results after First Round                                                | 58 |

| 4.3 | Summary of SA and SET Results for Benchmark Circuits ( $N_{max} = 400$ ) | 63 |

# LIST OF FIGURES

| 1.1  | 1 Charge generation and collection phases in a reverse-biased junction caused by the passage of a high-energy particle.     |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.2  | passage of a high-energy particle.    2      An air shower created by the collision between a primary cosmic particle and a |  |  |  |

| 1,4  | molecule in the air.                                                                                                        |  |  |  |

| 1.3  | Three intrinsic masking mechanisms                                                                                          |  |  |  |

| 1.4  | Prediction of soft error rate against clock frequency[1]                                                                    |  |  |  |

| 2.1  | Summary of SET mitigation techniques                                                                                        |  |  |  |

| 2.2  | Triple Modular Redundancy                                                                                                   |  |  |  |

| 2.3  | The structure of SOI technology                                                                                             |  |  |  |

| 2.4  | Basic structure of EDAC code approach implementation                                                                        |  |  |  |

| 2.5  | The basic structure of the approximate logic technique                                                                      |  |  |  |

| 3.1  | Example circuit with random generated signatures                                                                            |  |  |  |

| 3.2  | Example circuit with implications                                                                                           |  |  |  |

| 3.3  | Netlist manipulation to insert redundant wires                                                                              |  |  |  |

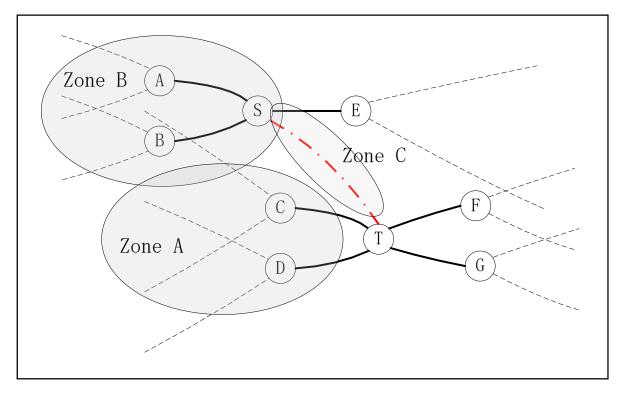

| 3.4  | Zones for protection effect evaluation                                                                                      |  |  |  |

| 3.5  | Example of new gates in Zone C                                                                                              |  |  |  |

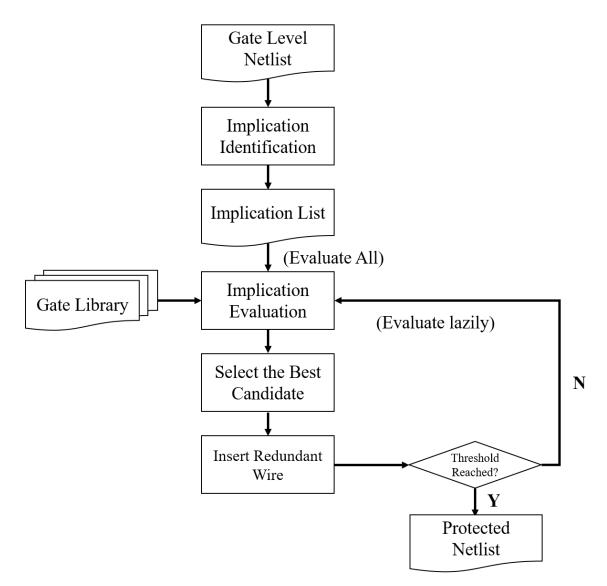

| 3.6  | High-level Algorithm Flow.    43                                                                                            |  |  |  |

| 3.7  | Failure rate reduction for benchmark \$71348                                                                                |  |  |  |

| 3.8  | Failure rate reduction for benchmark S1488.49                                                                               |  |  |  |

| 4.1  | Approximate Logic Functions                                                                                                 |  |  |  |

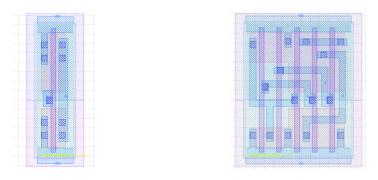

| 4.2  | Layout of INV and XOR Gate                                                                                                  |  |  |  |

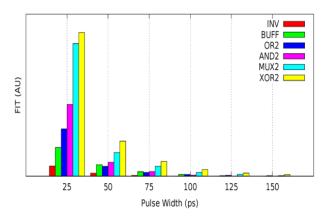

| 4.3  | Transient Sensitivity of 28nm Gates                                                                                         |  |  |  |

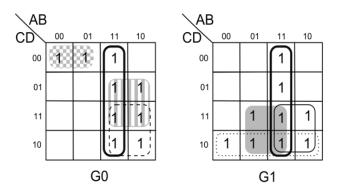

| 4.4  | Karnaugh Map Examples                                                                                                       |  |  |  |

| 4.5  | High-Level Algorithm Flow                                                                                                   |  |  |  |

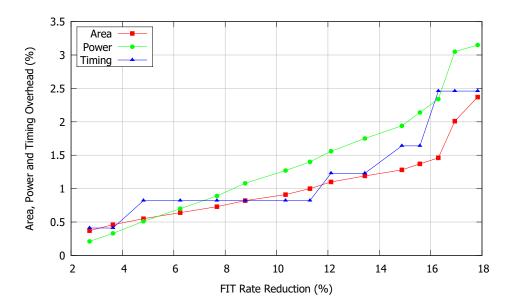

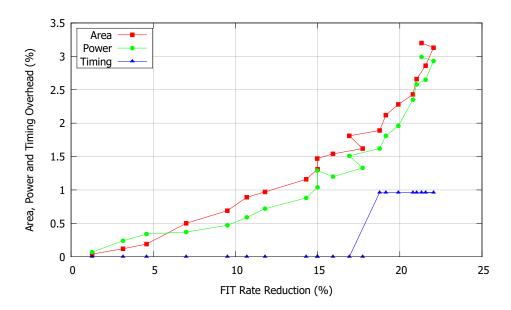

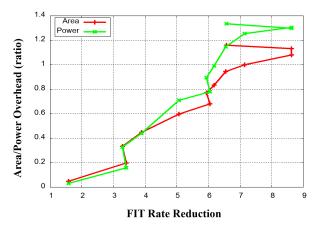

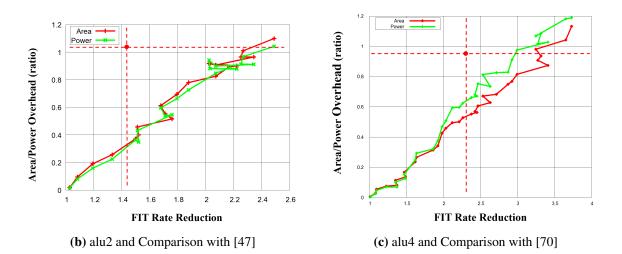

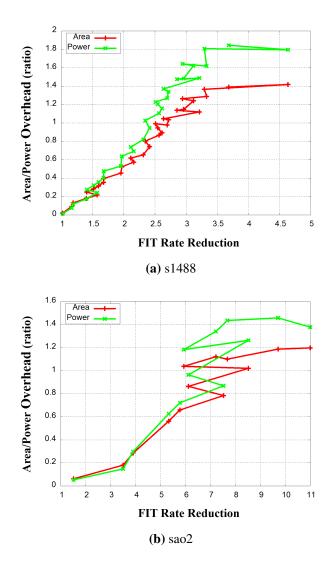

| 4.6  | Area, Power Overheads vs FIT Reduction Results with SA Fault Model (SA) 61                                                  |  |  |  |

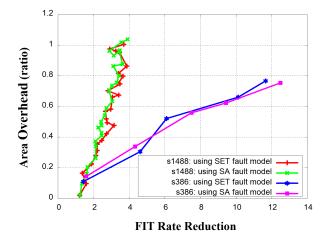

| 4.7  | Area, Power Overheads vs FIT Reduction Results with SET Fault Model 62                                                      |  |  |  |

| 4.8  | SET Masking Effect of Redundant Logic Generated Using SA Fault Model (s386                                                  |  |  |  |

|      | and s1488)                                                                                                                  |  |  |  |

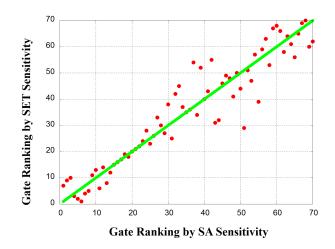

| 4.9  | Per Gate - Fault Model Correlation (sao2)                                                                                   |  |  |  |

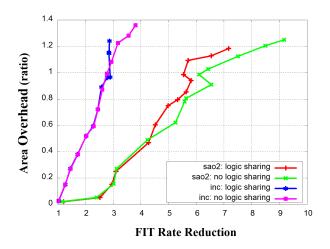

| 4.10 | Effect of Logic Sharing $(F, H)$ for sao2 and inc                                                                           |  |  |  |

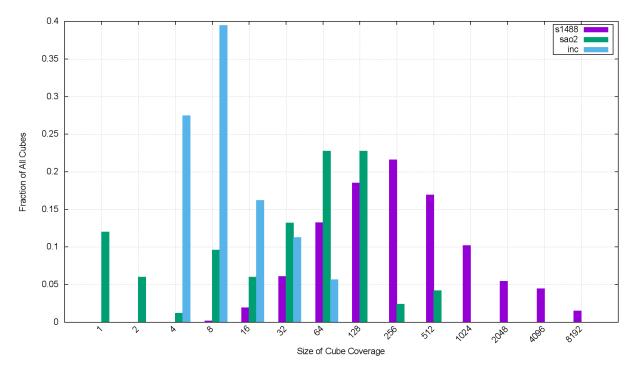

| 4.11 | Cube Size Distribution for sao2, inc and s1488                                                                              |  |  |  |

# LIST OF ABBREVIATIONS

| BDD  | Binary Decision Diagram                                              |  |  |

|------|----------------------------------------------------------------------|--|--|

| CEC  |                                                                      |  |  |

| CED  | Concurrent Error Detection                                           |  |  |

| CPU  | Central Processing Unit                                              |  |  |

| DRAM | Dynamic Random-Access Memory                                         |  |  |

| EDAC | Error detection and correction                                       |  |  |

| EPP  | Error Propagation Probability                                        |  |  |

| FIT  | Failure In Time, one FIT is equivalent to one failure in one billion |  |  |

|      | hours                                                                |  |  |

| FR   | Fault Reduction                                                      |  |  |

| GMR  | Generalized Modular Redundancy                                       |  |  |

| IC   | Integrated Circuit                                                   |  |  |

| MA   | Mandatory Assignment                                                 |  |  |

| NP   | A complexity class used to describe certain types of decision        |  |  |

|      | problems in computational complexity theory                          |  |  |

| QoR  | Quality of Result                                                    |  |  |

| SA   | Stuck-At                                                             |  |  |

| SAT  | Satisfiability                                                       |  |  |

| SEE  | Single Event Effect                                                  |  |  |

| SER  | Soft Error Rate                                                      |  |  |

| SET  | Single Event Transient                                               |  |  |

| SEU  | Single Event Upset                                                   |  |  |

| SIA  | Semiconductor Industry Association                                   |  |  |

| SOI  | Silicon On Insulator                                                 |  |  |

| SOP  | Sum Of Product                                                       |  |  |

| SRAM | Static Random-Access Memory                                          |  |  |

- SRAM Static Random-Access Memory

- TMR Triple Modular Redundancy

# CHAPTER 1 INTRODUCTION

### 1.1 Introduction

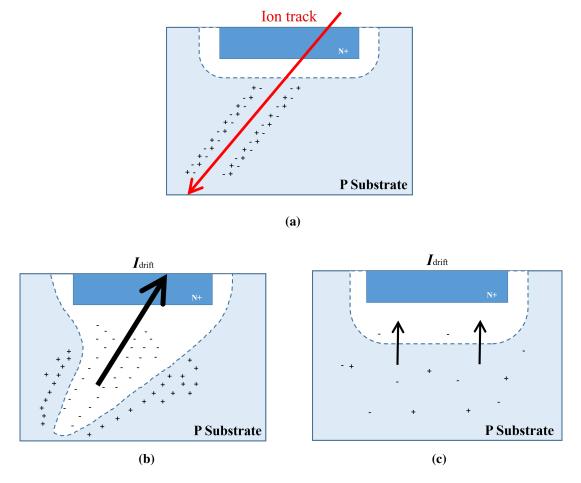

When an integrated circuit (IC) is operating in a radiation environment, it is vulnerable to a strike from various energetic particles, such as protons, neutrons, alpha particles and other heavy ions. As a high-energy particle penetrates through IC materials, extra electrons and holes are generated along the track due to the ionization effect, as shown in Figure 1.1a. These excess carriers will then be collected by the sensitive node nearby in two stages, ion drift (Figure 1.1b) and ion diffusion (Figure 1.1c), and if the charge collected exceeds the charge threshold of the given node, the state of the node is erroneously altered. These adverse interactions between high-energy particles and semiconductor material are denoted as Single Event Effects (SEEs).

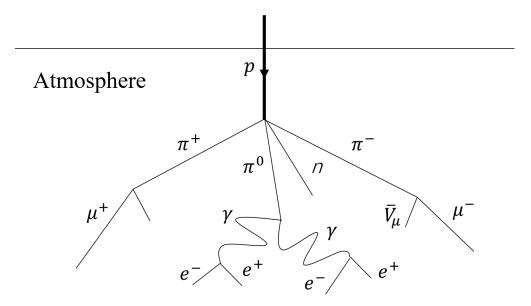

Cosmic rays are one of the major radiation sources. They are high-energy particles originating from a sun particle event or other astrophysical processes outside the solar system. Cosmic rays have two phases called primary cosmic rays and secondary cosmic rays. Primary cosmic rays are the original product of astrophysical processes which consist of protons (85%), alpha particles (14%) and other heavier nuclei (1%)[2]. They exist primarily in the space environment. In 1975, Binder et al. identified that primary cosmic rays were the main culprit of single event errors observed in a satellite integrated circuits [3]. This is the first published observation of SEEs. Secondary cosmic rays are a product of collisions that occur when primary cosmic rays enter the atmosphere. The interaction between high-energy particles and molecules in the air generate an air shower of various secondary lighter particles, including neutrons, pions, positrons and muons, as shown in Figure 1.2[4]. The flux of secondary particles has been discovered to be dependent on

**Figure 1.1:** Charge generation and collection phases in a reverse-biased junction caused by the passage of a high-energy particle.

both altitude and longitude[5]. The strength of the radiation generally increases with the altitude and longitude. In 1995, Taber and Normand summarized and released a series of experimental results of SEEs at different flight altitudes, and indicated that the range of upset rates on avionics overlaps with the range measured in low-earth orbit [6].

Unpurified packaging materials are another radiation source. The radioactive elements residing in the unpurified materials were found occasionally to emit alpha particles. Alpha particles are +2 particles consisting of two protons and two neutrons. They have a relatively low penetration depth and can be stopped by a few centimeters of air. However, the alpha particles emitted by unpurified packaging materials can easily impact the chips within the package and cause soft errors like SEEs. The first observation of SEEs caused by unpurified materials dates back to the late 1970s in Intel's

**Figure 1.2:** An air shower created by the collision between a primary cosmic particle and a molecule in the air.

new Dynamic Random-Access Memory (DRAM) chips [7, 8].

In addition, facilities like nuclear reactors and particle accelerators are artificial radiation sources. Nuclear reactions mainly produce gamma radiation and neutron particles. Particle accelerators produce high-energy protons and electrons which will interact with each other and create radioactive secondary particles. Thus, sensors and control circuits operating in these facilities are highly susceptible to a variety of radiation effects.

To summarize, primary cosmic rays are the major threat to circuits operating in a space environment. Within the atmosphere, primary cosmic particles interact with molecules in the air, forming a cascade of lighter particles. Even though the energy of these secondary particles is attenuated with the distance of penetration, there are still some energetic particles able to reach the surface of the Earth. Thus, devices located from the ground up to flight altitudes are all affected by secondary cosmic rays. Additionally, unpurified packaging materials are an insidious source of radiation, threatening both ground and space devices. In facilities like nuclear reactors and particle accelerators, radioactive particles produced during operation are also a potential threat to nearby devices.

Non-destructive SEEs, which are called soft errors, are classified into two categories based

on the area struck by radiation particles: Single Event Upset (SEU) and Single Event Transient (SET). If an energetic particle strikes the sensitive nodes of an element in Dynamic Random-Access Memories (DRAMs), Static Random-Access Memories (SRAMs), latches or flip-flops, and the induced voltage or current transient changes the state of the element, this incorrect state will be preserved until the next writing operation. This phenomenon is referred to as an SEU. Based on the result of a strike, an SEU error can be categorized into one of four groups: masked, corrected, detected or silent [9, 10]. Without protection, the damage of a silent error may vary from a single undesired operation to as serious as a system lockup.

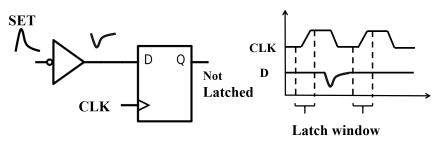

On the other hand, if a radiation particle strikes a sensitive node in combinatorial logic, the formed transient current will propagate along the sensitive paths and finally be latched by sequential elements. This phenomenon is referred to as an SET. For a long time, however, an SET was considered to be a less challenging single event effect than an SEU due to three intrinsic masking mechanisms found in combinatorial circuits, which can inhibit an SET from being latched and which are described later.

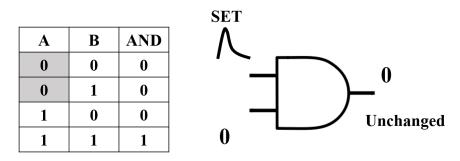

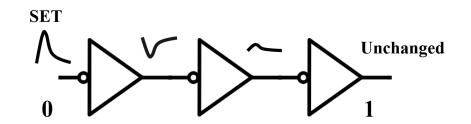

- **Logical Masking:** Logical masking is a mechanism utilizing the concepts of dominant value and don't-care in logical operations. If it is the case that when an input of a gate holds a particular value (1 or 0), and it follows that the output of the gate is always either 1 or 0, notwithstanding the values of other side inputs, then this specific value is denoted as the dominant value and the status of the dominated side inputs are denoted as don't-care. For example, if an SET pulse propagates to an input of an AND gate, but another input occupies the dominant value (0 in this case), the output of the gate will not be affected; therefore, the SET will be masked (Figure 1.3a).

- **Electrical Masking:** Each gate has a logic transition time. If the width of an SET pulse is shorter than this time, the amplitude of the pulse will be attenuated while passing through the gate. Then, this reduced amplitude will decrease the pulse width, and eventually, the pulse will fade away as it propagates, as shown in Figure 1.3b. Generally, pulses wider than the transition time will not be attenuated, pulses shorter than half the time will be eliminated and pulses in-between will be attenuated to some extent [11].

(a) Logical masking

(b) Electrical masking

(c) Temporal masking

Figure 1.3: Three intrinsic masking mechanisms.

**Temporal Masking:** When an SET arrives at the input of a memory element, its pulse has to cover completely the latching window so that this SET can be latched. In other words, it has to arrive before the setup time and last until the hold time; otherwise it will be stopped (Figure 1.3c). Buchner et al. proposed the concept of "window of vulnerability" to define this time interval when the memory element is sensitive to SET pulses [12].

Thus, for an SET induced error to be latched, the radiation particle must strike the sensitive area of a node and collect sufficient charge to generate an SET pulse of sufficient duration and amplitude. There also must exist an active path allowing the pulse to reach storage, and the storage must be within the window of vulnerability to latch the error. Thus, the probability of SET induced soft error  $P_{SET}$  can be evaluated by Equation 1.1 [13, 14]

$$P_{SET} = (Flux) \times \sum_{i=1}^{n} A_i Q_i P_{prop} \times T_{mask}$$

(1.1)

where Flux is the flux of high-energy particles, which is independent of technologies,  $A_i$  is the proportion of sensitive area of a node i,  $Q_i$  is the probability that sufficient charge at node i can be collected to form an SET pulse with sufficient amplitude and duration to survive from the electrical masking,  $P_{prop}$  is the probability that the SET pulse can propagate to the storage cells, and  $T_{mask}$  is the probability that the SET is latched.

#### **1.2** Motivation

Moore's Law projects that the performance of an integrated circuit will double approximately every 18 months. This proved to be accurate for almost 50 years until the technology scaled down to 22nm around 2012 [15] and progress was close to saturation. This performance improvement resulted technically from the scaling of transistors. As feature size shrinks, transistor density of a chip increases, which allows integrating more functional units into one chip; the power consumption and transition delay also decreases, allowing the emergence of high performance and low energy IC designs. While these advancements enormously contributed towards the wide application of digital devices in a variety of fields, scientists also observed a rising susceptibility to radiation effects, including SETs.

As technology scales, a single transistor's physical area shrinks, which dramatically increases the density of transistors on a chip. In 1978, the Intel 8086 processor, which gave rise to the famous x86 architecture, was first introduced. It was the most advanced processor at that time, was produced with a 3000nm process, and had an average of 88 transistors per square mm. Today, the Intel Broadwell-EP Xeon 22-core processor with the 14nm process has reached an astounding 15.8 million transistors per square mm. Meanwhile, the smaller spacing between devices leads to lower critical charge threshold and larger sensitive area per unit transistor. The increases in transistor density and sensitive area increase  $A_i$  in Equation 1.1, and thus, makes integrated circuits more susceptible to SET effects.

At the same time, technology scaling is weakening combinatorial logic's natural immunity. As briefly introduced in Section 1.1, three intrinsic masking mechanisms inhibit the SET effect. However, technology scaling, especially energy and frequency scaling, has shown varying degrees of influence on these masking mechanisms. First, the scaling of operating frequencies, i.e., more state transitions per unit time, increases the chance that an SET pulse is latched, and consequently, reduces the effect of temporal masking. Electrical masking is also weakened by technology scaling. SET pulses narrower than the unit transition time are likely to be attenuated during propagation or to be filtered thoroughly before latching. However, technology scaling leads to faster transition time on each unit, which in turn allows more SET pulses to propagate through the data path. Experiments have indicated that modern circuit designs cannot rely on natural electrical masking any longer [16]. Unlike temporal and electrical masking, logical masking is rarely influenced by scaling. This is because logical masking is independent of the technology process and is only relevant to a circuit's own logic.

According to the evaluating model represented by Equation 1.1, the SET error rate is mainly determined by five factors: Flux,  $A_i$ ,  $Q_i$ ,  $P_{prop}$  and  $T_{mask}$ . Flux and  $P_{prop}$  are independent of technology scaling. The ratio of sensitive area  $A_i$  increases with a transistor's dimension scaling and density increase. Meanwhile, the weakening of electrical and temporal masking exacerbate  $Q_i$  and  $T_{mask}$ . Overall, all these changes have rendered increasing SET error rates as technology advances.

Decades of experiment and observation have confirmed the aforementioned deduction. The first SET observation dates back to the early 80's [17] when unit dimensions of main technologies were within a range of microns. During that period, the charge deposit phenomenon was only observed occasionally on limited parts of circuits with exposure to relatively high radioactive energies, and thus, it was not regarded as a major threat by most academics [18]. Following the development of fast circuits (up to 100Mbps) in the 90's, the increasing SET errors became a growing concern to developers of space applications. In 1997, Buchner et al. made the predic-

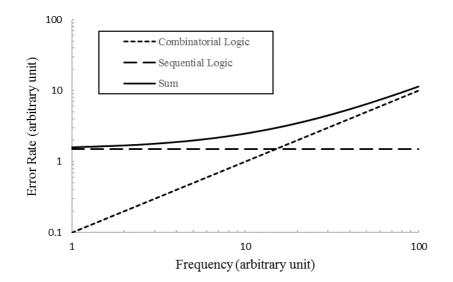

tion that SET errors will dominate soft errors as frequency increases, as shown in Figure 1.4[1]. Subsequently, an increasing number of studies set out to reveal the characteristics and the trends of SETs, and they all reported the growing threat of SETs in reliability issues[19, 20, 21, 22]. In 2009 and 2010, Sridharan et al. conducted a study to evaluate the soft error on a supercomputer and the surprising result was that the detected error rate on the unprotected devices reached as high as 350 per minute[23]. As of today, the Semiconductor Industry Association (SIA) has clearly identified transient errors in combinatorial logic as a major threat and a huge challenge to robust system design in the future[24].

**Figure 1.4:** Prediction of soft error rate against clock frequency[1].

## 1.3 Objectives

Well aware of radiation problems including SETs, researchers have put in great effort to make electronic devices resistant to errors caused by high-energy particles, a field known as radiation hardening. Originally, radiation hardening was mainly aimed towards devices operating in space or in high altitude flight, and around nuclear reactors and particle accelerators, where high-energy particles are more intense and reliability is strictly required[25]. Radiation hardening techniques involve all aspects of design, process and testing. Redundancy is a hardening theory widely utilized in component and system design, e.g., Triple Modular Redundancy (TMR). There are also

special processing techniques, like Silicon On Insulator (SOI), that are used to make the sensitive area resistant to collecting charges. Additionally, space and nuclear-related projects may enclose their critical circuits in a shield made of lead or other dense materials. With these technologies, radiation-tolerant devices can resist radiation thousands of times stronger than ground-level commercial devices can [26, 8, 27]. However due to the considerable time and effort required to develop and test a radiation-tolerant design, the performance of radiation-hardened devices is typically two to four generations behind that of commercial devices.

With technology scaling, the sensitive area of a transistor increases, and the critical charge for both combinatorial and sequential logic decreases, which makes new electronic devices more susceptible to SEEs. Without protection, advanced computer chips can easily have an error rate in excess of 50,000 FIT/chip, where one FIT (failure in time) is equivalent to one failure in one billion hours. This rate is higher than the sum of all other reliability issues [24]. The increasing threat makes radiation tolerance a necessity for designs even in applications at ground level. Previously, ground-level design was mainly focused on protecting memory and registers, because they utilize a significant portion of chip area and have dominant error rates. However, as discussed above, with technology and frequency scaling, combinatorial logic errors may eventually dominate, negating the effort of strategies focused on hardening conventional memory[13, 28]. Thus, developers need to reallocate resources in both directions in order to achieve a balanced protecting effect in future designs.

In order to withstand severe radiation environments, space and nuclear related designs have to expend tremendous area, power and delay overheads on radiation hardening. For example, the classic TMR needs more than 200% in area and power overheads as well as two extra layers of delay. It also takes considerable extra time for developing and testing. Nevertheless, all these demanding requirements may not be suitable for ground-level applications. First, ground-level environment is not as severe as environment in space or around nuclear reactors. Then, instead of pursuing extreme reliability, ground-level applications focus more on efficiency in radiation protection. A balance between the protecting effect and overheads needs be achieved. Furthermore, ground-level commercial applications are responsive to the newest technology, and thus, there is limited time for developing and testing the application of radiation hardening techniques. As a result, a lightweight SET mitigation technique with the following features is the most desirable solution for ground-level radiation applications:

- **Flexible trade-off:** The trade-off between the protecting effect and cost overheads is adjustable. The adjustable trade-off allows designers to achieve different SET coverage under various design constraints.

- High efficiency: The technique can achieve remarkable coverage with relatively low overheads.

- **General purpose:** The technique should be applicable to most combinatorial circuits. The generality makes it possible to integrate the technique into automatic design flow with which developers are able to utilize the mitigation technique without a complete knowledge of design.

- **Fast computation:** The technique should be able to find a result close to optimal within reasonable computing time. The fast computation guarantees the feasibility of the technique.

In this thesis, I will propose two generic and high efficient SET error mitigation techniques based on the redundant theory. Since the techniques are aimed at generic combinatorial logic, they can be utilized to most of digital designs. Additionally, the mitigation techniques protect the target design by enhancing the logical masking effect, which is not affected by the technology or radiation environment. The effectiveness of the proposed algorithms is tested by fault injection simulations.

#### **1.4 Thesis Organization**

Chapter 1 introduces the basic concepts around Single Event Transient effects. As technology advances, the growing trend of SET errors is explained, which is the motivation for designing soft error mitigation techniques for ground-level applications. The author then presents the objectives of this thesis based on the special demands of ground-level applications.

Chapter 2 reviews state-of-the-art SET mitigation techniques. The techniques are classified based on different levels of design granularity, ranging from the chip level to the process level.

At the package and chip levels, shielding and package purifying are briefly introduced. At the core and module levels, Triple Modular Redundancy and its extensions are discussed. At the cell and process levels, techniques focusing on increasing the resupplying current and limiting charge collection are discussed. Three main block level mitigation approaches, i.e., coding, redundant logic and rewiring, are demonstrated and their features and limits are discussed.

Chapter 3 presents a new algorithm for quickly selecting redundant wires for the purpose of masking logic faults. The approach is general purpose and can be applied to any combinatorial circuit. Since the technique is based on increasing the logical masking of faults, it is thus independent of technology scaling. In Section 3.1, the author briefly reviews the notions of signatures, controllability and observability. Then, in Section 3.2, logic implications, redundant wires and techniques for modifying circuits in order to insert redundant wires are discussed. Following this, in Section 3.3, the author presents the new contribution, a novel algorithm for identifying, evaluating and selecting implications. The simulation results are described in Section 3.4. This section also includes a study of the influence of the synthesis constraints used in the original circuit.

Chapter 4 presents an enhanced approximate logic algorithm that quickly computes a series of redundant logic functions with increasing fault-masking coverage. In Section 4.1, two different fault models, stuck-at model and transient model, are introduced. In Section 4.2, the author describes the proposed algorithm, and in Section 4.3, simulation results for several benchmark circuits evaluated for stuck-at (SA) and transient faults are presented.

Chapter 5 summarizes the two presented SET mitigation techniques and outlines the contributions and future directions.

# CHAPTER 2

## **OVERVIEW OF SET MITIGATION TECHNIQUES**

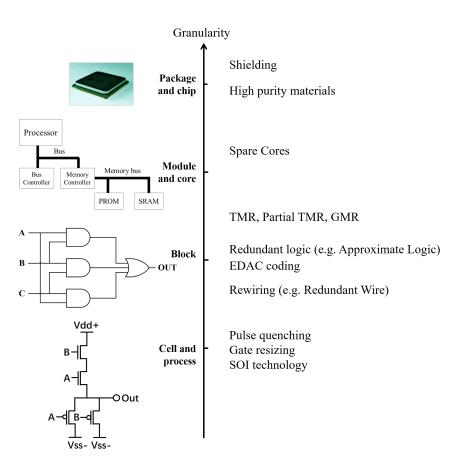

Studies on SET mitigation techniques have been conducted at different levels of design granularity, and researchers have proposed a variety of techniques spanning from the chip level down to the process level, as shown in Figure 2.1. Generally, SET mitigation techniques are classified into two types: fault avoidance and fault correction. Fault avoidance involves isolating radiation sources from devices or constraining the amplitude or width of the pulse so as to minimize the occurrence of the SET actively. Techniques at the package/chip level and the cell/process level mainly fall into this type. On the other hand, fault correction method focuses on maximizing the effects of the three masking mechanisms, which decreases the probability of the fault being latched. Techniques of this type are mainly at the module and block levels that are closely related to the design logic. In this section, a brief overview of the state of the art in SET mitigation is presented.

#### 2.1 Package and Chip Level

Protons and neutrons are two primary sources of radiation particles from cosmic rays[2]. Shielding is the most straightforward and widely applied strategy to protect digital circuits against these particles. For different radiation sources, various shielding materials and strategies are used. For example, an aluminum shielding in the range of 100-250 mils can achieve good protection against protons in a space environment [8]. As for neutrons, materials with low quantivalence have been found to be more effective[4]. Thick shields are required against high energetic particles; nonetheless, it is challenging to eliminate all particles thoroughly. Moreover, this technique is

Figure 2.1: Summary of SET mitigation techniques.

not applicable to most ground-level commercial applications. Besides protons and neutrons, alpha particles are another major culprit of SETs, and impure package materials are the primary source of them. To control alpha particle emission, manufacturers adopt high-purity materials and go through dedicated processes during manufacturing. These measures have dramatically decreased the number of SETs induced by alpha particles.

### 2.2 Core and Module Levels

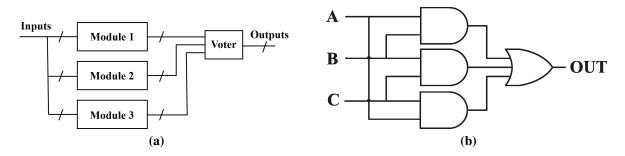

At the core or module level, Triple Modular Redundancy (TMR) is the most well-known and widely applied SET mitigation technique[26]. As is shown in Figure 2.2, the TMR method initially triplicates the target hardware module and then feeds the outputs of these three modules into a voter circuit. The voter circuit takes the majority result as the final output, which ensures that all single-

bit errors are corrected at the final output. Moreover, multi-bit errors can also be masked if they do not affect the same outputs on more than one copy. Nevertheless, TMR requires more than 200% area and power overhead, which is too costly for many ground-level applications. Consequently, a selective TMR scheme is proposed in [29]. Instead of protecting the whole module, the scheme identifies and triplicates only the part of the module with high error susceptibility. In [30], a module used to select the final result based on the history index is proposed to replace the majority voter. Another recent study [31] has looked at a generalization of the TMR called General Modular Redundancy (GMR). In this technique, the TMR is relaxed by ignoring the output combinations with a low probability of occurrence. However, the experimental results indicate the overheads are still not far below the TMR.

Figure 2.2: Triple Modular Redundancy.

#### 2.3 Cell and Process Levels

At the cell level, researchers have put in great effort to adjust the parameters of layouts such as transistor sizing and spacing. For example, gate resizing techniques prove to be effective in fault avoidance because increasing the gate size can enhance the resupplying current, and in turn, decrease the recovery time of transient pulses [32, 33]. In [34, 35], a method to minimize SETs by replacing high-vulnerability nodes with alternative but insensitive implementations is proposed. In [36], Jonathan et al. reported a new mechanism in which charge collection happened simultaneously on adjacent nodes, behaving in such a way as to quench the voltage transient. This pulse quenching mechanism can effectively constrain the width of SET pulses.

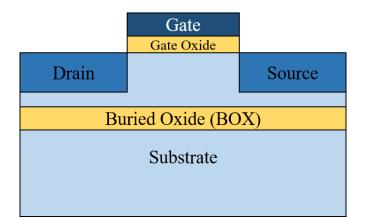

At the process level, studies mainly focus on how to limit the charge collection process at SET origins, since the charge collection process is responsible for the voltage pulse generation and directly influences the magnitude of the transient pulse. Mavis et al. proposed that by delicately selecting node structure and materials, both width and amplitude of SET pulses can be effectively limited[37]. Silicon on insulator (SOI) is a processing technology which places a layer of silicon oxide between substrate and transistors, as demonstrated in Figure 2.3. This isolated structure dramatically reduced the charge collected form adjacent materials. Experimental results has shown that the SOI process has higher radiation tolerance than conventional bulk process[27].

However, the cell and process level techniques require either delicate layout designing or specific technologies, which usually conflicts with ground-level application's need for fast design and high-cost performance.

Figure 2.3: The structure of SOI technology.

#### 2.4 Block Level

At the block level, the most common mitigation strategy is redundancy. Either physical or logical redundancy protects the target circuit by comparing the circuit output with pre-generated redundant information.

#### 2.4.1 Coding Techniques

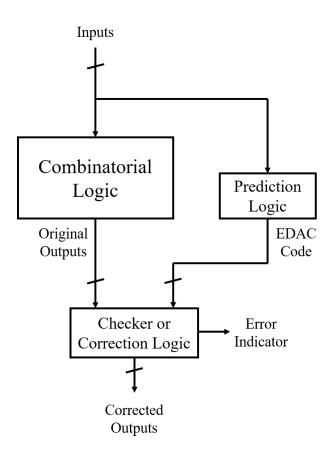

Error detection and correction (EDAC) codes are a major class of redundant techniques. The coding technique has been widely used in the digital communication area to ensure the correctness of the message during transmission. The parity bit, for example, is the simplest coding form with the ability to detect single-bit errors, and Hamming codes are a coding family with the ability to correct single-bit errors and detect double-bit errors. Besides digital communication, the coding technique has also been applied to and found effective in memory designs due to the memory's regular structure. However, to protect the irregular combinatorial logic, the coding technique usually requires a code generation logic called prediction logic (Figure 2.4). The cost of this prediction logic highly depends on the target logic, the coding method as well as the coverage requirement. In [38, 39, 40, 41], a series of Concurrent Error Detection (CED) methods based on the parity code is proposed. On the other hand, Lo et al. applies both error detection and correction codes to arithmetic circuits[42]. A customized Concurrent Error Correction (CEC) code is presented to balance the protective coverage against the overhead incurred[43].

#### 2.4.2 Redundant Logic Techniques

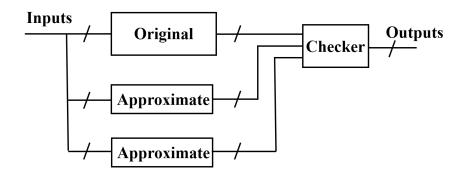

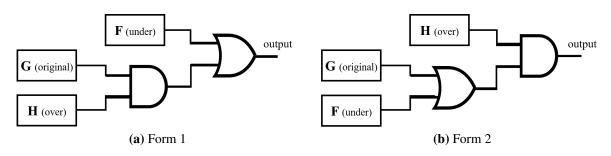

Redundant logic is another major class of mitigation techniques. A typical example is the TMR method discussed on page 13. At the block level, in order to reduce TMR's high overhead, researchers proposed a group of partial TMR techniques named approximate logic. Approximate logic consists of an approximation of the on-set and the off-set of the target combinatorial logic. The generated approximations and the original logic will be connected to a checker logic. The checker is a two-layer logic with an AND/OR structure, and its output is the final output of the circuit, as shown in Figure 2.5. Compared to the conventional TMR, the approximate logic technique has more flexibility over cost control, whereas selecting a good approximation requires skillful maneuvers.

The approximate logic technique was first published in [44]. It uses Binary Decision Diagrams (BDDs) to represent the target circuit and generates the approximations by repeatedly pruning

Figure 2.4: Basic structure of EDAC code approach implementation

the longest branch from the BDD tree. It assumes pruning the longest branch will remove the logic taking the most overhead while losing the least coverage. However, this technique does not scale well to large circuits since the BDD representation is not capable of handling large circuits. Choudhury et al. solved this limitation by utilizing a circuit partitioning technique[45, 46]. On the other hand, a technique which prunes the original circuit netlist and gives fault coverage estimation dynamically is proposed by [47, 48]. While this method results in better scalability, the flexibility may be limited by the structure of the original netlist. In addition, the approximate logic is capable of masking timing faults [49].

#### 2.4.3 **Rewiring Techniques**

Unlike the coding and the approximate logic methods generating redundancy on logic blocks, the rewiring technique focuses on partially restructuring the circuit to increase the overall soft error

Figure 2.5: The basic structure of the approximate logic technique.

rate (SER) resilience. The restructuring process mainly falls into two categories: local rewriting and redundant wire addition, where the local rewriting refers to partially changing the circuit connections while keeping the circuit's original functionality, and the redundant wire addition, as the name indicates, focuses on adding redundant wires to protect the critical nodes identified. The local rewriting method results in less area overhead than the redundant wire addition method, while its SER mitigation benefit is relatively lower. Since the rewiring technique operates on a subtler scale than the other two techniques, it is more flexible and efficient, which is particularly suitable to ground-level applications with moderate reliability requirements.

The largest difficulty in implementing the rewiring technique is identifying the critical nodes given a complex netlist. In [50], the redundant wire addition method was first applied to soft error mitigation. Its identification algorithm is based on fault injection simulations, which is known for demanding tremendous simulations, and thus, is quite computationally expensive. In addistion, its results are inaccurate due to the inevitable compromise made with the computational limitation and the unexamined side effects induced by the newly added wires. In [51, 52, 53], techniques based on local rewriting with more efficient identification algorithms are presented. However, they all lack an algorithm which thoroughly and effectively takes all factors (like logical masking benefits as well as newly induced faults after addition or restructuring) into consideration, and which gives an accurate estimate about the gross benefits achieved in order to guide the SER hardening process.

## CHAPTER 3

# LOW COST MITIGATION OF LOGIC FAULTS WITH RE-DUNDANT WIRES

Chapter 2 reviewed state-of-the-art SET mitigation techniques classified based on the design granularity. In this and next chapters, two novel block-level mitigation methods belonging to rewiring and redundant logic techniques separately are presented.

# 3.1 Signature Based Method to Estimate Controllability and Observability

For each internal node of a digital circuit, the difficulty of controlling the specific logic value from circuit inputs and observing the value from circuit outputs are defined as controllability and observability, respectively. These two metrics are closely related to and widely applied in circuit testability analysis[54, 55, 56, 57, 58]. Likewise, the algorithms for evaluating and selecting redundant wires rely on accurate determination of controllability and observability metrics for the circuit nodes. In this project, a signature based method which is capable of accurately and efficiently estimating these metrics is introduced. In this chapter, we first review the notion of signatures and then present how they can be used in the computation of controllability and observability metrics.

#### 3.1.1 Signature

The probability of faults propagating through a combinatorial network depends on the state of both inputs and nodes in a circuit. In some cases, probabilities are used to deduce the state of nodes; however, the drawback of this approach is that the correlation between the states on different nodes is lost. Thus, when calculating the state probability of a node combination, these approaches can easily lead to a significant difference between estimated and real values. In order to reduce the error, more complicated probability reasoning methods are required.

A logic signature is a randomly generated sequence of logic values on all the nodes of a network, and these signatures can be used to deduce the expected state of an individual node or the expected state of a combination of multiple nodes. As shown in [52], logic signatures can be effective in analyzing masking effects.

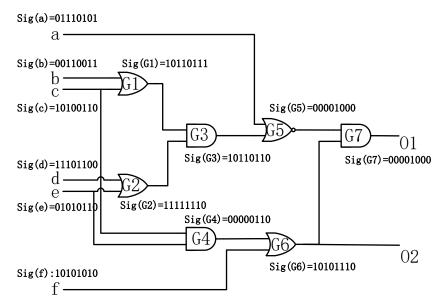

Figure 3.1: Example circuit with random generated signatures.

A *K*-bit signature of a node n in a circuit C is a *K*-bit sequence of logic values appearing at node n corresponding to a sequence of K input vectors (see Figure 3.1). The signature provides information about the probability of a node having the logic value of 0 or 1. However, the  $k^{th}$  bit in the signature of one node is logically consistent with the  $k^{th}$  bit in the signature of another node, which facilitates reasoning about implications. A *K*-bit signature at node *n* can be represented as shown in Equation 3.1.

$$Sig_K(n) = F_n(I_1) \cdot F_n(I_2) \cdots F_n(I_K)$$

(3.1)

where  $I_i$  indicates the  $i^{th}$  random input vector, and  $F_n(I_i) \in 0, 1$  is the local value at *n* when the

$i^{th}$  input vector is applied.

The algorithm used to generate *K*-bit signatures for all the nodes in a circuit C is shown in Algorithm 1. *SortTopological()* sorts all the nodes in topological sequence, so that the nodes can be evaluated in a single pass from input to output. *RandomSignal()* generates a random value for the specified input. *EvaluateParallel()* computes the logic value for all of the input values in parallel using the techniques originally described in [59]. The complexity of generating *K*-bit signatures for a circuit with *N* nodes is  $O(N \cdot K)$ .

```

Algorithm 1 : Signature Generation

function GENERATESIGNATURES(C,K) SORTTOPOLOGICAL(C_{Nodes})

for j = 1 to k do

for i in C_{Inputs} do

I_j(i) = RANDOMSIGNAL

end for

end for

for c in Nodes_{sorted} do

c = EVALUATEPARALLEL(I_1 \cdots I_k)

end for

end for

```

#### 3.1.2 Controllability

In a given logic circuit, the 1(0) controllability of a given node is directly correlated to the percentage of input vectors justifying the logical value 1(0) on the given node. In this paper, we use a *K*-bit vector  $cc_v(n)$  to estimate the *v* controllability of node *n* where  $v \in 0, 1$ . When  $cc_v(n)$ 's  $i^{th}$  bit is 1, it means the value of node *n* is set to *v* under the  $i^{th}$  input vector; otherwise it is 0. Thus, the computation of the *v* controllability of a node *n* is achieved by counting the number of 1s in the the *K* samples within the vector  $cc_v(n)$ . Moreover, with the definition of signatures, approximating  $cc_v(n)$  with *K*-bit signatures is straightforward, as shown in Equation 3.2.

$$cc_{\nu}(n) \approx \begin{cases} Sig_k(n) & \nu = 1\\ \hline Sig_k(n) & \nu = 0 \end{cases}$$

(3.2)

#### 3.1.3 Observability

Depending on the input vector, there may or may not exist sensitized paths from a given node, n, to at least one of the primary outputs. In this paper, we use  $ob_{T,X}(n)$  to represent the observability of node n to any of the target nodes in the targeting set T while the sensitized path does not pass through any of the nodes in the exclusion set X. When  $ob_{T,X}(n)$ 's  $i^{th}$  bit is 1, it means that under the  $i^{th}$  input vector, the value at node n is observable on at least one of the target nodes in T without passing through any nodes in the exclusion set X; otherwise, it is equal to 0. With this generalized definition, the traditional observability of node n can be represented as  $ob_{O,\{\}}(n)$ , where O stands for all the primary outputs and the exclusion set X is empty. In [52], an algorithm for computing the traditional observability  $ob_{O,\{\}}(n)$  is proposed, and here, we extended that algorithm to compute the generalized concept of observability proposed.

This algorithm takes three arguments, *C*, *T* and *X*, as described above and is shown in Algorithm 2.

The method *SortReverseTopological()* sorts all the nodes in circuit C in a reverse topological sequence. The method *ComputeObsCond(n,f)* computes the conditions when node n is observable through direct fanout f. It first decides the non-dominant values at the side inputs of n. Then it gets the signatures of those side inputs and, if the non-dominant value is 0, inverts the corresponding

signature. Finally, those signatures are ANDed with the observability of node f.

|    | signature | $ob_{\{O1,O2\},\{\}}$ | $ob_{\{O1,O2\},\{G5\}}$ |

|----|-----------|-----------------------|-------------------------|

| а  | 01110101  | 00001000              | 0000000                 |

| b  | 00110011  | 00001000              | 00000000                |

| с  | 10100110  | 11011100              | 01010100                |

| d  | 11101100  | 10000000              | 00000000                |

| e  | 01010110  | 00000110              | 00000100                |

| f  | 10101010  | 11111001              | 11111001                |

| G1 | 10110111  | 10001010              | 00000000                |

| G2 | 11111110  | 10000010              | 00000000                |

| G3 | 10110110  | 10001010              | 00000000                |

| G4 | 00000110  | 01010101              | 01010101                |

| G5 | 00001000  | 10101110              | 00000000                |

| G6 | 10101110  | 11111111              | 11111111                |

| G7 | 00001000  | 11111111              | 11111111                |

Table 3.1: Observability of Nodes in Example Circuit

Consider the six inputs, two outputs circuit shown in Figure 3.1. A set of randomly generated signatures and the resulting observability computations are shown in Table 3.1. Two sets of observability are computed, both targeting the same primary outputs but the second one has an excluded gate, G3. The  $ob_{\{O1,O2\},\{\}}(c)$ , for instance, is derived by computing the observability through nodes G1 and G4 respectively and then ORing the two results. The  $ob_{\{O1,O2\},\{\}}(G1)$  is 10001010 and since G1 is an OR gate whose non-dominant value is 0, the signature of b is inverted to 11001100. ANDing these two gives the observability of c at the path through G1 which is 10001000. Similarly, the observability of c at the path through G4 is 01010100, and finally, ORing these two gives  $ob_{\{O1,O2\},\{\}}(c)$  which is 11011100.

If instead we want to compute the observability excluding gate G3,  $ob_{\{O1,O2\},\{G3\}}(c)$ , since the path through G1 is blocked by the G3 node and is no longer observable,  $ob_{O1,O2\}, \{G3\}}(c)$  is equal to the observability of c at the path through G4, which is 01010100.

Similar to Algorithm 1, the observability algorithm traverses the circuit in a single pass from output to input, and for each node in the circuit, a constant number of basic signature operations is performed. Thus the complexity of computing the observability for a circuit with N nodes is  $O(N \cdot K)$ .

The application of controllability and the generalized observability will be described later where they are used for selecting implications.

#### 3.2 Redundant Wires

The proposed logic fault mitigation methodology is based on the logic coverage provided by redundant wires. In this chapter, we review the basic notions of logic implications and redundant wires, and how to modify circuits in order to insert redundant wires.

#### 3.2.1 Logic Implications

An implication is a relationship that exists in a circuit between two nodes, called the source (S) and the target (T). If it is the case that whenever S is true (or false), and it follows that T is always either true or false, then there exists a 1-to-1 implication from S to T. Logic implications have been widely used in areas like probabilistic analysis [48], logic optimization [60, 61], design verification [62] and test-pattern generation [63]. In this project, logic implications are used to guide the selection of redundant wires.

Let us consider the example circuit from Figure 3.1, but re-draw it to illustrate the implications in Figure 3.2. It can be seen that when G3 = 1, then G5 = 0 because G5 is a NOR gate and the dominant value of its inputs is 1. This implication is denoted as  $(G3, 1) \rightarrow (G5, 0)$ .

#### 3.2.2 Redundant Wires

A redundant wire, as the name implies, is a functionally redundant connection whose logic is fully covered by the rest of the circuit, and thus, the addition of a redundant wire preserves the functionality of the original circuit. As proposed in [50], implications can be used to identify and generate redundant wires. The way redundant wires are inserted in the circuit is introduced in Section 3.2.3. Like many spare redundancy methods used to mask faults, the redundant wire is able to mask logical faults under its coverage from being observed on primary outputs. A model for evaluating the protective effect of a redundant wire is proposed in Section 3.3.2.

Figure 3.2: Example circuit with implications.

Let us once again consider the example circuit shown in Figure 3.2. It can be seen that when G3 = 1, then G5 = 0 and G7 = 0. Let us suppose that when G3 = 1 and G6 = 1, there is a fault at G5 that causes a bit flip  $(0 \rightarrow 1)$ . This fault would propagate to the output O1 and generate an incorrect output value (1 instead of 0). If, however, a redundant wire were connected from G3 to the input of G7, this fault would be masked at G7 and the outputs would be correct.

#### 3.2.3 Circuit Modification

In this section, we discuss how to modify a netlist in order to insert redundant wires, based on a given implication. First, given an implication, the basic idea behind how to insert a redundant wire is to add a connection originating from the source to the input of the target gate. However, in order to preserve the functionality of the original circuit, two necessary conditions must be satisfied. The first condition is that the source of the implication must be out of the fan-out cone of the target. The

reason is straightforward. Suppose the source is a transitive fan-out of the target and it is connected back to the target, a combinatorial loop would be created.

The second condition is that the implicated value must be able to dominate the target. For instance, the value 1 is the dominant value of OR and NAND gates, and value 0 is the dominant value of AND and NOR gates. Of course, XOR gates have no dominant value and a NOT gate has both 1 and 0 as dominant values. This condition combined with the manipulations introduced later guarantee that the redundant wire will always be dominated under fault-free conditions, ensuring that the circuit is not modified.

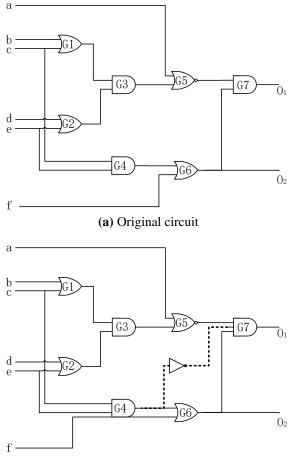

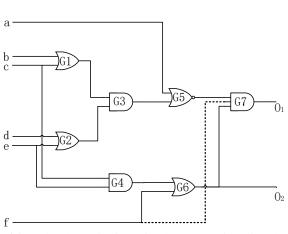

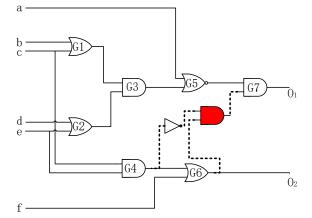

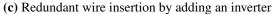

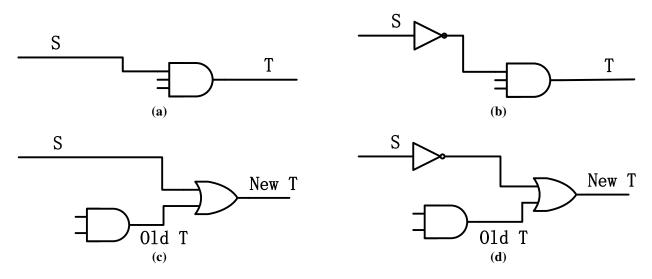

(b) Redundant wire insertion by connecting directly

(d) Redundant wire insertion by adding an inverter and a checker Figure 3.3: Netlist manipulation to insert redundant wires.

For example, in the circuit shown in Figure 3.3, we can identify two implications,  $(G4, 1) \rightarrow$ (G7,0) and  $(G4,1) \rightarrow (G3,1)$ . Both of their target gates are AND gates, while their implicated values are 0 and 1, respectively. Since the dominant value of an AND gate is 0, we can add a redundant wire by inverting the output of G4 and adding it to the input of G7 for the first implication, as shown in Figure 3.3c. But for the second implication, connecting the output of G4, whether inverted or not, to the input of G3 will change the original functionality.

Besides the necessary conditions discussed above, there are two additional factors which influence the addition of redundant wires. The first factor is the implicant value of the implication. If it dominates the target gate, then the source can be connected directly to the input of the target gate. Otherwise, an inverter must be inserted before connecting the source to the target. Figure 3.3b and Figure 3.3c show the insertion of implications  $(f,0) \rightarrow (G7,0)$  and  $(G4,0) \rightarrow (G7,0)$ , which illustrate these two situations. Notice that the second situation introduces a new inverter into the circuit, and consequently, increases the risk of faults. Our evaluation algorithm will take into consideration the new faults that can occur in the gates that are inserted when an implication is mapped.