# A COST SHARED QUANTIZATION ALGORITHM AND ITS IMPLEMENTATION FOR MULTI - STANDARD VIDEO CODECS

A Thesis Submitted to the College of

Graduate Studies and Research

In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

Ву

**MOUSUMI DAS**

© Copyright Mousumi Das, December, 2012. All rights reserved.

PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree

from the University of Saskatchewan, I agree that the Libraries of this University may make it

freely available for inspection. I further agree that permission for copying of this thesis in any

manner, in whole or in part, for scholarly purposes may be granted by the professor or professors

who supervised my thesis work or, in their absence, by the Head of the Department or the Dean

of the College in which my thesis work was done. It is understood that any copying or

publication or use of this thesis or parts thereof for financial gain shall not be allowed without my

written permission. It is also understood that due recognition shall be given to me and to the

University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or

part should be addressed to:

Head of the Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan

Canada, S7N 5A9

i

#### **ABSTRACT**

The current trend of digital convergence creates the need for the video encoder and decoder system, known as codec in short, that should support multiple video standards on a single platform. In a modern video codec, quantization is a key unit used for video compression. In this thesis, a generalized quantization algorithm and hardware implementation is presented to compute quantized coefficient for six different video codecs including the new developing codec High Efficiency Video Coding (HEVC). HEVC, successor to H.264/MPEG-4 AVC, aims to substantially improve coding efficiency compared to AVC High Profile. The thesis presents a high performance circuit shared architecture that can perform the quantization operation for HEVC, H.264/AVC, AVS, VC-1, MPEG- 2/4 and Motion JPEG (MJPEG). Since HEVC is still in drafting stage, the architecture was designed in such a way that any final changes can be accommodated into the design. The proposed quantizer architecture is completely division free as the division operation is replaced by multiplication, shift and addition operations. The design was implemented on FPGA and later synthesized in CMOS 0.18 µm technology. The results show that the proposed design satisfies the requirement of all codecs with a maximum decoding capability of 60 fps at 187.3 MHz for Xilinx Virtex4 LX60 FPGA of a 1080p HD video. The scheme is also suitable for low-cost implementation in modern multi-codec systems.

#### **ACKNOWLEDGMENTS**

The work presented in this thesis has been carried out at the Department of Electrical and Computer Engineering, University of Saskatchewan, Saskatoon, Saskatchewan during the years 2010 – 2012 under the kind supervision of Dr. Khan A. Wahid.

First I would like to express my gratitude to my supervisor, Dr. Wahid for introducing me to the research field and for his continuous support, inspiration and guideline throughout the project. His vast knowledge and expertise in this field added considerably to my graduate experience.

Then, I would like to thank my thesis committee members for their time to examine my thesis and insightful comments. I would also like to acknowledge the financial support from NSERC. Finally, I would like to thank my family for their love, encouragement and support.

Mousumi Das

# TABLE OF CONTENTS

| PERMI  | SSION TO USE                                      | i    |

|--------|---------------------------------------------------|------|

| ABSTR  | ACT                                               | ii   |

| ACKNO  | OWLEDGEMENT                                       | iii  |

| TABLE  | OF CONTENTS                                       | iv   |

| LIST O | F TABLES                                          | vii  |

| LIST O | F FIGURES                                         | viii |

| LIST O | F ABBREVIATIONS                                   | ix   |

| 1      | INTRODUCTION                                      | 1    |

|        | 1.1 Digital convergence in consumer products      | 1    |

|        | 1.2 Different video coding standards              | 2    |

|        | 1.2.1 MPEG-2 standard                             | 2    |

|        | 1.2.2 Motion JPEG (MJPEG) standard                | 2    |

|        | 1.2.3 Windows Media Video 9 (WMV-9)/VC-1 standard | 3    |

|        | 1.2.4 H.264/MPEG-4 (part-10)/AVC standard         | 4    |

|        | 1.2.5 AVS standard                                |      |

|        | 1.2.6 Developing HEVC standard                    | 5    |

|        | 1.3 Basics of video compression.                  | 6    |

|        | 1.4 Components in a video codec                   | 7    |

|        | 1.5 Overview of a multi quantizer unit            | 8    |

|        | 1.6 Previous works                                |      |

|        | 1.7 Thesis objectives                             |      |

|        | 1.8 Thesis organizations                          | 13   |

| 2      | DIFFERENT QUANTIZATION SCHEMES                    |      |

|        | 2.1 Introduction.                                 |      |

|        | 2.2 Overview of quantization                      |      |

|        | 2.3 Quantization in H.264                         |      |

|        | 2.3.1 8x8 quantization in H.264                   |      |

|        | 2.4 Quantization in AVS                           |      |

|        | 2.4.1 8x8 quantization in AVS                     |      |

|        | 2.5 Quantization in VC-1                          |      |

|        | 2.6 Quantization in MPEG-2/4                      |      |

|        | 2.7 Quantization in Motion JPEG (MJPEG)           |      |

|        | 2.7.1 8x8 quantization in MJPEG                   | 23   |

| 2.8 Quantization in HEVC (draft stage)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.8.1 Proposal by Samsung Electronics, Ltd, FastVDO                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| 2.8.2 Proposal by Cisco Systems, Texas Instrument Inc                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

| PROPOSED ALGORITHM                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                               |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27                               |

| 3.2 Proposed Division Free Quantization Algorithm (DFQA)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                               |

| 3.2.1 Steps of DFQA                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| 3.2.2 Equation to calculate MF for VC-1, MPEG-2/4 and MJPEG                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                               |

| 3.2.3 DFQA applied to H.264                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |

| 3.2.3.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                               |

| 3.2.4 DFQA applied to AVS                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

| 3.2.4.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

| 3.2.5 DFQA applied to VC-1 and MPEG-2/4                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33                               |

| 3.2.5.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

| 3.2.6 DFQA applied to MJPEG                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                               |

| 3.2.6.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 37                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |

| 3.2.7 DFQA applied to HEVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                               |

| 3.2.7 DFQA applied to HEVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                               |

| 3.2.7.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                               |

| 3.2.7.1 Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41<br>42<br>42                   |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture                                                                                                                                                                                                                                                                                                                                                                                                      | 41<br>42<br>42<br>43             |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture 4.2.1 Architecture of the multi quantizer                                                                                                                                                                                                                                                                                                                                                            | 41<br>42<br>42<br>43             |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture                                                                                                                                                                                                                                                                                                                                                                                                      | 41<br>42<br>43<br>44<br>46       |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture 4.2.1 Architecture of the multi quantizer 4.2.2 Architecture of the look-up tables.                                                                                                                                                                                                                                                                                                                  | 41<br>42<br>43<br>44<br>46<br>49 |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture 4.2.1 Architecture of the multi quantizer 4.2.2 Architecture of the look-up tables 4.3 Overall operation                                                                                                                                                                                                                                                                                             | 414242434649                     |

| 3.2.7.1 Example.  HARDWARE IMPLEMENTATION.  4.1 Introduction.  4.2 Overall hardware architecture.  4.2.1 Architecture of the multi quantizer.  4.2.2 Architecture of the look-up tables.  4.3 Overall operation.  HARDWARE COMPARISON.  5.1 Introduction.                                                                                                                                                                                                                                        | 414243464952                     |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture 4.2.1 Architecture of the multi quantizer 4.2.2 Architecture of the look-up tables. 4.3 Overall operation  HARDWARE COMPARISON 5.1 Introduction 5.2 Performance comparison in FPGA                                                                                                                                                                                                                   | 4142424346495252                 |

| 3.2.7.1 Example.  HARDWARE IMPLEMENTATION.  4.1 Introduction.  4.2 Overall hardware architecture.  4.2.1 Architecture of the multi quantizer.  4.2.2 Architecture of the look-up tables.  4.3 Overall operation.  HARDWARE COMPARISON.  5.1 Introduction.  5.2 Performance comparison in FPGA.  5.2.1 Resource utilization summary in FPGA.                                                                                                                                                      | 41424346495252                   |

| 3.2.7.1 Example  HARDWARE IMPLEMENTATION 4.1 Introduction 4.2 Overall hardware architecture 4.2.1 Architecture of the multi quantizer 4.2.2 Architecture of the look-up tables 4.3 Overall operation  HARDWARE COMPARISON 5.1 Introduction 5.2 Performance comparison in FPGA 5.2.1 Resource utilization summary in FPGA 5.2.2 Performance comparison of the multi quantizer                                                                                                                     | 41424244464952525253             |

| HARDWARE IMPLEMENTATION.  4.1 Introduction.  4.2 Overall hardware architecture.  4.2.1 Architecture of the multi quantizer.  4.2.2 Architecture of the look-up tables.  4.3 Overall operation.  HARDWARE COMPARISON.  5.1 Introduction.  5.2 Performance comparison in FPGA.  5.2.1 Resource utilization summary in FPGA.  5.2.2 Performance comparison of the multi quantizer.  5.2.3 Performance comparison of the transform-quantizer.                                                        | 4142424346495252525555           |

| 3.2.7.1 Example.  HARDWARE IMPLEMENTATION.  4.1 Introduction.  4.2 Overall hardware architecture.  4.2.1 Architecture of the multi quantizer.  4.2.2 Architecture of the look-up tables.  4.3 Overall operation.  HARDWARE COMPARISON.  5.1 Introduction.  5.2 Performance comparison in FPGA.  5.2.1 Resource utilization summary in FPGA.  5.2.2 Performance comparison of the multi quantizer.  5.2.3 Performance comparison of the transform-quantizer.  5.3 Performance comparison in VLSI. | 41424346495252525355             |

| HARDWARE IMPLEMENTATION.  4.1 Introduction.  4.2 Overall hardware architecture.  4.2.1 Architecture of the multi quantizer.  4.2.2 Architecture of the look-up tables.  4.3 Overall operation.  HARDWARE COMPARISON.  5.1 Introduction.  5.2 Performance comparison in FPGA.  5.2.1 Resource utilization summary in FPGA.  5.2.2 Performance comparison of the multi quantizer.  5.2.3 Performance comparison of the transform-quantizer.                                                        | 414243444649525252535557         |

| 6  | CONCLUSIONSAND SUGGESTIONS FOR FUTURE WORK | 63 |

|----|--------------------------------------------|----|

|    | 6.1 Conclusion                             | 63 |

|    | 6.2 Suggestions for future works           | 64 |

| RE | FERENCES                                   | 66 |

# LIST OF TABLES

| Table 2.1. | Quantization step sizes in H.264                                  | 17 |

|------------|-------------------------------------------------------------------|----|

| Table 2.2. | Quantization parameter and the values of MF                       | 17 |

| Table 2.3. | Quantization table for AVS encoder                                | 19 |

| Table 2.4. | Derivation of DC StepSize for uniform and non-uniform quantizer   | 21 |

| Table 3.1. | Description of different parameters used in the DFQA              | 41 |

| Table 5.1. | Resource utilization in Virtex2 FPGA                              | 53 |

| Table 5.2. | Resource utilization in Virtex4 FPGA                              | 53 |

| Table 5.3. | Resource utilization in Virtex5 FPGA                              | 53 |

| Table 5.4. | Comparison with the existing designs (quantizer only)             | 54 |

| Table 5.5. | Comparison with the existing designs (transform and quantization) | 56 |

| Table 5.6. | Comparison of multi quant with the estimated cost (VLSI only)     | 57 |

| Table 5.7. | Comparison of decoding capability of the multi quantizer schemes  | 61 |

| Table 5.8. | Comparison of decoding capability of combined transform-quantizer | 61 |

# LIST OF FIGURES

| Figure 1.1. | Series of still images representing "scenes in motion"                 | 6  |

|-------------|------------------------------------------------------------------------|----|

| Figure 1.2. | Functional block dagram of modern video codec                          | 8  |

| Figure 1.3. | Look-up table based multi quantizer unit                               | 10 |

| Figure 2.1. | Four basic steps of transform coding.                                  | 15 |

| Figure 2.2. | The position specification of MF                                       | 16 |

| Figure 2.3. | VC-1 quantization and dequantization rule showing                      |    |

|             | (a) dead zone                                                          |    |

|             | (b) regular uniform quantization                                       | 20 |

|             | Barbara image                                                          |    |

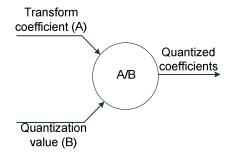

| Figure 4.1. | Basic quantization scheme using division operation.                    | 42 |

| Figure 4.2. | Quantization scheme of the proposed multi quantizer                    | 42 |

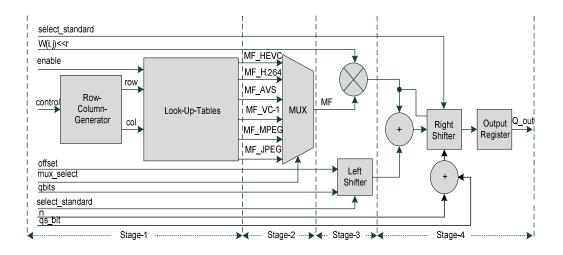

| Figure 4.3. | Overall block diagram of the DFQA                                      | 43 |

| Figure 4.4. | Orientation of multi quantizer, multi transform, QP processing and LUT | 44 |

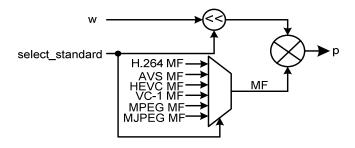

| Figure 4.5. | Hardware of step 1 of the DFQA                                         | 45 |

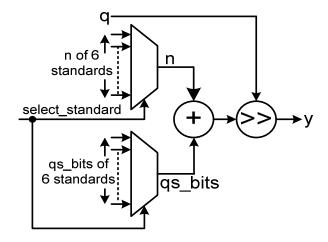

| Figure 4.6. | Hardware of step 2 of the DFQA                                         | 46 |

|             | Hardware of step 3 of the DFQA                                         |    |

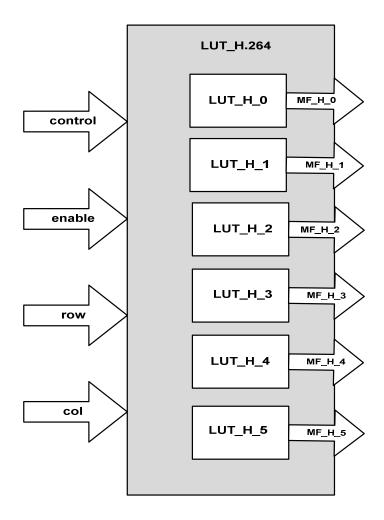

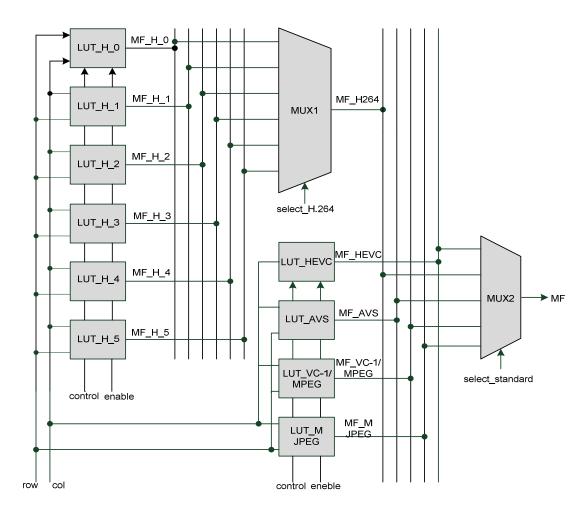

| Figure 4.8. | Look-up tables of all six standards                                    | 47 |

| Figure 4.9. | Look-up tables of H.264 standard                                       | 48 |

| Figure 4.10 | Look-up tables and complete data flow diagram                          | 49 |

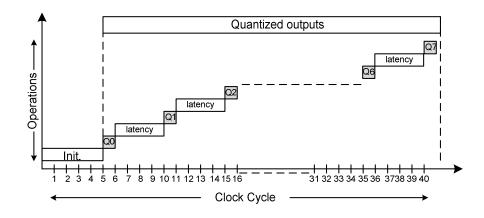

| Figure 4.11 | . Entire operation with all pipelining boundaries                      | 50 |

| Figure 4.12 | . Timing diagram of the multi quantizer                                | 51 |

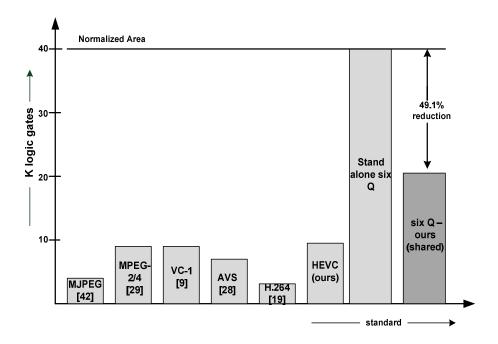

| Figure 5.1. | Comparison of normalized area of the multi quantizer                   | 58 |

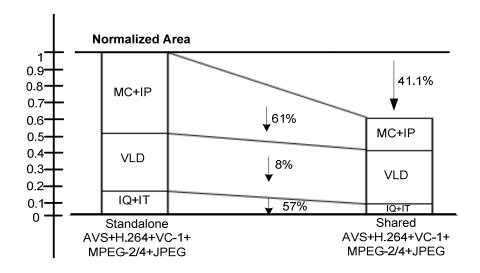

| Figure 5.2. | Cost reduction map of decoder using the multi quantizer architecture   | 59 |

|             |                                                                        |    |

# LIST OF ABBREVIATIONS

| 1D      | One Dimensional                          |

|---------|------------------------------------------|

| 2D      | Two Dimensional                          |

| ASIC    |                                          |

| AVC     |                                          |

| AVS     | Audio Video coding Standard              |

| CMOS    |                                          |

| DCT     |                                          |

| FPGA    | Field Programmable Gate Array            |

| FSM     | Finite State Machine                     |

| fps     | Frame Per Second                         |

| HD      | High Definition                          |

| HDL     |                                          |

| HEVC.   |                                          |

| IDCT    |                                          |

| IEC     |                                          |

| IEEE    |                                          |

| Int-DCT | Integer Discrete Cosine Transform        |

| Int-IDC | Γ                                        |

| IP      |                                          |

| IQ      |                                          |

| IT      |                                          |

|         |                                          |

| ITU     |                                          |

| JCT-VC  | Joint Collaborative Team on Video Coding |

| JPEG    | Joint Photographic Experts Group         |

| LUT     | Look-up Table                            |

| MC      |                                          |

|         |                                          |

| MJPEG   |                                          |

|         |                                          |

| Msec    |                                          |

| Q       |                                          |

| -       | Quantization Parameter                   |

| QS      | Quantization Step                        |

|         | System On a Chip                         |

|         | Ultra High Definition                    |

|         | Video Codec -1                           |

| VCEG    |                                          |

| VLD  | Variable Length Decoder      |

|------|------------------------------|

|      | Very Large Scale Integration |

| WMV9 | Windows Media Video 9        |

#### CHAPTER 1

#### INTRODUCTION

This chapter presents a brief description of materials which are necessary for this research work. It begins with the current demand of the modern world focusing on digital convergence of electronic consumer products in a single system-on-chip (SoC) platform. Then, different video coding standards are described briefly followed by basics of video compression. After that, the units of modern video codecs are discussed. This initiates the need of the multi quantizer unit which is the main focus of this thesis. Finally, previous research works have been presented.

## 1.1 Digital convergence in consumer products

An evident trend in modern world is the digital convergence in the current electronic consumer products. Recently, reconfigurable concept has become one of the most important issues for video coding technology. Nowadays people usually want a product that can support various formats and features, such as, Video on Demand (VOD), Digital Multimedia Broadcasting (DMB) and Portable Multimedia Player (PMP) and so on. Due to such demand and realizing the fact that the intercommunication among different video devices supporting different standards is inconvenient, it is necessary to support widely used video compression standards in a single system-on-chip (SoC) platform. So the goal is to find a way to develop a multi-codec system that achieves high performance i.e. higher decoding capability, as well as low hardware cost. To develop reconfigurable architecture or algorithm which meets both of the objectives is a challenge.

With the significant development of multimedia technology during the last decade, various video coding standards, such as, MJPEG [1], MPEG-2/4 [2], VC-1 [3], H.264/AVC [4], AVS [5] has been developed for different applications. Moreover, to improve the coding efficiency further, a joint collaborative team on video coding (JCT-VC) has starred drafting a new video standard known as High Efficiency Video Coding (HEVC) [6]. Therefore, a multi-codec system that supports all these standards is needed to satisfy the requirements of different applications.

## 1.2 Different video coding standards

There are several video coding standards in use. The following sections describe six popular video coding standards.

#### 1.2.1 MPEG-2 standard

MPEG-2 is a standard for generic coding of moving pictures and associated audio information [7]. MPEG-2 is widely used as the format of digital television signals that are broadcasted by terrestrial, cable and direct broadcast satellite TV systems. It also specifies the format of movies and other programs that are distributed on DVDs and similar discs. All standards-compliant MPEG-2 video decoders are fully capable of playing back MPEG-1 Video streams conforming to the Constrained Parameters Bitstream syntax. With some enhancements, MPEG-2 Video and Systems are also used in some HDTV transmission systems.

### 1.2.2 Motion JPEG (MJPEG) standard

Motion JPEG (MJPEG) standard separately compresses each frame of video sequence in JPEG format [8]. Hence this standard does not exploit the redundancy presented in successive

frames. As a result as compared to MPEG, MJPEG has lower attainable compression but is also less computationally complex. It is popularly used for non-linear editing which requires easy access to any frame. Another application for MJPEG is medical imaging which requires high quality images and error resilience. The disadvantage of MJPEG is that it does not exploit the temporal redundancies of successive frames to achieve higher compression and consequently MJPEG has higher bit-rate than MPEG for the same quality. Typical quality problems for MJPEG are blocking and ringing artifacts, especially at low bit-rate compression.

## 1.2.3 Windows Media Video 9 (WMV-9)/VC-1 standard

Microsoft Windows Media 9 series is a set of technologies that enables rich digital media experiences across many types of networks and devices [9]. These technologies are widely used in industry for media delivery over the internet and other media, and are also applied to broadcast, high definition DVDs and digital projection in theaters. At the core of these technologies is a state-of-the-art video codec called Windows Media Video 9 (WMV-9), which provides highly competitive video quality for reasonable computational complexity. Although the origins of Windows Media focused on streaming compressed audio and video over the internet to personal computers, the vision moving forward is to enable effective delivery of digital media through any network to any device. In addition to Internet-based applications (e.g., subscription services, video on demand over IP, web broadcast, etc.), content compressed with Windows Media codecs is being consumed by a wide range of wired and wireless consumer electronic devices such as mobile phones, DVD players, portable music players, car stereos, etc.

## 1.2.4 H.264/MPEG-4 (part-10)/AVC standard

The continuing development of digital video coding has produced ITU-T H.264/MPEG-4 (part-10), also known as Advanced Video Coding (AVC)[4]. H.264/MPEG-4 (part-10)/AVC is a block-oriented motion-compensation-based codec standard developed by the ITU-T Video Coding Experts Group (VCEG) together with the International Organization for Standardization (ISO)/International Electro technical Commission (IEC) joint working group, the Moving Picture Experts Group (MPEG). It provides gains in compression efficiency up to 50% over the wide range of bit rates and video resolution compared to the previous video standards [10]. Compared to the other video standards, H.264 has many features that make it one of the most powerful standards. Besides, network friendliness and good video quality at high and low bit rates are important features that distinguish H.264 from other standards. This video compression standard is currently one of the most commonly used formats for the recording, compression, and distribution of high definition video. Moreover, H.264 video format has a very broad application range that covers all forms of digital compressed video from low bit-rate internet streaming applications to HDTV broadcast and Digital Cinema applications with nearly lossless coding.

#### 1.2.5 AVS standard

AVS (Audio Video Coding Standard), developed by the China AudioVideo Coding Standard Working Group, was adopted by the Chinese government to reduce foreign dependence on core intellectual properties used in digital media technology [11]. Proposed as a national standard in 2004, AVS soon became the mandatory video compression standard in China terrestrial digital TV. AVS-video is an application driven coding standard. AVS Part 2 targets high-definition digital video broadcasting and high-density storage media and AVS Part 7 targets

low complexity, low picture resolution mobility applications [11]. Integer transform, intra and inter-picture prediction, in-loop deblocking filter and context-based two dimensional variable length coding are the major components in AVS-video compression, which are well-tuned for target applications. It achieves similar performance to H.264/AVC with lower cost. Up to now, there are two separate parts in this standard targeting to different video compression applications:

(a) AVS Part 2 for high-definition digital video broadcasting and high-density storage media; (b) AVS Part 7 for low complexity, low picture resolution mobility applications. The informal names, AVS 1 .0 and AVS-M, are used to represent for AVS Part 2 and Part 7 respectively [11].

## 1.2.6 Developing HEVC standard

High Efficiency Video Coding (HEVC) is a draft video compression standard, a successor to H.264/MPEG-4 AVC (Advanced Video Coding) currently under joint development by the ISO/IEC Moving Picture Experts Group (MPEG) and ITU-T Video Coding Experts Group (VCEG) [6]. HEVC is said to improve video quality, double the data compression ratio compared to H.264, and can support resolutions up to 8K UHD (7680 × 4320). It aims to substantially improve coding efficiency compared to AVC High Profile, i.e., to reduce bitrate requirements by half with comparable image quality, at the expense of increased computational complexity. Two of the key features where HEVC was improved compared to H.264/MPEG-4 AVC were support for higher resolution video and improved parallel processing methods. HEVC is targeted at next-generation HDTV displays and content capture systems which feature progressive scanned frame rates and display resolutions from QVGA (320×240) up to 1080p (1920×1080) and 4320p (7680×4320), as well as improved picture quality in terms of noise level, color gamut, and dynamic range.

## 1.3 Basics of video compression

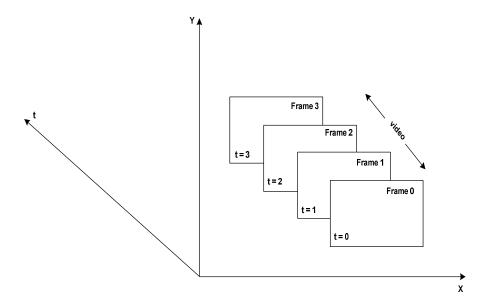

Video refers to pictorial (visual) information, including still images and time-varying images. A series (or set) of still images which represents "scenes in motion" is referred to as video which is shown by Figure 1.1. A time varying image is a spatiotemporal intensity pattern, denoted by  $s_a(x, y, t)$ , where x and y is the spatial variable and t is the temporal variable.

Figure 1.1. Series of still images representing "scenes in motion"

A typical video scene is composed of multiple objects each with their own characteristics such as shape, depth, texture, and illumination. An object has two characteristics: (i) spatial characteristics (texture variation, number and shape of objects, color, etc) and (ii) temporal characteristics (object motion, changes in illumination (brightness), movements of camera, etc). However, video compression is necessary everywhere in our modern day life as it helps reduce resource usage, such as data storage space or transmission capacity. Since a video stream has two spatial and one temporal dimension, video compression is usually done independently in all dimensions. A common characteristic of an image is that the neighboring pixels are correlated and therefore, contains redundant information. So, image compression is achieved by eliminating

redundancies of neighboring pixels and frames. There are three types of redundancies to consider.

(i) spatial redundancies or correlation between neighboring pixel values (ii) spectral redundancies or correlation between different color planes or spectral bands (iii) temporal redundancy or correlation between adjacent frames in a sequence of images (in video applications). In video compression, the encoder removes spatial and temporal redundancies and the decoder puts them back. However, in modern video compression technique exploiting the spatial and spectral redundancies is not enough. So the modern multimedia codecs employ another technique known as, motion compensation/estimation which is the temporal redundancy.

## 1.4 Components in a video codec

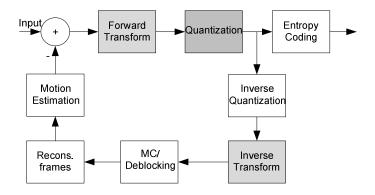

Most modern multimedia codecs (both encoder and decoder) employ transform-quantization pair as well as entropy coding, motion compensation/estimation as shown in Figure 1.2. The transform-quantization pair is very important for lossy video compression. The transform unit isolates various image frequencies, i.e. low frequency and high frequency components. Low frequencies correspond to the important image features, whereas high frequencies correspond to the details of the image, which are less important as human visual system is less sensitive to high frequency components. The transform coefficients go through the quantization stage to reduce perceptual redundancies and bit rates. A quantization parameter at the encoder divides transform coefficients, and the quotient is transmitted. The decoder multiplies this quotient by the same quantization parameter to reconstruct the coefficient. Thus the quantization unit quantizes each transform coefficient separately coming from the transform unit. During this process, the pixels that correspond to high frequencies can be quantized heavily, whereas pixels that correspond to low frequencies can be quantized lightly or not at all. This is

how a transform-quantization pair can compress an image very effectively by losing information, associated with unimportant image details. The encoder treats the quantized coefficients as symbols which are then entropy encoded. The motion estimation stage of an encoder finds matching blocks in reference pictures that are similar to the block that's currently being coded. To compensate for motion in a video, the matched block is subtracted from the current block. The closer the block match, the smaller the difference, and the smaller the amount of information transmitted to a decoder.

Figure 1.2. Functional block diagram of modern video codec

The quantization unit serves a key role in video compression and the current demand leads to various devices that support different features, therefore, the focus is on developing and efficiently implementing a multi-quantizer unit to compute quantization of six widely used multimedia codecs: MJPEG, MPEG-2/4, VC-1, H.264/AVC, AVS and HEVC.

## 1.5 Overview of a multi quantizer unit

Different video standard has different quantization parameters and quantization matrices. While developing the architecture, all the quantization (Q) coefficients of the Q-tables of different standards have been considered carefully to establish a relationship between them. The quantization in Motion JPEG (MJPEG) is defined as the division of the DCT coefficient by the

corresponding Q-values specified by the Q-matrices. Similarly for MPEG-2, according to [7] the quantized value is obtained by dividing the DCT coefficient by the corresponding values of the Q matrices. The work in [12] states that MPEG-4 part 2 supports custom quantization table that can be tuned to content and bit rate like MPEG-2. Hence in this proposed design the same quantization scheme for both MPEG-2 and MPEG-4 part 2 is used and referred to as the quantization of MPEG-2/4. On the other hand, the two most popular video standards, H.264/AVC and AVS, exploit multiplication and shift operation for the purpose of quantization to avoid the division operation for reduced computational complexity. Moreover, HEVC uses similar Q-scheme as H.264. The quantization in VC-1 is user-defined and similar to the process in MPEG-2 [9].

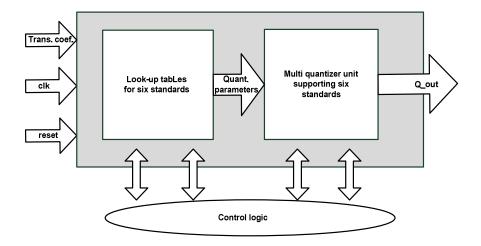

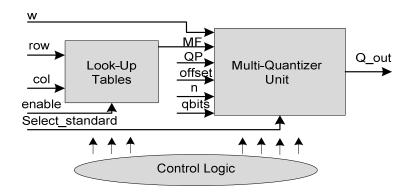

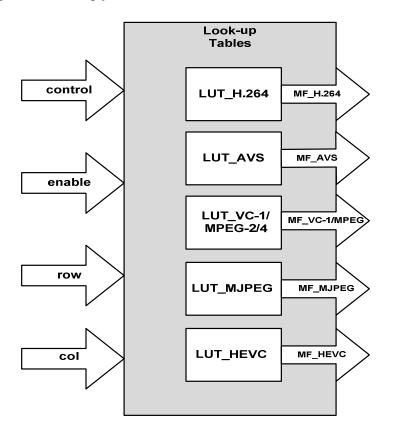

Based on the observation, a new multi-quantizer architecture to support these six codecs is developed. This architecture, shown in Figure 1.3 follows a look-up table based approach. It is completely division free, as division operation is replaced by multiplication, addition and shift operation. Note that the right shift operation can be a replacement of division operation. For example, the binary of 16 is (10000)<sub>2</sub>. Now if 1 is right shifted by one bit, the result is (01000)<sub>2</sub> which is the binary form of 8. So, right shift is equivalent to the division operation. In addition, the right shift operation reduces the hardware complexity as compared to the division. The multi quantizer architecture has only one shared multiplier and one control logic for all the six standards. The concept of using shared multiplier and control logic reduces the hardware cost as well as less computational complexity. The architecture is later synthesized into both FPGA and ASIC level and the result is compared with existing designs. The proposed design serves as a key unit in a multi-codec system in transcoding applications [13] and [14].

Figure 1.3. Look-up table based multi quantizer unit

#### 1.6 Previous works

A significant amount of research has been conducted to efficiently combine and implement the transform units for multiple codecs [15-18]. On the other hand little research is focused on the implementation of multi-quantizer unit. Among the multiple-transform units, a unified Inverse Discrete Cosine Transform (IDCT) architecture to support five standards (such as, AVS, H.264, VC-1, MPEG-2/4 and JPEG) is presented in [15]. The authors in [16] offer an area efficient architecture to perform a DCT-based transform for JPEG, MPEG-4, VC-1 and H.264 using delta mapping. The design in [17] is an IDCT and IQ circuit for H.264, MPEG-4 and VC-1. However, it shows a general implementation of the inverse quantization. The full IQ design including all the quantization tables of these three standards is not implemented. The authors in [18] present a design to support 8x8 transform and quantization for H.264, MPEG-4 and VC-1 where the quantization circuit is again a generalized implementation like the design in [17]. A design to support the 4x4 transform and quantization of H.264 has been presented in [19]. The 8x8 transform and quantization for H.264 is presented in [20] and [21]. Several other designs

based on H.264 codec have been reported in [22-27]. The authors in [28] present a design for the quantization for AVS. The design in [29] describes an MPEG-2 encoder. In [30], another JPEG encoder is implemented for images where the quantization block is designed using multiplication and shift operation instead of division. The design in [31] describes a multi standard video decoder to support four codecs - AVS, H.264, VC-1 and MPEG-2. Silicon Image Inc. currently supplies a Multi-standard High-Definition Video Decoder (MSVD-HD) core that supports H.264, VC-1, and MPEG- 1/2 codecs [32]. Their multiplexed decoder chip costs 970K gates using TSMC 90 nm technology (including complete memory interfacing, stream reader functionality and extra logic for context switch support). In a recent JCT-VC meeting, the transform and quantization algorithms for the new developing standard, HEVC are finalized [33]. The work in [34] presents a multi-codec design for IDCT implementation including HEVC. However, none of the existing designs can compute the quantization of all six video codecs. In this thesis, a new division-free quantization algorithm (DFQA) is presented to compute the quantization units for six multimedia codecs: MJPEG, MPEG-2/4, VC-1, H.264/AVC, AVS and HEVC. In addition, the dedicated hardware implementation as compared to a software program executed on a general purpose processor has several advantages [35]. The hardware implementation is necessary to increase the speed and efficiency of operation of the whole process. The software simulation is executed sequentially [36]. On the other hand, complete parallel architecture can be realized in hardware based implementation. Moreover, it is well known that the dedicated FPGA based processor offer high data rate over the general purpose software processors. So in high data throughput application such as video processing applications, FPGAs provide throughput advantages over the general purpose processors due to the massive parallelism capability they offer. The authors of [35] present an assessment of hardware vs. software implementations for

video microscopy. The results show that the hardware based implementations speedup up to  $\sim$ 5 times as compared to the software based implementation. Due to all these advantages, an efficient hardware implementation of division free multi quantizer architecture has been presented in this thesis.

## 1.7 Thesis objectives

The objectives of this thesis is to develop a unified architecture on a single chip that performs 8x8 quantization operation for the six modern video coding standards, (AVS, H.264, VC-1, MPEG-2/4, MJPEG and HEVC). The focus is on the efficient implementation of multiple quantization units; the implementation of the full encoder (or decoder) is not explored. However, integrating multiple quantization units of different standards into a single chip increases the area (size) and decreases the frequency, which has negative impact on the overall performance. Therefore, the ultimate goal is to design and implement a low cost multi quantizer unit that meets the real-time performance requirements. To accomplish this goal, the thesis work is focused on following points:

- Investigate different quantization schemes and parameters to find a relationship among them and consequently develop a generalized quantization algorithm which can be applied to all the six standards.

- 2. Implement the developed algorithm in hardware using Verilog HDL. Circuit sharing strategy is explored to reduce the hardware cost and computational complexity.

- 3. Verify the functionality and synthesize the developed design in both FPGA (Field Programmable Gate Array) and ASIC (Application-Specific Integrated Circuit).

4. Compare the performance of the design with that of the existing designs in terms of hardware count, operational frequency and decoding capability.

## 1.8 Thesis organization

The thesis is organized into six chapters. Chapter 1 gives an overview of need of multicodec system followed by brief description of different video coding standards. It also illustrates the basics of video compression and modern multimedia codec system which in turn presents the need of a multi-quantizer unit which is the main part of this dissertation. Objectives of this thesis dissertation are also described in this chapter.

Chapter 2 presents brief description of quantization operation of six different standards. It includes different quantization equations for different standards, different quantization matrices and other quantization parameters specified by these standards.

In Chapter 3 the generalized Division Free Quantization Algorithm (DFQA) has been described.

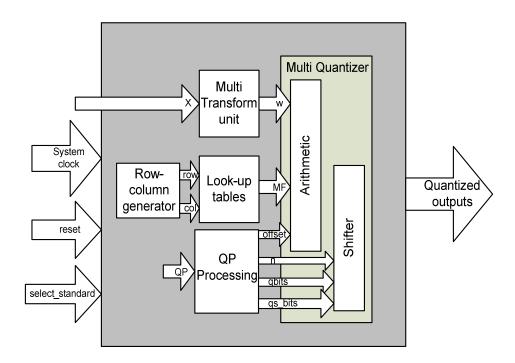

Chapter 4 illustrates the entire circuit shared hardware architecture which includes the multi quantizer unit, arrangement of Look-up tables and the control logic.

The performance comparison is presented in Chapter 5. Finally, Chapter 6 presents conclusion and future works

#### **CHAPTER 2**

### DIFFERENT QUANTIZATION SCHEMES

#### 2.1 Introduction

This chapter presents an overview of quantization schemes of six different video codecs-H.264/AVC, VC-1, AVS, MPEG-2/4, MJPEG and HEVC (under development). Here different quantization parameters, quantization matrices, quantization equations etc. has been described briefly for all the standards.

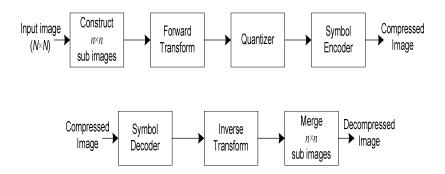

## 2.2 Overview of quantization

Most modern multimedia codecs (both encoder and decoder) employ transform-quantization pair. Transform coding is the basis of all lossy compression which has four basic steps shown by Figure 2.1. A basic transform coder segments the image into smaller square blocks. Each block undergoes a 2-D orthogonal transformation. The transform coefficients are individually quantized and coded (the coefficients with higher energy are finely quantized). The encoder treats the quantized coefficients as symbols which are then entropy encoded. Low frequency components in image correspond to important image features whereas the high frequency components correspond to the details of the image which are less important. The transform isolates various image frequencies. Thus the pixels correspond to high frequencies are quantized heavily. On the other hand, the pixels correspond to lower frequencies are quantized lightly. In some cases, they are not quantized at all.

Figure 2.1. Four basic steps of transform coding

Different video coding standard has different quantization parameters and algorithm specified by that particular standard. The following sections demonstrate a brief description of quantization of different standards.

## 2.3 Quantization in H.264

A key approach to transform and quantization in H.264 is to intentionally magnify the transform in the middle (just before division part of quantization) to involve the right shift operations in both encoder and decoder. This right shift operation is a part of quantization process. Typically quantization loses some resolution in the encoder due to the division operation, thus amplifying the random noise in the decoder due to multiplication of the inverse quantization. In contrast, only right shift operation is performed in both encoder and decoder in H.264 – with no random noise amplified during the decoder's inverse quantization stage. In H.264, the overall quantization is performed by multiplication and right shift operation. This standard defines its own multiplication factor (MF). These MFs are multiplied with the transform coefficients and finally right shifted to obtain the final quantized value. As a result, the quantization in H.264 does not need any direct division operation.

## **2.3.1** 8x8 quantization in H.264

H.264 standard supports both 4x4 and 8x8 quantization. The 8x8 quantization with all the quantization parameter is briefly discussed below. For a given step size, the encoder can perform quantization by the following equation:

$$y = (w[i, j] \cdot MF[i, j] + f \ll qbits) >> qbits, \text{ for } i, j = 0, ..., 7;$$

(2-1)

Where, w denotes the transform coefficient, i and j are the row and column indices, qbits = (16 + QP/6), MF is the Multiplying factor and y denotes the corresponding quantized value (level). QP is the Quantization Parameter which specifies MFs, f is the offset value ranging from 0 to 0.5 and is chosen by the encoder. Here, QP is the quantization parameter ranging from 0 to 51. In case of H.264 as specified in, Multiplication Factor MF depends on m (= QP/6) and the position (i, j) of the element is given by Figure 2.2.

$$MF[m;i,j] = \begin{cases} M_{m0} & \text{for } (i,j) \text{ with } & i = [0,4], j = [0,4] \\ M_{m1} & \text{for } (i,j) \text{ with } & i = [1,3,5,7], j = [1,3,5,7] \\ M_{m2} & \text{for } (i,j) \text{ with } & i = [2,6], j = [2,6] \\ M_{m3} & \text{for } (i,j) \text{ with } & (i = [0,4], j = [1,3,5,7]) \cap (i = [1,3,5,7], j = [0,4]) \\ M_{m4} & \text{for } (i,j) \text{ with } & (i = [0,4], j = [2,6]) \cap (i = [2,6], j = [0,4]) \\ M_{m5} & \text{for } (i,j) \text{ with } & (i = [2,6], j = [1,3,5,7]) \cap (i = [1,3,5,7], j = [2,6]) \end{cases}$$

Figure 2.2. The position specification of MF

According to [7], total of 52 values of Qstep are supported by the standard and these are indexed by QP. The values of Qstep corresponding to each QP are shown in Table 2.1. Note that, Qstep doubles in size for every increment of 6 in QP and Qstep increases by 12.5% for each increment of 1 in QP.

Table 2.1. Quantization step sizes in H.264

| QP    | 0     | 1      | 2 | 3  | 4 | 5     | 6 | 7  | 8     | 9  | 10 | 11 | 12  |

|-------|-------|--------|---|----|---|-------|---|----|-------|----|----|----|-----|

| Qstep | 0.625 | 0.6875 |   |    | 1 | 1.125 |   |    | 1.625 |    | 2  |    | 2.5 |

| QP    |       | 18     |   | 24 |   | 30    |   | 36 |       | 42 |    |    | 51  |

| Qstep |       | 5      |   | 10 |   | 20    |   | 40 |       | 80 |    |    | 224 |

This standard specifies the first six values of MF as shown in Table 2.2. For QP > 5 the factor MF remains unchanged but the value of qbits will change. For example, qbits = 16 for  $0 \le QP \le 5$  (as qbits = 16 + QP/6), qbits = 17 for  $6 \le QP \le 11$  and so on.

Table 2.2. Quantization parameter and the values of MF

| QP | QP MF |       |       |       |       |       |  |  |

|----|-------|-------|-------|-------|-------|-------|--|--|

| 0  | 13107 | 11428 | 20972 | 12222 | 16777 | 15481 |  |  |

| 1  | 11916 | 10826 | 19174 | 11058 | 14980 | 14290 |  |  |

| 2  | 10082 | 8943  | 15978 | 9675  | 12710 | 11985 |  |  |

| 3  | 9362  | 8228  | 14913 | 8931  | 11984 | 11259 |  |  |

| 4  | 8192  | 7346  | 13159 | 7740  | 10486 | 9777  |  |  |

| 5  | 7282  | 6428  | 11570 | 6830  | 9118  | 8640  |  |  |

Table 2.2 is used to generate six 8x8 matrices corresponding to each QP in accordance with the position defined in Figure 2.2. For QP > 5 same matrices will be used. For example, for QP = 6 the same matrix for QP = 0 will be used. Similarly for QP = 7 the same matrix for QP = 1 will be used and so on. Equation (2-2) shows the 8x8 matrix for QP = 0. Other matrices can be developed in the same way.

$$MF_{-}0 = \begin{bmatrix} 13107 & 12222 & 16777 & 12222 & 13107 & 12222 & 16777 & 12222 \\ 12222 & 11428 & 15481 & 11428 & 12222 & 11428 & 15481 & 11428 \\ 16777 & 15481 & 20972 & 15481 & 16777 & 15481 & 20972 & 15481 \\ 12222 & 11428 & 15481 & 11428 & 12222 & 11428 & 15481 & 11428 \\ 13107 & 12222 & 16777 & 12222 & 13107 & 12222 & 16777 & 12222 \\ 12222 & 11428 & 15481 & 11428 & 12222 & 11428 & 15481 & 11428 \\ 16777 & 15481 & 20972 & 15481 & 16777 & 15481 & 20972 & 15481 \\ 12222 & 11428 & 15481 & 11428 & 12222 & 11428 & 15481 & 11428 \end{bmatrix}$$

(2 - 2)

### 2.4 Quantization in AVS

Transform and quantization in AVS is based on 4x4 and 8x8 block. The forward quantization that quantizes the transform coefficients are mainly consists of two steps, (i) scaling and (ii) quantization. The 4x4 and 8x8 quantization scheme has two different 4x4 and 8x8 scale matrices. The structure of 4x4 and 8x8 quantization equations is similar with slightly different quantization parameters.

## 2.4.1 8x8 quantization in AVS

The quantization scheme of AVS standard undergoes through Scaling process followed by the quantization operation on the scaled coefficients. The scaling process to the transform coefficients are defined by equation (2-3) [28]:

$$d = (w[i, j] \cdot scaleM + 1 << 18) >> 19, \text{ for } i, j = 0, ..., 7;$$

(2-3)

The quantization is performed to the scaled coefficient obtained in first step by the equation (2-4). The scale matrix based on [28] is illustrated by (2-5). Value of scale parameter varies for different coefficient position in 8x8 matrix.

$$y = (d[i, j]. MF[QP] + 1 \ll qbits) >> (1 + qbits), \text{ for } i, j = 0,...,7;$$

(2-4)

Where, w denotes the transform coefficient, i and j are the row and column indices, qbits = 14, MF is the Multiplying factor which depends on QP and y denotes the corresponding quantized value (level). QP is the Quantization Parameter ranging from 0 to 63. According to [28] each QP specifies one particular MF described by Table 2.3.

$$ScaleM = \begin{bmatrix} 32768 & 37958 & 36158 & 37958 & 32768 & 37958 & 36158 & 37958 \\ 37958 & 43969 & 41884 & 43969 & 37958 & 43969 & 41884 & 43969 \\ 36158 & 41884 & 39898 & 41884 & 36158 & 41884 & 39898 & 41884 \\ 37958 & 43969 & 41884 & 43969 & 37958 & 43969 & 41884 & 43969 \\ 32768 & 37958 & 36158 & 37958 & 32768 & 37958 & 36158 & 37958 \\ 37958 & 43969 & 41884 & 43969 & 37958 & 43969 & 41884 & 43969 \\ 36158 & 41884 & 39898 & 41884 & 36158 & 41884 & 39898 & 41884 \\ 37958 & 43969 & 41884 & 43969 & 37958 & 43969 & 41884 & 43969 \end{bmatrix}$$

$(2-5)$

Table 2.3. Quantization table for AVS encoder

| QP | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

|----|-------|-------|-------|-------|-------|-------|-------|-------|

| MF | 32768 | 29775 | 27554 | 25268 | 23170 | 21247 | 19369 | 17770 |

| QP | 8     | 9     | 10    | 11    | 12    | 13    | 14    | 15    |

| MF | 16302 | 15024 | 13777 | 12634 | 11626 | 10624 | 9742  | 8958  |

| QP | 16    | 17    | 18    | 19    | 20    | 21    | 22    | 23    |

| MF | 8192  | 7512  | 6889  | 6305  | 5793  | 5303  | 4878  | 4467  |

| QP | 24    | 25    | 26    | 27    | 28    | 29    | 30    | 31    |

| MF | 4091  | 3756  | 3444  | 3161  | 2894  | 2654  | 2435  | 2235  |

| QP | 32    | 33    | 34    | 35    | 36    | 37    | 38    | 39    |

| MF | 2048  | 1878  | 1722  | 1579  | 1449  | 1329  | 1218  | 1117  |

| QP | 40    | 41    | 42    | 43    | 44    | 45    | 46    | 47    |

| MF | 1024  | 939   | 861   | 790   | 724   | 664   | 609   | 558   |

| QP | 48    | 49    | 50    | 51    | 52    | 53    | 54    | 55    |

| MF | 512   | 470   | 430   | 395   | 362   | 332   | 304   | 279   |

| QP | 56    | 57    | 58    | 59    | 60    | 61    | 62    | 63    |

| MF | 256   | 235   | 215   | 197   | 181   | 166   | 152   | 140   |

### 2.5 Quantization in VC-1

VC-1 uses multiple transform sizes but the same quantization rule is applied to all the coefficients. This standard allows both dead-zone and regular uniform quantization. The regular uniform quantization is the simplest but most pervasive method to quantize DCT transform coefficient. In uniform quantization the quantization intervals are identical. The dead zone quantization uses similar principle as the uniform quantization but it has a larger interval, i.e. larger quantization step size than the uniform quantization around zero which is called the "dead

zone". All the coefficients falling in this interval (small coefficients close to zero) are quantized to zero. All the quantization intervals except the dead-zone are of same size - the dead-zone being typically larger. The use of dead-zone leads to substantially bit savings at low bitrates. The dead-zone and regular uniform quantization with the reconstruction level is shown in Figure 2.3 (a) and (b).

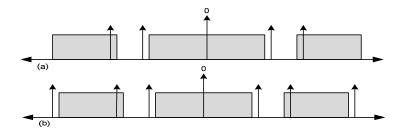

Figure 2.3. VC-1 quantization and dequantization rule showing (a) dead-zone and (b) regular uniform quantization-arrows are reconstructed levels and gray boxes are recommended quantization bins (for alternate intervals)

The reconstruction levels obtained from the regular uniform dequantization are equally spaced. In practice, a dead-zone may be applied on the encoder side, but this is not revealed by the reconstruction set. As this standard allows both dead-zone and regular uniform quantization, the specific type of quantization is signaled at the frame level and appropriate dequantization rule is applied to all coefficients within the frame by the decoder.

There are two inverse quantization methods, (i) uniform quantizer and (ii) non-uniform quantizer [7]. The uniform quantizer method is composed of two sub cases – one for intra DCs and the other for all other ACs. The intra DC is constructed as DC = qDC\*DCStepSize, where qDC is a quantized DC differential value and DCStepSize is shown by Table 2.4.

Table 2.4. Derivation of DC StepSize for uniform and non-uniform quantizer

| Block Type | $MQUANT \leq 2$ | $3 \le MQUANT \le 4$ | 5 ≤ MQUANT   |

|------------|-----------------|----------------------|--------------|

| Luma       | 2 × MQUANT      | 8                    | MQUANT/2 + 6 |

| Chroma     | 2 × MQUANT      | 8                    | MQUANT/2 + 6 |

All other ACs are reconstructed as  $F'' = qF * (2 * MQUANT + \triangle(syntax))$ ; where  $\triangle(syntax) = \text{HALFQP}$  when PQUANT based decoding is performed, whereas  $\triangle(syntax) = 0$  when VOPDQUANT based decoding is performed.

Second, the non-uniform based quantization is performed in two sub cases, one for intra DC and the other for all other ACs. The intra DC in non-uniform quantizer is reconstructed the same way as that of the uniform quantizer. All other ACs are reconstructed as  $F'' = qF * (2*MQUANT + \triangle(syntax)) + sign(qF)*MQUANT$ . The coefficients obtained from the IQ arithmetic are rounded to the nearest integer. The quantization for both uniform and non-uniform quantizer is just the inverse operation of the IQ arithmetic.

However the quantization in VC-1 is user defined. At a high level the quantization process (scalar quantization where each transform coefficient is independently quantized and coded) in VC-1 is similar to the corresponding process in MPEG-2 standard. So they can use the same quantization scheme.

#### 2.6 Quantization in MPEG-2/4

The MPEG-2 video standard defines only the inverse quantization (IQ) process at the decoder [7]. Therefore the quantization (Q) process in the encoder can be inferred from the IQ definition of the decoder. The work in [12] states that MPEG-4 part 2 supports custom

quantization table that can be tuned to content and bit rate like MPEG-2 standard. Hence they can use identical quantization approach.

The quantizer method is composed of two sub cases – one for intra DCs and the other for all other ACs [7]. The intra DC is constructed as DC = qDC\*qs, where qDC is a quantized DC differential value and qs is the quantization step. The intra AC is reconstructed as F'' = (2\*qF\*qs\*qm)/32, where qF is the quantized AC value, qs is the quantization step and qm is the quantization matrix parameter. Hence the quantization process for the intra DC is performed as qDC = DC/qs and that for intra AC is performed as qF = (16\*w)/(qm\*qs), where w is the transform coefficient.

The non-intra DC is reconstructed the same way as the intra DC. However the non-intra AC is reconstructed as  $F'' = ((2*w + sign(qF))*qs*non_qm)/32$ , where  $non_qm$  is the non-intra quantization matrix parameter. Hence the quantization process for the non-intra DC and AC can be derived in the similar way as the intra DC and AC. MPEG-2 defines the intra and non-intra quantization matrices as specified by (2-6) and (2-7).

$$\operatorname{int} ra_{Q} = \begin{bmatrix} 8 & 16 & 19 & 22 & 26 & 27 & 29 & 34 \\ 16 & 16 & 22 & 24 & 27 & 29 & 34 & 37 \\ 19 & 22 & 26 & 27 & 29 & 34 & 38 \\ 22 & 22 & 26 & 27 & 29 & 34 & 37 & 40 \\ 22 & 26 & 27 & 29 & 32 & 35 & 40 & 48 \\ 26 & 27 & 29 & 32 & 35 & 40 & 48 & 58 \\ 26 & 27 & 29 & 34 & 38 & 46 & 56 & 69 \\ 27 & 29 & 35 & 38 & 46 & 56 & 69 & 83 \end{bmatrix}$$

(2-6)

## 2.7 Quantization in Motion JPEG (MJPEG)

The MJPEG standard defines quantization as the division operation of the DCT coefficient coming from the transform unit by the corresponding Q value (specified by the quantization matrix). MJPEG allows specification of Q-matrices that facilitates the allocation of more bits for the representation of coefficients which are visually more significant.

### 2.7.1 8x8 quantization in MJPEG

Although this standard defines quantization as the division of the DCT by the corresponding quantization matrix coefficients, there is no specific quantization matrix defined by this standard. It is progressive of the user to select a quantization matrix. However there are two default quantization matrices specified by [37] for Luma and Chroma. The elements of these matrices are based on the visibility of individual 8x8 DCT basis functions with a viewing distance equal to six times the screen width. The Luminance and chrominance quantization matrices specified by [37] are given by (2-8) and (2-9).

$$Lum\_Q = \begin{bmatrix} 16 & 11 & 10 & 16 & 24 & 40 & 51 & 61 \\ 12 & 12 & 14 & 19 & 26 & 58 & 60 & 55 \\ 14 & 13 & 16 & 24 & 40 & 57 & 69 & 56 \\ 14 & 17 & 22 & 29 & 51 & 87 & 80 & 62 \\ 18 & 22 & 37 & 56 & 68 & 109 & 103 & 77 \\ 24 & 35 & 55 & 64 & 81 & 104 & 113 & 92 \\ 49 & 64 & 78 & 87 & 103 & 121 & 120 & 101 \\ 72 & 92 & 95 & 98 & 112 & 100 & 103 & 99 \end{bmatrix}$$

$$(2-8)$$

$$chrom_{Q} = \begin{bmatrix} 17 & 18 & 24 & 47 & 99 & 99 & 99 & 99 \\ 18 & 21 & 26 & 66 & 99 & 99 & 99 & 99 \\ 24 & 26 & 56 & 99 & 99 & 99 & 99 & 99 \\ 47 & 66 & 99 & 99 & 99 & 99 & 99 & 99 \\ 99 & 99 & 99 & 99 & 99 & 99 & 99 & 99 \\ 99 & 99 & 99 & 99 & 99 & 99 & 99 & 99 \\ 99 & 99 & 99 & 99 & 99 & 99 & 99 & 99 \end{bmatrix}$$

$$(2-9)$$

The quantization is performed as qF = round(F(u,v)/qm(u,v)), where F(u,v) is the transformed coefficient and Q(u,v) is the corresponding matrix coefficient. This standard also defines Quality Factor (QF) to vary the image quality. Quality Factor is a number ranging from 1 to 100. The lower the Quality Factor the more the compression. A Quality Factor of 100 does not mean lossless compression instead it generally represents the Quality Factor that will generate the highest quality compressed image for the scaling algorithm. The work in [38] shows how the varying quality factor changes the JPEG image quality.

### 2.8 Quantization in HEVC (draft stage)

High Efficiency Video Coding (HEVC), successor to H.264/MPEG-4 AVC, is a new standard under development that aims to substantially improve coding efficiency compared to AVC High Profile. The development of this standard has been undertaken by a new Joint Collaborative Team on Video Coding (JCT-VC) formed by the two organizations, ITU-T VCEG

and ISO/IEC MPEG. The HEVC standard is intended to improve significantly better compression capability than the existing H.264/AVC (ITU-T H.264 ISO/IEC MPEG-4 part-10) standard. The quantization in HEVC does not use the division operation rather it uses multiplication and shift operation to replace the division operation similar to H.264 standard. This developing standard supports several transform sizes ranging from 4x4 to 32x32. However the quantization/dequantization scheme is same for all the transform sizes where the multiplier depends on value of the Quantization Parameter and the shifts depend on the transform size. As the standard has not yet been finalized, some quantization algorithm proposals which are consistent to each other are described below:

## 2.8.1 Proposal by Samsung Electronics, Ltd, FastVDO

According to [39], the quantization is implemented by the equation (2-10):

$$qF = (w*MF + offset) >> (21 + QP / 6 - M - (B - 8))$$

(2-10)

Where, offset = (1 << (M-2+(B-8))) and B =internal bit depth (8 or 10 bit),  $M = \log_2(N)$ , N = transform size, MF = f(QP/6). QP is the quantization parameter ranging from 0 to 51. The values of MF are given below:

$$MF = \{26214, 23302, 20560, 18396, 16384, 14564\}$$

(2-11)

For QP = 0 to 5, QP/6=0 and hence the corresponding MF = 26214. Similarly for QP/6=5, corresponding MF = 14564.

Dequantizer equation is specified as follows:

q = ((qF \* MF' << (QP/6)) + offset) >> (M - 1(B - 8)), where offset is same as the quantizer and MF' = g(QP/6) which is specified as follows:

$$MF' = \{40, 45, 51, 57, 64, 72\}$$

(2-12)

# 2.8.2 Proposal by Cisco Systems, Texas Instrument Inc

The quantization is implemented by the following equation based on [33] which is similar to the proposal of Samsung Electronics discussed earlier:

$$qF = (w*MF + offset) >> (21 + QP/6 - M - (B-8))$$

(2-13)

Where offset = (1 << (M-2) + (B-8)), B = internal bit depth (8 or 10 bit),  $M = \log_2(N)$ , N = transform size, MF = f(QP/6). QP is the quantization parameter ranging from 0 to 51. The values of MF are given below:

$$MF = \{26214, 23302, 20560, 18396, 16384, 14564\}$$

(2-14) For

QP = 0 to 5, QP/6=0 and hence the corresponding MF = 26214. Similarly for QP/6=5, corresponding MF = 14564.

The Dequantizer equation is also same as the proposal of Samsung Electronics, Ltd, FastVDO (JCTVC-F251). Moreover, Cisco Systems and Texas Instrument Inc. proposed the same quantization and dequantization equation in their previous proposals in JCTVC-F446 [40] and JCTVC-E243 [41] which are similar to the proposal of Samsung Electronics, LTD, FastVDO [39].

### **CHAPTER 3**

### PROPOSED ALGORITHM

### 3.1 Introduction

This chapter describes the Division free Quantization Algorithm (DFQA) which is applicable to five popular video standards (H.264, AVS, VC-1, MPEG-2/4 and MJPEG) and standard HEVC under development. Although each standard defines a specific quantization scheme, here a generalized Division free Quantization Algorithm (DFQA) is developed which is applicable to any of the six standards. This algorithm is completely division free to make it simple in terms of hardware overhead and to be applicable to all standards those define quantization as division operation or multiplication followed by shift operation.

## 3.2 Proposed Division Free Quantization Algorithm (DFQA)

Quantization is the division of the transform coefficient from the transform unit by the corresponding Q-value to reduce the bit rate. But in H.264, AVS and HEVC, it is done by multiplication and right shift operation. Hence these standards define their own Multiplication Factors (*MF*). These MFs are multiplied with the transform coefficients and finally right shifted. However, the quantization in VC-1, MPEG-2/4 and MJPEG is defined as division operation only (using 8x8 matrices). As a result, it is a challenge to establish a relationship that is general enough to merge all these schemes. All the quantization schemes and parameters of six different standards are observed carefully and a relationship is developed among them. To integrate VC-1, MPEG-2/4 and MJPEG with the newer standards such as H.264, AVS and HEVC, the division operation of VC-1, MPEG-2/4 and MJPEG is replaced with multiplication, addition and shift operation.

In light of this observation, an equation to calculate the multiplication factor (*MF*) for VC-1, MPEG-2/4 and MJPEG is developed to make the quantization operation of these standards compatible to those of H.264, AVS and HEVC. Finally a generalized algorithm is developed for all these six standards.

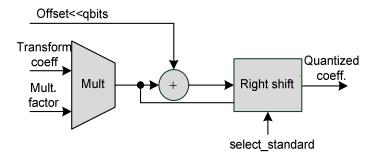

## 3.2.1 Steps of DFQA

Our DFQA is divided into three steps. The third and final stage gives the quantized level. These steps and the parameters are described below using equation (3-1) to (3-3).

Step 1:

$$p = (w[i, j] << r) \cdot MF[i, j], \text{ for } i, j = 0, ..., 7;$$

(3-1)

Step 2:

$$q = p + (offset << qbits); (3-2)$$

Step 3:

$$y = q \gg (n + qs\_bit); \tag{3-3}$$

Where, w denotes the transform coefficient, MF is the Multiplying factor and y denotes the corresponding quantized value (level), << r = left shift by r bits,  $>> (n+qs\_bit) =$  right shift by  $(n+qs\_bit)$  bits. QP is the Quantization Parameter which specifies MFs,  $M = \log 2(N)$ , N is the transform size, DB = B - 8, B is source bit width (8 or 10 bits according to [33]). In the next sections, the general DFQA is applied to individual codecs including examples for each of them.

## 3.2.2 Equation to calculate MF for VC-1, MPEG-2/4 and MJPEG

The proposed algorithm exploits similar quantization parameters and equations for VC-1 and MPEG-2 [9]. Moreover, according to [12] MPEG-4 part 2 can also use similar quantization approach as it supports custom quantization table that can be tuned to content and bit rate like MPEG-2. So, in the proposed algorithm the same quantization scheme for both MPEG-2 and MPEG-4 part 2 is used and referred to as the quantization of MPEG-2/4. As a result, the value of *MF* of VC-1 and MPEG-2/4 is similar in this work. However, the *MF* is different for MJPEG standard. The *MF* for VC-1/MPEG-2/4 is calculated from the intra matrix described in Chapter 2 by equation (2-6). The *MF* for MJPEG is calculated from the luminance matrix shown by equation (2-8). For the calculation of *MF*, we follow the simple equation given by (3-4):

$$MF(i, j) = \text{round}((2 \land n) / qm(i, j)); \text{ where } i, j = 0, 1, ..., 7$$

(3-4)

Where n is the same parameter used in (3-3) which are described in Table 3.1 and qm(i,j) is the Q matrix coefficient described in equation (2-6) and (2-8) for VC-1/MPEG-2/4 and MJPEG respectively. The example of MF calculations for VC-1/MPEG-2/4 and MJPEG are given in section 3.2.5 and 3.2.6 respectively.

# 3.2.3 DFQA applied to H.264

In this section, the generalized DFQA is applied to perform the quantization operation in H.264. Firstly, the transform coefficients coming from the transform unit are directly multiplied by MF as the value of r is equal to 0 for this standard and hence no left shift operation is applied to the transform coefficients. In the second stage, *offset* is left shifted by *qbits* and then added to the result coming from the first stage. Here, the *offset* value ranges between 0 and 0.5 as specified by the standard. Moreover *qbits* is specified as (16+QP/6). Here, QP is the quantization