# A Low-Power Quadrature Digital Modulator ${\rm in}~ {\rm 0.18 \mu m}~ {\rm CMOS}$

A Thesis Submitted to the College of

Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

$\mathbf{b}\mathbf{y}$

Song Hu

<sup>©</sup> Copyright Song Hu, April 2007. All rights reserved.

#### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering University of Saskatchewan Saskatoon, Saskatchewan, Canada S7N 5A9

#### ABSTRACT

Quadrature digital modulation techniques are widely used in modern communication systems because of their high performance and flexibility. However, these advantages come at the cost of high power consumption. As a result, power consumption has to be taken into account as a main design factor of the modulator.

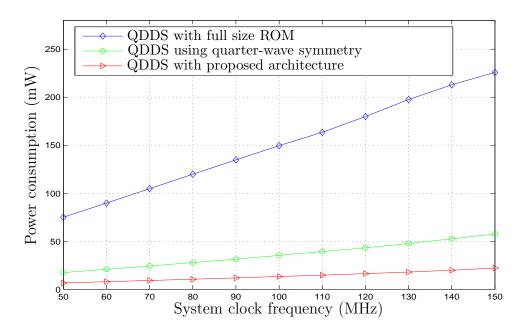

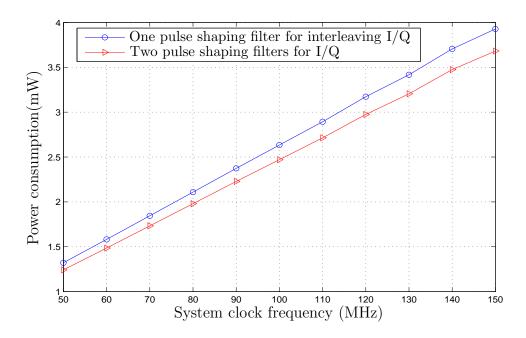

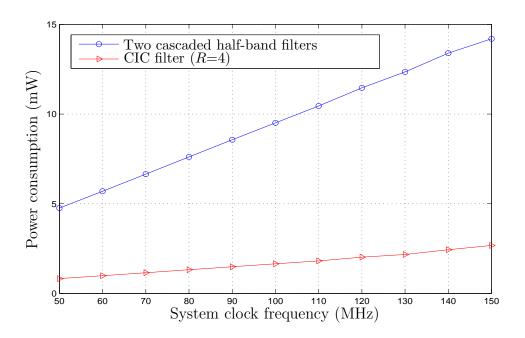

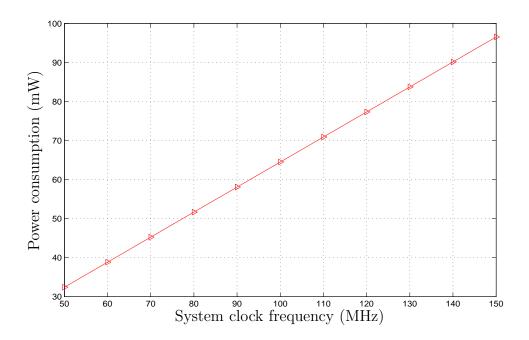

In this thesis, a low-power quadrature digital modulator in  $0.18\mu m$  CMOS is presented with the target system clock speed of 150 MHz. The quadrature digital modulator consists of several key blocks: quadrature direct digital synthesizer (QDDS), pulse shaping filter, interpolation filter and inverse sinc filter. The design strategy is to investigate different implementations for each block and compare the power consumption of these implementations. Based on the comparison results, the implementation that consumes the lowest power will be chosen for each block. First of all, a novel low-power QDDS is proposed in the thesis. Power consumption estimation shows that it can save up to 60% of the power consumption at 150 MHz system clock frequency compared with one conventional design. Power consumption estimation results also show that using two pulse shaping blocks to process I/Q data, cascaded integrator comb (CIC) interpolation structure, and inverse sinc filter with modified canonic signed digit (MCSD) multiplication consume less power than alternative design choices. These low-power blocks are integrated together to achieve a low-power modulator. The power consumption estimation after layout shows that it only consumes about 95 mW at 150 MHz system clock rate, which is much lower than similar commercial products.

The designed modulator can provide a low-power solution for various quadrature modulators. It also has an output bandwidth from 0 to 75 MHz, configurable pulse shaping filters and interpolation filters, and an internal  $\sin(x)/x$  correction filter.

#### ACKNOWLEDGEMENTS

I would like to express my most special gratitude to my supervisor Professor Daniel Teng for his patient guidance and financial support during this research. Some discussions with him inspired me a lot, not only for this research but also for my future professional career. Another special gratitude goes to CMC microsystems for their software and tutorial.

I would like to thank Professor Ron Bolton who taught me VLSI class and also gave me some suggestions for my research. I also want to thank all the other professors who taught me classes at the University of Saskatchewan.

Finally, I would like to thank my wife, Li Sha, and my parents, Yang Guoqing and Hu Jiyuan, for their support. Their love and patience give me a lot of faith during some difficult times.

## **DEDICATION**

This thesis is dedicated to my wife and my parents.

## Contents

| Ρ.               | ERM   | IISSION TO USE                        | j    |

|------------------|-------|---------------------------------------|------|

| $\mathbf{A}$     | BST   | RACT                                  | i    |

| $\mathbf{A}$     | CKN   | IOWLEDGEMENTS                         | iii  |

| D                | EDIO  | CATION                                | iv   |

| $\mathbf{T}_{2}$ | ABL   | E OF CONTENTS                         | v    |

| Ll               | IST ( | OF FIGURES                            | ix   |

| Ll               | IST ( | OF TABLES                             | xiii |

| $\mathbf{A}$     | BBR   | EVIATIONS                             | xiv  |

| 1                | Inti  | roduction                             | 1    |

|                  | 1.1   | Research motivation                   | 2    |

|                  | 1.2   | Research objectives                   | 3    |

|                  | 1.3   | Thesis outline                        | 4    |

| 2                | Bac   | ekground                              | 5    |

|                  | 2.1   | Quadrature direct digital synthesizer | 5    |

|                  | 2.2   | Pulse shaping filter                  | 8    |

|                  | 2.3   | Interpolation filter                  | 11   |

|                  | 2.4   | Modulation                            | 16   |

|                  | 2.5   | Digital to analog converter (DAC)     | 19   |

|                  | 2.6   | Inverse sinc filter                   | 20   |

|   | 2.7  | Summ    | nary                                              | 23 |

|---|------|---------|---------------------------------------------------|----|

| 3 | Inte | egrated | d Circuit Design Flow                             | 24 |

|   | 3.1  | Digita  | al IC design flow                                 | 25 |

|   |      | 3.1.1   | Front-end design flow                             | 25 |

|   |      | 3.1.2   | Back-end design                                   | 28 |

|   | 3.2  | Summ    | nary                                              | 31 |

| 4 | Circ | cuit D  | esign and Low Power Considerations                | 32 |

|   | 4.1  | Quadi   | rature digital modulator                          | 32 |

|   | 4.2  | QDDS    | 5                                                 | 34 |

|   |      | 4.2.1   | ROM compression                                   | 34 |

|   |      | 4.2.2   | Quadrature outputs                                | 41 |

|   | 4.3  | Pulse   | shaping filter                                    | 44 |

|   |      | 4.3.1   | Polyphase structure                               | 44 |

|   |      | 4.3.2   | Design considerations of the pulse shaping filter | 45 |

|   |      | 4.3.3   | Quadrature processing                             | 46 |

|   | 4.4  | Interp  | polation filter                                   | 49 |

|   |      | 4.4.1   | Design of CIC filter                              | 49 |

|   |      | 4.4.2   | Design of half-band filter                        | 52 |

|   | 4.5  | Invers  | e sinc filter                                     | 54 |

|   |      | 4.5.1   | Multiplication for inverse sinc filter            | 57 |

|   |      | 4.5.2   | Clock gating                                      | 58 |

|   | 4.6  | Multij  | pliers                                            | 61 |

|   | 4.7  | Summ    | nary                                              | 64 |

| 5 | Per  | formaı  | nce Evaluation                                    | 65 |

|   | 5.1  | High-l  | level power estimation                            | 65 |

|   |      | 5.1.1   | Sources of power consumption                      | 65 |

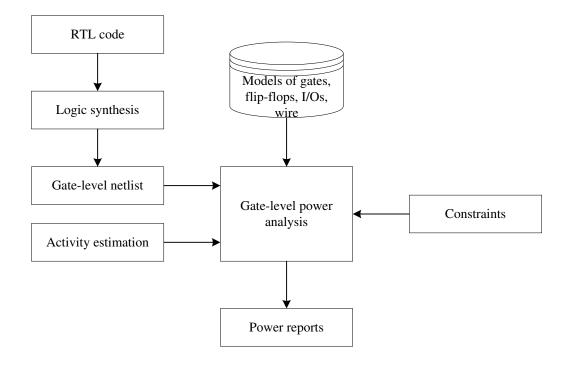

|   |      | 5.1.2   | Power estimation and analysis flow                | 66 |

|   |      | 5.1.3   | Power estimation in logic synthesizer             | 67 |

|              | 5.2                  | Performance of QDDS                                        |  |  |  |  |

|--------------|----------------------|------------------------------------------------------------|--|--|--|--|

|              |                      | 5.2.1 Output spectrum                                      |  |  |  |  |

|              |                      | 5.2.2 Power consumption                                    |  |  |  |  |

|              | 5.3                  | Performance of pulse shaping filter                        |  |  |  |  |

|              | 5.4                  | Performance of interpolation filter                        |  |  |  |  |

|              |                      | 5.4.1 Frequency response                                   |  |  |  |  |

|              |                      | 5.4.2 Power consumption                                    |  |  |  |  |

|              | 5.5                  | Performance of inverse sinc filter                         |  |  |  |  |

|              | 5.6                  | Summary                                                    |  |  |  |  |

| 6            | System Integration 7 |                                                            |  |  |  |  |

|              | 6.1                  | Functional verification                                    |  |  |  |  |

|              |                      | 6.1.1 Testing model                                        |  |  |  |  |

|              |                      | 6.1.2 QDDS                                                 |  |  |  |  |

|              |                      | 5.1.3 Pulse shaping filter                                 |  |  |  |  |

|              |                      | 6.1.4 CIC filter                                           |  |  |  |  |

|              |                      | 6.1.5 Modulator                                            |  |  |  |  |

|              | 6.2                  | Power consumption estimation                               |  |  |  |  |

|              |                      | 6.2.1 Power consumption estimation after logic synthesis 8 |  |  |  |  |

|              |                      | 3.2.2 Power consumption estimation after layout            |  |  |  |  |

|              | 6.3                  | Summary                                                    |  |  |  |  |

| 7            | Con                  | clusions 9                                                 |  |  |  |  |

|              | 7.1                  | Conclusions                                                |  |  |  |  |

|              | 7.2                  | Future work                                                |  |  |  |  |

| $\mathbf{R}$ | EFEI                 | ENCES 9                                                    |  |  |  |  |

| $\mathbf{A}$ | PPE:                 | DICES 9                                                    |  |  |  |  |

| $\mathbf{A}$ | Scri                 | ts for Digital IC Design 9                                 |  |  |  |  |

|              | A 1                  | A script for invoking NCsim in batch mode                  |  |  |  |  |

| A.2 | A script for invoking Synopsys Design Compiler in batch mode     | 98 |

|-----|------------------------------------------------------------------|----|

| A.3 | A script for invoking Cadence PKS in batch mode for timing opti- |    |

|     | mization                                                         | 99 |

# List of Figures

| 1.1  | Analog transmitter                                                  | 2  |

|------|---------------------------------------------------------------------|----|

| 1.2  | Hybrid implementation                                               | 2  |

| 2.1  | Digital quadrature modulator                                        | 5  |

| 2.2  | Block diagram of a basic DDS                                        | 6  |

| 2.3  | Digital phase wheel. As the vector rotates around the wheel, a cor- |    |

|      | responding sine wave is being generated                             | 6  |

| 2.4  | Raised cosine pulse and spectrum.                                   | 9  |

| 2.5  | Signal flow graph of the direct form structure FIR filter           | 11 |

| 2.6  | An example of 1-to-4 upsampling. "x" shows the input binary data    |    |

|      | and "o" shows the output after 1-to-4 upsampling                    | 12 |

| 2.7  | Output sequence of a SQRC filter. "x" shows the input binary data   |    |

|      | and "o" shows the output sequence                                   | 12 |

| 2.8  | Block diagram of the CIC interpolation filter                       | 13 |

| 2.9  | Impulse response and frequency response of a half band FIR filter   |    |

|      | with the length of 21                                               | 15 |

| 2.10 | I-Q format                                                          | 16 |

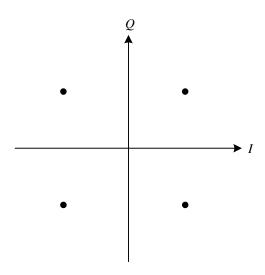

| 2.11 | QPSK constellation                                                  | 18 |

| 2.12 | 16-QAM square constellation                                         | 18 |

| 2.13 | Conceptual block diagram of a DAC                                   | 20 |

| 2.14 | Ideal input output characteristics for a 2 bit DAC                  | 20 |

| 2.15 | Output spectrum of a real world DAC                                 | 22 |

| 2.16 | Amplitude response of the ideal inverse sinc filter                 | 22 |

| 3 1  | Block diagram of the front-end design flow                          | 26 |

| 3.2  | One example to compare the circuit before and after scan chain in-           |    |

|------|------------------------------------------------------------------------------|----|

|      | sertion. After adding scan circuitry, the design has two additional          |    |

|      | inputs, sc_in and sc_en, and one additional output, sc_out. These            |    |

|      | extra ports will be used when the design is in scan mode                     | 29 |

| 3.3  | Block diagram of the back-end design flow                                    | 30 |

| 4.1  | The detailed block diagram of the designed quadrature digital mod-           |    |

|      | ulator                                                                       | 33 |

| 4.2  | ROM design using quarter-wave symmetry                                       | 34 |

| 4.3  | Phase wheel comparison between no phase offset and $\frac{1}{2}$ -LSB phase  |    |

|      | offset                                                                       | 35 |

| 4.4  | Error comparison between no phase offset and $\frac{1}{2}$ -LSB phase offset | 35 |

| 4.5  | Curves of sine-phase difference, double trigonometric approximation          |    |

|      | and QLA and the error curves of double trigonometric approximation           |    |

|      | and QLA                                                                      | 39 |

| 4.6  | Sine phase to amplitude converter using QLA method                           | 40 |

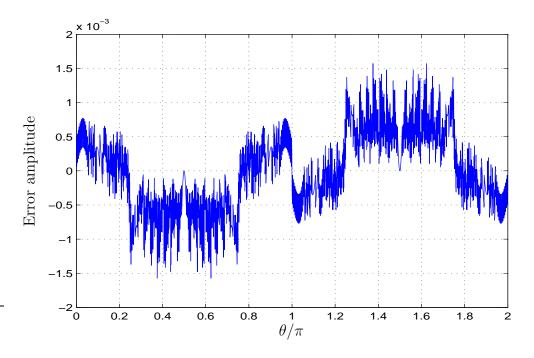

| 4.7  | Errors for QLA sine phase to amplitude converter                             | 41 |

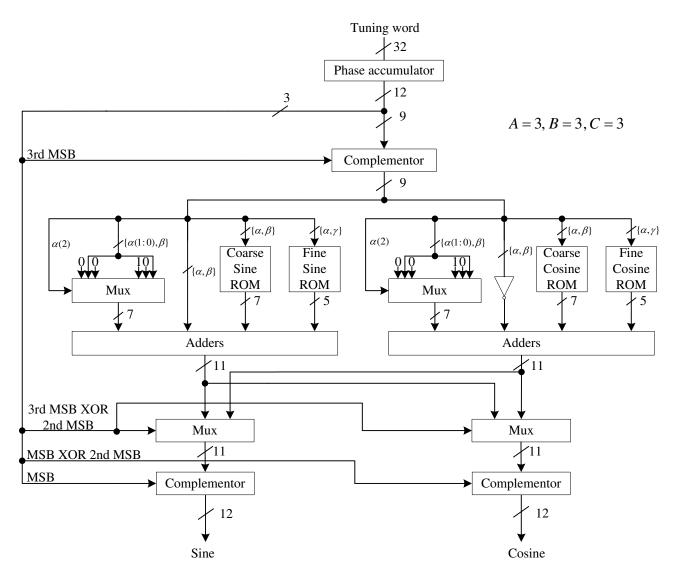

| 4.8  | Proposed QDDS architecture                                                   | 43 |

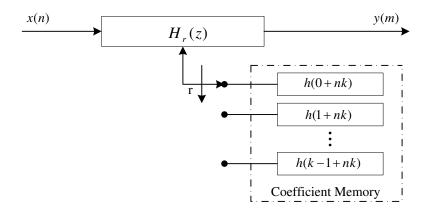

| 4.9  | An efficient implementation of 1-to- $k$ upsampling polyphase filter         | 45 |

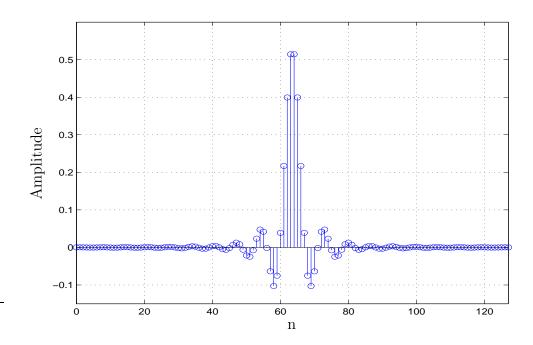

| 4.10 | An example of the SQRC impulse response                                      | 47 |

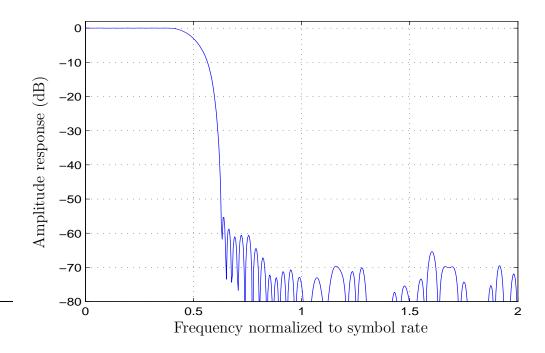

| 4.11 | The frequency response of the SQRC filter whose impulse response             |    |

|      | is shown in Figure 4.10                                                      | 47 |

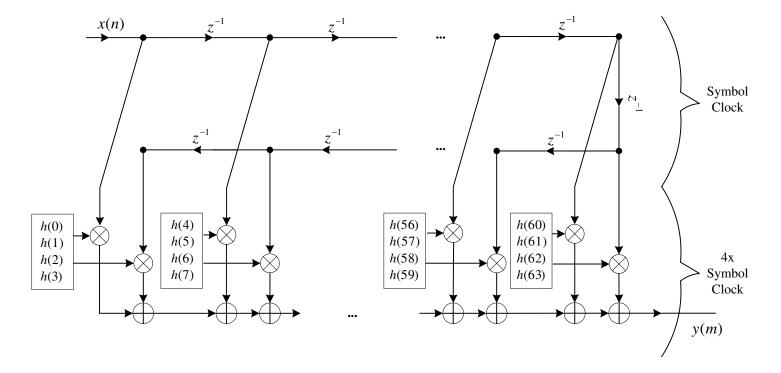

| 4.12 | Block diagram of the SQRC filter                                             | 48 |

| 4.13 | Pipelined CIC interpolation filter                                           | 50 |

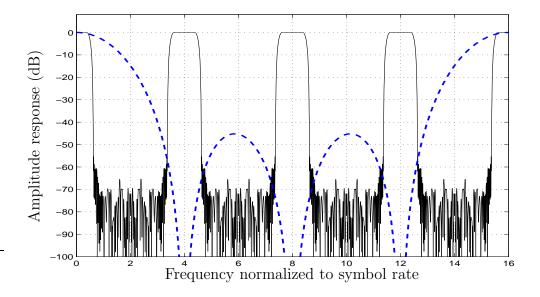

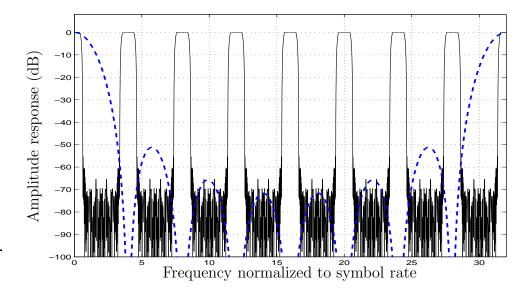

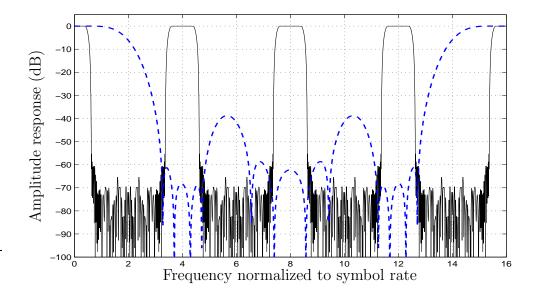

| 4.14 | Spectral response of 1-to-4 CIC interpolator. Solid line shows the           |    |

|      | periodic spectrum of the zero packed time series and dashed line             |    |

|      | shows the frequency response of the CIC filter with rate change factor       |    |

|      | of 4                                                                         | 51 |

| 4.15 | Spectral response of 1-to-8 CIC interpolator. Solid line shows the      |    |

|------|-------------------------------------------------------------------------|----|

|      | periodic spectrum of the zero packed time series and dashed line        |    |

|      | shows the frequency response of the CIC filter with rate change factor  |    |

|      | of 8                                                                    | 51 |

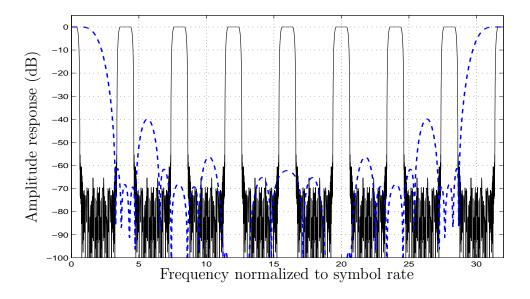

| 4.16 | Spectral response of two cascaded half-band FIR filters. Solid line     |    |

|      | shows the periodic spectrum of the zero packed time series and          |    |

|      | dashed line shows the frequency response of the two cascaded half-      |    |

|      | band FIR filters                                                        | 53 |

| 4.17 | Spectral response of three cascaded half-band FIR filters. Solid        |    |

|      | line shows the periodic spectrum of the zero packed time series and     |    |

|      | dashed line shows the frequency response of the three cascaded half-    |    |

|      | band FIR filters                                                        | 53 |

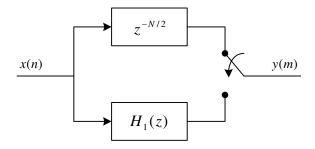

| 4.18 | Polyphase half-band filter                                              | 54 |

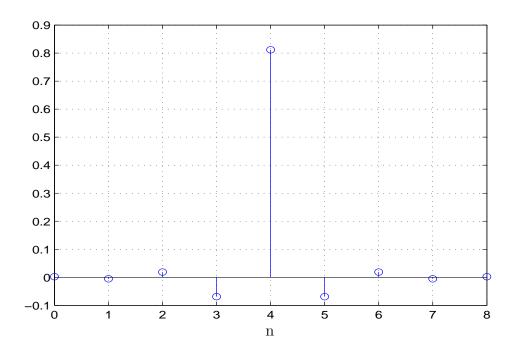

| 4.19 | Impulse response of the designed inverse sinc filter                    | 55 |

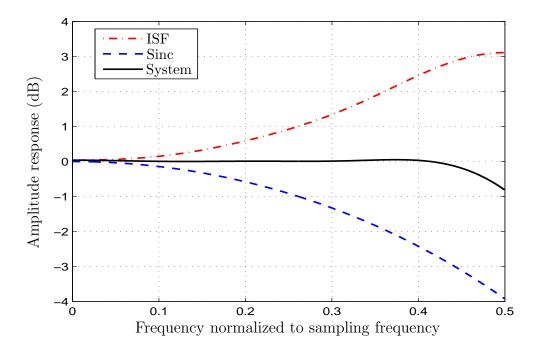

| 4.20 | Frequency responses of the sinc distortion, ISF and the combined        |    |

|      | system                                                                  | 55 |

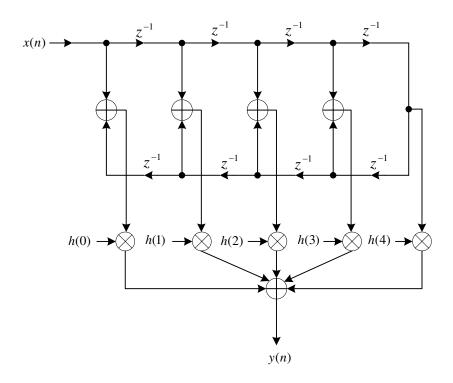

| 4.21 | Signal flow graph of symmetrical FIR filter                             | 57 |

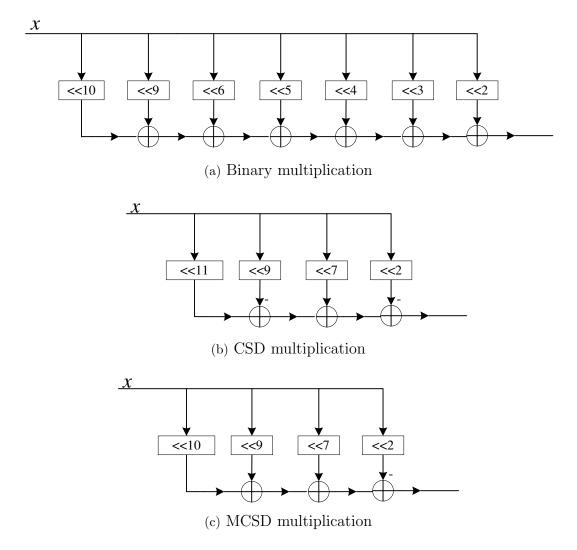

| 4.22 | Comparison of the three different ways to implement $x \times h(4)$     | 59 |

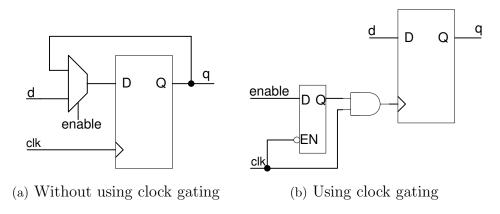

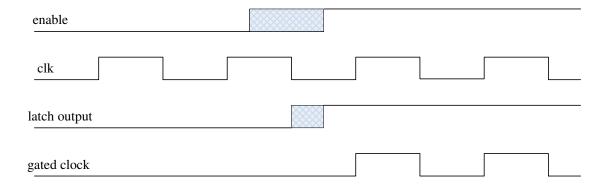

| 4.23 | Implementation comparison between a flip-flop without clock gating      |    |

|      | and with clock gating.                                                  | 60 |

| 4.24 | The mechanism of using latch to prevent the glitch on the gated clock   |    |

|      | net                                                                     | 61 |

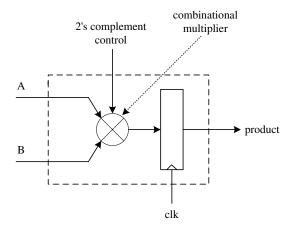

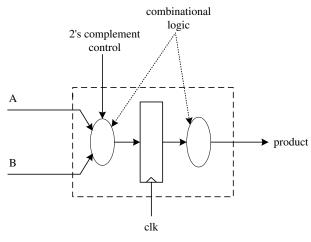

| 4.25 | Block diagram of DW02_mult_2_stage before register retiming and         |    |

|      | after register retiming                                                 | 63 |

| 5.1  | Power estimation in logic synthesizer                                   | 68 |

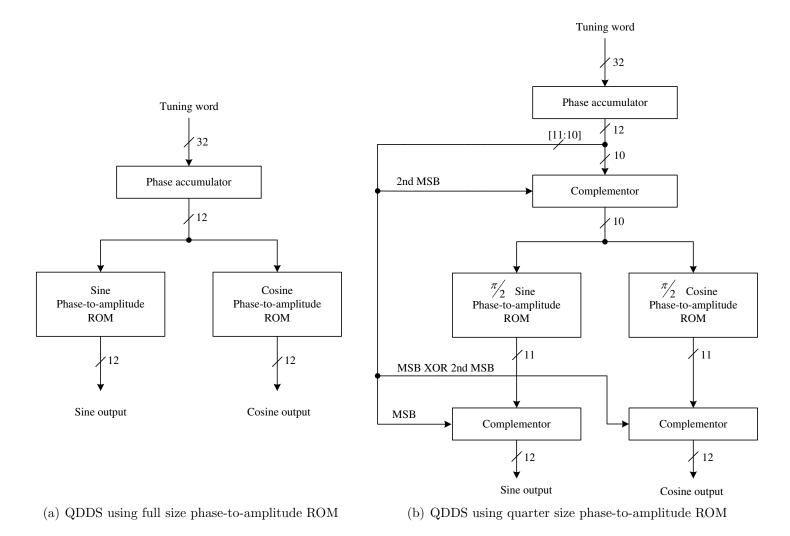

| 5.2  | Two conventional QDDS implementations                                   | 69 |

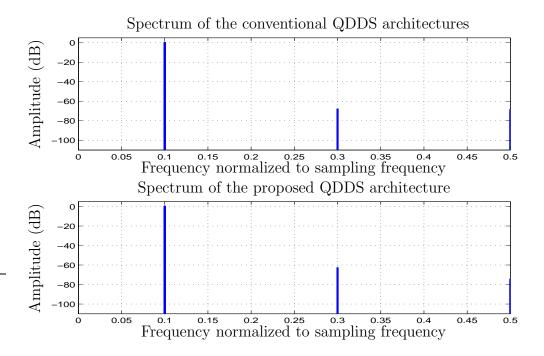

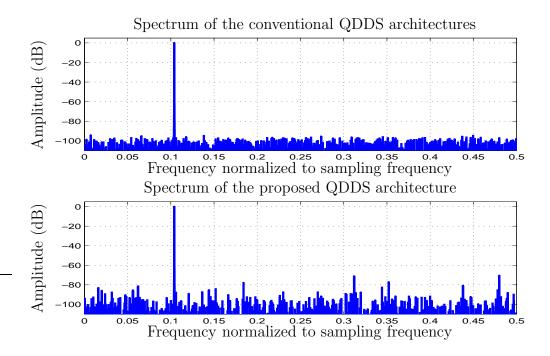

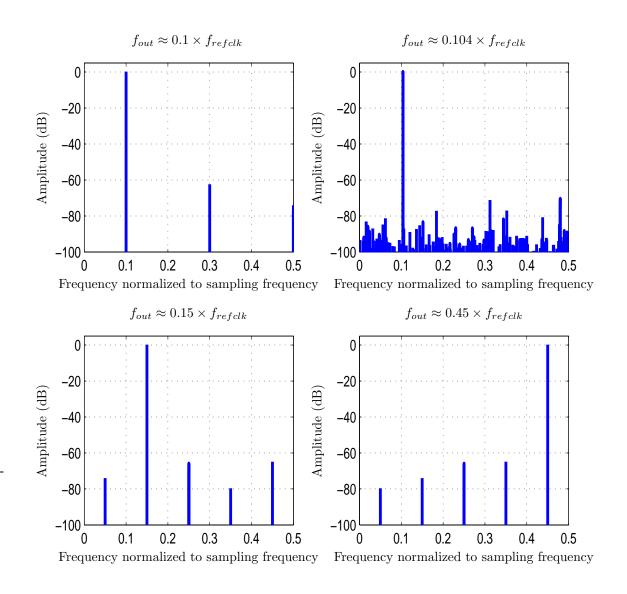

| 5.3  | Spectrum of the QDDS output $(f_{out} \approx 0.1 \times f_{refclk})$   | 71 |

| 5.4  | Spectrum of the QDDS output $(f_{out} \approx 0.104 \times f_{refclk})$ | 71 |

| 5.5  | Power consumption comparison for 3 different QDDS architectures.        | 72 |

| 5.6  | Power consumption comparison for 2 different pulse shaping filter                    |    |

|------|--------------------------------------------------------------------------------------|----|

|      | implementations (interpolation ratio of interpolation filter=4)                      | 73 |

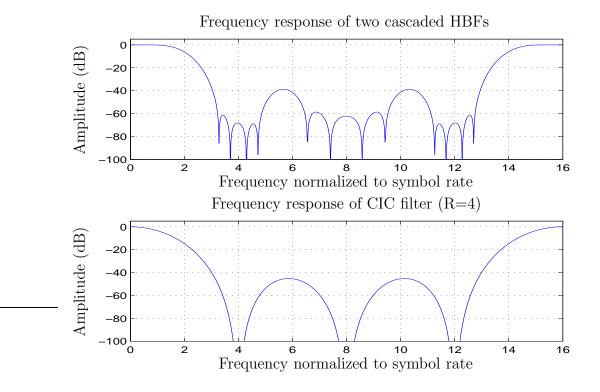

| 5.7  | Comparison of HBF and CIC frequency response                                         | 74 |

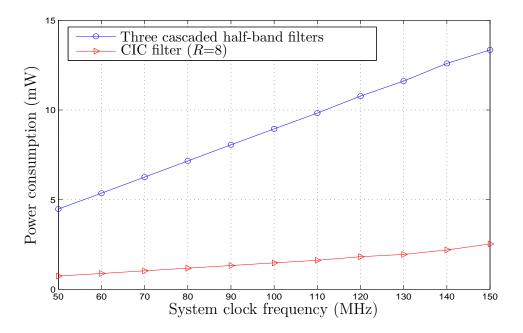

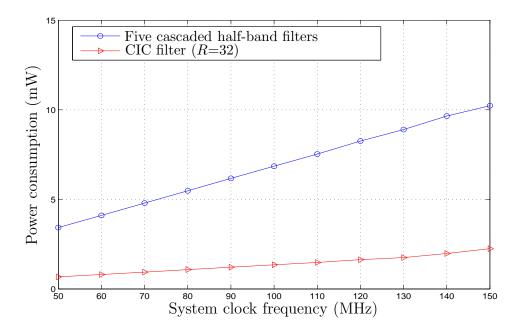

| 5.8  | Power consumption comparison for two interpolation filters with the                  |    |

|      | interpolation ratio of 4                                                             | 75 |

| 5.9  | Power consumption comparison for two interpolation filters with the                  |    |

|      | interpolation ratio of 8                                                             | 75 |

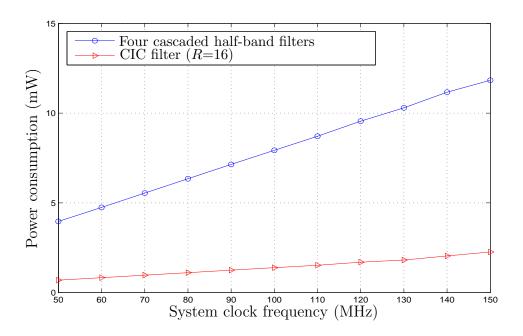

| 5.10 | Power consumption comparison for two interpolation filters with the                  |    |

|      | interpolation ratio of 16                                                            | 76 |

| 5.11 | Power consumption comparison for two interpolation filters with the                  |    |

|      | interpolation ratio of 32                                                            | 76 |

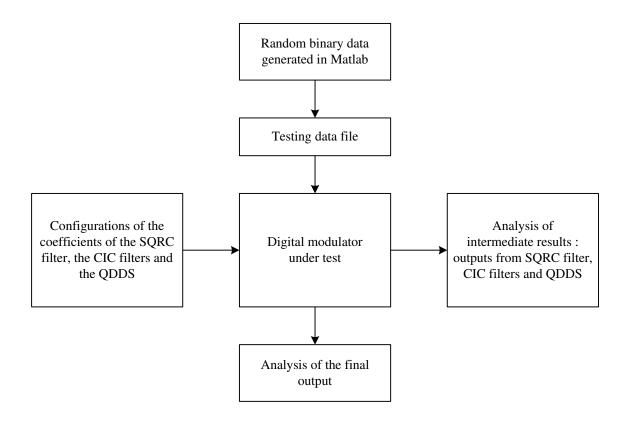

| 6.1  | Testing model                                                                        | 80 |

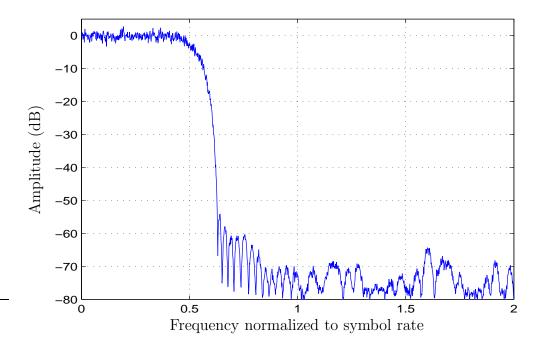

| 6.2  | Spectrum of QDDS outputs                                                             | 81 |

| 6.3  | Signal spectrum after pulse shaping filter                                           | 82 |

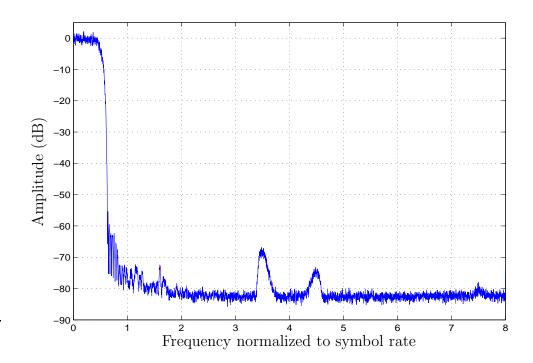

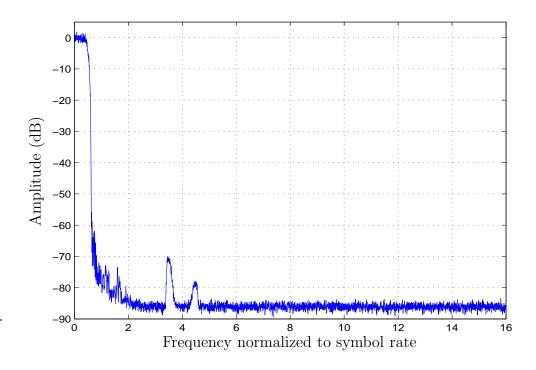

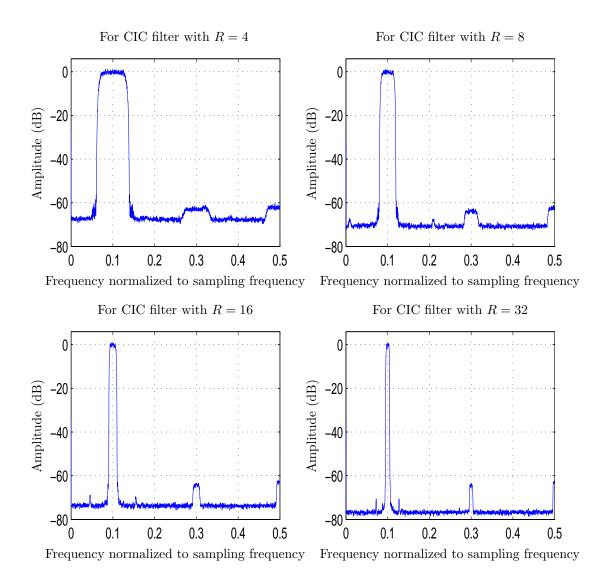

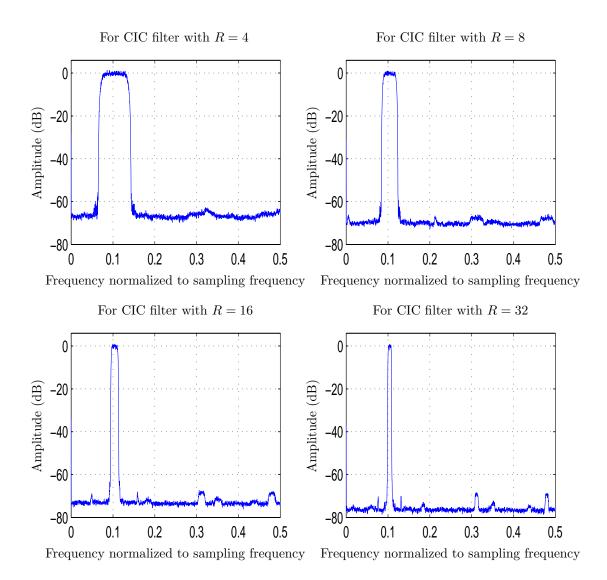

| 6.4  | Signal spectrum after CIC filter $(R = 4)$                                           | 83 |

| 6.5  | Signal spectrum after CIC filter (R=8)                                               | 83 |

| 6.6  | Output signal spectrum of the designed modulator with $f_{out} \approx 0.1 \times$   |    |

|      | $f_{refclk}$                                                                         | 85 |

| 6.7  | Output signal spectrum of the designed modulator with $f_{out} \approx 0.104 \times$ |    |

|      | $f_{refclk}$                                                                         | 86 |

| 6.8  | Power consumption estimation of the designed modulator after logic                   |    |

|      | synthesis                                                                            | 87 |

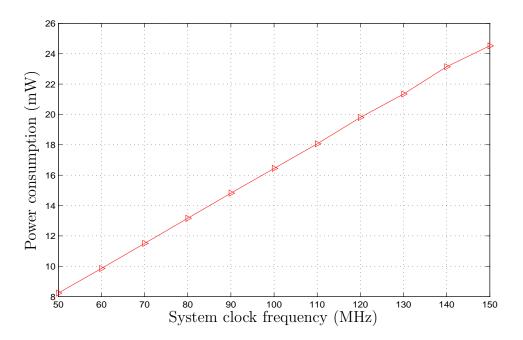

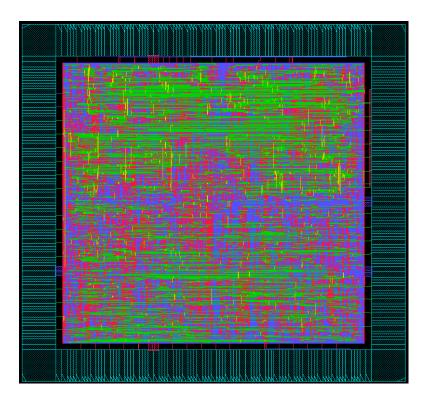

| 6.9  | Layout of the designed modulator                                                     | 88 |

| 6.10 | Power consumption estimation of the designed modulator after layout.                 | 89 |

## List of Tables

| 4.1 | Comparison between different $A, B, C$ partitions                    | 37 |

|-----|----------------------------------------------------------------------|----|

| 4.2 | Comparison between various sine approximation methods to reduce      |    |

|     | the coarse ROM output bits                                           | 39 |

| 4.3 | Coefficients for the designed inverse sinc filter                    | 56 |

| 4.4 | Comparison of binary, CSD and MCSD representations for the coef-     |    |

|     | ficients of the inverse sinc filter                                  | 58 |

| 4.5 | Verilog codes of a flip-flop without clock gating and one with clock |    |

|     | gating                                                               | 60 |

| 5.1 | Power consumption comparison of ISF using CSD multiplication and     |    |

|     | MCSD multiplication                                                  | 77 |

| 6.1 | Comparison of different modulator ICs                                | 89 |

#### **ABBREVIATIONS**

ASIC Application Specific Integrated Circuit

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

BPF Band-Pass Filter

CIC Cascaded Integrator Comb

CMOS Complementary Metal Oxide Silicon

CSD Canonic Signed Digit

DAC Digital to Analog Converter

DDS Direct Digital Synthesizer

DRC Design Rule Check

DSP Digital Signal Processor

FFT Fast Fourier Transform

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FS Full Scale

GUI Graphical User Interface

HBF Half-Band Filter

HDL Hardware Descriptive Language

IC Integrated Circuit

IF Intermediate Frequency

IP Intellectual Property

ISF Inverse Sinc Filter

ISI Intersymbol Interference

ITRS International Technology Roadmap for Semiconductors

LO Local Oscillator

LPF Low-Pass Filter

LSB Least Significant Bit

LVS Layout Versus Schematic

MCSD Modified Canonic Signed Digit

MSB Most Significant Bit

PKS Physically Knowledgable Synthesis

QAM Quadrature Amplitude Modulation

QDDS Quadrature Direct Digital Synthesizer

QLA Quad Line Approximation

QPSK Quadrature Phase Shift Keying

RF Radio Frequency

RTL Register Transfer Level

SNR Signal to Noise Ratio

SOC System on Chip

SQRC Squared Root Raised Cosine

VGA Variable Gain Amplifier

VLSI Very Large Scale Integration

## Chapter 1

## Introduction

Transmitter and receiver are two major components for all the communication systems. The basic function of the transmitter is to take the information bearing signal produced by the source of information and modify it into a form suitable for transmission over a channel. The receiver operates on the received signal to produce an estimate of the original information bearing signal.

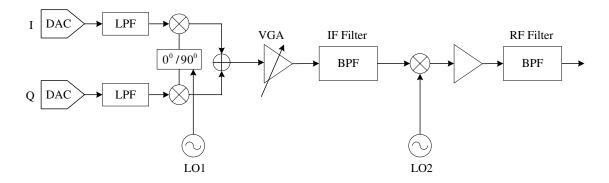

Traditional designs of analog transmitter employ the use of the phase locked loop, mixers, analog filters and amplifiers. Figure 1.1 shows an example of traditional analog transmitter. Digital baseband in-phase (I) and quadrature (Q) signals are converted to analog signals by digital to analog converters (DAC) and then fed into low-pass filters (LPF). Analog I/Q signals are upconverted to an intermediate frequency (IF) by mixing with the first local oscillator which goes through a phase splitter to provide in-phase and quadrature local oscillation (LO) signals. The outputs of the mixers are then summed. This IF signal is amplified, filtered and then mixed to the radio frequency (RF) by the IF variable gain amplifier (VGA), IF band-pass filter (BPF) and second local oscillator, respectively. The RF signal that has been processed by RF amplifier and RF band-pass filter is then ready to be fed to an antenna. As one can see from this figure, all the components are analog circuits. There are several disadvantages for this analog architecture. First, analog electronic circuits consume more space and power. Second, they are more subject to performance variations as a result of environmental factors such as temperature changes. Third, it is difficult to integrate these functions into one chip according to the current technology [1].

Figure 1.1 Analog transmitter.

In recent years, there is an increasing trend to replace most of these analog circuits with digital circuits and integrate them into one chip [1]. The advantage of this approach is that full digital control of the function is maintained as far as possible, and the limitations of analog design are minimized. Another trend in transceiver design is trying to reduce the cost and power consumption. It is becoming more and more important because it makes them feasible to be embedded into more types of electronic devices.

#### 1.1 Research motivation

The ideal radio architecture brings the digital signal processing techniques as close as possible to the antenna. In this ideal architecture, the analog circuits are restricted to those which can not be performed digitally, i.e., antenna, RF filter and power amplifier. According to the newest technology, the closest towards this ideal architecture is the hybrid implementation, as shown in Figure 1.2, which consists of a digital subsystem and a analog subsystem. Compared with analog transceiver,

Figure 1.2 Hybrid implementation.

this architecture offers more flexibility, longer product life and lower cost; it is also more suitable for mass production. Devices such as digital signal processors (DSPs), field programmable gate arrays (FPGAs) and application specific integrated circuits (ASICs) can be used to realize the required digital functionality.

Although there are many advantages to using digital modulator in communication systems, power consumption is still a problem for high-performance quadrature digital modulator. For example, one commercially used quadrature digital modulator, AD9856 [2], consumes about 1100 mW at 150 MHz. The power consumption is unacceptable for most of the portable applications due to the limited battery capacity. Also, according to international technology roadmap for semiconductors (ITRS) 2005 report, "Power consumption is an urgent, short-term challenge. How to quickly shift from a performance-driven design procedure to a performance and power driven design procedure has to be solved. Design issues include high level power estimation, dynamic and leakage power reduction at different design stages and power optimization, etc [3]." As a result, power consumption has to be taken into account as a main design factor. Generally speaking, to achieve a low-power integrated circuit, many low-power design techniques can be used. These techniques can be applied at system level, algorithm level, circuit level and transistor level.

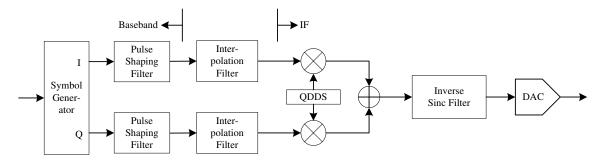

In this thesis, a fully digital modulator with low-power consumption is implemented, which is intended to function as a quadrature modulator and can be used in various portable devices where power and performance are critical. The designed modulator consists of pulse shaping filters, interpolation filters, a quadrature direct digital frequency synthesizer (QDDS) and an inverse sinc filter. Several low-power techniques are used to reduce the power consumption while maintaining high performance.

## 1.2 Research objectives

The objectives of the research work in this thesis are:

- To develop a quadrature digital modulator with less power dissipation

- To develop a novel low-power consumption QDDS that can be used in various

quadrature modulators and demodulators

- To investigate low-power design techniques and their application to quadrature digital modulator

- To develop a configurable digital quadrature digital modulator with high performance

#### 1.3 Thesis outline

Chapter 2 reviews the principles of the digital modulator, including the principles of QDDS, pulse shaping filter, interpolation filter, digital modulation, DAC and inverse sinc filter.

Chapter 3 discusses integrated circuit (IC) design challenges and digital IC design flow that is used in this thesis. The main design flow described in this chapter follows CMC Microsystems' design flow. However, some changes have been made to make the whole design process more flexible and efficient.

Chapter 4 covers the circuit implementation details of the modulator. For the QDDS circuit, a novel architecture with low-power consumption is proposed. For the other blocks, several hardware efficient design approaches are considered as the possible choices.

Chapter 5 introduces high-level power estimation techniques and also presents the performance comparisons for each key block with different design options. The proposed QDDS is compared with conventional QDDS circuits. Pulse shaping filter, interpolation filter, inverse sinc filter are also compared with different design choices.

Chapter 6 concentrates on the functional verification of the final modulator which is implemented with the proposed QDDS and the other relatively low-power blocks. It also covers the power consumption estimation of the whole modulator.

Chapter 7 gives conclusions and several suggestions for future work.

## Chapter 2

## Background

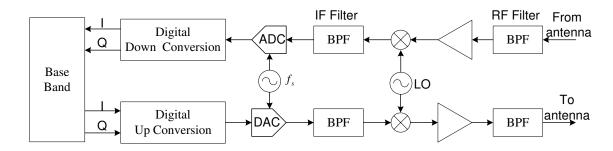

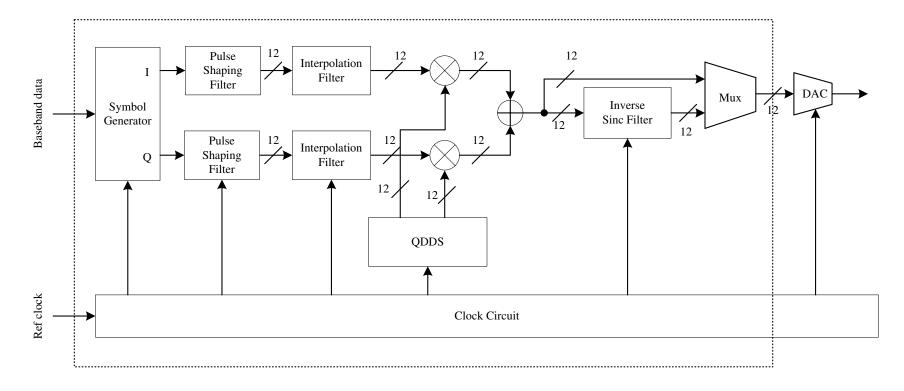

As shown in Figure 2.1, a quadrature digital modulator consists of several key blocks: QDDS, pulse shaping filters, interpolation filters and inverse sinc filter. QDDS is used to generate sine/cosine reference carrier signals. Pulse shaping filters are used to limit the transmitting bandwidth and reduce intersymbol interference (ISI). Interpolation filters are used to increase sampling rate and inverse sinc filter is used to precompensate sinc distortion coming from the following DAC. This chapter provides the background related to these key blocks.

**Figure 2.1** Digital quadrature modulator.

## 2.1 Quadrature direct digital synthesizer

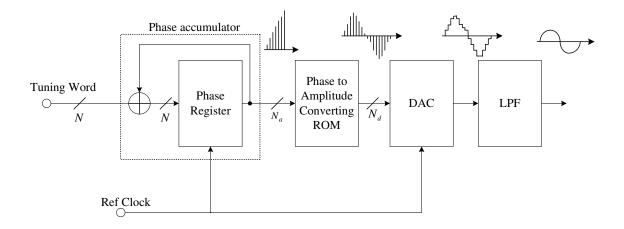

Direct digital synthesizer (DDS) is a circuit which uses digital signal processing technique to generate a frequency-tunable output signal referred to a fixed frequency and high precision clock source [4]. As shown in Figure 2.2, a basic form DDS is composed of a precise reference clock, a phase accumulator, a sine look-up table and a DAC.

The phase accumulator can be an N bit counter that increments the stored

Figure 2.2 Block diagram of a basic DDS.

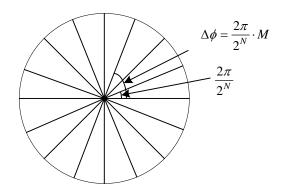

Figure 2.3 Digital phase wheel. As the vector rotates around the wheel, a corresponding sine wave is being generated.

number each time it receives a clock pulse. Figure 2.3 shows the diagram of digital phase wheel. The magnitude of the increment is determined by a digital word M, which sets how many points to skip around the phase wheel. The larger the M, the faster the phase accumulator overflows and completes the equivalence of a sine wave cycle.

The output from the phase accumulator addresses a sine look-up table which stores sine samples to generate a digital sine wave. The following DAC generates an analog sine wave in response to the digital input words from the sine look-up table. Low-pass filter is used to further smooth the sine wave output from the DAC so that a higher purity spectrum can be obtained.

For any tuning word M, the output frequency of the DDS is

$$f_{out} = M \cdot \frac{f_{refclk}}{2^N},\tag{2.1}$$

where  $f_{out}$  is the output frequency of DDS, M is the binary tuning word,  $f_{refclk}$  is the reference clock frequency and N is the length in bits of the phase accumulator. It is clear that the frequency resolution is  $f_{res} = \frac{f_{refclk}}{2^N}$ .

Phase truncation is an important aspect of DDS. For example, to directly convert 32 bits of phase to corresponding 8 bit amplitude would require a 4 gigabytes ROM. It is impractical to implement such a huge ROM in a design. In real design, the solution is to use a fraction of the most significant bits of the phase accumulator output to provide phase information. This means that the N bits output from the phase accumulator is usually truncated to  $N_a$  bits. This truncation results in errors in the output signal. The worse case signal to noise ratio (SNR) for the basic DDS structure can be expressed by following equation [5]:

SNR (dB) =

$$10 \cdot \log_{10} \left( \frac{1}{\frac{\pi^2}{2} 2^{-2N_a} + \frac{2}{2} 2^{-2N_d}} \right),$$

(2.2)

where  $N_a$  is the phase length after truncation and  $N_d$  is the amplitude word length stored in ROM.

Assume the maximum reference clock is 150 MHz and the phase accumulator is 32 bits. If the phase after truncation is 12 bits and the sine amplitude is stored with 12 bit accuracy, the frequency resolution,  $f_{res}$ , is  $\frac{150\times10^6}{2^{32}}=0.034$ Hz. If there is no compression applied to the sine ROM, the worse case SNR of the design is approximately  $10 \cdot \log_{10}(\frac{1}{\frac{\pi^2}{3} \cdot 2^{-2N_d} + \frac{2}{3} \cdot 2^{-2N_d}}) = 66.3 \text{ dB}.$

The DDS structure shown in Figure 2.2 can only generate one sine signal. Since the targeted application in this thesis is a quadrature digital modulator, quadrature digital reference carrier signals are desired. In other words, another ROM which stores cosine values has to be added to the basic DDS architecture to form a QDDS circuit.

## 2.2 Pulse shaping filter

As one can see from the system block diagram shown in Figure 2.1, I and Q data are processed by two kinds of digital filters. One is pulse shaping filter and the other is interpolation filter.

Rectangular pulses lead to a relatively large transmitting bandwidth because the frequency contents of a rectangular pulse have a  $\sin(x)/x$  shape and the tails of the this sinc function decay slowly. This large signal bandwidth is not desirable for most of the bandwidth constrained communication systems. In order to reduce the bandwidth and mitigate ISI with adjacent pulses, these rectangular pulses must be filtered properly. Raised cosine filter is one of the pulse shaping filters that can limit the transmitting bandwidth of signals and avoiding ISI.

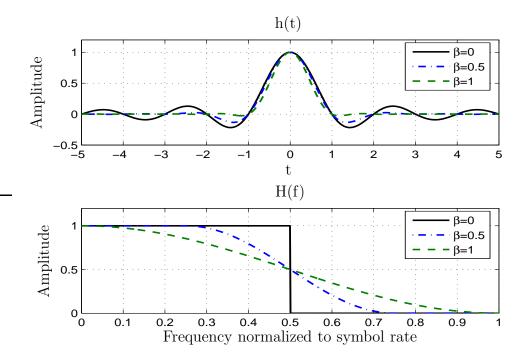

The frequency characteristic of the raised cosine filter can be described as [6]:

$$H_{rc}(f) = \begin{cases} T & \text{if } 0 \le |f| < \frac{1-\beta}{2T}, \\ \frac{T}{2} \{ 1 + \cos\left[\frac{\pi T}{\beta} (|f| - \frac{1-\beta}{2T})\right] \} & \text{if } \frac{1-\beta}{2T} \le |f| < \frac{1+\beta}{2T}, \\ 0 & \text{if } |f| \ge \frac{1+\beta}{2T}. \end{cases}$$

(2.3)

where T is the symbol duration, and  $\beta$  is a roll-off factor which takes a value between 0 to 1. The corresponding impulse response of a raised cosine filter has the form [6]:

$$h_{rc}(t) = \frac{\sin(\pi t/T)}{\pi t/T} \cdot \frac{\cos(\pi \beta t/T)}{1 - 4\beta^2 t^2/T^2}.$$

(2.4)

The raised cosine impulse response and spectral characteristics for  $\beta = 0, 0.5$  and 1 are illustrated in Figure 2.4. As one can see from this figure, larger  $\beta$  leads to smaller pulse tails and larger bandwidth.

In practical communication systems, the raised cosine filter is split evenly between transmitter and receiver, with each implementing a squared root raised cosine (SQRC) filter. The cascaded response of these two filters is equivalent to the response of the raised cosine filter. The frequency response of the square root raised

Figure 2.4 Raised cosine pulse and spectrum.

cosine filter is given as [7]:

$$H_{sqrc}(f) = \begin{cases} \sqrt{T} & \text{if } 0 \le |f| < \frac{1-\beta}{2T}, \\ \sqrt{\frac{T}{2}} \{1 + \cos\left[\frac{\pi T}{\beta}(|f| - \frac{1-\beta}{2T})\right]\} & \text{if } \frac{1-\beta}{2T} \le |f| < \frac{1+\beta}{2T}, \\ 0 & \text{if } |f| \ge \frac{1+\beta}{2T}. \end{cases}$$

(2.5)

The impulse response of the square root raised cosine filter is [7]:

$$h_{sqrc}(t) = 4\beta \cdot \frac{\cos((1+\beta)\pi t/T) + \frac{\sin((1-\beta)\pi t/T)}{4\beta t/T}}{\pi\sqrt{T}(1 - (4Rt/T)^2)}.$$

(2.6)

Equation (2.6) represents a noncausal pulse. To implement this SQRC filter in a communication system, the pulse is first delayed by an integer number of symbol periods, say mT, and truncated 2mT. The value of m is a tradeoff between simplicity and accuracy. The pulse is then sampled by taking k samples per symbol so that  $T = kT_s$ , where  $T_s$  is the sampling period. It is common to operate the filter at 4 or 8 samples per symbol. Replacing t by t - mT, letting  $t = nT_s$  and  $T = kT_s$  yields:

$$\frac{t}{T} \to \frac{nT_s - mkT_s}{kT_s} = \frac{n}{k} - m. \tag{2.7}$$

Substituting Equation (2.7) into Equation (2.6), the sampled version of SQRC filter can be expressed as:

$$h_{sqrc}(n) = 4\beta \frac{\cos[(1+\beta)\pi(\frac{n}{k}-m)] + \frac{\sin[(1-\beta)\pi(\frac{n}{k}-m)]}{4\beta(\frac{n}{k}-m)}}{\pi\sqrt{T}\{1 - [4\beta(\frac{n}{k}-m)]^2\}}.$$

(2.8)

It should be noted that impulse response truncation introduces a rectangular window. Filters using a rectangular window usually result in poor stopband response and passband ripples due to time discontinuity introduced by the rectangle window. These disadvantages can be alleviated by choosing a window function which does not have abrupt discontinuities in its time domain characteristics. Kaiser window is one of the window functions that can be used [8]. Applying Kaiser window leads to increased ISI level at the receiver end. The tradeoff between acceptable ISI and required spectral performance must be considered when choosing a window function.

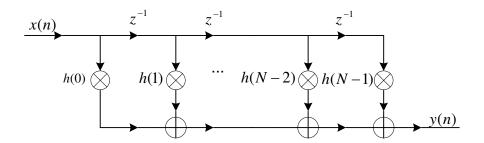

Another problem is the implementation of the finite impulse response (FIR) filter with impulse response shown in Equation (2.8). Figure 2.5 illustrates the signal-flow of a direct form structure FIR filter. The FIR filter computes the current output sample as a weighted sum of the current input sample and N-1 past samples.

$$y(n) = \sum_{i=0}^{N-1} h(i)x(n-i), \tag{2.9}$$

where y(n) is the output sequence, x(n) is the input sequence, and h(n) is the corresponding impulse response. In many applications the FIR filter is designed to have linear phase [6]. Consequently, the impulse response is symmetric and satisfies the relation

$$h(i) = h(N - 1 - i)$$

where  $0 \le i \le N - 1$ . (2.10)

By using this symmetric characteristic, one can simplify the signal flow shown in

Figure 2.5 Signal flow graph of the direct form structure FIR filter.

Figure 2.5.

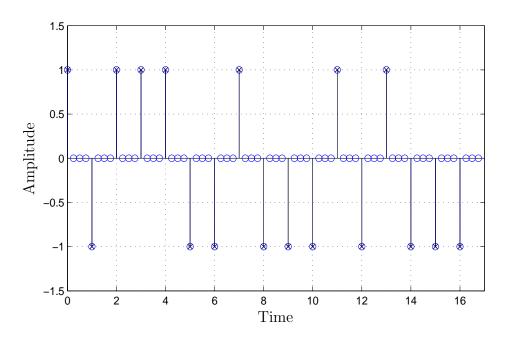

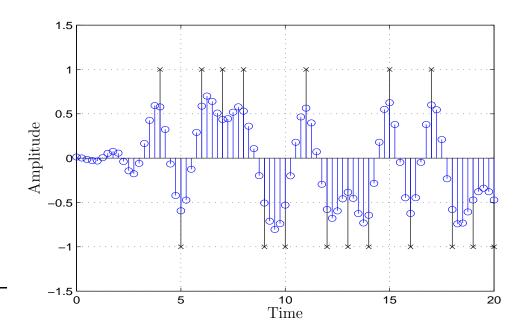

The pulse shaping filter in a quadrature digital modulator can also be an FIR filter with symmetric impulse response. From the theoretical point of view, the input data sequences are upsampled by k before being processed by the pulse shaping filters. The upsampled time series contains samples of the original inputs separated by k-1 zero valued samples. Figure 2.6 shows an example that the input data sequence is upsampled by 4. This zero packed data sequence is then processed by the SQRC filter. The SQRC filter actually limits the bandwidth to the band of interest and computes output samples at an increased rate (k-to-1) relative to input rate, replacing the zero packed values with the interpolated values. Figure 2.7 shows the output sequence when the upsampled data sequence shown in Figure 2.6 has been processed by a SQRC filter, where the filter length is 8 symbols (4 samples per symbol) and the roll-off factor is 0.22.

## 2.3 Interpolation filter

Interpolation filters in a modulator are used to raise the sampling rate to allow the translation of the input signal spectrum to an intermediate frequency in the digital domain. Two interpolation filter structures are considered here, cascaded integrator comb (CIC) filter and half-band FIR filter. Both of these two structures are hardware-efficient.

#### • Cascaded integrator comb (CIC) filter

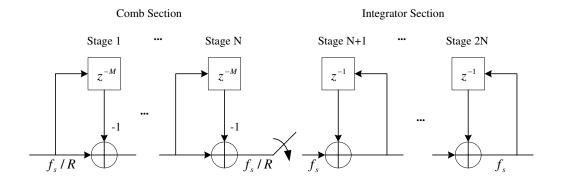

A CIC filter consists of an integrator section operating at the high sampling rate and a comb section operating at the low sampling rate [9]. From the theoretical

Figure 2.6 An example of 1-to-4 upsampling. "x" shows the input binary data and "o" shows the output after 1-to-4 upsampling.

Figure 2.7 Output sequence of a SQRC filter. "x" shows the input binary data and "o" shows the output sequence.

point of view, the CIC filter can either increase or decrease the sampling rate at the output relative to the input, depending on the filter architecture.

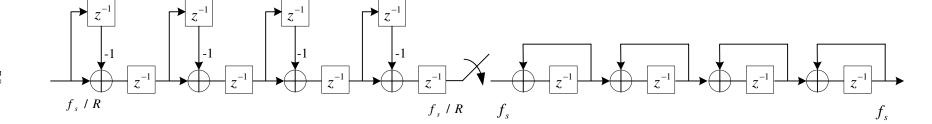

Figure 2.8 shows the basic structure of the CIC interpolation filter. The comb section operates at a low sampling rate,  $f_s/R$ , where R is the integer rate change factor. This section consists of N comb stages with a differential delay of M samples per stage. The differential delay factor, which is usually 1 or 2 in a practical system, is a filter design parameter used to control the filter's frequency response. The integrator section of the CIC filters consists of N ideal integrator stages operating at the high sampling rate,  $f_s$ . A rate change switch between two sections can cause a rate increase by a factor of R by inserting R-1 zero valued samples between consecutive samples of the comb section output.

The system function for the composite CIC filter referenced to the high sampling rate,  $f_s$ , is

$$H_{CIC}(z) = \frac{(1 - z^{-RM})^N}{(1 - z^{-1})^N} = \left(\sum_{k=0}^{RM-1} z^{-k}\right)^N.$$

(2.11)

The frequency response of CIC filter evaluated at  $z = e^{(2\pi f/R)}$  is:

$$H_{CIC}(f) = \left[\frac{\sin(\pi M f)}{\sin(\pi f/R)}\right]^{N}, \qquad (2.12)$$

where f is the frequency relative to the low sampling rate  $f_s/R$ .

CIC filter is chosen as one of the possible interpolation structures because it is

Figure 2.8 Block diagram of the CIC interpolation filter.

very hardware efficient. The advantages of CIC filter are: (1) no multipliers are required; (2) no storage is required for filter coefficients; (3) intermediate storage is reduced compared to the equivalent implementation using cascaded uniform FIR filters; and (4) the same filter design can be easily extended to a wide range of rate change factors.

For the CIC interpolation filter design, the minimum register width must be determined. Rounding can not be used because the small error in the integrator stages can cause the variance of the error to grow without bound and result in an unstable filter [9].

The minimum register width for jth filter stage,  $W_j$ , is determined by [9].

$$W_j = \lceil B_{in} + \log_2 G_j \rceil$$

for  $j = 1, 2, ..., 2N,$  (2.13)

where  $B_{in}$  is the input register width,  $G_j$  is the maximum register growth up to jth stage, and  $\lceil \rceil$  represents for ceiling function.  $G_j$  can be calculated according to Equation (2.14).

$$G_{j} = \begin{cases} 2^{j} & \text{if } j = 1, 2, ..., N, \\ \frac{2^{2N-j}(RM)^{j-N}}{R} & \text{if } j = N+1, ..., 2N. \end{cases}$$

(2.14)

There is a special case for Equation (2.13). When M = 1, the equation used to calculate the minimum register width for Nth stage is expressed as:

$$W_N = B_{in} + N - 1$$

if  $M = 1$ . (2.15)

### • Half-band filter

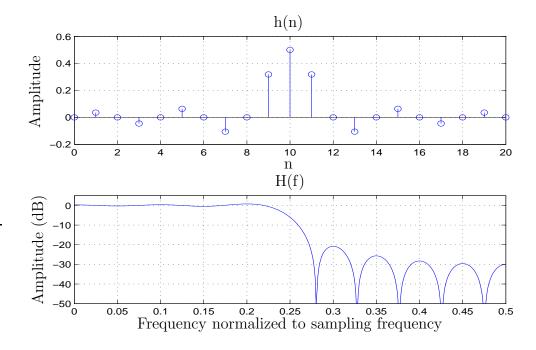

Half-band filters are widely used in multirate signal processing applications when interpolating/decimating by a factor of two. A half-band low pass filter has a pass band bandwidth between  $\pm \frac{1}{4}$  sampling rate for a two-sided bandwidth equal to half the sampling rate [10]. The impulse response of an ideal noncasual discrete filter

**Figure 2.9** Impulse response and frequency response of a half band FIR filter with the length of 21.

can be shown as:

$$h_{hb}(n) = \frac{1}{2} \cdot \frac{\sin(n\pi/2)}{n\pi/2}.$$

(2.16)

The impulse response and the corresponding frequency response of a casual halfband filter with the length of 21 are shown in Figure 2.9.

The impulse response of the half-band filter are all zero at the even index offsets from the center point of the filter. The coefficients with odd index offsets are symmetric about the filter center point. These two properties permit a half-band filter with the length of 2N+1 to be implemented with only  $\frac{N}{2}$  multiplications per output sample. This structure is very efficient for upsampling applications. The limitation for this filter is that the interpolation ratio can only be two. If several half-band filters are connected serially, the interpolation ratio can be expanded to the power of two.

Figure 2.10 I-Q format.

#### 2.4 Modulation

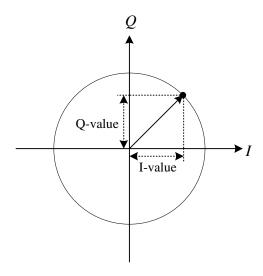

To transmit a signal over the air, a carrier is modulated with the information to be transmitted. This process usually involves modulating the amplitude, frequency and/or phase of the carrier. A simple way to view the amplitude and phase is with polar diagram. The carrier becomes a frequency and phase reference and the signal is interpreted relative to the carrier. The signal can be expressed in polar form as a magnitude and a phase.

In digital communication, modulation is often expressed in terms of I and Q [11]. As shown in Figure 2.10, the I axis lies on the zero degree phase reference and the Q axis is rotated by 90 degrees. The signal vector's projection to the I axis is the I component and projection to the Q axis is the Q component. I/Q diagrams are particularly useful because they can mirror the way most digital communication signals are created using an I/Q modulator.

At the transmitter side, I and Q signals are mixed with LO. A 90 degree phase shifter is placed in one of the LO paths. Signals that are separated by 90 degrees are also known as being orthogonal to each other or in quadrature. A composite output signal is generated by combining these two signals. The main advantage of I/Q modulation is the convenience of combining independent signal components into a composite signal and later splitting the signal into its independent component parts.

At the receiver side, the composite signal with magnitude and phase information is mixed with the LO signal at the carrier frequency in two forms. One is at an arbitrary zero phase and another one has a 90 degree phase shift. The composite input signal is thus broken into an in-phase component, I, and a quadrature component Q. These two components are independent and orthogonal.

Quadrature modulation can be accomplished with quadrature modulators. Most quadrature modulators map the data to a number of discrete points on the I/Q plane. These are known as constellation points. As the signal moves from one points to another, simultaneous amplitude and phase modulation results.

#### • QPSK modulation

Quadrature Phase Shift Keying (QPSK) is a common type of phase modulation, which is widely used in applications including CDMA cellular systems, wireless local loop and DVB-S (Digital Video Broadcasting - Satellite). Quadrature means that the signal shifts between phase states which are separated by 90 degrees. The equation describing QPSK is:

$$s(t) = u(t)\cos(\omega_c t + \theta_m), \tag{2.17}$$

where  $\theta_m \in \left\{\frac{\pi}{4}, -\frac{\pi}{4}, \frac{3\pi}{4}, -\frac{3\pi}{4}\right\}$  and u(t) is a real value pulse. The constellation diagram for QPSK is shown in Figure 2.11. The signal shifts in increments of 90 degrees from 45 to 135, -45 or -135 degrees. These points are chosen as they can be easily implemented using I/Q modulator. The symbol rate is half of the bit rate.

#### • QAM modulation

Another member of quadrature digital modulation family is Quadrature Amplitude Modulation (QAM). QAM is used in applications including microwave digital radio, DVB-C (Digital Video Broadcasting - Cable) and modems. The equation describing QAM is:

$$s(t) = V_m u(t) \cos(\omega t + \theta_m), \tag{2.18}$$

Figure 2.11 QPSK constellation.

where  $\theta_m$  represents possible phase values,  $V_m$  represents possible amplitude values and u(t) is a real value pulse.

Here, 16-QAM is used as an example. The constellation diagram for 16-QAM is shown in Figure 2.12. There are four I values and four Q values resulting in a total of 16 possible states for the signal. Transit from any state to another state is allowed at every symbol time. In each symbol period, 4 bits, i.e., two bits I and two bits Q, can be sent.

For these quadrature modulations described above, I and Q data are mixed

Figure 2.12 16-QAM square constellation.

together in a modulator after the pulse shaping and interpolation stages. The whole modulation process can be described as:

$$y(t) = I(t)\cos(\omega_c t) - Q(t)\sin(\omega_c t). \tag{2.19}$$

The carrier frequency is decided by programming the QDDS circuit with an appropriate tuning word. The digital sine and cosine data is multiplied by the Q and I data respectively to create the quadrature components of the original data upconverted to the carrier frequency. The quadrature components are then digitally summed and passed on to the following stages. The key point is that the modulation is done totally digital, which eliminates the phase and gain imbalance and crosstalk issues typically associated with analog modulators [2].

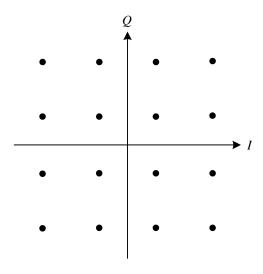

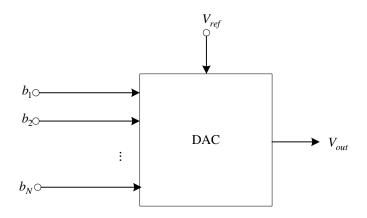

## 2.5 Digital to analog converter (DAC)

At the end of digital modulator, a DAC is needed to convert digital signals into analog signals. There are several advantages with a DAC circuit on-chip. One advantage is that the power consumption can be reduced compared with the design which needs to drive an off-chip DAC. Another advantage is that it can avoid delays and line loading caused by interchip connections.

Figure 2.13 shows the conceptual block diagram of the DAC. The inputs of the DAC consists of a digital word of N bits and a reference voltage,  $V_{ref}$ . The voltage output,  $V_{out}$ , can be expressed as:

$$V_{out} = KV_{ref}D, (2.20)$$

where K is a scaling factor and the digital word D is given as:

$$D = b_1 2^{-1} + b_2 2^{-2} + b_3 2^{-3} + b_N 2^{-N}, (2.21)$$

where  $b_i$  is the *i*th bit coefficient. It is preferred that the digital word is synchronously clocked. In this case, latches can be used to hold the word for conversion

Figure 2.13 Conceptual block diagram of a DAC.

Figure 2.14 Ideal input output characteristics for a 2 bit DAC.

and a sample and hold circuit is provided at the output [12].

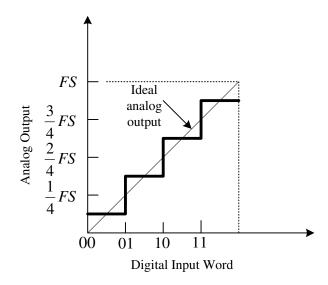

Figure 2.14 shows the transfer characteristic of an ideal 2-bit DAC, where analog outputs occur at odd multiples of  $\frac{1}{8}$  of the the full scale (FS) signal.

## 2.6 Inverse sinc filter

In a digital modulator, input data propagate through the device as digital stream. At the end of this processing, this digital stream must be converted into analog signals. The output signal of DAC that shows staircase pattern in Figure 2.14, is known as the zero-order hold function; i.e., the DAC holds its output con-

stant for the entire sampling period. The spectrum of zero-order hold function is a sinc envelope. The frequency response of the zero-order hold of the DAC is shown in Equation (2.22) [13].

$$H_{zo}(f) = \frac{\sin(\pi f/f_s)}{\pi f} e^{-j\pi f/f_s},$$

(2.22)

where  $f_s$  is sampling frequency.

The series of digital words presented at the input of the DAC represent the desired transmitting signal. Due to the zero-order hold effect of the DAC, the output spectrum of the output signal is the product of the sinc envelope and Fourier transform of the desired output signal. Thus, there is an intrinsic sinc distortion in the output spectrum.

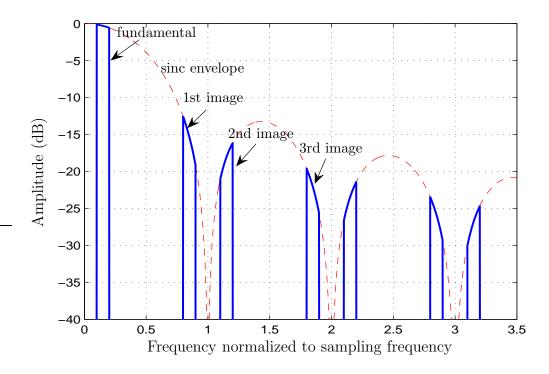

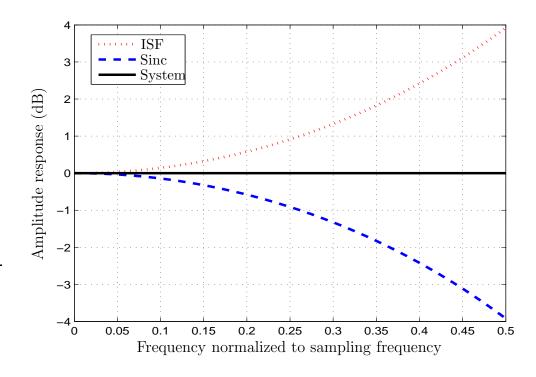

If the desired output signal spectrum has the flat top amplitude, the output spectrum from a real world DAC is illustrated in Figure 2.15. The amplitude of the output signal and its images follows a sinc response. The amplitude roll off due to this envelop in a system is 3.92 dB in the first Nyquist zone. Since the sinc response is deterministic and predictable, it is possible to predistort the input data stream in a manner that compensates for the sinc envelop distortion. An inverse sinc filter (ISF) can be used in front of DAC which will pre-compensate for the roll off and maintain flat output amplitude over the bandwidth of the first Nyquist zone. The amplitude response of an ideal inverse sinc filter and its impact on the whole system is shown in Figure 2.16. The frequency response of this FIR filter is the inverse sinc function. Thus, the data sent through this filter is altered to correct for the sinc envelop distortion. This inverse sinc filter can also be bypassed depending upon applications.

The desired amplitude response of the inverse sinc filter can be described as:

$$H_d(f) = \frac{\pi f/f_s}{\sin(\pi f/f_s)} \qquad \text{where } 0 \le f \le f_s/2.$$

(2.23)

With this desired response, a digital filter can be designed using the minimum mean

Figure 2.15 Output spectrum of a real world DAC.

Figure 2.16 Amplitude response of the ideal inverse sinc filter.

square error method. Given the desired frequency response, the impulse response of the designed filter is symmetrical and the filter length is odd. The equation used to get h(0), h(1),...,  $h(\frac{N-1}{2})$  is shown in Equation (2.24).

$$h(\frac{N-1}{2}-k) = \frac{2}{f_s} \int_0^{\frac{f_s}{2}} H_d(f) \cos(\frac{2\pi k f}{f_s}) df \qquad \text{for } k = 0, 1, ..., \frac{N-1}{2}, \quad (2.24)$$

where N is the filter length.  $h(\frac{N+1}{2})$ ,  $h(\frac{N+3}{2})$ ,...,h(N-1) are symmetrical about the midpoint, i.e.,  $h(\frac{N-1}{2})$ . The designed filter coefficients can be windowed to reduce ripples. Normally, the designed filter can compensate for the roll off and maintain flat output amplitude over the bandwidth of DC to 80% of the first Nyquist zone.

#### 2.7 Summary

QDDS, pulse shaping filter, interpolation filter and inverse sinc filter are key blocks in a quadrature digital modulator. The background information related to these blocks are introduced in this chapter, including the basic form of DDS structure and its performance, principles and implementation of square root raised cosine filter, CIC filter and half-band filter. Quadrature digital modulation techniques, including QPSK and QAM, are also introduced. Since a DAC circuit is necessary at the end of a digital modulator, DAC and its zero-order hold characteristic are discussed. In order to precompensate the sinc distortion introduced by DAC, an inverse sinc filter has to be included. The design technique for this inverse sinc filter is also covered. These background information are the basis of the circuit implementation.

## Chapter 3

# Integrated Circuit Design Flow

The semiconductor industry has evolved from the first integrated circuit of early 1960s and matured rapidly since then. Early small-scale integrated circuits contained only a few logic gates. It is well known as Moore's law that the number of transistors on an integrated circuit for minimum component cost doubles every 18 months [14]. Current very large scale integration (VLSI) ICs can combine millions of gates on a single device.

Accompanied with the fast advancement of IC fabrication processing technology, IC designers face many design challenges. ITRS 2005 report listed a number of the challenges [3] in which two are related to design technology.

- 1. Design productivity, which is closely linked to system and design process complexity, and of course affecting design cost, is the most massive and critical challenge. Issues related to it include high level of abstraction, system integration and analog circuit synthesis, etc.

- 2. Manufacturability, that is, the ability to produce a chip in large quantities at acceptable cost and according to an economically feasible schedule, has been affecting the industry primarily due to lithography hardware limitations but will become a major crisis in the long term as variability in its multiple forms invades all aspects of a design. Design issues include device parameter variability, mixed-signal test and quality models, etc.

A good design flow can increase both design productivity and manufacturability. Since the IC design in this thesis is totally digital, the digital IC design flow chosen is described as follows.

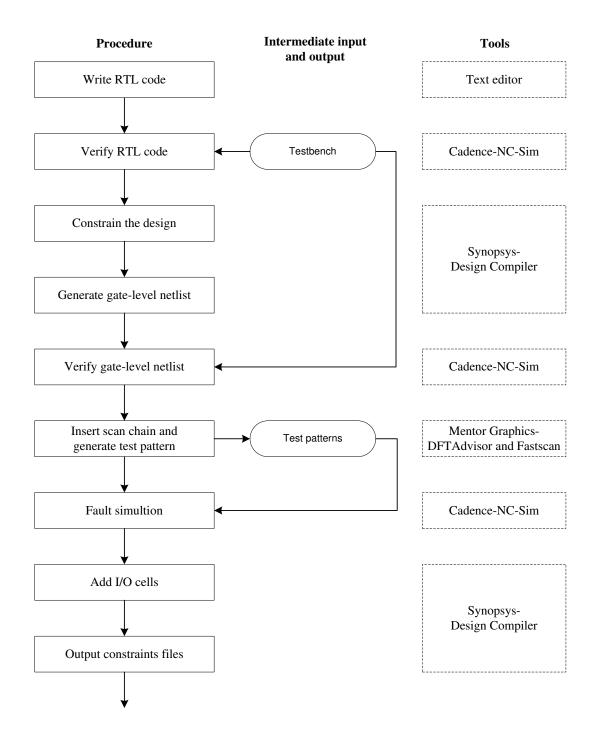

#### 3.1 Digital IC design flow

The design flow for creating VLSI digital circuits consists of a sequence of steps. Each step in the design flow either creates a database supporting the design flow, or verifies that the design meets specific requirements. Generally speaking, these steps can be separated into front-end design flow and back-end design flow. The front-end design flow focuses on the steps of preparing a gate-level netlist to be used in physical design of the chip. The back-end design flow focuses on steps of the physical design and ends up with a mask layout for fabrication. The main design flow described in this chapter is similar to the design flow provided by CMC microsystems [15]. Some modifications are made to make the whole design flow more flexible and more suitable for large designs.

#### 3.1.1 Front-end design flow

Figure 3.1 shows the front-end design flow which includes the design steps before the physical layout of an IC design. The first step is register transfer level (RTL) coding which describes the functionality of a design. The RTL coding can be written in Verilog or VHDL. Verilog is chosen as the RTL coding language in this thesis.

The second step is to verify the functionality of the RTL code using an hard-ware descriptive language (HDL) simulator. A corresponding testbench must be provided for verification. The simulator used in this step is NC-Sim. The design and the testbench files, both in Verilog, must be compiled first. The command used to compile Verilog files is nevlog. It performs syntactic and semantic checking on the Verilog design units. If no errors are found, compilation produces an internal representation for each HDL design unit in the source files. Before one can run simulation, the design must be 'elaborated' to construct a design hierarchy based on the instantiation and configuration information in the design, to establish signal connectivity, and to compute initial values for all objects in the design. The command used for elaborating the design is called neelab. The elaborated design hierarchy is stored as a simulation 'snapshot', which is the representation of the design that the simulator uses to run simulations. The snapshot is stored in a library

Figure 3.1 Block diagram of the front-end design flow.

database file along with the other intermediate objects generated by the compiler and elaborator. After compilation and elaboration, one can invoke the simulator, NC-Sim, to verify Verilog design.

The design flow provided by CMC microsystems suggests that users use NC-Sim in graphical user interface (GUI) mode. However, it is more convenient to verify the functionality in batch mode for large designs so that designers can observe inputs, outputs and internal nodes over a long period of time. Appendix A.1 shows one script example for invoking the simulator in batch mode.

After functional verification, the design is ready for synthesis. The logic synthesizer used is Synopsys Design Compiler. In order to synthesize the design, the same RTL code has to be analyzed and elaborated again. Similar with NC-Sim, the analysis step checks the syntax and semantics of Verilog files. The elaborate command replaces Verilog operators with equivalent combinational logic and determines correct bus sizes.

The next step is to set constraints for the design. The constraints here refer to defining the clock, specifying I/O cells, defining output load, etc. With these pre-set constraints, the design compiler can automatically create a gate-level netlist for a targeted processing technology. Synopsys Design Compiler can also report the timing, area and power consumption of the design.

The logic synthesis procedure described in the CMC microsystems' design flow are performed in GUI mode. Due to the fact that a design will be synthesized for several times with different constraints, an efficient way to use the logic synthesizer is to perform the synthesis in batch mode instead of GUI mode. Appendix A.2 shows one example script for using the logic synthesizer in batch mode. It should be noted that this example script contains basic synthesis steps only. One needs to modify it to meet different synthesis requirements.

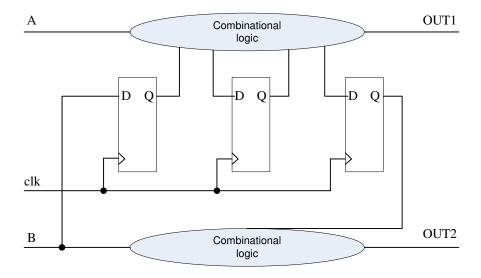

To ensure the resulted gate-level netlist is correct, one needs to verify the functionality of the gate-level netlist following the same procedure as RTL code verification. With the verified gate-level netlist, one can insert the scan chain using Mentor Graphics DFTAdvisor. The purpose of inserting scan chain is to improve

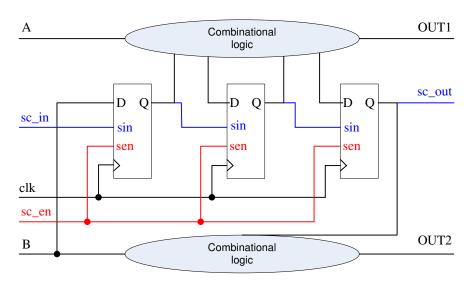

the testability of the fabricated chip for physical defects. This step involves replacing sequential elements with scannable sequential elements and then stitching the scan cells together into scan registers, or scan chains. Figure 3.2 shows one example before and after scan chain insertion [16]. Testing engineers can then use these serially-connected scan cells to shift data in and out when the design is in scan mode.

The next step after scan chain insertion is automatic test pattern generation (ATPG). Test patterns generated in this step are sets of 1s and 0s placed on primary input pins during manufacturing test process to determine if the chip is functioning properly. When the test pattern is applied, the automatic test equipment (ATE) determines if the circuit is free from manufacturing defects by comparing the fault-free output which is also contained in the test pattern with the actual output measured by the ATE. The tool used in this step is Mentor Graphics Fastscan. Both the DFTAdvisor and Fastscan are used under batch mode. The generated test patterns can be verified in NC-Sim.

After scan chain insertion, the gate-level netlist with scan chain is read back to Synopsys Design Compiler to finalize the design by adding I/O cells and output corresponding constraint files.

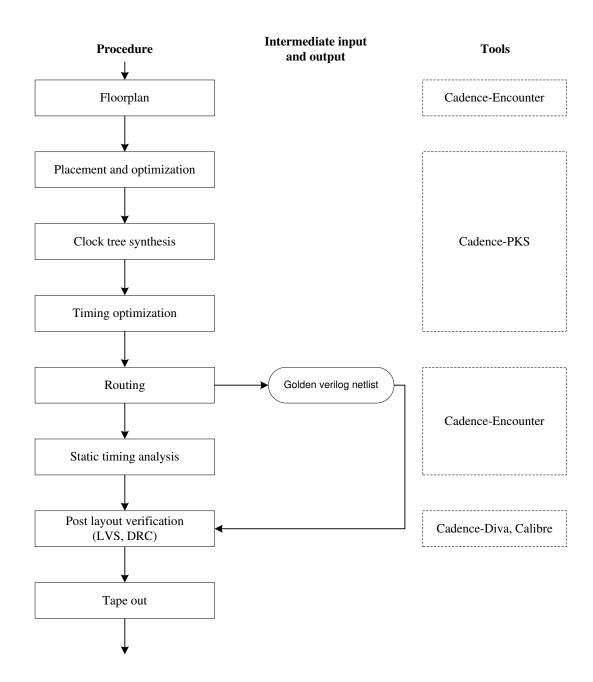

## 3.1.2 Back-end design

The back-end design flow, which consists of the design steps of physical layout, is shown in Figure 3.3. The flow begins with virtual design procedure, which involves I/O cells placement, power planning and trial placement and routing. During the trial placement and routing of the virtual design procedure, cells are placed and routed without consideration for timing. The next step is to use Cadence Physically Knowledgeable Synthesis (PKS) to optimize the design with the consideration of timing constraints and parasitic values. The design is optimized for three separate times to account for parasitics that are obtained during place and route to attain a high performance. It should be noted that all the optimizations in this step are based on an 'ideal' clock.

(a) Before scan chain insertion

(b) After scan chain insertion

Figure 3.2 One example to compare the circuit before and after scan chain insertion. After adding scan circuitry, the design has two additional inputs, sc\_in and sc\_en, and one additional output, sc\_out. These extra ports will be used when the design is in scan mode.

Figure 3.3 Block diagram of the back-end design flow.

After the placement and optimization, clock tree synthesis can be performed. Cadence PKS treats clock tree as an entire sub-circuit and adds buffers into the tree during the clock tree synthesis process. With the physically inserted clock tree, optimizations based on the real propagated clock can be performed.

The design is ready for the final route and optimization after the clock tree insertion. With this step done, one needs to perform static timing analysis to make sure the routed design meets the timing goal.

The final steps before tape out are mainly to verify the physical layout of the design. These steps include layout versus schematic (LVS) verification and design rule check (DRC). LVS is to verify that the physical layout contains the same instances, nets and connectivity as the verified design netlist and DRC is to verify that the physical layout meets the foundrys design rule.

It is a good practice to carry out all the steps involved in back-end design in batch mode in stead of GUI mode. Appendix A.3 shows one script example for timing optimization after clock tree insertion using Cadence PKS.

It should be noted that the design flows of front-end design and back-end design shown in Figure 3.1 and Figure 3.3 assume that the design requirements can be met at every stage. In practical design, there will be several changes in iterations of the design or constraints at various design points until the design requirements are met.

## 3.2 Summary

To tackle the challenges of integrated circuit design productivity and manufacturability, it is very important to choose the right design flow. The whole integrated circuit design flow are generally split into front-end design flow and back-end design flow. Both of them are discussed step by step in this chapter. Compared with CMC microsystems' design flow, the design flow introduced here is more efficient and flexible as a result of extensive use of scripts for batch mode processing. Some simple scripts are also provided as examples.

## Chapter 4

## Circuit Design and Low Power Considerations

Low-power circuits can be achieved at different levels. At system level, dynamic power management can be used to dynamically reconfiguring systems to provide the requested services and performances with a minimum number of active components or a minimum load on such components. At algorithm level, different algorithms can be compared for their power consumptions to identify one with the lowest power consumption. At circuit level, parallelization implementation, multiple supply voltages, dynamic supply voltage scaling, retiming, etc., can be used to reduce power consumption. At transistor level, variable threshold transistors, dynamic threshold voltage scaling, input vector control, etc., can be used to reduce leakage power which has become more and more important in nanometric technologies. Most of the low-power techniques used in this thesis are at algorithm level. Some low-power techniques at system level and circuit level are also used.

## 4.1 Quadrature digital modulator

The detailed block diagram of the designed modulator is shown in Figure 4.1. Most of the interfaces in this modulator are chosen to be 12 bits. This interface width is chosen to be the same as [2]. The width of the interface between symbol generator block and pulse shaping block is decided by the modulation technique used. All the blocks in this modulator which are not working at system clock rate, i.e., pulse shaping filter and interpolation filter blocks, use clock split from system clock. This clock splitting technique causes clock skew, but as will be described in Chapter 5, total power consumption is less than the scheme where the circuits

Figure 4.1 The detailed block diagram of the designed quadrature digital modulator.

Figure 4.2 ROM design using quarter-wave symmetry.

operate at the same high clock speed. The maximum system clock rate is targeted at 150 MHz in this design, i.e., output bandwidth is from 0 to 75 MHz. This clock speed is enough for most of the real applications because the highest intermediate frequency is usually 70 MHz.

#### 4.2 QDDS

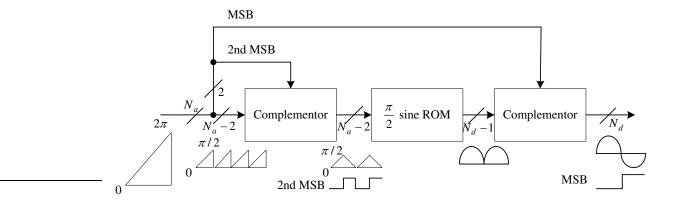

#### 4.2.1 ROM compression

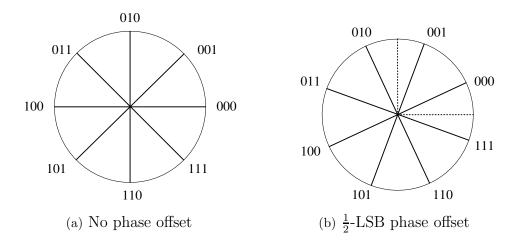

In the conventional DDS design [17], a commonly used technique to design the phase-to-amplitude converting ROM is illustrated in Figure 4.2. The ROM stores only 0 to  $\frac{\pi}{2}$  of sine wave instead of 0 to  $2\pi$ , i.e., it uses quarter-wave symmetry to generate a full range sine wave. The most significant bit (MSB) determines the sign of the output and second MSB determines whether the phase between 0 to  $\frac{\pi}{2}$  should be increasing or decreasing. The rest  $N_a - 2$  bits are used to address a sine ROM.

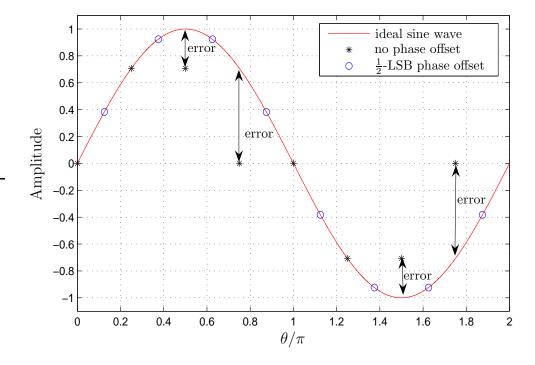

In this design, a  $\frac{1}{2}$  least significant bit (LSB) offset must be introduced in all phase addresses. If the phase address,  $N_a$ , is assumed to be 3 bits, Figure 4.3 shows the phase wheel comparison between no phase offset and  $\frac{1}{2}$ -LSB phase offset. Figure 4.4 shows error comparison between them. As one can see from Figure 4.4, if quarter-wave ROM stores  $\sin(0)$  and  $\sin(\frac{\pi}{4})$ , i.e., without phase offset, there are some errors introduced because one's complementor can't map the phase values without errors. If quarter-wave ROM stores  $\sin(\frac{\pi}{8})$  and  $\sin(\frac{3\pi}{8})$ , i.e., with  $\frac{1}{2}$ -LSB

phase offset, one's complementor can map the phase values to the first quadrant without error. This  $\frac{1}{2}$ -LSB offset is also necessary for all the ROM compression methods introduced later.

Figure 4.3 Phase wheel comparison between no phase offset and  $\frac{1}{2}$ -LSB phase offset.

**Figure 4.4** Error comparison between no phase offset and  $\frac{1}{2}$ -LSB phase offset.

The conventional design only needs to store a quarter of the sine wave values without introducing any errors. However, the ROM size is still too big considering ROM is the most power hungry part in a DDS circuit [17]. One way to reduce the ROM size is Suntherland algorithm [18]. In this algorithm, the phase address of the quarter-wave,  $\theta$ , is decomposed to three components; i.e.,  $\theta = \alpha + \beta + \gamma$ .

$$\sin(\alpha + \beta + \gamma) = \sin(\alpha + \beta)\cos(\gamma) + \cos(\alpha + \beta)\sin(\gamma)$$

$$\approx \sin(\alpha + \beta) + \cos(\alpha)\sin(\gamma), \tag{4.1}$$

where  $\alpha$ ,  $\beta$  and  $\gamma$  are the MSBs, the middle bits, and the LSBs of the phase address, respectively. The variables  $\alpha$  and  $\beta$  form a 'coarse' ROM address and the variables  $\alpha$  and  $\gamma$  form a 'fine' ROM address. If the word lengths of  $\alpha$ ,  $\beta$  and  $\gamma$  are assumed to be A, B and C, computer simulations are usually used to determine the optimum partitioning of the ROM address. Assume the word length of the input phase address is 12 bits and output sine samples are also 12 bits, i.e., the phase address of the quarter-wave sine ROM is 10 bits and the output of quarter-wave sine ROM is 11 bits, Table 4.1 shows partition simulation results. Given the tradeoff between mean square error and ROM size, A = 4, B = 3 and C = 3 are optimum choices for this scenario, where the output of the coarse ROM is 11 bits and the output of the fine ROM is 5 bits. As one can see from this example, this method can compress the ROM size. The compression ratio achieved here is  $\frac{2^{10} \times 11}{2^7 \times 11 + 2^7 \times 5} = 5.5$ .

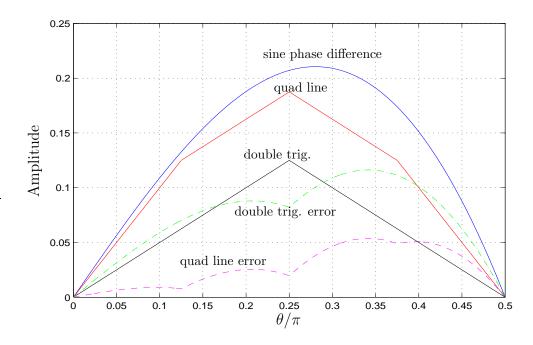

Based on the Suntherland algorithm, the sine phase difference method was introduced in [19] to reduce the size of coarse ROM. With the sine phase difference method, the coarse ROM stores the sine phase difference instead of the real sine values. The equation used to describe sine phase difference method is:

$$y(\theta) = \sin(\theta) - \frac{2\theta}{\pi}.\tag{4.2}$$

Since the maximum value of sine phase difference,  $y(\theta)$ , is less than  $\frac{1}{4}$ , this method can save 2 bits of word length of the data in the coarse ROM.

**Table 4.1** Comparison between different A, B, C partitions.

|                     | $\overline{\mathrm{error}^2}$ | ROM size (bits)                       |

|---------------------|-------------------------------|---------------------------------------|

| A = 6, B = 3, C = 1 | $2.7675 \times 10^{-10}$      | $2^9 \times 11 + 2^7 \times 3 = 6016$ |

| A = 4, B = 3, C = 3 | $7.4979 \times 10^{-8}$       | $2^7 \times 11 + 2^7 \times 5 = 2048$ |

| A = 3, B = 5, C = 2 | $7.5748 \times 10^{-8}$       | $2^8 \times 11 + 2^5 \times 4 = 2944$ |

| A = 3, B = 4, C = 3 | $3.0273 \times 10^{-7}$       | $2^7 \times 11 + 2^6 \times 5 = 1728$ |

| A = 3, B = 3, C = 4 | $1.1813 \times 10^{-6}$       | $2^6 \times 11 + 2^7 \times 6 = 1472$ |

| A = 3, B = 2, C = 5 | $4.4364 \times 10^{-6}$       | $2^5 \times 11 + 2^8 \times 7 = 2144$ |

| A = 2, B = 5, C = 3 | $1.1784 \times 10^{-6}$       | $2^7 \times 11 + 2^5 \times 5 = 1568$ |

| A = 2, B = 4, C = 4 | $4.6640 \times 10^{-6}$       | $2^6 \times 11 + 2^6 \times 6 = 1088$ |

| A = 2, B = 3, C = 5 | $1.8129 \times 10^{-5}$       | $2^5 \times 11 + 2^7 \times 7 = 1248$ |

| A = 1, B = 5, C = 4 | $1.7011 \times 10^{-5}$       | $2^6 \times 11 + 2^5 \times 6 = 896$  |

| A = 1, B = 3, C = 6 | $2.5962 \times 10^{-4}$       | $2^4 \times 11 + 2^7 \times 8 = 1200$ |

Double trigonometric approximation method is revised to reduce the coarse ROM size. The coarse ROM stores the errors between the sine phase difference and a triangle waveform. The double trigonometric line,  $d(\theta)$ , can be expressed as:

$$d(\theta) = \begin{cases} \frac{\theta}{2\pi} & \text{if } 0 \le \theta < \frac{\pi}{4}, \\ \frac{1}{4} - \frac{\theta}{2\pi} & \text{if } \frac{\pi}{4} \le \theta \le \frac{\pi}{2}. \end{cases}$$

(4.3)

Because the maximum error of the double trigonometric approximation is less than  $\frac{1}{8}$ , this method can save 3 bits of word length of the data in the coarse ROM. The data for  $0 \le \theta < \frac{\pi}{4}$  are generated by shifting right the phase,  $\frac{2\theta}{\pi}$ , by 2 bits. The data for  $\frac{\pi}{4} \le \theta \le \frac{\pi}{2}$  are symmetric and can be accomplished by a complementor.

Quad line approximation (QLA) method [17] can further compress coarse ROM size. Similar to the double trigonometric approximation, the coarse ROM only stores the errors between the sine phase difference and the quad line waveform.

The quad line waveform,  $q(\theta)$ , is expressed as follows:

$$q(\theta) = \begin{cases} \frac{\theta}{\pi} & \text{if } 0 \le \theta < \frac{\pi}{8}, \\ \frac{1}{16} + \frac{\theta}{2\pi} & \text{if } \frac{\pi}{8} \le \theta < \frac{\pi}{4}, \\ \frac{1}{16} - \frac{\theta}{2\pi} + \frac{1}{4} & \text{if } \frac{\pi}{4} \le \theta < \frac{3\pi}{8}, \\ \frac{1}{2} - \frac{\theta}{\pi} & \text{if } \frac{3\pi}{8} \le \theta \le \frac{\pi}{2}. \end{cases}$$

(4.4)

The data for  $0 \le \theta < \frac{\pi}{8}$  are generated by shifting right the phase,  $\frac{2\theta}{\pi}$ , by 1 bits. The data for  $\frac{\pi}{8} \le \theta < \frac{\pi}{4}$  are generated by shifting right the phase by 2 bits and by changing the first and second MSBs of the phase to "10". These data are implemented with a MUX. The data for  $\frac{\pi}{4} \le \theta \le \frac{\pi}{2}$  are symmetric and can be accomplished by a complementor.

Since the maximum value of QLA errors is less than  $\frac{1}{16}$ , the QLA method can save 4 bits of word length of the data in the coarse ROM. The waveforms of sine-phase difference, double trigonometric approximation, QLA are shown in Figure 4.5. The errors of double trigonometric approximation and QLA methods are also shown in the same figure.

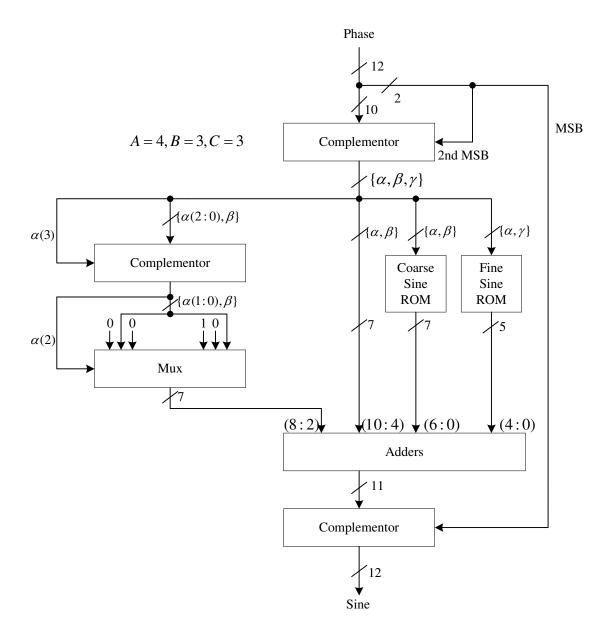

Table 4.2 compares different implementation choices for the coarse ROM. As the QLA method can save 4 bits of the word length for the coarse ROM with simple additional circuits, this method is chosen as the DDS implementation structure in the modulator. For a DDS ROM with 12 bits phase address and 12 bits output sine samples, the conventional design needs a  $2^{10} \times 11$  bits ROM. Based on the Suntherland algorithm and the simulation results shown in Table 4.1, the input phase address can first be decomposed to  $\alpha$ ,  $\beta$  and  $\gamma$  with lengths of 4, 3 and 3 respectively. Together with the QLA method, the ROM can be implemented with a  $2^7 \times 7$  bits coarse ROM and a  $2^7 \times 5$  bits fine ROM. The total compression ratio achieved is  $\frac{2^{10}\times11}{2^7\times7+2^7\times5}=7.33$ . The implementation block diagram of such a sine-to-amplitude converting ROM using QLA method is shown in Figure 4.6. Similar to the conventional design shown in Figure 4.2, the second MSB determines whether the amplitude is increasing or decreasing.  $\{\alpha, \beta\}$  is used to address the coarse sine

**Figure 4.5** Curves of sine-phase difference, double trigonometric approximation and QLA and the error curves of double trigonometric approximation and QLA.