# OBJECT DETECTION NETWORKS AT THE EDGE: HARDWARE OPTIMIZATION AND INTELLIGENT TRANSPORTATION SYSTEMS APPLICATIONS

A Thesis Submitted to the

College of Graduate and Postdoctoral Studies

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

By

Juan Fernando Yépez Rodríguez

© Juan Fernando Yépez Rodríguez, October 2021. All rights reserved. Unless otherwise noted, copyright of the material in this thesis belongs to the author.

#### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

3B48 Engineering Building

University of Saskatchewan

57 Campus Drive

Saskatoon, Saskatchewan S7N 5A9

Canada

Or

Dean of College of Graduate and Postdoctoral Studies

116 Thorvaldson Building

University of Saskatchewan

110 Science Place

Saskatoon, Saskatchewan S7N 5C9

Canada

#### ABSTRACT

In recent years, deep learning (DL) and especially Convolutional Neural Networks (CNNs) have become a key component of many computer vision systems and applications due to their demonstrated capability to accurately process visual information. Object detection is one of the most important and challenging problems capable of being solved by DL; in general, higher object detection accuracy can be achieved by DL compared to other techniques. However, DL tends to require expensive GPUs or cloud-based services (the latter requiring a high internet bandwidth, latency, and other associated costs), making DL applications traditionally very expensive to implement in practice. This thesis emphasizes the optimization of DL computation for object detection and proposes designs of real-time Intelligent Transportation Systems (ITS) applications at the edge using hardware accelerators.

To optimize DL computation, a novel stride 2 Winograd method is proposed for deep neural network (DNN) inference optimization. The proposed method provides new algorithms that trade expensive multiplications for cheap additions, thereby increasing efficiency by vastly decreasing computational complexity. The proposed algorithms support 1D, 2D, and 3D input for CNNs. Additionally, a novel Processing Element (PE) is proposed to process stride one and two convolution in the same FPGA module. These algorithms, implemented using a GPU and an FPGA, are demonstrated to provide better efficiency compared to regular convolution implementations for a variety of kernels.

Additionally, three ITS applications are proposed. The first application is a License Plate Localization (LPL) system constructed using an architecture comprised of bottleneck depth-separable convolutions with inverted residuals. The second proposed application is a novel two stage real-time deep CNN recognition system for decals issued by the Commercial Vehicle Safety Alliance (CVSA). The third proposed application is a novel three stage real-time deep learning-based edge system for hazardous materials (HAZMATs) recognition. The designed custom object detection architectures for ITS applications are capable of highly accurate real-time prediction on edge computing devices (Intel, Google, and/or NVIDIA), thus providing enormous cost and performance advantages compared to current implementations.

#### ACKNOWLEDGEMENTS

The research works presented in this thesis are sponsored by the Natural Sciences and Engineering Research Council (NSERC) of Canada, Mitacs of Canada, International Road Dynamics (IRD) Inc., and the Department of Electrical and Computer Engineering at the University of Saskatchewan.

The compilation of this thesis would have been impossible without the love and support I received from my lovely wife, Lucia. She stayed by my side during the many arduous and sleepless nights. She was always my source of encouragement in difficult situations.

Thanks to God for the gift of life and special thanks for the lovely gift of my children, Anthony and Juan Andrés. They have been my source of motivation and joy each day.

I would also like to acknowledge and appreciate the guidance and constructive role played by my supervisor, Dr. Seok-Bum Ko. Without his thoughtful insights, comments and patience with me, this task would have been difficult to accomplish. He assisted me in seeing many new perspectives in every draft that I presented to him. This has translated my view and broadened my scope regarding this area. Thank you.

Sincere thanks to all my colleagues for assisting me throughout my PhD program. I also extend my gratitude to all the ECE faculties for the important lessons regarding this particular discipline.

I am also indebted to my family and friends who were so helpful. All they did may be too much to mention on this piece. Special thanks to my mother Cecilia, my sister Andrea, and my brother Christian for their unwavering support. Last but not least, thanks to my father, Juan, who is not with me physically but spiritually.

Thank you all so much.

# CONTENTS

| Permiss  | sion to Usei                                         |

|----------|------------------------------------------------------|

| Abstrac  | etii                                                 |

| Acknow   | vledgements iv                                       |

| Conten   | tsv                                                  |

| List of  | Tablesix                                             |

| List of  | Figures xi                                           |

| List of  | Abbreviationsxiii                                    |

| Part I F | Preface                                              |

| Chapter  | r 1: Introduction                                    |

| 1.1      | Intelligent Transportation Systems                   |

| 1.2      | Motivation of Research Works                         |

| 1.3      | Research Objectives                                  |

| 1.4      | Overview of Research Works                           |

| 1.5      | Summary of Contribution                              |

| Chapter  | r 2: Background                                      |

| 2.1      | Machine Learning and Deep Learning12                 |

| 2.2      | Convolutional Neural Networks                        |

|          | 2.2.1 Stride in Convolutional Neural Networks        |

|          | 2.2.2 Padding in Convolutional Neural Networks       |

| 2.3      | Optimized Layers for Convolutional Neural Networks17 |

|          | 2.3.1 Deep Residual Learning                         |

|          | 2.3.2 Depthwise Separable Convolution                |

|          | 2.3.3 Inverted Bottleneck Networks                   |

|          | 2.3.4 Fused Inverted Bottleneck Layers (Expansion)   |

|          | 2.3.5 Tucker Decomposition                           |

|          | 2.3.6 Linear Bottlenecks                             |

|          | 2.3.7 FFT Based Convolution                          |

|          | 2.3.8 Winograd Algorithm                             |

|          | 2.3.9 Winograd Works                                 |

| 2.4      | Object Detection                                     |

|           | 2.4.1 Multistage Object Detection Systems                         | 28 |

|-----------|-------------------------------------------------------------------|----|

|           | 2.4.2 Video Object Detection Systems                              | 29 |

| Part II H | lardware Optimization for Convolutional Neural Networks           | 30 |

| Chapter   | 3: Stride 2 Winograd for Convolutional Neural Networks            | 32 |

| 3.1       | Introduction                                                      | 32 |

| 3.2       | Proposed Winograd with Stride 2                                   | 34 |

|           | 3.2.1 One-dimension                                               | 34 |

|           | 3.2.2 Two-dimensions                                              | 39 |

|           | 3.2.2.1 Using Kernel 3×3                                          | 39 |

|           | 3.2.2.2 Using Kernel 5×5                                          | 41 |

|           | 3.2.2.3 Using Kernel 7×7                                          | 43 |

|           | 3.2.3 Three-dimensions                                            | 46 |

| 3.3       | CNN Architectures with Layer Stride > 1                           | 50 |

| 3.4       | GPU Implementation                                                | 51 |

| 3.5       | FPGA Implementation                                               | 53 |

|           | 3.5.1 CNN Architecture                                            | 53 |

|           | 3.5.2 FPGA Implementation                                         | 54 |

|           | 3.5.3 Memory Access                                               | 55 |

|           | 3.5.4 Proposed PE Architecture                                    | 56 |

|           | 3.5.4.1 Input Tile From Registers                                 | 57 |

|           | 3.5.4.2 Splitter Block                                            | 57 |

|           | 3.5.4.3 Input Transform Block                                     | 58 |

|           | 3.5.4.4 Filter Transform Block                                    | 59 |

|           | 3.5.4.5 Multiplication Block                                      | 59 |

|           | 3.5.4.6 Inverse Transform                                         | 59 |

|           | 3.5.4.7 Accumulator Block                                         | 59 |

|           | 3.5.5 Parallelization                                             | 60 |

|           | 3.5.6 Results                                                     | 61 |

| 3.6       | Summary                                                           | 64 |

| Part III  | Applications for Intelligent Transportation Systems               | 66 |

| Chapter   | 4: Deep Learning-based Embedded License Plate Localization System | 68 |

| 4.1                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                               |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 4.2                                                | Proposed Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70                                               |

|                                                    | 4.2.1 Neural Network Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70                                               |

|                                                    | 4.2.2 Training Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74                                               |

|                                                    | 4.2.3 Inference Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78                                               |

|                                                    | 4.2.4 Proposed DL LPL Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                               |

| 4.3                                                | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82                                               |

|                                                    | 4.3.1 Dataset Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82                                               |

|                                                    | 4.3.2 Comparisons to Public Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83                                               |

|                                                    | 4.3.2.1 The Caltech Dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83                                               |

|                                                    | 4.3.2.2 The University of Zagreb Database                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85                                               |

|                                                    | 4.3.2.3 The NTUA MediaLab Dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                  |

|                                                    | 4.3.3 Comparisons to Popular DL Object Detection Frameworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                               |

|                                                    | 4.3.4 Comparisons to other DL LPL Frameworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                                               |

|                                                    | 4.3.5 Real-life Real-time Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89                                               |

| 4.4                                                | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |

|                                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                  |

| -                                                  | 5: Real-time CVSA Decals Recognition System Using Deep Convolutional Neural                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                  |

| Archite                                            | ctures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                  |

| Archited 5.1                                       | ctures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 92<br>93                                         |

| Archite                                            | ctures<br>Introduction<br>Proposed Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92<br>93<br>95                                   |

| Archited 5.1                                       | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |

| Archited 5.1                                       | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification<br>5.2.2 Digit and Corner-cut Detection and Classification                                                                                                                                                                                                                                                                                                                                      | 92<br>93<br>93<br>95<br>97<br>98                 |

| Archited 5.1                                       | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification                                                                                                                                                                                                                                                                                                                                                                                                 | 92<br>93<br>93<br>95<br>97<br>98                 |

| Archited<br>5.1<br>5.2                             | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification<br>5.2.2 Digit and Corner-cut Detection and Classification                                                                                                                                                                                                                                                                                                                                      | 92<br>93<br>95<br>95<br>97<br>98<br>98           |

| Archited<br>5.1<br>5.2                             | <ul> <li>Introduction</li> <li>Proposed Architecture</li> <li>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification</li> <li>5.2.2 Digit and Corner-cut Detection and Classification</li> <li>Labelling and Training</li> </ul>                                                                                                                                                                                                                                                                          | 92<br>93<br>95<br>95<br>97<br>98<br>98<br>99<br> |

| Archited<br>5.1<br>5.2                             | <ul> <li>Introduction</li> <li>Proposed Architecture</li> <li>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification</li> <li>5.2.2 Digit and Corner-cut Detection and Classification</li> <li>Labelling and Training</li> <li>5.3.1 First Stage</li> </ul>                                                                                                                                                                                                                                               | 92<br>93<br>95<br>95<br>97<br>98<br>98<br>99<br> |

| Archited<br>5.1<br>5.2<br>5.3                      | <ul> <li>Introduction</li> <li>Proposed Architecture</li> <li>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification</li> <li>5.2.2 Digit and Corner-cut Detection and Classification</li> <li>Labelling and Training</li> <li>5.3.1 First Stage</li> <li>5.3.2 Second stage</li> </ul>                                                                                                                                                                                                                   |                                                  |

| Archited<br>5.1<br>5.2<br>5.3<br>5.4               | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification<br>5.2.2 Digit and Corner-cut Detection and Classification<br>Labelling and Training<br>5.3.1 First Stage<br>5.3.2 Second stage<br>Real-time Prediction                                                                                                                                                                                                                                         |                                                  |

| Archited<br>5.1<br>5.2<br>5.3<br>5.4               | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification<br>5.2.2 Digit and Corner-cut Detection and Classification<br>Labelling and Training<br>5.3.1 First Stage<br>5.3.2 Second stage<br>Real-time Prediction<br>Results                                                                                                                                                                                                                              |                                                  |

| Archited<br>5.1<br>5.2<br>5.3<br>5.4               | ctures<br>Introduction<br>Proposed Architecture<br>5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification<br>5.2.2 Digit and Corner-cut Detection and Classification<br>Labelling and Training<br>5.3.1 First Stage<br>5.3.2 Second stage<br>Real-time Prediction<br>Results<br>5.5.1 Model Comparison                                                                                                                                                                                                    |                                                  |

| Archited<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6 | ctures       Introduction         Proposed Architecture.       5.2.1 Windshield Detection, CVSA Decal Detection, and Colour Classification         5.2.2 Digit and Corner-cut Detection and Classification       5.2.2 Digit and Corner-cut Detection and Classification         Labelling and Training.       5.3.1 First Stage.         5.3.2 Second stage       8.2.1 Real-time Prediction         Results.       5.5.1 Model Comparison         5.5.2 Hardware Accelerators Result Testing.       1.1.1 Provide Comparison |                                                  |

| 6.2     | Proposed Solution                                       | 120 |

|---------|---------------------------------------------------------|-----|

|         | 6.2.1 HAZMAT Placard Localization and Classification    |     |

|         | 6.2.2 UN/NA Number Localization and Class Recognition   |     |

|         | 6.2.3 UN/NA Number Recognition                          |     |

| 6.3     | Dataset Description                                     | 124 |

|         | 6.3.1 Dataset                                           |     |

|         | 6.3.2 Dataset Augmentations                             |     |

| 6.4     | Training Methodology                                    | 128 |

|         | 6.4.1 Model and Training Environment.                   | 128 |

|         | 6.4.2 Models Training                                   |     |

| 6.5     | Real-time Prediction Methodology                        | 130 |

| 6.6     | Results                                                 | 133 |

|         | 6.6.1 Testing Environments                              |     |

|         | 6.6.2 Performance Metric                                | 134 |

|         | 6.6.3 Stage 1 Training Results Summary                  |     |

|         | 6.6.4 Stage 1 General Model Comparison                  |     |

|         | 6.6.5 Stage 2 and 3 Model Results                       |     |

|         | 6.6.6 Edge Hardware Deployment and Real-Time Results    | 139 |

|         | 6.6.7 Comparison to Others' Works                       | 141 |

| 6.7     | Discussion                                              | 143 |

|         | 6.7.1 General                                           | 143 |

|         | 6.7.2 Placard Localization (Stage 1) Deployment Results |     |

| 6.8     | Summary                                                 | 144 |

| Part IV | Conclusion                                              | 146 |

| Chapter | 7: Conclusions and Future Work                          | 147 |

| 7.1     | Conclusions                                             | 147 |

| 7.2     | Future Work                                             | 151 |

| Referen | ces                                                     |     |

# LIST OF TABLES

| 2.1         | Summary of object detection components                                                                                                  | 27  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1         | Architecture layers using stride >1                                                                                                     | 51  |

| 3.2         | Comparisons of the Regular convolution and Winograd Stride Two                                                                          | 52  |

| 3.3         | Performance Comparison using stride two in GPU                                                                                          | 52  |

| 3.4         | Modified VGG-16 Architecture with convolution stride two                                                                                | 53  |

| 3.5         | Resource Utilization of different PEs for kernel=3×3 on INTEL ARRIA-10                                                                  | 60  |

| 3.6         | Resource Utilization of CNN accelerator on INTEL ARRIA-10                                                                               | 62  |

| 3.7         | Performance comparison with state-of-the-art FPGA accelerators                                                                          | 63  |

| 4.1         | Bottleneck Residual Block Structure                                                                                                     | 71  |

| 4.2         | License plate localization neural network used as feature extractor                                                                     | 74  |

| 4.3         | Public datasets used to train the deep learning model                                                                                   | 82  |

| 4.4         | Comparison of LPL algorithms on the Caltech Cars 1999 (rear) 2 dataset                                                                  | 84  |

| 4.5<br>reco | Comparison of license plate localization algorithms on the University of Zagreb plate determinition, and automated storage dataset      |     |

| 4.6         | Set specifics of the NTUA Medialab LPR Database                                                                                         | 86  |

|             | Comparison of License Plate Localization Algorithms on the NTUA Medialab LPR Data                                                       |     |

| 4.8         | The proposed license plate localization deep learning architecture compared to popular DI                                               | Ĺ   |

|             | The proposed license plate localization deep learning architecture compared to other deep ning license plate localization architectures |     |

| 5.1         | First stage backbone                                                                                                                    | 98  |

| 5.2         | Second stage backbone                                                                                                                   | 99  |

| 5.3         | Summary of model training and results                                                                                                   | 111 |

| 5.4         | Hardware accelerator benchmark                                                                                                          | 113 |

|             | Neural Network Architecture for UN/NA Number Detection and Class Identification Feat ractor                                             |     |

| 6.2         | Modified ResNet-18 Backbone for UN/NA Number Recognition                                                                                | 124 |

| 6.3         | -                                                                                                                                       |     |

| 6.4         |                                                                                                                                         |     |

| 6.5         | Summary of Model Training and Results for Stage 1                                                                                       | 134 |

| 6.6 | Summary of Model Results for Stage 2      | 138 |

|-----|-------------------------------------------|-----|

| 6.7 | Summary of Model Results for Stage 3      | 138 |

| 6.8 | Results: Real-time Prediction Speed (FPS) | 140 |

| 6.9 | Per-Class comparisons                     | 142 |

# LIST OF FIGURES

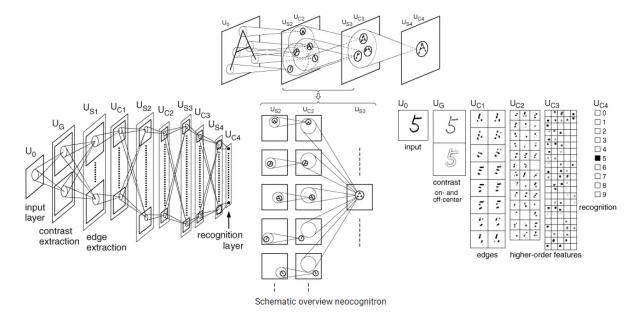

| 2.1         | Neocognition                                                                                                                          | 4   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

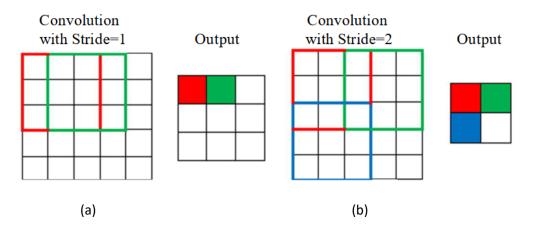

| 2.2         | Convolution with stride equal to 1 and 2                                                                                              | 5   |

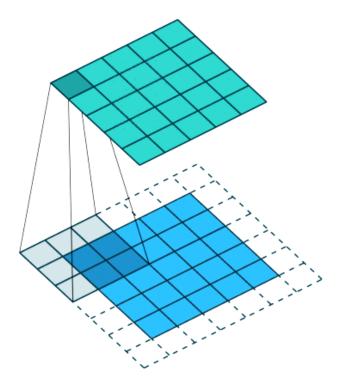

| 2.3         | Convolution with padding to 1 1                                                                                                       | 6   |

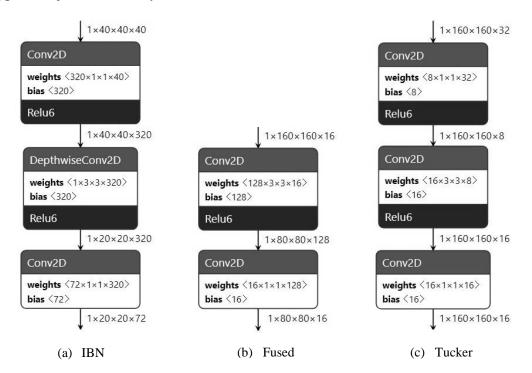

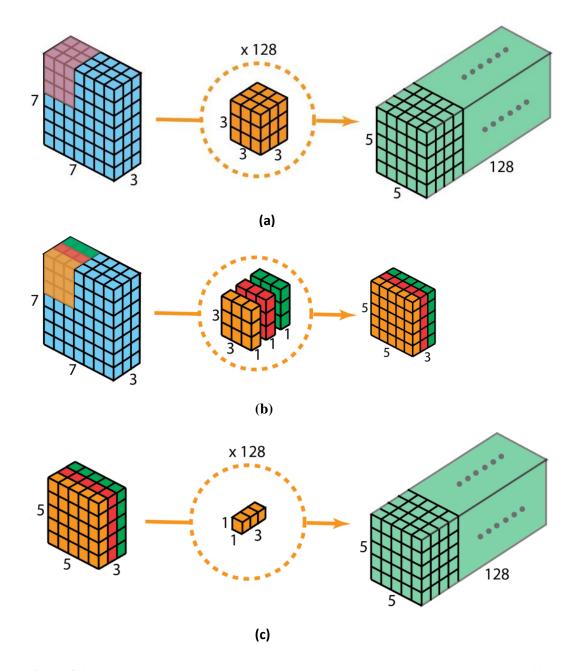

| 2.4         | (a) IBN layer, (b) Fused layer, and (c) Tucker layer                                                                                  | 20  |

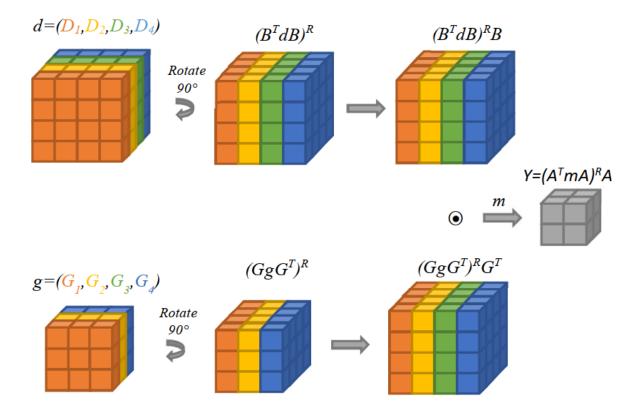

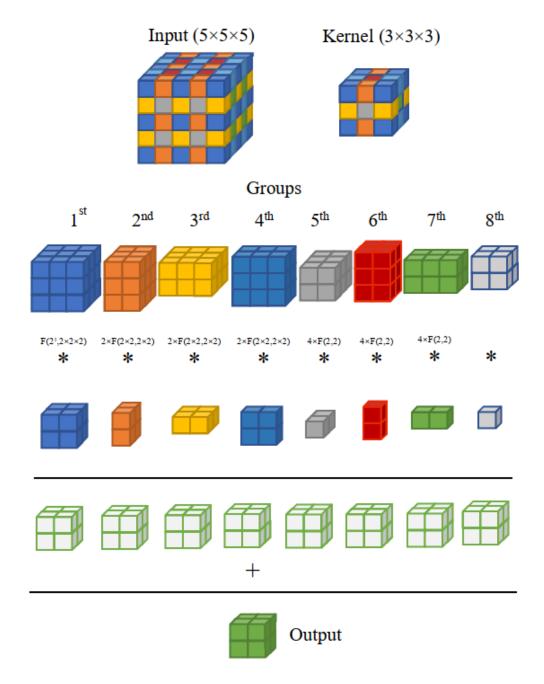

| 2.5         | Process of the 3D Winograd algorithm                                                                                                  | 24  |

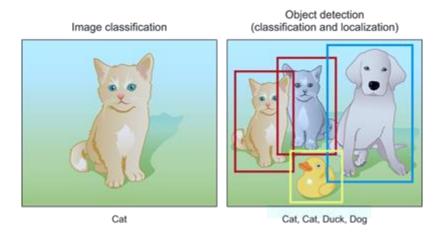

| 2.6         | (a) Image classification , (b) object detection                                                                                       | 6   |

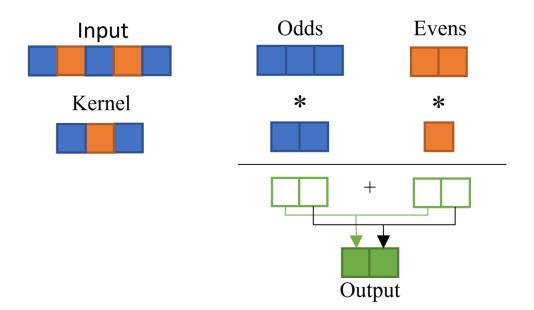

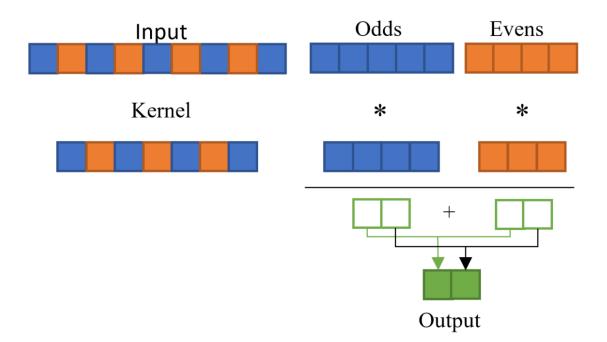

| 3.1         | Proposed convolution with stride=2 for kernel=3                                                                                       | 5   |

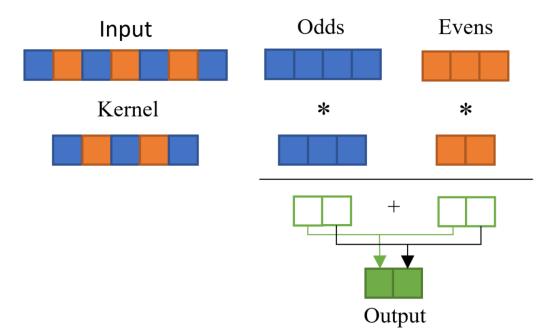

| 3.2         | Proposed convolution with stride=2 for kernel=5                                                                                       | 6   |

| 3.3         | Proposed convolution with stride=2 for kernel=7                                                                                       | 7   |

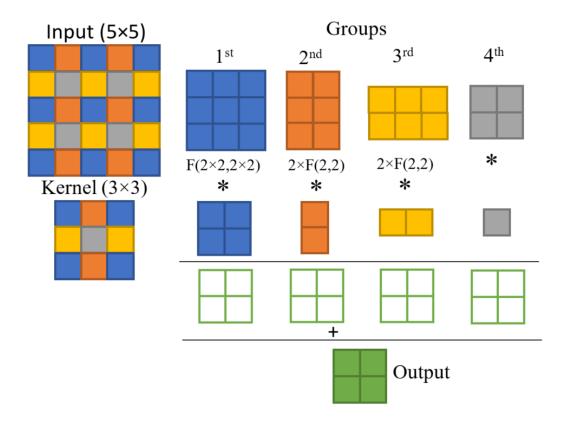

| 3.4         | Proposed convolution with stride=2 for kernel=3×3                                                                                     | 0   |

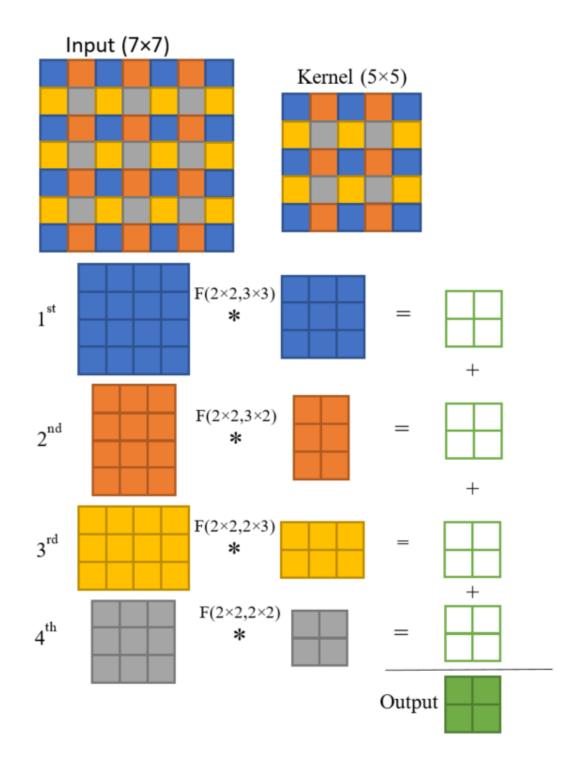

| 3.5         | Proposed convolution with stride=2 for kernel=5×5                                                                                     | -2  |

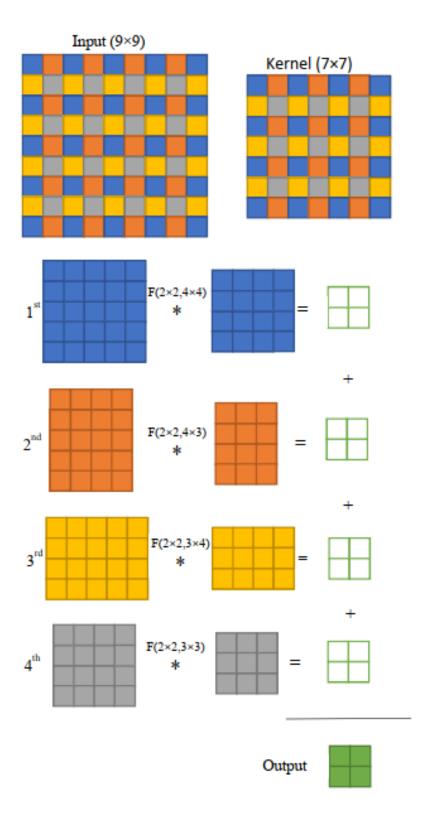

| 3.6         | Proposed convolution with stride=2 for kernel=7×7                                                                                     | 4   |

| 3.7         | Proposed convolution with stride=2 for kernel=3×3×3                                                                                   | 7   |

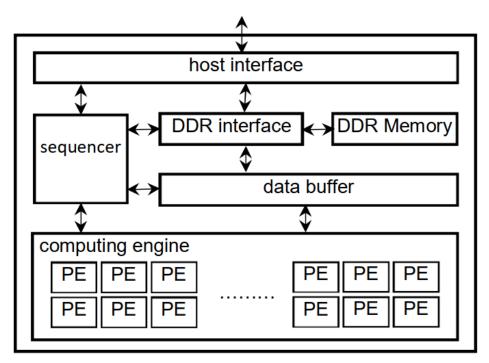

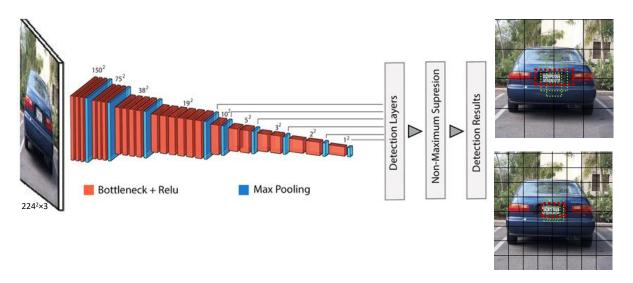

| 3.8         | Deep learning architecture                                                                                                            | 5   |

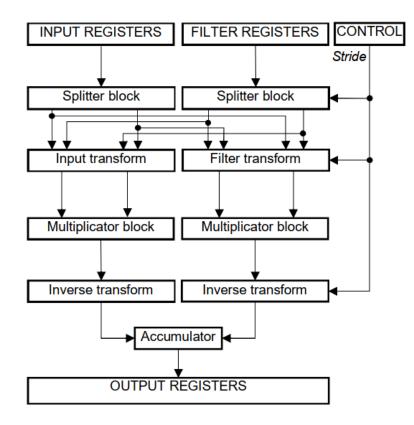

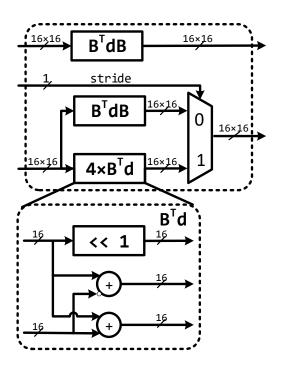

| 3.9         | Proposed PE architecture                                                                                                              | 6   |

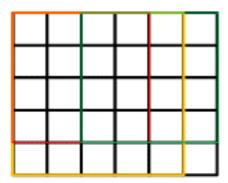

| 3.10        | Splitter the input in based on the stride selected                                                                                    | 8   |

| 3.11        | Input transform block                                                                                                                 | 8   |

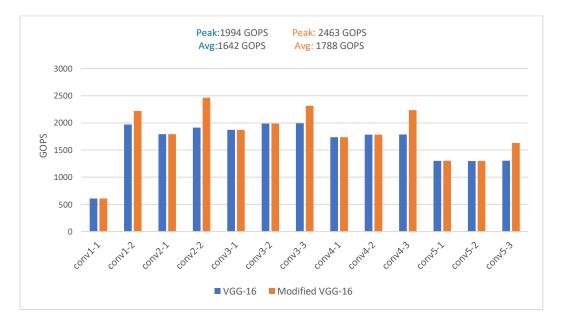

|             | Evaluation results of the original VGG-16 architecture compared to the proposed modified G-16 architecture                            | 51  |

| 4.1<br>dept | Standard vs. depthwise separable convolution operations to demonstrate the effectiveness of hwise separable convolution over standard | 2'2 |

| 4.2         | Architecture of the proposed license plate localization method                                                                        | '5  |

| 4.3         | Images of plate regions on vehicles labelled using labelImg7                                                                          | 6   |

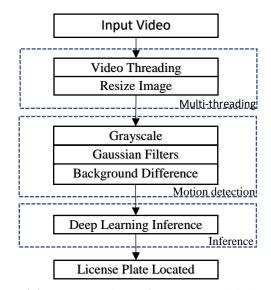

|             | Program flow of proposed multi-threading video capture with motion detection then inference 7                                         |     |

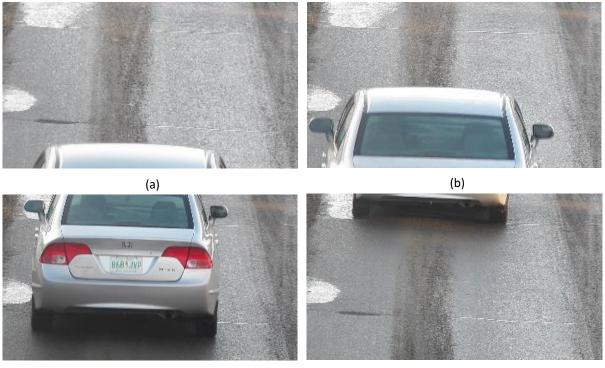

|             | Frames of a vehicle travelling at highway speed passing under a camera setup                                                          |     |

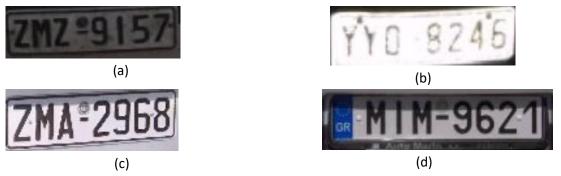

| 4.6         | Different obstructions on license plates in images from the NTUA Medialab dataset                                                     | 32  |

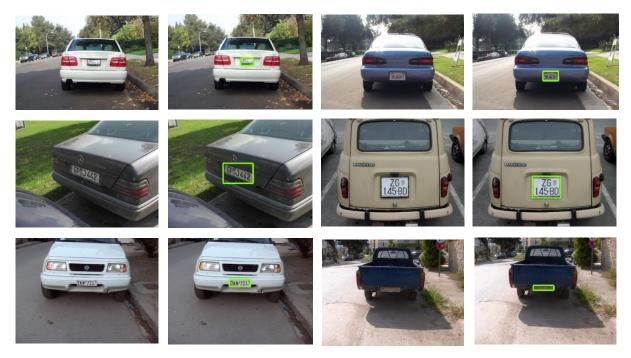

| 4.7<br>prop | Images of vehicles and their corresponding respective localized license plates generated by the bosed method                          | 33  |

| 4.8         | Real-time can detect one or multiple license plates at the same time                                                                  | 0   |

| 5.1         | CVSA decal color types                                                                                                                | 93  |

| 5.2 | Trucks with CVSA decals on different highways                                   | . 100 |

|-----|---------------------------------------------------------------------------------|-------|

| 5.3 | Windshield and CVSA decal labelled using the LabelImg program                   | . 102 |

| 5.4 | Digit and corner-cut labelled in a CVSA decal                                   | . 103 |

| 5.5 | (a) 7 spots filled, (b) 5 spots filled, and (c) 3 spots filled                  | . 105 |

| 5.6 | Real-time CVSA Decals Recognition Systems (CDRS)                                | . 108 |

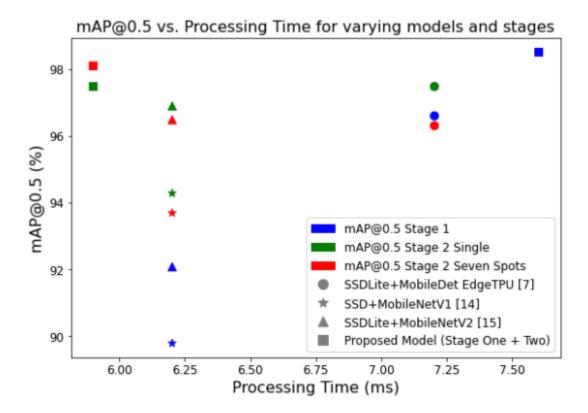

| 5.7 | Comparison of accuracy (mAP) vs. processing time by stage                       | . 110 |

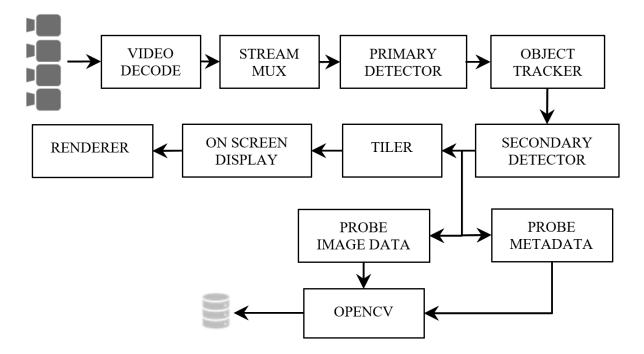

| 5.8 | DeepStream pipeline for the real-time CDRS on the Jetson Xavier                 | . 114 |

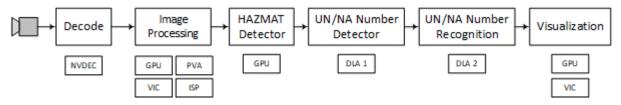

| 6.1 | HAZMAT recognition system                                                       | . 120 |

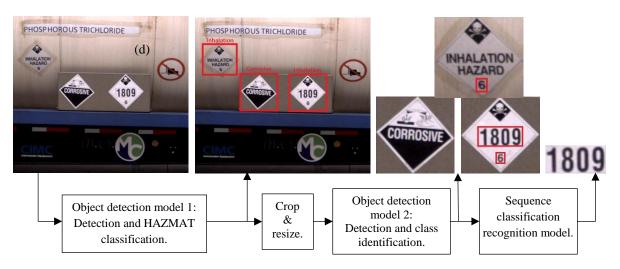

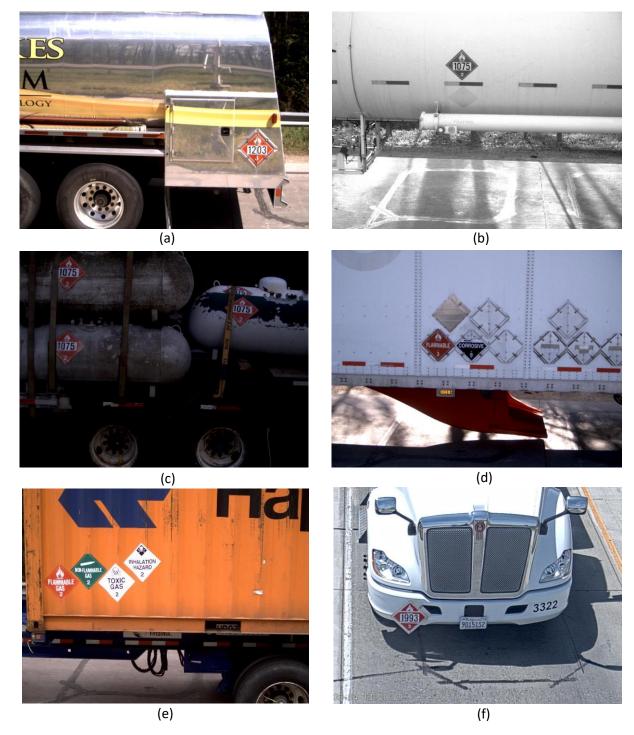

| 6.2 | UN/NA number recognition                                                        | . 123 |

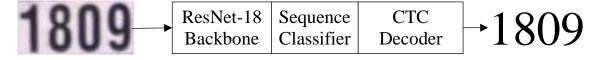

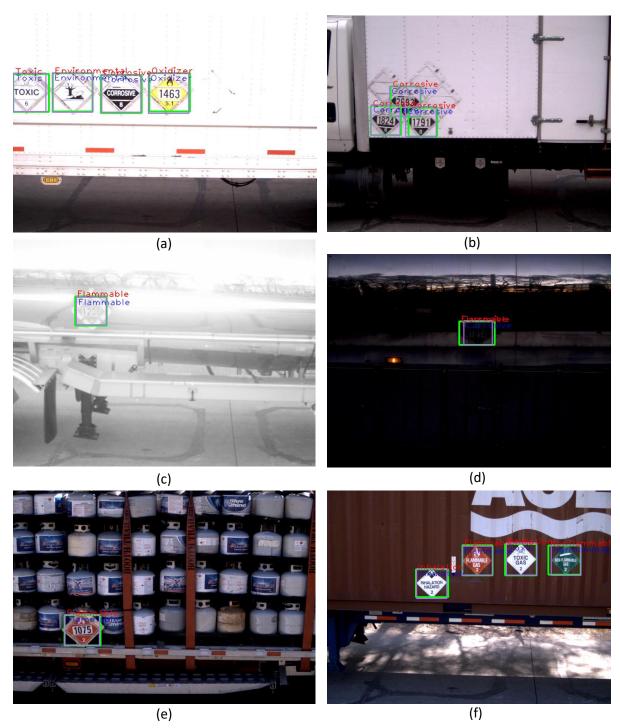

| 6.3 | Example images from the dataset                                                 | . 126 |

| 6.4 | Processing pipeline as deployed on the Jetsons, possible using Nvidia libraries | . 131 |

| 6.5 | Example test set inferences of the quantized SSDlite + Custom model             | . 137 |

|     |                                                                                 |       |

## LIST OF ABBREVIATIONS

| AI     | Artificial Intelligence                            |

|--------|----------------------------------------------------|

| ALPR   | Automatic License Plate Recognition                |

| AMQP   | Advanced Message Queuing Protocol                  |

| ANN    | Artificial Neural Network                          |

| AP     | Average Precision                                  |

| ASCII  | American Standard Code for Information Interchange |

| CDRS   | CVSA Decals Recognition Systems                    |

| CNN    | Convolutional Neural Network                       |

| CPU    | Central Processing Unit                            |

| CuDNN  | NVIDIA CUDA Deep Neural Network Library            |

| CV     | Computer Vision                                    |

| CVSA   | Commercial Vehicle Safety Alliance                 |

| DL     | Deep Learning                                      |

| DNN    | Deep Neural Network                                |

| DSP    | Digital Signal Processing                          |

| FLOPS  | Floating Point Operations Per Second               |

| FPGA   | Field-Programmable Gate Array                      |

| FPN    | Feature Pyramid Network                            |

| FPS    | Frames per Second                                  |

| GHz    | Gigahertz                                          |

| GOPS   | Giga Operations Per Second                         |

| GPU    | Graphics Processing Unit                           |

| HAZMAT | Hazardous materials                                |

| IBN    | Inverted Bottleneck Network                        |

| IoT    | Internet of things                                 |

| IoU                                                                       | Intersection over Union                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ITS                                                                       | Intelligent Transportation System                                                                                                                                                                                                                                                                                        |

| LiDAR                                                                     | Light Detection and Ranging                                                                                                                                                                                                                                                                                              |

| LPL                                                                       | License Plate Localization                                                                                                                                                                                                                                                                                               |

| LSTM                                                                      | Long Short-Term Memory                                                                                                                                                                                                                                                                                                   |

| mAP                                                                       | Mean Average Precision                                                                                                                                                                                                                                                                                                   |

| ML                                                                        | Machine Learning                                                                                                                                                                                                                                                                                                         |

| MQTT                                                                      | Message Queuing Telemetry Transport                                                                                                                                                                                                                                                                                      |

| NA                                                                        | North American                                                                                                                                                                                                                                                                                                           |

| NAS                                                                       | Neural Architecture Search                                                                                                                                                                                                                                                                                               |

| NTUA                                                                      | National Technical University of Athens                                                                                                                                                                                                                                                                                  |

| OCR                                                                       | Optical Character Recognition                                                                                                                                                                                                                                                                                            |

| OpenCL                                                                    | Open Computing Language                                                                                                                                                                                                                                                                                                  |

| PASCAL                                                                    | Pattern Analysis, Statistical Modelling and Computational Learning                                                                                                                                                                                                                                                       |

| PE                                                                        | Processing Element                                                                                                                                                                                                                                                                                                       |

| DAM                                                                       | Dandam Aaaaa Mamam                                                                                                                                                                                                                                                                                                       |

| RAM                                                                       | Random Access Memory                                                                                                                                                                                                                                                                                                     |

| R-CNN                                                                     | Region-based Convolutional Neural Network                                                                                                                                                                                                                                                                                |

|                                                                           | ·                                                                                                                                                                                                                                                                                                                        |

| R-CNN                                                                     | Region-based Convolutional Neural Network                                                                                                                                                                                                                                                                                |

| R-CNN<br>ReLU                                                             | Region-based Convolutional Neural Network<br>Rectified Linear Unit                                                                                                                                                                                                                                                       |

| R-CNN<br>ReLU<br>R-FCN                                                    | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network                                                                                                                                                                                                           |

| R-CNN<br>ReLU<br>R-FCN<br>RNN                                             | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network                                                                                                                                                                               |

| R-CNN<br>ReLU<br>R-FCN<br>RNN<br>ROI                                      | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network<br>Region of Interest                                                                                                                                                         |

| R-CNN<br>ReLU<br>R-FCN<br>RNN<br>ROI<br>RPN                               | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network<br>Region of Interest<br>Region Proposal Network                                                                                                                              |

| R-CNN<br>ReLU<br>R-FCN<br>RNN<br>ROI<br>RPN<br>SSD                        | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network<br>Region of Interest<br>Region Proposal Network<br>Single Shot Detector                                                                                                      |

| R-CNN<br>ReLU<br>R-FCN<br>RNN<br>ROI<br>RPN<br>SSD<br>SSVD                | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network<br>Region of Interest<br>Region Proposal Network<br>Single Shot Detector<br>Single Shot Video Object Detector                                                                 |

| R-CNN<br>ReLU<br>R-FCN<br>RNN<br>ROI<br>RPN<br>SSD<br>SSVD<br>UN          | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network<br>Region of Interest<br>Region Proposal Network<br>Single Shot Detector<br>Single Shot Video Object Detector<br>United Nations                                               |

| R-CNN<br>ReLU<br>R-FCN<br>RNN<br>ROI<br>RPN<br>SSD<br>SSVD<br>UN<br>USDOT | Region-based Convolutional Neural Network<br>Rectified Linear Unit<br>Region-based Fully Convolutional Network<br>Recurrent Neural Network<br>Region of Interest<br>Region Proposal Network<br>Single Shot Detector<br>Single Shot Video Object Detector<br>United Nations<br>United States Department of Transportation |

- WMFAs Winograd Minimal Filtering Algorithms

- YOLO You Only Look Once

# Part I

Preface

#### CHAPTER 1

#### INTRODUCTION

This chapter presents intelligent transportation systems (ITS), artificial intelligence in the context of ITS, and the importance of optimizing network architectures and hardware. Developing optimized real-time ITS on low-cost devices may increase the utilization of these systems around the world; this has motivated the research works proposed in this thesis. Section 1.1 presents ITS. The motivations of the research works are presented in Section 1.2. Section 1.3 presents the overview of the research works. The contributions of these research works are summarized in Section 1.4.

#### 1.1 Intelligent Transportation Systems

Intelligent Transportation Systems (ITS), officially defined at the 1994 World Congress in Paris, encompass all technology-driven applications within the broad field of transportation designed to improve the general driving experience. ITS incorporates a wide variety of technologies (e.g. within the fields of telecommunication, ICT, networks, automation, and sensors), methods (e.g. data-driven, measurement and statistics, algorithms, computer vision, and artificial intelligence (AI)), and management techniques [1]. ITS objectives include protecting the health and safety of traffic actors and pedestrians, safeguarding the natural environment and its resources, and increasing the effectiveness and streamlining the efficiency of transportation in generals, supply chains, cities and highways, and the broader field of ITS itself [2].

Innovative ITS services produce useful gains within transportation, traffic management, and traffic control. A well-designed system will communicate with applicable users or other systems to encourage safer and more coordinated utilization of transport channels [1]. ITS aims to improve traffic planners and road users' safety, mobility, productivity, and environmental performance [2].

Traditional ITS approaches use dedicated hardware such as inductive loop detectors, radar detectors, and laser detectors to locate vehicles and determine their speeds and characteristics, but such equipment may incur high maintenance and installation costs. Compared to these traditional sensor-based approaches, video cameras are more advantageous in terms of cost and flexibility [3].

Video cameras have long since been deployed for traffic surveillance because they provide important contextual information for human consumption and understanding [4]. Due to decreasing costs (Moore's Law), the number and coverage of road cameras has dramatically increased in recent years, resulting in broad accessibility of image/video data; this has led to the feasibility of camera image-based object detection—an incredibly promising new technique for large-scale traffic data analysis. Video analysis within the scope of smart transportation public safety has led to research and advancements in both academia and industry [4].

Compared with the "traditional" transportation system, the most significant characteristic of ITS is the integration of data-driven approaches including AI [5]. Leveraging AI for transportation may help the sector increase passenger safety, reduce traffic congestion and accidents, lessen carbon emissions, and minimize overall financial expenses for industries, governments, companies, and consumers.

AI can be defined as a technology that allows machines to learn from experience, oftentimes guided by human knowledge. Machines with AI capabilities can learn to mimic humans, automate manual tasks, create aesthetically-pleasing works, and practice continual learning—just like humans [6]. Computer/AI-driven automation frees human operators from repetitive and time-consuming tasks in a way that may also lessen (human) operator fatigue and stimulate higher and more deterministic accuracy. Moreover, specific AI-powered systems may exhibit human-level accuracy and/or continuous learning with new experiences, which may indicate the potential for AI-powered machines to self-improve and perform tasks that require critical-thinking or higher-level functions—possibly without human intervention, depending on task complexity [6]. Governments, the transportation sector, and academic institutions are making significant investments in

this relatively new and near limitless AI field [5]. Novel general or custom-tailored AIbased applications are designed with an emphasis on improving speed and accuracy, but also reliability, efficiency, robustness, quality, and—where applicable—safety.

#### 1.2 Motivation of Research Works

Recent and rapid AI developments have provided unprecedented opportunities to revolutionize different fields, industries, and businesses, including within the transport sector. Intelligent Transportation Systems (ITS) have seen a rise in application development through the implementation of AI methods [5]. One of the most promising areas of research within AI is computer vision.

Computer vision enables computers to process visual data and extract information from that data at a baseline level [7]. Visual input/output tends to be highly interpretable by humans, which can be useful for the design and implementation of certain systems. The general goal of computer vision is to teach computers how to identify, classify, and categorize the visual world as humans do. Although the field of computer vision has existed for some time, the advent of deep learning to computer vision pipelines has led to a revolution in vision technologies and systems [6].

Deep learning (DL) has made computer vision algorithms highly effective for realworld applications [6]. One famous DL architecture originally designed for image data is the convolutional neural network (CNN) [8]. CNNs have made computer vision feasible and relatively inexpensive for industrial applications, leading to high industry investment and adoption, especially for task automation.

In general, DL models consist of many of layers and parameters. For example, Deep Neural Networks (DNN) and Convolutional Neural Networks (CNN) require upwards of millions (sometimes into the billions) of interconnected units and parameters [8]. As a result, running most current DL applications requires high-performance computers with expensive GPUs, or centralized servers and/or cloud-based systems [9]. This can be a

huge limitation in terms of system implementation cost, e.g. on highways or remote locations where the Internet/remote access is limited.

Rather than sending real-time video to the cloud—which can be very expensive in terms of time and data consumption—the main goal of this thesis is the implementation of ITS systems on edge devices. This minimizes both data transmission time and system latency, as well as reduces the cost of data transmission, computation, and storage. Additionally, processing data at the edge can preserve the privacy of users and the integrity of the raw data itself, because uploading the video/images is unnecessary [9].

Due to the limited memory and computational resources of edge devices, powerefficient computation can be designed by reducing the number of hardware-expensive computations (i.e. multiplications) for convolutions making the development of custom and more specialized DL architectures becomes necessary.

#### 1.3 Research Objectives

The main objective of this present study is to unify recent advancements in deep learning architectures with the design of optimized computing hardware, with an emphasis on the development of new and novel applications with the scope of ITS on edge devices.

The specific objectives of this thesis are as follows:

- 1. Formulate algorithms to enhance the calculation of convolution stride 2 particularly important for deep learning object detection systems—using fewer hardware resources.

- Design a processing element capable of supporting both stride 1 and 2 convolution, to enhance FPGA efficiency.

- Benchmark the DSP efficiency of the processing elements implemented on an FPGA.

- 4. Develop ITS applications based on deep learning architectures that use convolution strides 1 and 2.

- 5. Design custom optimized deep learning models for specific detection/recognition tasks in each system.

- Implement and evaluate the ITS applications on available edge devices and hardware accelerators.

#### 1.4 Overview of Research Works

In this thesis, based on the motivation discussed in Section 1.2, optimized CNN algorithms and architectures capable of achieving a high convolution speed are proposed. The algorithms for 1-D, 2-D, and 3-D convolution reduce the number of multiplications when a convolution of stride 2 is performed. A Processing Element (PE) for a  $3\times3$  kernel, compatible with both stride 1 and 2 convolutions is introduced. Therefore, three ITS applications are presented: a License plate localization (LPL) system, a CVSA decal recognition system, and a HAZMAT recognition system. The applications are capable of deployment in real-time in complex outdoor environments. The whole thesis is composed of four parts with seven chapter shown as follows:

- Part I Preface includes:

- Chapter 1 *Introduction*: presents the importance of deep learning and the motivations, the overview, and the contributions of the research works.

- Chapter 2 *Background*: introduces the background information required to present the proposed research works.

- Part II Hardware Optimization for Convolutional Neural Networks includes:

- Chapter 3 *Stride 2 Winograd for Convolutional Neural Networks*: present a novel method to apply the Winograd algorithm to a stride (shift-displacement of a kernel over an input) of two. This method is valid for one, two, or three dimensions. In this chapter, new Winograd versions compatible with a kernel of size three, five, and seven were introduced. The algorithms were

successfully implemented on an NVIDIA K20c GPU and an Intel Arria-10 FPGA. The proposed implementation uses a novel Processing Element (PE) able to perform two Winograd stride one, or one Winograd stride two, operations per clock cycle. Compared to regular convolutions and other designs, the proposed implementations provide fast convolution for stride one and two and high DSP efficiencies.

- Part III Intelligent Transportation Systems Applications include:

- Chapter 4 Deep Learning-based Embedded License Plate Localization System: presents a novel neural network architecture for license plate localization (LPL) based on an inverted residual structure where the shortcut connections are between the linear bottleneck layers. The proposed deep learning (DL) solution was tested against three popular international research databases and achieves state-of-the-art results, proving that the proposed model is accurate and robust. Across those databases, the proposed model surpasses other recent LPL work, including DL-based methods, in terms of accuracy and speed. The proposed architecture is shown to have significant speedup and computational efficiency gains over other DL models, and to have fast per-image localization processing times sufficient for applications deployed on expensive and commodity hardware alike. Using a novel multi-threading video capture with motion detection then inference algorithm, computational efficiency is increased, thus dropping less frames overall and allowing for increased performance. Repeated tests show the proposed method is well-suited to realtime and highly accurate LPL, regardless of hardware.

- Chapter 5 *Real-time CVSA Decals Recognition System Using Deep Convolutional Neural Network Architectures*: presents a 2-step automatic Commercial Vehicle Safety Alliance (CVSA) decal recognition system using deep convolutional neural network architectures. The MobileDet architecture was used as a baseline for the proposed system and customized to better suit the system's tasks. The first step localizes a vehicle's windshield and the CVSA decal within, and classifies the decal colour. The CVSA decal is

cropped and used as input to the second stage, which localizes and classifies a digit and the corner-cut of a CVSA decal. The custom architectures reduce processing time and exceed accuracies relative to pre-trained architectures. The proposed model was implemented on different edge hardware accelerators, and the performance on each – in terms of high inference speed, real-time video processing, and high mean average precision – was contrasted.

- Chapter 6 *Real-Time Deep Learning-based Edge System for HAZMAT Recognition*: presents a 3-stages cascading system using deep learning networks. The first network localizes and classifies the HAZMAT placard. If the placard contains a United Nations (UN) / North American (NA) number, the second network localizes that number and identifies the nature of the substance. The third network recognizes the UN/NA number. For both the first and second stage, an SSDlite object detection network was developed using custom backbones based on MobileDet. For the third stage, a segmentation-free UN/NA number recognition network was developed using a lightweight sequence classification model. The system was deployed on a variety of AI edge hardware accelerators from vendors like NVIDIA, Google, and Intel, and performance differences among the accelerators were subsequently compared. For each stage, a detailed comparison with other networks was provided.

- Part IV Conclusions includes:

- Chapter 7 Conclusions *and Future Work*: includes the conclusions of all presented research works and the plan for futures works.

#### 1.5 Summary of Contribution

In this thesis, a novel set of algorithms are introduced to calculate the convolution when using a kernel sliding by two units about the input; this convolution is called "convolution stride 2". The presented algorithms of convolution stride 2 are based on the conventional Winograd Minimal Filtering Algorithm, which is only formulated for convolutions of stride 1. The proposed novel algorithms calculate the convolution stride 2 results using less multiplications than conventional convolution. They work in one, two and three dimensions using respective kernels of size 3, 5, 7,  $3 \times 3$ ,  $5 \times 5$ ,  $7 \times 7$ , and  $3 \times 3 \times 3$ . The convolution stride 2 downsamples the feature maps while preserving spatial information via feature learning. As further explained in Part II, this characteristic is particularly important for object detection systems. A novel Processing Element (PE) is presented that is able to perform two Winograd stride one, or one Winograd stride two, operations per clock cycle. The convolution stride 2 was implemented on an NVIDIA K20c GPU and an Intel Arria-10 FPGA.

Furthermore, three deep learning-based systems for ITS are presented. The first is an embedded license plate localization system, the second is a real-time CVSA decal recognition system, and the third is a real-time edge system for HAZMAT recognition. For each system, custom object detection architectures that use a mix of stride 1 and 2 convolution are designed. The proposed architectures are optimized to achieve high accuracies and low processing times. This feature makes the systems suitable to the implementation on varying edge devices. To evaluate the speed of the proposed systems, various hardware accelerators were used, including the Nvidia Jetsons (Nano and Xavier), Intel's Neural Compute Sticks (versions 1 and 2), and Google's Coral USB accelerator. Each ITS application's deep learning architectures and corresponding accuracies and prediction speeds are analyzed in detail in their respective chapters. To highlight the advantages and improvements of the proposed systems over existing methods, the systems are compared against related works (where applicable).

In this thesis, the computational efficiency for CNNs is improved—especially those architectures designed for object detection—by providing new algorithms to accelerate layers with a convolutional stride of 2; these novel algorithms are introduced in Chapter 3. Using this research, custom object detection architectures capable of real-time prediction on edge computing devices were designed for ITS applications, , thus providing enormous cost and performance advantages compared to current implementations: Chapter 4 presents a license plate localization system, Chapter 5 a real-time recognition system for Commercial Vehicle Safety Alliance (CVSA) decals, and

Chapter 6 a real-time edge system for recognizing hazardous material (HAZMAT) placards.

Below is the list of publications, arranged according to the order of appearance in this thesis:

- Chapter 3 Stride 2 Winograd for Convolutional Neural Networks:

- J. Yepez and S. Ko, "Stride 2 1-D, 2-D, and 3-D Winograd for Convolutional Neural Networks", in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, n0. 4, pp. 853-863, April 2020.

- Chapter 4 Deep Learning-based Embedded License Plate Localization System:

- J. Yepez, R. D. Castro-Zunti and S. Ko, "Deep learning-based embedded license plate localisation system", in IET Intelligent Transport Systems, vol. 13, no.10, pp. 1569-1578, 10 2019.

- Chapter 5 Real-time CVSA Decals Recognition System Using Deep Convolutional Neural Network Architectures:

- J. Yepez, R. D. Castro-Zunti and S. Ko, "Real-time CVSA Decals Recognition System Using Deep Convolutional Neural Network Architectures", in IET Intelligent Transport Systems 1–13 (2021), https://doi.org/10.1049/itr2.12103.

- Chapter 6 Real-Time Deep Learning-based Edge System for HAZMAT Recognition:

- J. Yepez, R. D. Castro-Zunti and S. Ko, "Real-Time Deep Learning-based Edge System for HAZMAT Recognition", under review Springer Machine Vision and Applications, submitted July 2021.

- Other publications that are not included in this thesis:

- J. Yepez and S. Ko, "IoT-Based Intelligent Residential Kitchen Fire Prevention System", in J. Electr. Eng. Technol. 15, pp. 2823-2832, August 2020.

- R.D. Castro-Zunti, J. Yepez and S. Ko, "License plate segmentation and recognition system using deep learning and OpenVINO", in IET Intelligent Transport Systems, vol. 14, no. 2, pp. 119-126, 2 2020.

- J. Yepez, X. Shi, and S. Ko, "An FPGA-based Closed-loop Approach of Angular Displacement for a Resolver-to-Digital- Converter", 2018 IEEE International Symposium on Circuits and Systems (ISCAS). Florence, 2018, pp. 1-4

- A. Dinh, M. Bayati, M. Bhatti, J. Yepez, and J. Zhexin, "Design and Implementation of a Wireless Wearable Band for Gait Analysis," in 6th International Conference on the Development of Biomedical Engineering in Vietnam (BME6), 2018, pp. 693-698.

- Z. Jiang, J. Yepez, S. An, and S. Ko, "Fast, accurate and robust retinal vessel segmentation system," Biocybern. Biomed. Eng., pp. 1-10, 2017.

- X. Shi, J. Dai, X. Luo, J. Yepez, and S. Ko, "Foreground-Background Separation Guided by Statistical Features of Surveillance Video," IEEE/IEIE ICCE-Asia, pp. 3-6, 2016.

#### CHAPTER 2

#### BACKGROUND

This chapter present the background information of the proposed works in this thesis. Machine and deep learning concepts are presented in Section 2.1 Section 2.2 presents the convolutional neural networks. Section 2.3 presents optimized layers for convolution. Section 2.4 presents object detection works in the literature.

#### 2.1 Machine Learning and Deep Learning

Machine learning (ML) can be described as an application of artificial intelligence (AI) that allows a system to enhance the accuracy of its algorithm without explicit changes to the algorithm by a (human) programmer [10]. A ML apparatus makes predictions based on sets of data, and thus a wealth of data is usually required for a ML algorithm to be effective. The predictions can include images where the content is divided into different categories, one of the most important applications of deep learning, currently common in machine learning systems.