# **Techniques for Low-Cost Spectrum Analysis on Quadrature Demodulation Architectures**

A Thesis submitted

to the College of Graduate Studies and Research

in partial fulfillment of the requirements

for the degree of Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon

By Brendon Fredlund

#### **Permission to Use**

In presenting this thesis in partial fulfillment of the requirements for a Masters degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

University of Saskatchewan

57 Campus Drive

Saskatoon, Saskatchewan, Canada

S7N5A9

# **Abstract**

The Decimator, an SED Systems Ltd. product, is a PCI slot card that performs both time and frequency domain measurements of given input signals. It is essentially a more economical version of a bench spectrum analyzer or oscilloscope, with a PC interface. Several issues limit the speed and accuracy of the results of the Decimator, and the study of these issues is the focus of this thesis. These issues, including but not limited to, are as follows: 1) Imbalances between the received In-phase and Quadrature-phase channels; 2) The FFT and Windowing functions are performed by a microcontroller, but it is desired that they be migrated to an FPGA. While solutions to improve the first issue is being implemented and verified, the second issue is not one of simply reducing a source of error. The second issue requires a cost-benefit analysis on the migration of these signal processing algorithms from an ARM microcontroller to a Xilinx FPGA.

# **Acknowledgments**

I greatly appreciate the guidance my supervisor, Dr. Dinh, has given me during the writing of this thesis. His encouragement and insights were important in helping me find my way through uncharted waters.

I would also like to thank Dr. Salt for his time and consideration. He inspired me to pursue a Masters degree, and he gave me the contacts I needed to find a meaningful and practical thesis topic. He showed me that I did not need to jump into industry in order to meet professionals and work on real-world problems.

My father, Delwyn, has supervised hundreds of graduate students during his tenure at the U of S, and the advice he imparted was invaluable to my journey through the Masters program. By discussing my graduate program with him I was able to see him in a different light than I did growing up. He went from being "Dad" to being "Professor", and through this transformation I was easily able to identify the skills and abilities he has utilized in his decorated career as an Engineer.

The Engineers at SED Systems Ltd. have been more than generous with their time during the course of this thesis. Mr. Akins, Mr. Gunderson, Mr. Armstrong, and Mr. Warkentin were able to provide me with a meaningful thesis project and they helped me greatly along the way. There was no question or request too mundane for them, and for that I am truly grateful.

This thesis was funded by the TRLabs Graduate scholarship and by Professor Dinh. I sincerely appreciate having the financial means necessary to complete my studies.

# **Table of Contents**

| Permission to Use                             | i    |

|-----------------------------------------------|------|

| Abstract                                      | ii   |

| Acknowledgments                               | iii  |

| Table of Contents                             | iv   |

| Nomenclature                                  | vii  |

| Acronyms                                      | vii  |

| List of Figures.                              | viii |

| CHAPTER 1 : INTRODUCTION                      | 1    |

| 1.1 General                                   | 1    |

| 1.2 The Decimator                             | 2    |

| 1.3 Known Decimator Issues                    | 2    |

| 1.3.1 I/Q Imbalance                           | 2    |

| 1.4 Other Decimator modifications             | 3    |

| 1.4.1 Windowing                               | 4    |

| 1.4.2 Fast Fourier Transform.                 | 4    |

| 1.5 Decimator Modification Overview           | 5    |

| 1.6 Summary                                   | 6    |

| 1.7 Thesis Outline                            | 7    |

| CHAPTER 2 : LITERATURE REVIEW AND THEORY      | 8    |

| 2.1 Introduction                              | 8    |

| 2.2 Direct Conversion Receivers.              | 8    |

| 2.3 I/Q Imbalance                             | 10   |

| 2.4 I/Q Imbalance Correction Schemes.         | 17   |

| 2.4.1 Non-Data-Aided (NDA) Correction Schemes | 17   |

| 2.4.1.1 Blind Source Separation (BSS)         | 17   |

| 2.4.1.2 Interference Cancellation (IC)        | 19   |

| 2.4.1.3 Adaptive Methodologies Summary        | 20   |

| 2.4.1.4 Statistical Correction Method ("Stat")   | 21 |

|--------------------------------------------------|----|

| 2.4.1.5 Other Statistical Correction Schemes     | 26 |

| 2.4.2 Data-Aided (DA) Correction Schemes         | 28 |

| 2.4.3 I and Q Imbalance Conclusions              | 29 |

| 2.5 Windowing                                    | 29 |

| 2.5.1 Finite Register Length.                    | 34 |

| 2.6 Fast Fourier Transform (FFT)                 | 34 |

| 2.6.1 FFT Background                             | 35 |

| 2.6.1.1 Decimation-in-Time (DIT) Algorithms      | 36 |

| 2.6.1.2 Decimation-in-Frequency (DIF) Algorithms | 37 |

| 2.6.1.3 FFT Radix Size                           | 38 |

| 2.6.2 Finite Register Lengths                    | 39 |

| 2.6.2.1 Full Precision Unscaled                  | 40 |

| 2.6.2.2 Scaled Fixed Point.                      | 40 |

| 2.6.2.3 Block Floating Point (BFP)               | 41 |

| 2.6.3 Dynamic Range                              | 41 |

| CHAPTER 3: RESEARCH PROGRAM / METHODOLOGY        | 45 |

| 3.1 Introduction                                 | 45 |

| 3.2 I and Q Imbalance.                           | 45 |

| 3.2.1 Stat Design Overview                       | 45 |

| 3.2.2 Stat Sources of Error.                     | 48 |

| 3.2.2.1 Coefficient Estimate Accuracy            | 48 |

| 3.2.2.2 32-Bit Floating Point Stat Performance   | 50 |

| 3.2.2.3 Fixed Point Precision Affect on Stat     | 51 |

| 3.2.2.4 Arcsin Affect on Phase Estimates         | 52 |

| 3.2.3 Stat Resource Usage                        | 52 |

| 3.3 Windowing                                    | 53 |

| 3.4 Fast Fourier Transform (FFT)                 | 54 |

| 3.4.1 Xilinx FFT Core                            | 54 |

| 3.5 Windowing and FFT VHDL Simulation                         | 57 |

|---------------------------------------------------------------|----|

| 3.5.1 Block Floating Point (BFP) Versus 32-bit Floating Point | 59 |

| 3.5.2 16-bit Fixed Point Versus 32-bit Floating Point         | 60 |

| CHAPTER 4: PRESENTATION of the RESULTS                        | 61 |

| 4.1 Introduction                                              | 61 |

| 4.1.1 Stat Sources of Error                                   | 61 |

| 4.1.1.1 Coefficient Estimate Accuracy                         | 61 |

| 4.1.1.2 32-Bit Floating Point Stat Performance                | 63 |

| 4.1.1.3 Fixed Point Precision Affect on Stat                  | 69 |

| 4.1.1.4 Arcsin Affect on Phase Estimates                      | 70 |

| 4.1.2 VHDL Resource Requirements                              | 72 |

| 4.1.3 Speed Requirements                                      | 73 |

| 4.2 Windowing and the Fast Fourier Transform (FFT)            | 74 |

| 4.2.1 Simulation Results                                      | 74 |

| 4.2.1.1 Block Floating Point (BFP) Versus Floating Point      | 74 |

| 4.2.1.2 Fixed Point Versus BFP and Floating Point             | 78 |

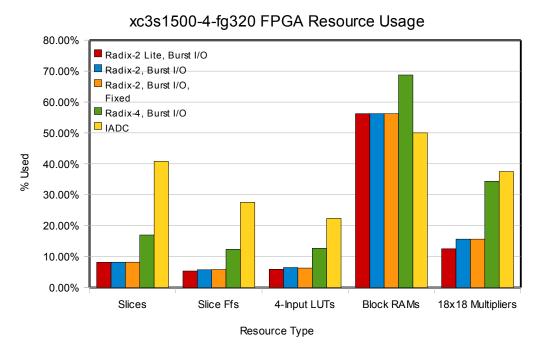

| 4.2.2 Hardware Usage                                          | 81 |

| 4.2.3 Speed Requirements                                      | 83 |

| CHAPTER 5: CONCLUSIONS and RECOMMENDATIONS                    | 84 |

| 5.1 Introduction                                              | 84 |

| 5.2 I and Q Imbalance                                         | 85 |

| 5.3 Windowing                                                 | 85 |

| 5.4 Fast Fourier Transform (FFT)                              | 86 |

| 5.5 Conclusions                                               | 86 |

| References                                                    | 88 |

#### **Nomenclature**

ξ Gain imbalance coefficientφ Phase imbalance coefficient

# **Acronyms**

ADC Analog to Digital Converter

BER Bit Error Rate

BFP Block Floating Point

BSS Blind Source Separation

DA Data Aided

DAC Digital to Analog Converter

DCR Direct Conversion Receiver

DIF Decimation In Frequency

DIT Decimation In Time

DSP Digital Signal Processing

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

IC Interference Cancellation

I In-phase

IRR Image Rejection Ratio

NDA Non-Data Aided

OFDM Orthogonal Frequency Division Multiplexing

LPF Low Pass Filter

Q Quadrature-phase

QAM Quadrature Amplitude Modulation

QPSK Quadrature Phase Shift Keying

RF Radio Frequency

SNR Signal to Noise Ratio

VHDL Very high speed integrated circuit Hardware Description Language

# **List of Figures**

| Figure 1.1: Decimator block diagram.                                                    | 5  |

|-----------------------------------------------------------------------------------------|----|

| Figure 2.1: Direct conversion receiver architecture.                                    | 9  |

| Figure 2.2: Example RF and baseband spectra depicting an I/Q imbalance                  | 11 |

| Figure 2.3: Image Rejection Ratio (IRR) with respect to gain and phase imbalances       | 13 |

| Figure 2.4: 4-QAM original modulation scheme                                            | 14 |

| Figure 2.5: 4-QAM gain imbalanced modulation, (2dB)                                     | 14 |

| Figure 2.6: 4-QAM phase imbalanced modulation, (10°)                                    | 15 |

| Figure 2.7: Received data corrupted by gain and phase imbalances                        | 16 |

| Figure 2.8: Independent Component Analysis problem definition                           | 18 |

| Figure 2.9: Torkkola's feedback network for separating convolved mixtures               | 19 |

| Figure 2.10: Adaptive interference canceler (IC) architecture                           | 20 |

| Figure 2.11: I and Q Imbalance Correction Block Diagram.                                | 25 |

| Figure 2.12: Simplified I and Q Imbalance Correction Block Diagram                      | 26 |

| Figure 2.13: Moseley and Slump's I and Q Imbalance Compensation Block Diagram           | 27 |

| Figure 2.14: Non-periodic frame of data from a periodic sinusoid                        | 30 |

| Figure 2.15: Periodic frame of data from a periodic sinusoid                            | 31 |

| Figure 2.16: Several common window functions                                            | 32 |

| Figure 2.17: Effect of the Hamming window on a periodic signal capture                  | 33 |

| Figure 2.18: Flow graph of an 8-point DIT decomposition.                                | 37 |

| Figure 2.19: Flow Graph of an 8-point DIF decomposition                                 | 38 |

| Figure 2.20: Xilinx dynamic range results.                                              | 43 |

| Figure 3.1: System level design of I/Q imbalance correction implementation              | 46 |

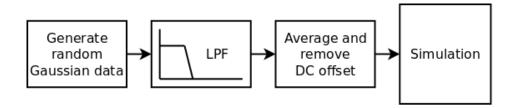

| Figure 3.2: Data generation for coefficient estimate accuracy simulation                | 49 |

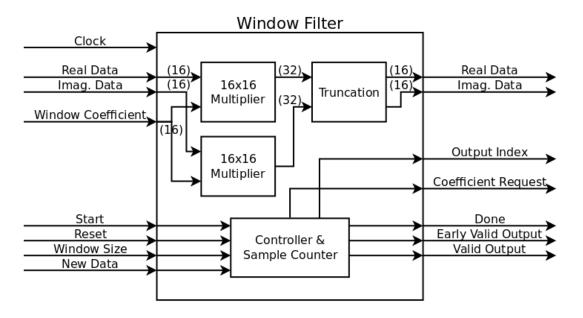

| Figure 3.3: Window filter VHDL implementation block diagram                             | 53 |

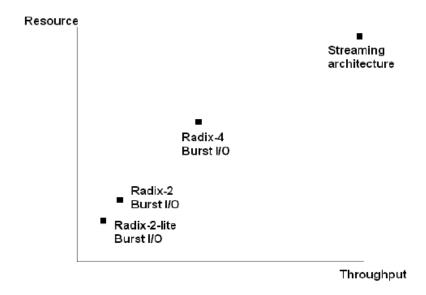

| Figure 3.4: Resource usage V.S. throughput for Xilinx architecture options [21]         | 55 |

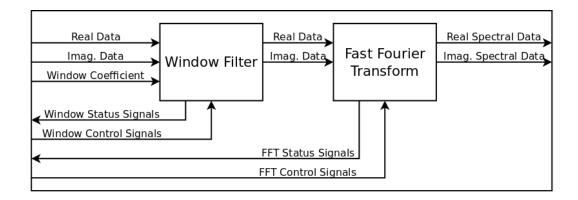

| Figure 3.5: Window filter and FFT system level layout                                   | 59 |

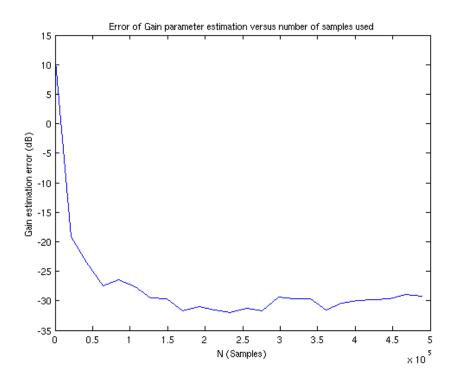

| Figure 4.1: Error of gain coefficient estimate with respect to number of samples used   | 62 |

| Figure 4.2: Error of phase coefficient estimate with respect to number of samples used. | 62 |

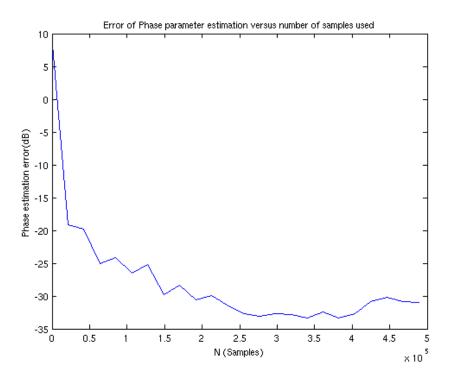

| Figure 4.3: Capture 1 – Error visualized using best fit line estimate                   | 63 |

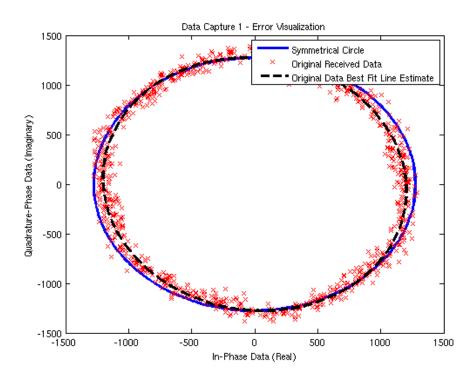

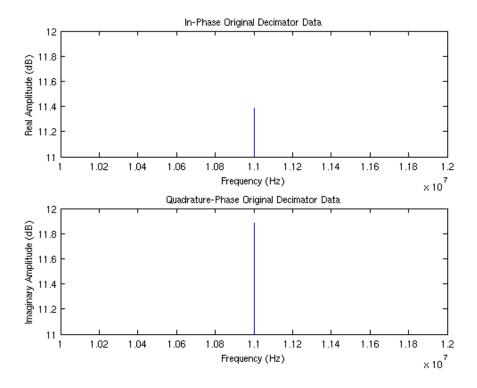

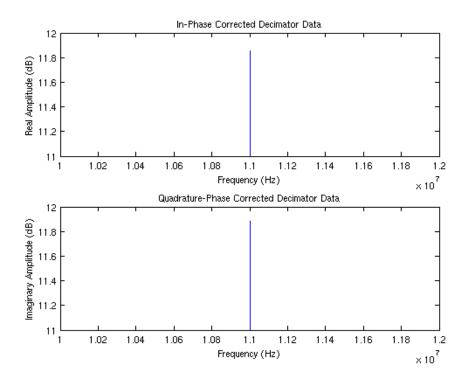

| Figure 4.4: Capture 1 – Spectral peaks before correction                                | 64 |

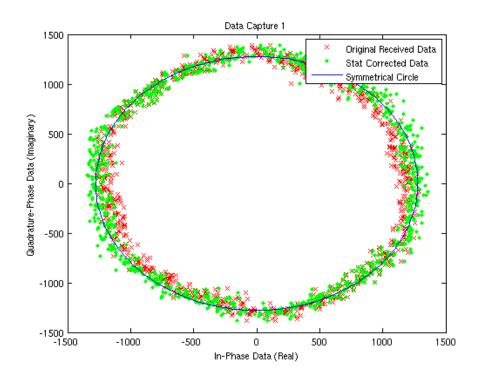

| Figure 4.5: Capture 1 - PSK modulated data with significant imbalances              | 65    |

|-------------------------------------------------------------------------------------|-------|

| Figure 4.6: Capture 1 - Spectral peaks after correction                             | 66    |

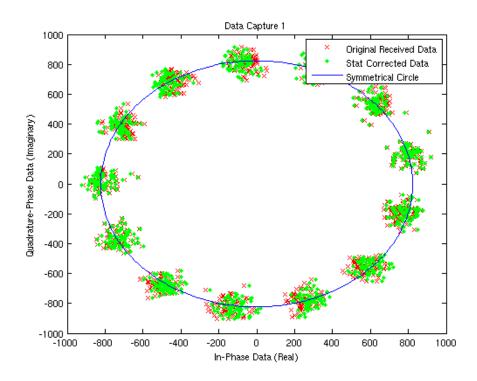

| Figure 4.7: Capture 2 - PSK modulated received data                                 | 67    |

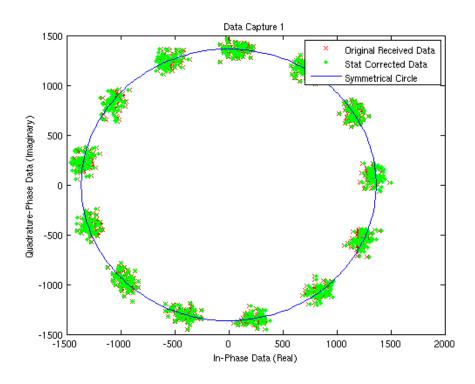

| Figure 4.8: Capture 3 - PSK modulated received data                                 | 68    |

| Figure 4.9: Data capture results summary                                            | 69    |

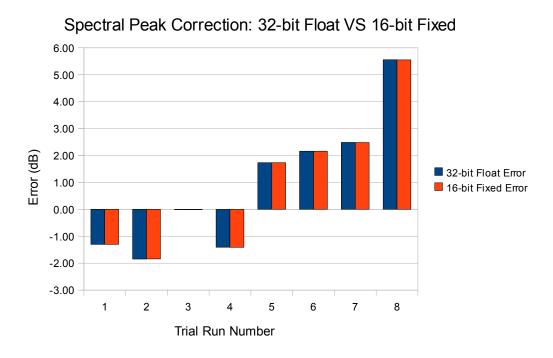

| Figure 4.10: Spectral peak error comparison between Matlab and Xilinx ISE simulatio | n. 69 |

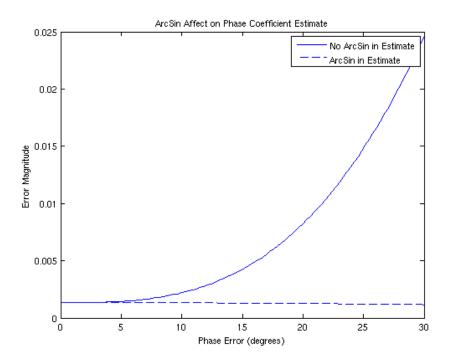

| Figure 4.11: Arcsin Affect on Phase Coefficient Estimate                            | 70    |

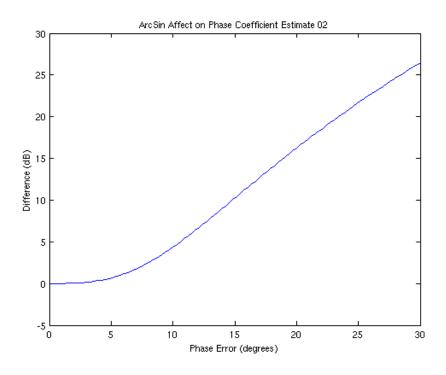

| Figure 4.12: Error introduced in phase coefficient from not using Arcsin            | 71    |

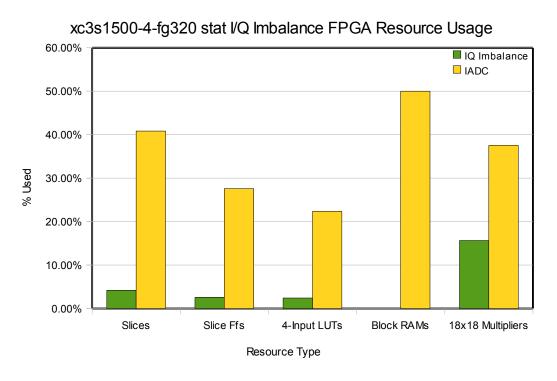

| Figure 4.13: Stat I and Q Imbalance VHDL Resource Requirements                      | 72    |

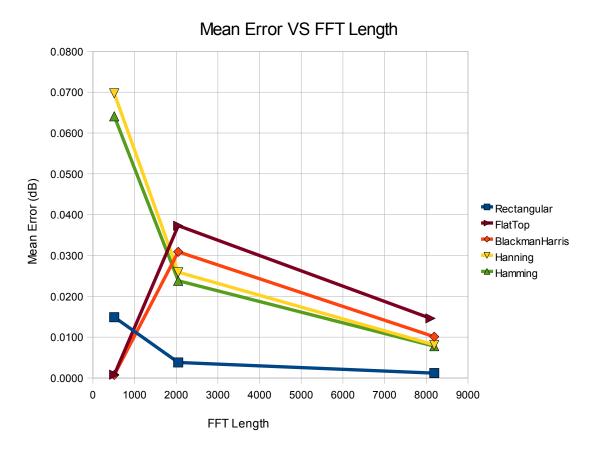

| Figure 4.14: Average FFT bin error VS length of FFT                                 | 75    |

| Figure 4.15: Carrier peak error VS length of FFT                                    | 76    |

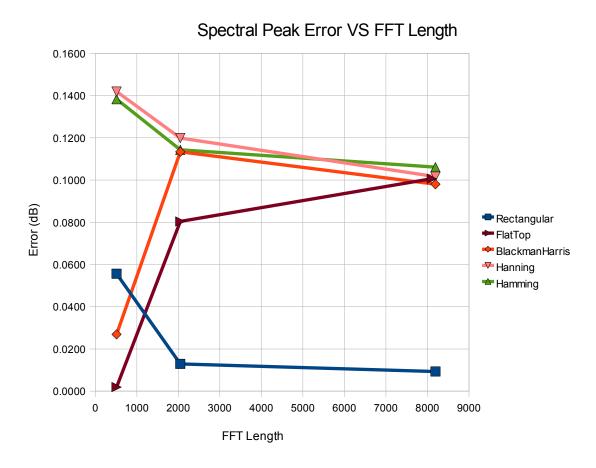

| Figure 4.16: Window and FFT calculated results: Matlab vs Xillinx                   | 77    |

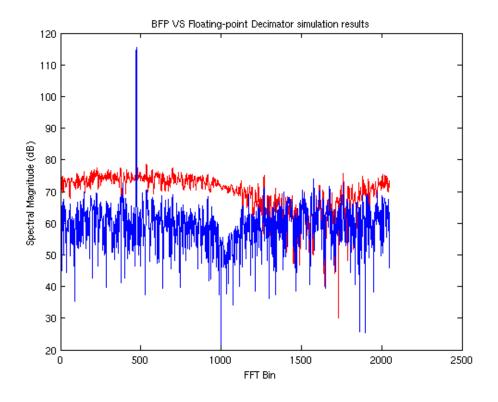

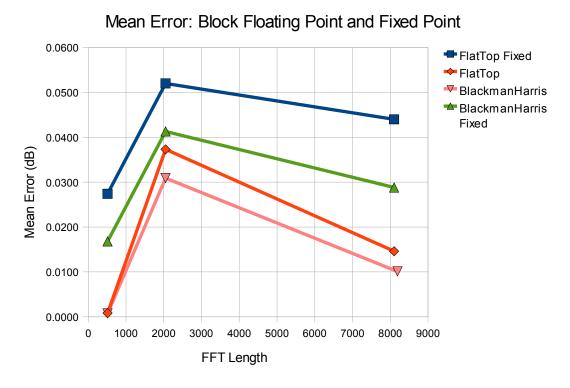

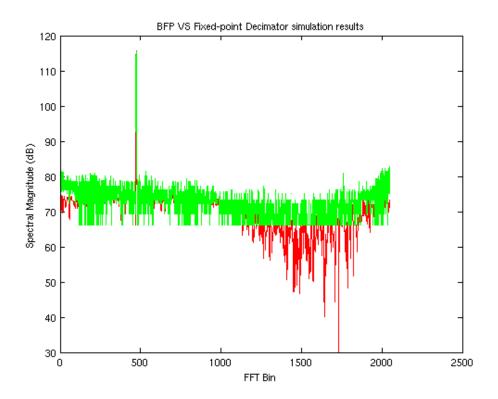

| Figure 4.17: Loss of precision caused by BFP and fixed point arithmetic in the FFT  | 79    |

| Figure 4.18: Block floating point VS fixed point FFT implementation. 2048-point Fla | ıtTop |

| window                                                                              | 80    |

| Figure 4.19: Windowing and FFT Resource Usage                                       | 82    |

# **CHAPTER 1: INTRODUCTION**

#### 1.1 General

Communication schemes have developed from simple dot and dash Morse code to complex high speed systems where numerous transmitters are simultaneously communicating with numerous receivers. The continual drive to explore new ideas and push known boundaries keeps technology marching steadily forward.

Global communications standards have emerged and are enforced federally in all modern countries. The regulations require wireless communication to adhere to stringent transmission and reception constraints. Power and bandwidth are the two most limited factors that ensure a wide variety of wireless communication systems are able to co-exist without interference. An example of one such highly regulated frequency band is the L-band, which is used for satellite communication, and ranges from about 1 to 2GHz. From the perspective of a designer, a spectrum analyzer may be used for research and development, troubleshooting, and the verification of its functionality as a legal transmitter/receiver device. From the perspective of a federal regulator, a spectrum analyzer may be used to monitor the frequency spectrum to ensure that legal limits are observed.

The complexity of communication systems increases with each advancement in technology, and new methods must be developed for verification and analysis. An example of one such method for analyzing a signal is the Fast Fourier Transform, (FFT), which allows a time based signal to be viewed in the frequency domain (i.e., spectrum). A spectrum analyzer is the hardware realization of the FFT, and it has become a common

tool used to monitor communication systems. One such device is the Decimator.

#### 1.2 The Decimator

The Decimator is a Peripheral Component Interconnect, (PCI), slot form factor L-Band spectrum analyzer developed by SED Systems Ltd.. The Decimator is functionally a spectrum analyzer and an oscilloscope with a Personal Computer, (PC), interface. The Decimator receives power from the PCI slot of the PC and communicates with the host computer via an Ethernet connection. As long as the Decimator is powered, any PC with network access can use the Decimator and display its output either in a browser window, or the provided software Application Programming Interface, (API).

The market value of the Decimator comes as a result of its low cost in comparison to equivalent bench spectrum analyzers and oscilloscopes, as well as its small form factor. A device of this nature works well in embedded systems because of its remote access and low power requirements. While the Decimator was initially developed as a low cost test device for a communication system that was being developed, its market value was recognized and has since become one of SED Systems' stand-alone products. The Decimator uses a direct conversion receiver architecture to convert a received Radio Frequency, (RF), signal directly to baseband. This architecture has allowed the Decimator to retain its small form factor and low power requirements. However, it has also led to the introduction of errors that limit its accuracy.

#### 1.3 Known Decimator Issues

#### 1.3.1 I/Q Imbalance

The main issue affecting the Decimator is the introduction of In-Phase (I) and

Quadrature-Phase (Q) imbalances in the received signals from the RF receiver. The gain and phase imbalances are a result of the Direct Conversion Receiver (DCR) architecture that the Decimator employs. In certain applications these imbalances cause a relatively significant error to be present at the output from the receiver. The output of the Decimator is processed and either the frequency or time domain information is displayed on a computer screen. In and of itself these errors may not be significant enough to warrant correction in some applications, but the usefulness of the Decimator is directly linked to the accuracy of its calculations. Since other communication schemes and transmitters can be tested, calibrated, and verified using the Decimator, residual errors may also be transferred, and possibly amplified, in other applications.

#### 1.4 Other Decimator modifications

The majority of known error present in Decimator output signals is due to the issues described above. However, not all changes to the Decimator are being done for the sole purpose of increased accuracy. Speed is also a factor that must be considered. Changes to a major bottleneck in the Decimator's signal processing system will also be studied in an effort to increase its speed. In the existing design, a Xilinx Spartan-3 FPGA and an Analog Devices ARM microcontroller shared the signal processing in the Decimator. The microcontroller currently handles two signal processing algorithms that limit the speed of the Decimator. These two algorithms are "windowing" and the "Fast Fourier Transform," (FFT). By coding these two algorithms in the FPGA and removing them from the microcontroller, an increase in speed should be achieved at the cost of some accuracy. This trade off comes as a result of the increased streamlining ability of the FPGA and performing the mathematical calculations in a fixed point precision environment. The

fixed point precision math of the FPGA will be compared and contrasted with the 32-bit floating point precision math of the microcontroller to help evaluate this migration.

#### 1.4.1 Windowing

A windowing function is a filter that converts a continuous signal into one where the only non-zero values are those within the bandwidth of the window function. The windowing function acts as a buffer and allows a finite length of samples to be analyzed by hardware-implemented signal processing algorithms. In the case of the Decimator, the windowing function buffers the data for the FFT. The windowing function is currently implemented in the microcontroller using floating point precision calculations, but this causes a bottleneck in the signal processing chain. The effect of the fixed point precision on a windowing algorithm will be explored from theoretical and practical viewpoints. The windowing algorithm will be implemented in the FPGA to verify its performance and help conclude whether this migration is economical.

#### 1.4.2 Fast Fourier Transform

The FFT is a practical DSP algorithm that allows the Discrete Fourier Transform, (DFT), of a signal to be calculated in real-world devices such as FPGAs and microcontroller. The FFT converts a signal from the time domain to the frequency domain by calculating the frequency components that are present in a given waveform. Since the FFT is behind much of the functionality of the Decimator, its performance is of utmost important to the overall performance of the Decimator.

Implementing a FFT in a FPGA is not a new endeavor. Xilinx, for example, has patented logic cores that can be dropped into a design and easily configured in a short

period of time. By implementing the Xilinx core in the FPGA of the Decimator, it will be possible to perform an economic evaluation of the migration and determine whether the change is feasible. Specifically, the results of the implemented algorithm will be analyzed to confirm whether or not the solution is faster than the current implementation. The degradation in accuracy will also be studied to ensure that it is not beyond acceptable levels.

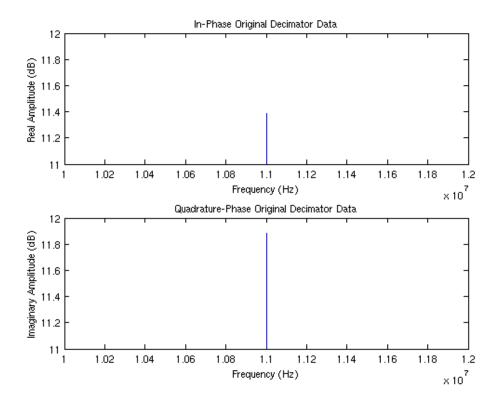

#### 1.5 Decimator Modification Overview

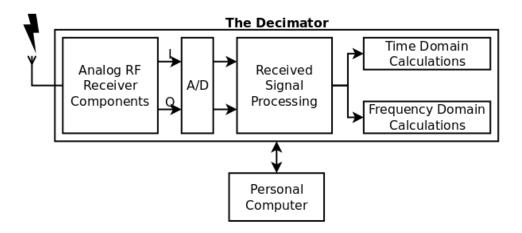

A basic overview of the Decimator can be seen in Figure 1.1. The incoming L-band signal is received by the analog RF front-end components. The received signal is converted from analog to digital form and is passed to a chain of signal processing algorithms. The signal processing algorithms demodulate the received signal so the samples passed to the time and frequency domain calculations are at baseband.

Figure 1.1: Decimator block diagram.

An I and Q imbalance correction scheme will be sought that can be implemented in the "Received Signal Processing" block from Figure 1.1. Implementing an I and Q imbalance correction algorithm in the "Received Signal Processing" block is desired because it would not require hardware changes to be made to the Decimator. The correction algorithm would only require modification to the firmware of the Decimator.

The Windowing and FFT algorithms are present in the "Frequency Domain Calculations" block seen in Figure 1.1. Migrating these two algorithms from the microcontroller to the FPGA in the Decimator will not change the block diagram, it will only change the way the Decimator calculates the functions.

# 1.6 Summary

This thesis will seek Digital Signal Processing (DSP) solutions that should improve the accuracy of the Decimator while not disrupting the current data throughput. The proposed solutions will result in a stand-alone signal processing algorithm that will work with a wide variety of incoming signals, as is expected of a spectrum analyzer. The DSP algorithms should require neither a training sequence nor a calibration signal, (which would require transmitter modification), to help with the correction of the gain and phase imbalances. The DSP algorithms will be implemented between a Spartan-3 FPGA and an ARM microcontroller so that the proposed solutions are compatible with the hardware requirements.

The windowing and FFT algorithms will be theoretically analyzed to show the effect of fixed-precision calculations. Both algorithms will then be migrated from the microcontroller of the Decimator to its FPGA to obtain bit accurate results. The bit accurate simulations, along with the theoretical analysis, will help determine whether the changes are economical and worth implementing in all new Decimators.

# 1.7 Thesis Outline

This thesis provides detailed descriptions related to the background, concepts, and implementation of the proposed Decimator modifications. Chapter 2 gives a theoretical basis for the proposed changes and reviews literature pertinent to the issues related to the Decimator. Chapter 3 provides details of the changes that are proposed and how each change ought to be simulated for verification. Chapter 4 reviews the simulation results obtained from the proposed methodology. Chapter 5 discusses the results and forms conclusions based on the findings. Future work is also suggested.

# **CHAPTER 2: LITERATURE REVIEW AND THEORY**

#### 2.1 Introduction

This thesis is not proposing a radically new system; rather, its purpose is to take known solutions to given problems and evaluate whether these solutions can be successfully used to solve the known issues within the Decimator. The issue of I and Q imbalance in DCRs is well documented. Various ways of dealing with I and Q imbalance will be discussed and evaluated to show whether previously proposed solutions can provide an acceptable solution to this problem. The algorithm migrations will be discussed from a theoretical standpoint and simulated to study the implications of the proposed changes.

#### 2.2 Direct Conversion Receivers

The driving motive behind technological advances in communication systems is the desire to make transceivers with higher levels of integration. Bulky off-chip components that are prominent in the popular heterodyne receivers are a limiting factor in system integration because of their high power requirements and larger form factors. This has led to transceiver designs such as the low-IF, (Intermediate Frequency), and zero-IF, or direct conversion, receivers. The low-IF and zero-IF receivers greatly reduce the off-chip hardware requirements, and thus improve efficiency and reduce size. The issues related to direct conversion receivers are therefore the major topic of study in this thesis since the Decimator utilizes the direct conversion receiver architecture.

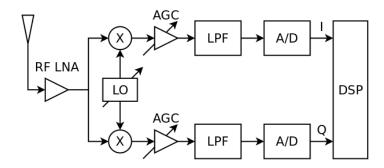

Direct conversion receivers use quadrature demodulation to split the received signal into real, (In-phase), and imaginary, (Quadrature-phase), components by multiplying incoming signals by orthogonal sine and cosine functions. Figure 2.1 depicts the basic architecture for a direct conversion receiver. Theoretically, quadrature mixing removes the need for anti-alias filtering by infinitely attenuating the image of the signal. Practically, however, there will always be a certain amount of gain and phase imbalances between the I and Q branches of the receiver because of the inability to perfectly match the receiver's analog components [5]. The errors that are introduced prevent the direct conversion receiver architecture from being used in many high-end applications.

*Figure 2.1: Direct conversion receiver architecture.*

The error-free Local Oscillator, (LO), can be modeled as,

$$X_{LO}(t) = \cos(w_{LO}t) - j\sin(w_{LO}t)$$

(2.1)

where  $\cos(w_{LO}t)$  demodulates the I branch, and  $-jsin(w_{LO}t)$  demodulates the Q branch. An arbitrary quadrature incoming signal,  $s_M = s_I \cos(wt) + s_Q \sin(wt)$ , is split into its real and imaginary branches when it is multiplied by the LO function. The received inphase signal is mathematically demodulated as shown below.

$$R_I(t) = \cos(w_{LO}t) S_M$$

$$R_{I}(t) = \cos(w_{LO}t)(S_{I}\cos(wt) + S_{Q}\sin(w_{LO}t))$$

$$R_{I}(t) = S_{I}\cos(wt)\cos(w_{LO}t) + S_{Q}\sin(w_{LO}t)\cos(wt)$$

(2.2)

The LO frequency is tuned to the transmitted signal frequency, so  $w=w_{LO}$ . Using standard trigonometric identities yields

$$R_I(t) = \frac{1}{2}S_I + \frac{1}{2}S_I\cos(2wt) + \frac{1}{2}S_Q\sin(2wt)$$

(2.3)

Following the down-conversion is the Automatic Gain Control, (AGC), which equalizes the received signal. The LPF, as seen in Figure 2.1, then removes the high frequency components containing 2w. Only the baseband components of the original signal remain. The quadrature-phase branch equation seen in Equation 2.4 can be derived similarly.

$$R_{Q}(t) = \frac{1}{2} S_{Q} + \frac{1}{2} S_{Q} \cos(2wt) + \frac{1}{2} S_{I} \sin(2wt)$$

(2.4)

#### 2.3 I/Q Imbalance

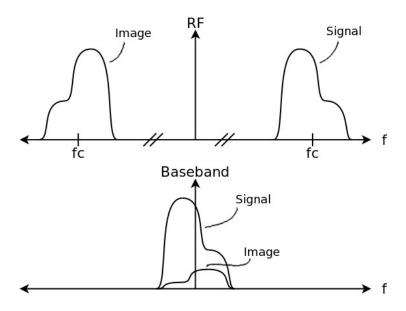

The dual path architecture makes the quadrature demodulator prone to gain and phase mismatches between the I and Q branches, and these are called I and Q imbalances. Analog component imperfections alter the received signals differently despite an identical signal processing chain in both branches. The result is a difference in the gain and phase between the I and Q branches of the received signal. This causes the image of the signal to act as interference on top of the desired signal. In theory, a direct conversion receiver can provide infinite attenuation to the received image signal, however, in practice this image cannot be fully removed. Figure 2.2 depicts a RF to baseband conversion and shows the

effect that the image has on the received signal at baseband.

Figure 2.2: Example RF and baseband spectra depicting an I/Q imbalance.

The imperfections in the receiver can be modeled by the complex Local Oscillator (LO) function in the time domain as,

$$X_{LO}(t) = (1 - \varepsilon)\cos(w_{LO}t - \phi/2) - j(1 + \varepsilon)\sin(w_{LO}t + \phi/2)$$

(2.5)

where  $\epsilon$  is the gain imbalance factor and  $\varphi$  is the phase imbalance in radians. The gain imbalance in dB is found by,

$$\beta = 20\log\left((1+\varepsilon)/(1-\varepsilon)\right) \tag{2.6}$$

Equation (2.5) shows an equal amount of the imbalances being applied to the I and Q channels. This is an appropriate representation because the difference in gain and phase between the two channels is what is important, and not the absolute values. Therefore,  $\varepsilon$  and  $\varphi$  are determined by finding the differences between the gain and phase of the two channels. It is possible to model  $\varepsilon$  and  $\varphi$  by applying half the total errors to each channel. This concept is important, and will be discussed later when the correction architectures are

discussed.

Using Euler's formula and some basic mathematical considerations, the unbalanced Local Oscillator (LO) signal can be expressed as,

$$x_{LO}(t) = K_1 e^{-jw_{LO}t} + K_2 e^{jw_{LO}t}$$

(2.7)

where  $K_1$  is the desired signal, and  $K_2$  is its image. Mathematically,  $K_1$  and  $K_2$  are,

$$K_{1} = \frac{(1-\varepsilon)e^{j\frac{\phi}{2}} + (1+\varepsilon)e^{-j\frac{\phi}{2}}}{2}$$

(2.8)

$$K_{2} = \frac{(1-\varepsilon)e^{-j\frac{\phi}{2}} - (1+\varepsilon)e^{j\frac{\phi}{2}}}{2}$$

(2.9)

To obtain infinite attenuation of the image,  $\varepsilon = 1$  and  $\varphi = 0$ . This would lead to  $K_I = 1$  and  $K_2 = 0$ , and thus an ideal down-conversion of the RF signal to baseband. It is not currently possible to implement a direct conversion receiver without I and Q imbalances. Therefore the effect of the I and Q imbalances on the received data must be studied to determine the severity of the problem and to understand the nature of the solution.

Equation (2.10) shows how the imbalanced LO signal propagates error on the received signal. Using the imbalanced LO signal from Equation (2.5) to demodulate the received signal rather than the perfectly balanced theoretical LO in Eq (2.1) yields,

$$R_I(t) = (1 - \varepsilon)\cos(w_{LO}t - \frac{\phi}{2})(S_I\cos(wt) + S_Q\sin(wt))$$

(2.10)

$$R_I(t) = (1 - \varepsilon)(S_I \cos(\frac{\phi}{2}) - S_Q \sin(\frac{\phi}{2}))$$

(2.11)

Following the same procedure, the received quadrature phase branch can be shown as

$$R_{\mathcal{Q}}(t) = (1+\varepsilon)\left(S_{\mathcal{Q}}\cos\left(\frac{\phi}{2}\right) - S_{I}\sin\left(\frac{\phi}{2}\right)\right) \tag{2.12}$$

The ratio between  $K_1$  and  $K_2$  gives a measure of the power of the signal versus the power of the image. To represent the attenuation achieved by the analog components in the receiver, or the Image Rejection Ratio, (IRR), the following relationship can be used,

$$IRR_{dB} = 20 \log \left( \frac{|K_1|}{|K_2|} \right) \tag{2.13}$$

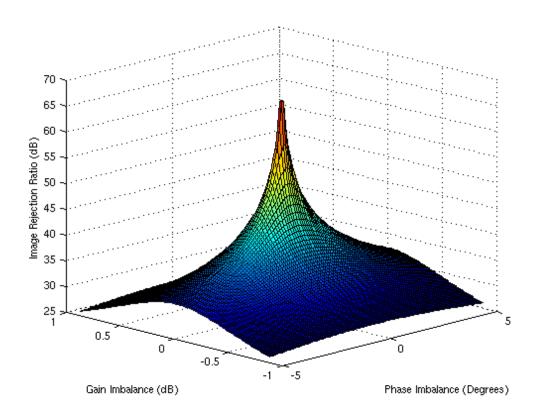

Figure 2.3: Image Rejection Ratio (IRR) with respect to gain and phase imbalances.

Figure 2.3 displays the effect that gain and phase mismatches have on the Image Rejection Ratio, (IRR). The relationship is highly non-linear, so even small errors in gain and phase lead to a significant degradation of the received signal. To achieve at least 50 dB in image attenuation, the gain and phase errors must be held to less than 0.05 dB and 0.2° respectively [6].

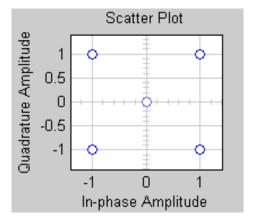

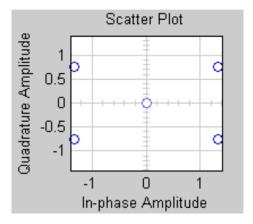

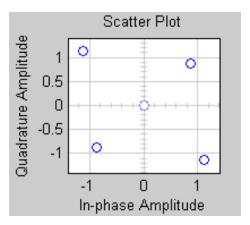

The modulation schemes received by the Decimator will almost all be symmetric with a mean of zero. These schemes include, but are not limited to: QAM, PSK, and OFDM. To visualize the effects of gain and phase imbalances in the receiver, Figures 2.4 to 2.6 represent QAM demodulation functions with imbalance errors. Rather than demodulating a signal with a perfectly orthogonal set of functions, an imbalanced set of functions demodulates the signal. Figure 2.4 shows how a perfectly balanced receiver will demodulate a received 4-QAM signal. Both the I and Q branches of the signal will be accurately demodulated, as the constellation depicts. Figure 2.5 illustrates the effect of a gain imbalance in the receiver. The received signal will be demodulated with an imbalance that causes the I branch data to have a higher amplitude than the Q branch data. Figure 2.6 shows the skew associated with a phase imbalanced receiver.

Figure 2.4: 4-QAM original modulation scheme.

Figure 2.5: 4-QAM gain imbalanced modulation, (2dB).

Figure 2.6: 4-QAM phase imbalanced modulation, (10°).

The Decimator receives these signals and displays them graphically to the user. The issue of concern is not one of Bit Error Rates, (BER), and data corruption, but of visual ambiguity. The Decimator is not a part of a larger system that tries to decipher instructions from the received data that is being transmitted; rather, it is simply creating a visual display of the received data for the user. An example of how this is detrimental to the usage of the Decimator becomes obvious when the practical applications of a Spectrum Analyzer are outlined. Spectrum Analyzers are commonly used for testing, debugging, verification, and calibration. From the visual inaccuracies displayed by the Decimator, it is possible to inaccurately calibrate another unit or system. The errors in the Decimator then have the possibility of propagating themselves to other systems, which is why correcting the I and Q imbalance errors is so important.

Figure 2.7: Received data corrupted by gain and phase imbalances.

An RF signal with identical I and Q data was generated using a signal generator with arbitrary waveform generation capability. The generated signal was then fed into the Decimator. A zoomed-in result of the Decimator's spectrum analysis can be seen in Figure 2.7. It is clear that the imbalances in the receiver have excessively increased the amplitude of the Q branch. Based on the received data, there is an estimated gain imbalance of 0.4922 dB and a phase imbalance of 2.9303° in the particular Decimator this data capture was obtained from. These errors lead to a 0.4944 dB difference between the peak FFT bins of the two signals. Now the problem of I and Q imbalances has been properly defined, and its effect on received signals has been quantified. The next step is to determine how these errors can be corrected.

#### 2.4 I/Q Imbalance Correction Schemes

The errors introduced by gain and phase imbalances in the receiver should now be apparent. With direct conversion receivers being a viable option for small scale applications, and with imbalances being prevalent in their architecture, a large number of research papers have been published on the subject [5, 7, 8, 14, 16]. Each paper may bring some subtle nuance to a well-known solution but for the most part, these solutions can be categorized into several different types of correction schemes.

# 2.4.1 Non-Data-Aided (NDA) Correction Schemes

Non-data-aided (NDA), or blind, correction schemes are a popular form of I/Q imbalance solution that do not require knowledge of the modulation scheme and do not utilize training sequences or test tones. NDA correction methods utilize samples of the received data to determine the amount of error that is present, and then a correction is applied to remove the estimated error. The procedures whereby NDA algorithms estimate the error and then apply corrections differ from method to method. However, all methods share the fact that statistical characteristics are utilized to apply a correction to the received signal.

#### 2.4.1.1 Blind Source Separation (BSS)

Blind Source Separation, (BSS), is the process of taking a mixture of N statistically independent signals and recovering all N signals in their original form using no outside knowledge of the source or mixing matrices. In other words, only the signal mixture is used [10]. An imbalanced direct-conversion receiver causes the I and Q channels to mix. Consequently, the signals become correlated and are no longer independent of one another.

BSS makes the implicit assumption that the mixed signals are independent. Therefore, the I and Q imbalance problem is solvable via the BSS method with N=2 independent sources.

One method of BSS is Independent Component Analysis, (ICA), which provides a mathematical approach to solving the BSS problem. While there are other methods to solve the BSS problem, ICA requires that the sources be independent to achieve an applicable solution. ICA reconstructs both the source signals and the mixing matrix by minimizing the statistical dependencies, (i.e., cross-correlation), between the signals. Bell and Sejnowski showed that in signals that have a positive kurtosis, maximizing the amount of information, or entropy, was equivalent to de-correlating the signals [9]. Rather than minimizing the statistical dependencies between the signals, the proposed method attempts to correct the problem by maximizing the signal information.

Figure 2.8 displays the basic structure of the ICA problem where S(t) is the original signals, R(t) is the received signals after being mixed, and C(t) is the corrected output after unmixing has occurred. Both S(t) and A are unknown, but using only R(t) and the ICA technique, W can be adapted to remove the error introduced by A. From this model it is possible to write,

$$R(t) = AS(t)$$

$$C(t) = WR(t)$$

$$(2.14)$$

$$S(t)$$

$$A$$

$$R(t)$$

$$W$$

$$C(t)$$

$$W$$

$$Mixing Matrix Unmixing Matrix$$

Figure 2.8: Independent Component Analysis problem definition.

The problem becomes one of developing a set of adaptive filters that will undo the effects of the mixing matrix.

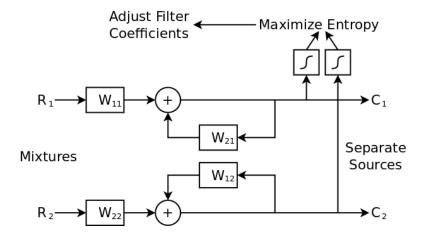

A number of applicable learning algorithms have been proposed to update the coefficients in the unmixing matrix. In [11], four of the most prominent learning rules are outlined, and a hybrid learning rule is developed. While all four learning rules have been utilized successfully in other applications, arguably the most important learning rule was developed by Bell and Sejnowski [9]. Their proof of the information maximization rule, (i.e., Infomax), was developed into an effective hardware model using adaptive filters proposed by Torkkola [10]. Torkkola proposed a hardware feedback network that has been at the heart of most adaptive filter techniques for decorrelating independent signals because it provides a structure that can be realized in the receiver hardware. Figure 2.9 shows the Torkkola feedback architecture as it applies to the general case of convolved mixtures.

Figure 2.9: Torkkola's feedback network for separating convolved mixtures.

### 2.4.1.2 Interference Cancellation (IC)

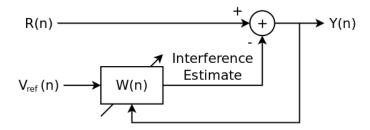

The Interference Cancellation, (IC), based technique attempts to create an

interference signal that, when subtracted from the received signal, will remove the erroneous component from the desired signal. This method also requires no knowledge of the received signal, but makes the fundamental assumption that the desired signal and its interfering component are uncorrelated. Since in the case of I and Q imbalance the erroneous component of the signal is from the other branch of the receiver, this relationship holds and the IC method can be utilized to solve the I and Q imbalance problem.

The basic architecture behind the IC method is depicted in Figure 2.10. The adaptive filter modifies the reference signal such that it correlates with the erroneous component of the signal but not the desired portion. The modified reference signal is then subtracted from the incoming signal in an attempt to remove the noise, or in the case of I and Q imbalance, the cross-talk. Similar to the BSS solution, IC based methods rely heavily on the learning rules employed to modify the adaptive filter.

Figure 2.10: Adaptive interference canceler (IC) architecture.

#### 2.4.1.3 Adaptive Methodologies Summary

Valkama et. al. analyzed several BSS and IC based methods and determined that both provide feasible solutions to the problem of I and Q imbalances in low-IF receivers [5]. While the Decimator uses a zero-IF receiver architecture, the methodologies are still applicable and have been applied to direct conversion receivers in other cases [6, 11].

Valkama concluded that the BSS based solutions are more robust and can correct a wider range of receiver imbalances at a variety of received signal levels. BSS also avoids the signal leakage problems that inhibit the IC based methods. On the other hand, IC based methods are more capable of handling the effects of additive noise and symbol timing errors. The IC based method can also be less sensitive to the type of modulation scheme.

Both methods track changes in I and Q imbalances with time, as is expected of the adaptive techniques. The speed and accuracy of convergence of these methods vary depending on the learning rule used to update the filter coefficients. Both methods are comparable in this respect with the proper update rule selection.

Valkama shows that both methods would be successful in various situations; however, these solutions are not the most promising when considering the nature of the Decimator [5]. The most obvious shortcoming is the fact that the number of filter coefficients needed to obtain acceptable results may easily be in the range of 60 to 100. To keep the Decimator operating at 65 MHz on the Spartan 3 FPGA, this would require a large number of dedicated multipliers. These added multipliers would also cause a considerable amount of added latency in the DSP. The adaptive filtering techniques, while promising in other applications with different hardware, would most likely not provide the best results for the Decimator.

#### 2.4.1.4 Statistical Correction Method ("Stat")

Figures 2.4 to 2.6 show the changes that occur to a modulation scheme in the presence of I and Q imbalances. These changes alter the shape of the incoming signals such that the statistical characteristics of the received signals are also modified. There are a number of I and Q correction schemes that take advantage of these known signal

alterations to estimate the error that was introduced into the signal. Error estimates can be made and then used to reverse the effect of the errors on the signals. Several statistical methods will be evaluated to determine their viability as a solution to the I and Q imbalance problem in the Decimator.

Statistical methods for solving the receiver I and Q imbalance problem are relatively new. One of the earliest methods that is applicable to the Decimator architecture is presented in [12]. The problems encountered with direct conversion receivers were discussed at length, and several variations of statistical methods for correcting gain and phase imbalances were proposed. Unfortunately, the paper does not provide any verification of the proposed methodologies. Consequently, the proposed techniques requires further study.

Around the same time as [12] was published, a methodology was proposed (and presumably independently developed) by Kocic et al. [13]. The proposed methodologies offered simple hardware implementation and promising error correction results. Shortly after the Kocic et al. [13] paper, an essentially identical methodology was proposed by Rykaczewski et al. [14]. Their proposed methodology offered good Bit Error Rate (BER) improvements while using only received data to formulate the correction scheme. The performances of both [13] and [14] have been verified, and their methodologies are similar in many respects to [12]. Therefore, it appears that the methodologies proposed in [13] and [14] should be pursued as a solution rather than [12].

The statistical-based correction scheme proposed in [13] and [14], known henceforth as "Stat", makes several basic assumptions about the form of the signal being received. The first assumption is that the real and imaginary portions of the received signal be

statistically independent. This assumption differs from that of the BSS based solutions which make the assumption that the two original signals are uncorrelated. For the two signals to be independent, the following relationship must hold [4]

$$E[R_I R_O] = E[R_I] E[R_O]$$

(2.15)

The second assumption was that the real and imaginary portions of the received signal are of equal power. That is, the following relationship must hold.

$$E[R_I^2] = E[R_Q^2] (2.16)$$

While the second assumption is not required by the BSS solutions, it is not an assumption that limits the practicality of the *Stat* solution. These assumptions will still cover approximately 98% of all incoming transmitted signals. One notable modulation scheme that does not meet the requirement in (2.16) is BPSK. BPSK transmits data that is modulated on the I branch only which means the real branch power will be much larger than the imaginary branch power.

The signal model in Equations 2.11 and 2.12 show how the desired signal is interfered with by the gain and phase imbalance components present in the receiver. The *Stat* method proposes an estimation of the variables  $\varepsilon$  and  $\varphi$ , and then use those estimates to reverse the effects of the imbalance error. From Equation (2.6) it is evident that the scaling factor between the two channels is  $(\varepsilon+1)/(\varepsilon-1)$ . Using mean-squared calculations on both channels, [14] proposes the gain imbalance estimate to be,

$$\varepsilon = \frac{\sqrt{E[R_Q^2]} - \sqrt{E[R_I^2]}}{\sqrt{E[R_Q^2]} + \sqrt{E[R_I^2]}}$$

(2.17)

The gain imbalance can easily be removed by multiplying each branch by the estimated imbalance.

Once the gain imbalance has been corrected, the phase imbalance can be addressed. Squaring the I and Q branches yields

$$S_{I}^{2} = R_{I}^{2} \cos^{2}(\frac{\phi}{2}) + R_{Q}^{2} \sin^{2}(\frac{\phi}{2}) - R_{I} R_{Q} \sin(\phi)$$

(2.18)

$$S_{Q}^{2} = R_{I}^{2} \sin^{2}(\frac{\phi}{2}) + R_{Q}^{2} \cos^{2}(\frac{\phi}{2}) - R_{I} R_{Q} \sin(\phi)$$

(2.19)

After the assumption in Equation (2.16) is acknowledged, it can be seen that,

$$E[S_I^2] + E[S_O^2] = E[R_I^2] + E[R_O^2]$$

(2.20)

And since  $R_I R_Q = S_I S_Q - 1/2 \sin(\phi) (S_I^2 + S_Q^2)$ , it follows that,

$$\phi = -\arcsin\left(\frac{2E[R_I E_Q]}{E[R_I^2] + E[R_Q^2]}\right)$$

(2.21)

The calculations required to find the phase estimate are quite simple to compute in an FPGA, with the exception of the Arcsin function. According to [13] the following simplification can be made,

$$\phi = -\left(\frac{2E[R_I E_Q]}{E[R_I^2] + E[R_Q^2]}\right)$$

(2.22)

Kocic et al. justify the removal of the *Arcsin* function by noting that in real world applications phase errors are typically less than 20° [13]. With small phase values, the Arcsin function does not significantly change the estimated value. Therefore, it can be removed to make the algorithm easier to implement in hardware without a substantial loss of precision to the phase estimate.

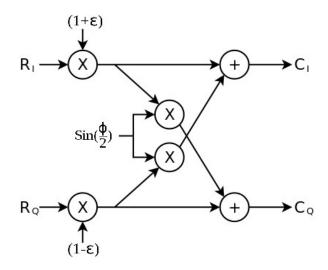

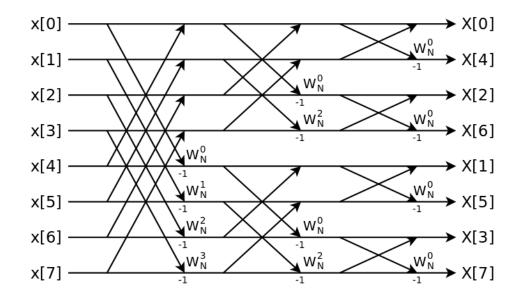

Once estimates of the error parameters have been calculated, a method is needed for applying these estimates in a way that removes the I and Q imbalance error. In [12], several time domain models for applying the correction coefficients are presented that look

quite similar to the feedback network solution proposed by Torkkola [10]. Figure 2.11 depicts the proposed gain and phase error correction block diagram. The gain is corrected first, and then the phase, as was outlined in [12]. Mathematically, it is clear that mixing the coefficients as shown in Figure 2.11 cancels the extra components in the received signal, as shown in Eqs. 2.11 and 2.12.

Figure 2.11: I and Q Imbalance Correction Block Diagram.

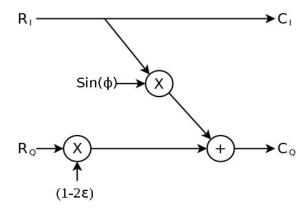

The block diagram in Figure 2.11 is a valid method of applying the correction coefficients; however, the method requires the use of four multipliers and two adders. The impaired signal was shown to have half the errors applied to the I channel, and the other half of the errors applied to the Q channel. Applying the I and Q errors to only one branch of the signal is well documented [5, 16, 19]. Rather than spreading the gain and phase corrections between the I and Q channels, the corrections can be applied to just one of the channels. This causes the Q branch of the receiver to be equalized to the I branch, and since the desire to make the spectral powers of the I and Q channels equal, this is a valid modification. The proposed modification is depicted in Figure 2.12. The simplification to

the hardware correction scheme reduces the dedicated FPGA hardware required to two multipliers and one adder.

Figure 2.12: Simplified I and Q Imbalance Correction Block Diagram.

#### 2.4.1.5 Other Statistical Correction Schemes

Stat is not the only statistical correction scheme that has been proposed and as a result, several other promising methods will also be presented and discussed. Moseley and Slump presented a novel method that uses only data from the received signal to correct subsequent incoming samples [18]. Figure 2.13 shows the proposed correction architecture. Three estimators are adapted in real time to determine the I and Q imbalance compensation coefficients. Windows of data anywhere from 32 to 256 samples are captured and basic averaging is performed. A Low Pass Filter (LPF) is used with each estimator to smooth the data that is generated by each window of samples. The output of the estimators is then used to generate the correction coefficients. Once the coefficients are computed, their application requires only two multipliers and one addition. This hardware requirement is the same for *Stat*.

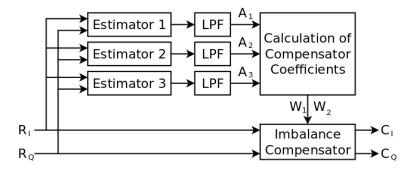

Figure 2.13: Moseley and Slump's I and Q Imbalance Compensation Block Diagram.

The Moseley and Slump method [18] provides an alternative to *Stat*. The performance of both methods cannot be compared based solely on the respective performances because one method contains IRR simulations, and the other method provides BER simulations. Without implementing both methods in Matlab to obtain numerical results, the decision can be made based on the ease of implementation in the Decimator.

The hardware requirements of [18] are only mildly greater than *Stat*. The only major difference is that three additional multipliers are needed for the LPFs. The main drawback comes from the flow of the correction algorithm. *Stat* calculates several running sums in the background and then uses the sums to calculate the error coefficients. Rather than calculating the coefficients in the FPGA, the sums can be passed to the microcontroller for processing. The results can then be passed back to the FPGA for use. Conversely, [18] would require full implementation in the FPGA because of its real time nature. The Mosely and Slump [18] method cannot wait for values to be passed back and forth from the microcontroller. For this reason, *Stat* still appears to be the more promising algorithm for implementation in the Decimator.

Another novel method for removing I and Q imbalances in both the transmitter and

receiver was proposed in [29]. Reference was made to *Stat* in the paper but no reasons were given as to why it should not be used were provided. The main benefit to the proposed scheme is that it provides a correction in the transmitter as well as in the receiver. The Bit Error Rate (BER) graphs provided in [29] indicates that the proposed method does not perform as well as *Stat* while correcting 16-QAM and 64-QAM signals under similar conditions. Since the Decimator is a receiver, and no modifications are being made to any transmitters, choosing *Stat* over the method proposed in [29] seems quite justified.

Another novel statistical correction technique was proposed by Anttila et al. [16, 17] which used second order statistics of a signal to obtain correction parameters. The basic assumptions of the methodology are that the received signals are zero-mean, circularly symmetric, mutually uncorrelated, and of equal power. This may seem like quite a number of assumptions to make, but these assumptions apply for the vast majority of modern communication systems. The drawback in the case of the Decimator is that the calculated estimates must be implemented with adaptive filters. Adaptive filters are not feasible in the case of the Decimator. While the Anttila et al. technique may prove invaluable in other receivers, it would probably not be of much value to the Decimator [16, 17].

#### 2.4.2 Data-Aided (DA) Correction Schemes

Data-aided correction schemes are less popular than their counterpart schemes because training sequences must be injected into the signal at the transmitter. Introducing a training sequence requires an increase of complexity in both the transmitter and the receiver due to the increased channel equalization and frequency synchronization. While the performance of DA correction schemes has been shown to be quite good, the usefulness of such correction schemes is still questionable. For these reasons, many

practical applications opt for a NDA type solution, rather than for a DA type solution [5]. DA solutions are not feasible in the case of the Decimator because the modulation scheme is unknown to the receiver and altering the transmitter is not an option.

#### 2.4.3 I and Q Imbalance Conclusions

The simplicity of *Stat* and its error improvements in other application make it a prime candidate for integration into the Decimator. It does not require calculations that are beyond the scope of an FPGA and it does not require any knowledge of the incoming signal. The signal is assumed to be symmetric about the origin and to have equal channel powers. For these reasons, *Stat* will be further evaluated as a solution to the I and Q imbalance problems present in the Decimator.

## 2.5 Windowing

Windowing is a term used to refer to a filter that passes a selected group of samples and sets all others to zero. In contrast with the other types of filters that pass data based on frequency content, a window filter passes data based on its time domain position. The result is a finite sequence of non-zero samples that may be processed further by subsequent DSP algorithms. In the case of the Decimator, the processing that follows the windowing is the FFT.

Windowing has become a common practice in applications that perform the FFT. The reasons for its necessity stem from issues that arise out of the calculation of the FFT. The FFT assumes it is calculating a periodic sequence of data, however, only a small sampling of the incoming data is used to make the calculation. The starting point and ending point of the window frame have to exactly line up to provide a seamless periodic representation

of the captured signal. In practice, a set number of samples are used to represent the incoming signal but its starting and ending points do not line up. This results in the energy of the signal being spread across a number of frequency bins, rather than being isolated from each other. This phenomenon is known as spectral leakage.

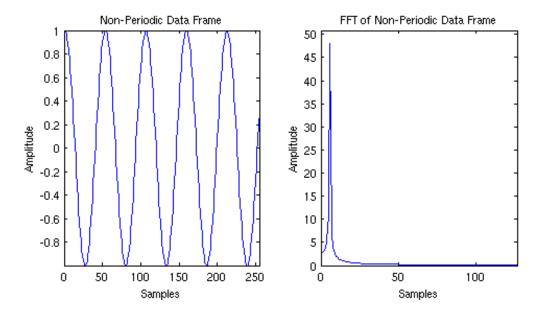

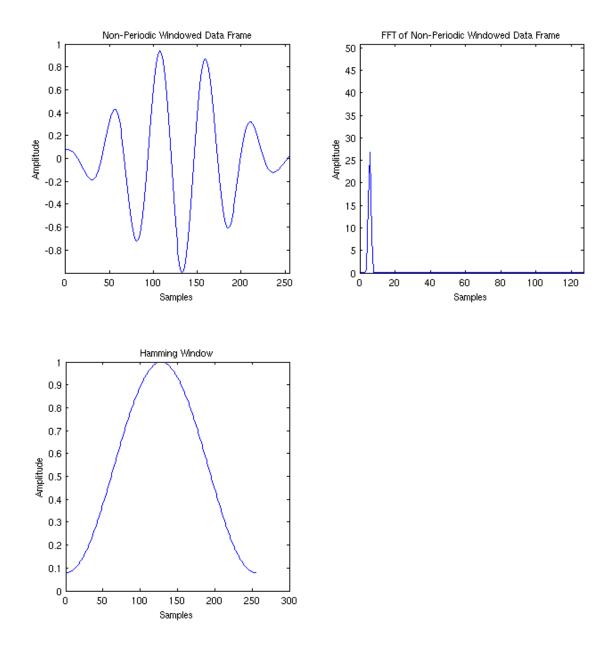

Figure 2.14: Non-periodic frame of data from a periodic sinusoid.

Figure 2.15 shows the 256 point FFT of a simple sinusoidal wave whose starting and ending samples line up to make the data frame periodic. The results in Figure 2.15 can be compared with the result seen in Figure 2.14, where the same sinusoid was processed and the frame of data did not line up. The differences between these two representations are evident. Firstly, the peak FFT bin value is lower because of the spectral leakage. Secondly, spectral leakage causes the base of the FFT spectrum to grow when it should be narrow, as shown in Figure 2.15. Obviously this introduction of error into the FFT calculation should be mitigated. This is why windowing has become an important process in the DSP chain of the Decimator.

Figure 2.15: Periodic frame of data from a periodic sinusoid.

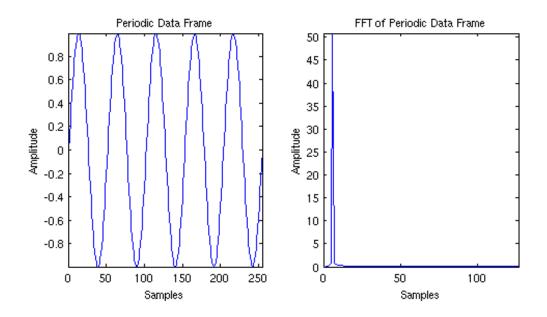

It should be noted that although windowing was not explicitly performed on the sinusoids from Figure 2.15 and Figure 2.14, the act of limiting the input to the 256 point FFT to 256 samples is itself an implicit application of a rectangular window. The rectangular window is what caused the sharp cut offs at each end of the data frame. There are a wide variety of window designs that round the corners of the data frame to reduce spectral leakage. Figure 2.16 shows a few of the most common windows in the time domain.

Figure 2.16: Several common window functions.

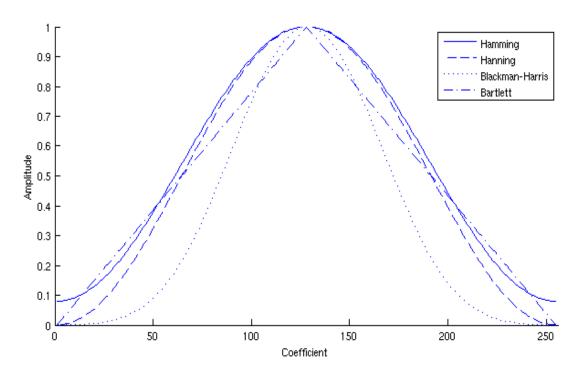

Taking the example from Figure 2.14 and applying a Hamming window prior to transformation yields improved results. Figure 2.17 shows these improved results, along with the Hamming window coefficients that were applied. Although the new frequency spectrum does not have the spectral leakage that was previously present, the amplitude of the spectrum is significantly lower. The lowered spectral gain is due to the windowing function which removed much of the signal power when it tapered the edges of the data frame. The amount by which the amplitude decreases is known for each type of window and can be corrected by applying a gain factor to the spectrum after the transformation.

Another significant difference can be seen by the overall width of the frequency component. While the frequency component no longer contains the leakage around the base, it is now wider than it was in Figure 2.15. The frequency component is now wider and it has lost some of its spectral resolution. Where two spectral components that are

very close to each other may have been distinguishable before the windowing operation, they may overlap each other and cause their spectral components to interfere with each other. Herein lies the trade-off that takes place with the application of a window function: spectral leakage versus frequency resolution.

Figure 2.17: Effect of the Hamming window on a periodic signal capture.

## 2.5.1 Finite Register Length

Finite register lengths degrade the precision of an algorithm in two ways. First, by limiting the precision of calculated values (coefficients), and second, by truncating the results of multiplication operations that overflow. Windowing coefficients are calculated by the Decimator in the microcontroller and may then be passed to the FPGA for storage and use. This process will require rounding operations to take place such that the 32-bit coefficients can be represented by fewer bits in the FPGA. This will be the first loss of precision in the window migration process. The second source of error will not be an issue as it was in the FFT algorithm. Each incoming sample is multiplied by its corresponding window coefficient, but each coefficient is less than 1. There will be no errors introduced by overflows in the windowing function. Only one of the two main sources of error are applicable to the windowing operation. Migration of the windowing to the FPGA should not induce as much error in this system as migration of the FFT algorithm.

# 2.6 Fast Fourier Transform (FFT)

Advances in mathematics have brought about new ways of viewing data. Various transforms such as the Hilbert, Cosine, and Fourier Transforms have become commonplace in a variety of signal processing applications. The Fourier Transform changes a signal so that rather than viewing a signal as an amplitude versus time function, the signal may be viewed as an amplitude versus frequency function. While the Fourier Transform is a theoretical transformation, the Fast Fourier Transform (FFT) is its practical realization [1, 2, 3]. The FFT has become one of the most important transforms in signal processing applications and much work has been done to implement the FFT on a variety of hardware platforms.

The FFT is currently performed in the ARM microcontroller on board the Decimator. However, there are several reasons why migrating the FFT to the FPGA is desired. The primary reason relates to speed; the microcontroller is much slower at processing data than the FPGA. The advantage of the microcontroller is that it has a 32-bit floating point mathematical operator, whereas the FPGA is inherently fixed point. Keeping as much of the signal processing chain on the FPGA makes for a much more maintainable product. As a side benefit, a logic core that performs the FFT adequately on the Decimator may be an asset to other related projects.

## 2.6.1 FFT Background

The Discrete Fourier Transform (DFT) provides a way for digital systems to realize the Fourier Transform of a function. However, it is a time consuming transform that is not practical in most systems. Exploiting some of the key properties of the DFT, such as periodicity and symmetry, a variety of more efficient algorithms have been developed to make the implementation of the DFT in hardware a practical reality. These more efficient algorithms fall under the blanketed term "Fast Fourier Transform" because of increased speed with which the transform is calculated [1, 2].

The general DFT equation can be written as,

$$X[k] = \sum_{n=0}^{N-1} x[n] W_N^{kn}$$

(2.23)

where X[k] represents the frequency bins found in the sequence x[n]. N represents the number of samples in the given frame of data, or window, and  $W_N^{kn}$  represents the complex exponential  $e^{-j(2\pi/N)kn}$ . By multiplying discrete samples by the complex vector  $e^{-j(2\pi/N)kn}$ , the frequency content of the signal at various angles can be summed and

transformed into a set of frequency bins [1, 2]. However, the way in which the DFT algorithm is implemented in hardware is a topic of much study, and a number of methods have been proposed to reduce its computational complexity.

## 2.6.1.1 Decimation-in-Time (DIT) Algorithms

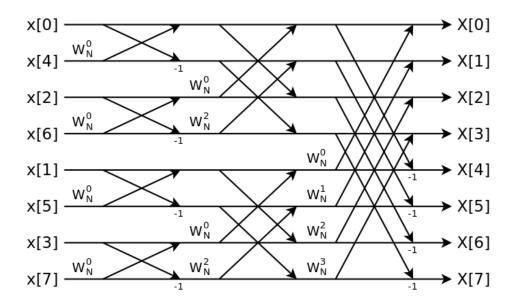

There are two main types of FFT algorithms; decimation-in-time (DIT) and decimation-in-frequency (DIF) algorithms. The DIT algorithms break an incoming frame of samples into successively smaller sub-sequences before performing the transform to only a small number of samples. The rest of the transform coefficients can then be deduced using the periodicity and symmetry principles of the Fourier Transform [1]. Figure 2.18 depicts the flow of a DIT algorithm. While this example flow chart shows an 8-point DIT FFT, the method can be expanded or contracted to apply to all FFT point sizes that are factors of  $2^N$ . The decomposition scheme leads to a reduction in the number of multiplication operations needed by more than a factor of 100 [1, 2].

The values of  $W_N^{kn}$ , referred to as "twiddle factors," need to be calculated for each FFT point size. They are reusable, however, so they only need to be calculated once per point size. As is seen in Figure 2.18, some of the twiddle factors may be simplified to either a "1" or "-1". This is a valid simplification since the angular frequencies at even multiples of  $\pi$  are  $W_N^{N/2} = e^{-j(2\pi/N)N/2} = e^{-j\pi} = -1$  and  $W_N^0 = e^{-j\theta} = 1$ .

Figure 2.18: Flow graph of an 8-point DIT decomposition.

## 2.6.1.2 Decimation-in-Frequency (DIF) Algorithms

The most notable difference with the DIF algorithms is that it takes the input data in its natural order and performs the FFTs starting with the  $2^N$  (for radix-2) FFT first. This is in contrast to the DIT algorithm which rearranges the input data window in order to perform the smallest FFT calculation first before moving up to the higher values. Both algorithms have strengths and weaknesses when compared to one another, so the right algorithm needs to be chosen to fit the system it is being implemented in. Figure 2.19 depicts the flow graph of a basic DIF implementation.

Comparing Figure 2.18 and Figure 2.19, one design consideration is immediately apparent. A choice between ordered inputs, or ordered outputs must be made. The DIT FFT must buffer the input data in order to rearrange it and apply the butterfly calculations. On the other hand, the DIF takes data in order and generates Fourier coefficients that are out of order. Because of this, the data at the output must either be buffered and rearranged, or the system using the generated Fourier coefficients must know that they are not in their

natural order (i.e. the coefficients are not ordered 0, 1,2,etc.).

Figure 2.19: Flow Graph of an 8-point DIF decomposition.

## 2.6.1.3 FFT Radix Size

In the previous examples of DIT and DIF FFTs, a radix size of N=2 has been assumed. That is, the FFT length is broken down by a factor of 2 at each step of the decomposition. Radix-2, where N=2, is one of the most common FFT settings because it greatly reduces the number of multiplications needed. The down side to decomposing the FFT this much is that it takes longer to calculate. When implemented in hardware, this equates to an increase in algorithm latency. Rather than decomposing the calculations down to a minimum of 2, as in the radix-2 calculation, setting N=4 simply causes the minimum FFT calculation to include 4 samples. This is known as radix-4, and it offers an alternative to radix-2 in that it performs the same FFT calculation in less time but with more multiplications. Unfortunately, it is less robust than radix-2 because it can only calculate FFT lengths that are a power of 4.

#### 2.6.2 Finite Register Lengths

The most important issue when discussing the migration from floating point hardware to a fixed point platform is the loss of data that can be attributed to truncation and rounding. One way these errors creep into the FFT calculation is through twiddle factor multiplications. Twiddle factors must be stored in memory with a fixed number of bits. The number of bits used determines how precisely the actual twiddle factor value is represented. Bit growth due to the multiplications that take place in each butterfly of the FFT is the other dominant source of error due to finite register lengths. Analyzing these two issues varies based on the FFT architecture and input signal model.

FFT algorithms contain a large number of multiplications, and twiddle factor quantization errors propagate with each multiplication. The way quantization noise is manifested in twiddle factors depends on the implementation of the complex multiplier (i.e. the architecture that is instantiated). The Chang and Nguyen model is based on the Radix-2 FFT, which limits their results to be applicable only to Radix-2 FFTs [27]. Comprehensively evaluating the effects of finite register lengths with respect to the Xilinx FFT core is a fairly in-depth task. Oppenheim and Weinstein believe the twiddle factor quantization errors are not a major source of error [22]. Rather, it was concluded that the quantization error varies directly with N, the number of bits used, which means doubling the number of bits used to represent the twiddle factors would produce only a small improvement in the noise-to-signal ratio of the FFT. It is important to note that more experimental verification is required since their hypothesis is based on an equation meant to give a rough estimate of quantization error.

Each butterfly in a Radix-2 FFT has the potential to increase the number of bits

required to represent the result by a factor of two [1]. In a Radix-4 FFT, an increase up to a factor of four is possible. Floating point arithmetic is able to handle these bit growths because of its superior dynamic range performance [22], however, fixed point arithmetic requires some form of intervention to keep the result manageable. The Xillinx FFT core comes with several configurable options to address this problem.

#### 2.6.2.1 Full Precision Unscaled

The Full Precision Unscaled settings introduces the least noise into the system. The number of bits at the output is determined by the worst case scenario formula, as seen in Equation (2.24).

$$input \ width + \log_2(FFT \ length) + 1$$

(2.24)

Therefore, 12-bit input samples will yield 22-bit FFT coefficients. While this setting does not introduce any truncation or rounding noise to the data, the data will not be usable by the rest of the system. As a result, the output will most likely require scaling to bring it back to a usable size. This is an elementary way of dealing with the bit growth problem, and it will introduce a substantial amount of error into the system.

## 2.6.2.2 Scaled Fixed Point

The next built-in function to deal with bit growth after each butterfly calculation is called Scaled Fixed Point. Rather than scaling the result at the output of the FFT, the scaled fixed point setting scales by a user-defined value at each butterfly calculation. This technique is quite common, and has been shown to be superior to having one large scaling factor at the input of the FFT [1, 22]. The down side to this procedure is that scaling is not necessarily required with each butterfly, but it is still applied anyway. Data that has a

higher average value and comes close to saturation quite frequently will not notice much of an issue with this solution. Data that is close to saturation requires scaling at most butterfly operations anyway. Conversely, data that has a lower amplitude will become much noisier with this setting since scaling is applied unnecessarily at most FFT stages.

## 2.6.2.3 Block Floating Point (BFP)

The final built-in FFT core setting implements Block Floating Point (BFP) arithmetic. BFP may be considered a special case of the floating point format where non-overlapping groups of data are joined together by a common scaling factor. The scaling factor acts as the mantissa in a floating point number, except the scaling factor is chosen to represent the largest samples within the group [23]. When the BFP arithmetic option is selected, the output of each butterfly is checked to determine whether an overflow has occurred. If an overflow has occurred, a scaling factor of two (for Radix-2) or four (for Radix-4) is used to bring the data back to the desired number of bits. The number of overflows and the stage at which they occur affect the SNR. The setting of this variable can greatly vary the SNR of the input data [1].

## 2.6.3 Dynamic Range

Dynamic range refers to the smallest and largest values that can be represented of a given variable. As it pertains to spectral analysis, dynamic range determines the ability of the FFT to distinguish between small and large spectral peaks. Measuring the dynamic range of an FFT system is not a trivial task. This is primarily because dynamic range has no specific definition as it pertains to FFT systems [24]. There are several common methods of measuring the dynamic range of an FFT system that are widely accepted. The

first method is to find the ratio between a full scale sinusoid and the noise floor. This is called a "two-toned" measurement and it provides an accurate theoretical measurement of dynamic range. The "two-toned" measurement does not take into consideration the fact that real-world signals contain numerous sinusoids, so it fails to provide an accurate practical measurement of dynamic range [25].

The second method for determining the dynamic range of an FFT system is called the "noise slot test" [21, 24] White Gaussian noise is created and passed through either a notch filter or a bandpass filter. The remaining data is then scaled and quantified to use the full range available given the number of bits in the system. This signal is then passed to the input of the FFT system. The difference between the average signal power and the average noise power is the dynamic range of the FFT system. There is a third method of determining dynamic range called the "mean-squared error technique" but it can be shown to be equivalent to the "noise slot test" [24].

Xilinx simulated a number of "noise slot tests" in Matlab and documented the results [21]. Figure 2.20 shows an overview of the results that were obtained. The slope of the graph is 6.06 dB/bit, which means that each additional bit used to represent the input and output increases the dynamic range of the FFT by 6.06 dB. The change of about 6 dB of dynamic range per bit is not an accurate representation of actual dynamic range, but of theoretical range [24, 25]. In reality, there are other factors that cause noise and prevent the 6 dB per bit rule to be followed explicitly.

#### Dynamic Range VS Number of Bits Oynamic Range (dB)

Figure 2.20: Xilinx dynamic range results.

Number of Bits

Xilinx documented several other "noise slot test" result that are of interest to this thesis. Xilinx calculated the dynamic ranges of the full precision unscaled arithmetic, the scaled (1/N) arithmetic, and the BFP arithmetic using a bit accurate Matlab model of the Xilinx FFT Core [21]. All simulations were run using 1024 point, Radix-4 Burst I/O transforms with 16-bit input data, 16-bit phase factors, and convergent rounding. The full precision unscaled simulation yielded a benchmark result of 91 dB. The BFP simulation calculated a dynamic range of 73 dB. The smallest dynamic range was the scaled arithmetic simulation, which found the dynamic range to be 64 dB. Therefore, moving from full precision unscaled to BFP lead to a loss of 18 dB. A further loss of 9 dB was sustained by going from the BFP to the scaled arithmetic.

A more practical look at the effective dynamic range of an FFT system was performed in [26]. Other factors that affect the dynamic range of an FFT system are the FFT algorithm that is used (i.e. DIT or DIF), the FFT length, and the window filter that is

used. Several simulations were run using a variety of settings, but one simulation in particular had similar settings to those used in [21]. Simulation 3 in [26] was run using the 1024 point DIT FFT, a rectangular window, 15-bit input data, 15-bit phase factors, and 15-bit output samples. The only notable difference from one of the Xilinx simulations is the use of 15-bits as opposed to 16-bits. The Dynamic range was found to be 70 dB in [26], which is very close to the 73 dB value found by Xilinx. The 3 dB difference may be attributed to the slight differences between the simulations.

## CHAPTER 3: RESEARCH PROGRAM / METHODOLOGY

## 3.1 Introduction

The research program is designed to study the effectiveness of the proposed changes to the Decimator. A methodology for simulating and verifying the chosen I and Q imbalance correction scheme will be outlined. Similarly, a plan for the algorithm migrations will be outlined that can be implemented in VHDL and simulated using the Xilinx ISE Simulator. The steps taken to study each of the issues in this thesis will be clearly defined. The results of the described simulations will be presented and discussed in Chapter 4.

## 3.2 I and Q Imbalance

Chapter 2 presented a variety of solutions to the I and Q imbalance problem. There are only a few that can be practically implemented in the Decimator. Statistical methods of correction showed promising results while using minimal resources and for these reasons, a statistical method was studied. The statistical method studied is called *Stat*, as discussed in Chapter 2. *Stat* will be implemented in VHDL and simulated using Xilinx ISE to obtain bit accurate data and hardware usage estimates. *Stat* will also be implemented in Matlab to give the bit accurate VHDL simulations 32-bit floating point reference results. The method of applying the correction coefficients will be implemented as outlined in Figure 2.12.

## 3.2.1 Stat Design Overview

The overall design of *Stat* was outlined in Chapter 2, but a more detailed discussion

regarding its implementation in VHDL is presented herein. The discussion describes the source of the simulation results. Figure 3.1 shows the VHDL system level design of *Stat*.