## A DIGITAL FREQUENCY-CUM-RATE OF CHANGE OF FREQUENCY RELAY

### A Thesis

## Submitted to the Faculty of Graduate Studies and Research in Partial Fulfilment of the Requirements for the Degree of

Master of Science

in the Department of Electrical Engineering University of Saskatchewan

by

### Mahmut.Mustafa Giray Saskatoon, Saskatchewan November 1978

The author claims copyright. Use shall not be made of the material contained herein without proper acknowledgement, as indicated on the following page.

The author has agreed that the Library, University of Saskatchewan, may make this thesis freely available for inspection. Moreover, the author has agreed that permission for extensive copying of this thesis for scholarly purposes may be granted by the ' professor or professors who supervised the thesis work recorded herein or, in their absence, by the Head of the Department or the Dean of the College in which the thesis work was done. It is understood that due recognition will be given to the author of this thesis and to the University of Saskatchewan in any use of the material in this thesis. Copying or publication or any other use of the thesis for financial gain without approval by the University of Saskatchewan and the author's written permission is prohibited.

Requests for permission to copy or to make any other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical Engineering

University of Saskatchewan

SASKATOON, Canada.

## ACKNOWLEDGEMENTS

The author expresses his gratitude and appreciation to Dr. M. S. Sachdev for his guidance and assistance in the preparation of this thesis.

The author is also grateful to Professor A. E. Krause for his help in the work conducted on PDP-8/E minicomputer.

Special thanks are extended to his wife for her encouragement during the study.

Financial assistance provided by University of Saskatchewan is thankfully acknowledged.

#### UNIVERSITY OF SASKATCHEWAN

#### Electrical Engineering Abstract 78A193

#### A DIGITAL FREQUENCY-CUM-RATE OF CHANGE OF FREQUENCY RELAY

Student: Mahmut Mustafa Giray Supervisor: Dr. M. S. Sachdev

M.Sc. Thesis Presented to the

College of Graduate Studies and Research

November 1978

#### ABSTRACT

Under-frequency relays are often used to detect deficiency of generation in a power system and to shed load to restore generationload balance. These relays operate somewhat after the frequency falls to a prespecified level. The difference between the set frequency and the frequency at which load shedding is initiated depends on the rate at which the frequency continues to change. To eliminate this delay frequency-cum-rate of change of frequency relays have been proposed, developed and used. These relays are designed using analog electronic circuits.

The availability of digital processing devices has considerably increased during the last few years while the cost of these devices has been rapidly decreasing. The use of digital processors in system control and protection is at the verge of becoming economically competitive.

This thesis examines the presently used methods of measuring frequency and rate of change of frequency at a power system bus. A few new and novel approaches are then proposed. Also examined are the relative advantages and suitability of these approaches for use in relays based on digital processors. A relay design using the selected techniques of measuring frequency and rate of change of frequency is then outlined. Implementation of this design and relay tests performed in the laboratory are also described.

# TABLE OF CONTENTS

|     |       |                                                                             | Page |

|-----|-------|-----------------------------------------------------------------------------|------|

| COP | YRIGH | T                                                                           | ii   |

| ACK | NOWLE | DGEMENTS                                                                    | iii  |

| ABS | TRACT |                                                                             | iv   |

| TAB | LE OF | CONTENTS                                                                    | v    |

| LIS | T OF  | FIGURES                                                                     | ix   |

| LIS | T OF  | TABLES                                                                      | xi   |

| 1.  | INTR  | ODUCTION                                                                    | 1    |

|     | 1.1   | Background                                                                  | 1    |

|     | 1.2   | Underfrequency Protection and<br>Frequency Relays                           | 2    |

|     | 1.3   | Objectives of the Project                                                   | 4    |

| 2.  | PROT  | ECTION PHILOSOPHY AND FREQUENCY RELAYING                                    | 6    |

|     | 2.1   | General Protection Philosophies                                             | 6    |

|     |       | 2.1.1 Classification of relays                                              | 7    |

|     |       | 2.1.2 Applying protective relays                                            | 7    |

|     | 2.2   | Frequency Relaying                                                          | 8    |

|     | 2.3   | Load Shedding                                                               | 9    |

|     | 2.4   | Frequency Relays                                                            | 10   |

|     | 2.5   | Rate of Change of Frequency                                                 | 11   |

|     | 2.6   | A Load Shedding Scheme                                                      | 12   |

|     | 2.7   | Other Frequency Relay Applications                                          | 17   |

| 3.  | TECH  | INIQUES OF MEASURING FREQUENCY                                              | 18   |

|     | 3.1   | Classification of Measurement Techniques                                    | 18   |

|     | 3.2   | Direct Method                                                               | 18   |

|     | 3.3   | Measuring Time for Specified Number of Periods<br>and Calculating Frequency | 22   |

|    |      |        |                                                                                                                 | Page |

|----|------|--------|-----------------------------------------------------------------------------------------------------------------|------|

|    |      | 3.3.1  | Gating Error                                                                                                    | 25   |

|    |      | 3.3.2  | High frequency clock errors                                                                                     | 25   |

|    |      | 3.3.3  | Noise                                                                                                           | 26   |

|    | 3.4  |        | ing Time for a Specified Number of Periods<br>Estimating Frequency                                              | 27   |

|    |      | 3.4.1  | First order approach                                                                                            | 27   |

|    |      | 3.4.2  | Second order approach                                                                                           | 28   |

|    | 3.5  |        | ne Testing of the Methods of Determining<br>uency                                                               | 30   |

|    |      | 3.5.1  | Measuring time for a specified number<br>of periods and calculating the<br>frequency                            | 30   |

|    |      | 3.5.2  | Measuring time for a specified number<br>of periods and estimating the frequency<br>by first order approach     | 32   |

|    |      | 3.5.3  | Measuring time for a specified number of periods and estimating the frequency by second order approach          | 34   |

| 4. | METH | ODS OF | DETERMINING RATE OF CHANGE OF FREQUENCY                                                                         | 38   |

|    | 4.1  | Classi | fication of Methods                                                                                             | 38   |

|    | 4.2  |        | ing the Periods of Successive Cycles and<br>ulating the Rate of Change of Frequency                             | 38   |

|    | 4.3  | of t   | ing the Period of Successive Cycles<br>he Signal and Estimating the Rate of<br>ge of Frequency                  | 39   |

|    |      |        | First order approximation                                                                                       | 40   |

|    |      |        | Second order approximation                                                                                      | 42   |

|    |      |        | Curve fitting approach                                                                                          | 45   |

|    | 4.4  |        | ne Testing                                                                                                      | 47   |

|    |      |        | Measuring time periods of successive<br>cycles of the signal and calculating<br>the rate of change of frequency | 47   |

|    |      |        |                                                                                                                 |      |

|    |      |         | í.                                                                                                     | Page |

|----|------|---------|--------------------------------------------------------------------------------------------------------|------|

|    |      | 4.4.2   | First order approximation                                                                              | 49   |

|    |      | 4.4.3   | Second order approximation                                                                             | 50   |

|    |      | 4.4.4   | Curve fitting approach                                                                                 | 52   |

| 5. | DESC | RIPTION | AND ON-LINE TESTING OF THE DIGITAL RELAY                                                               | 54   |

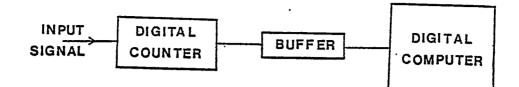

|    | 5.1  | Hardwa  | re Description of the Relay                                                                            | 54   |

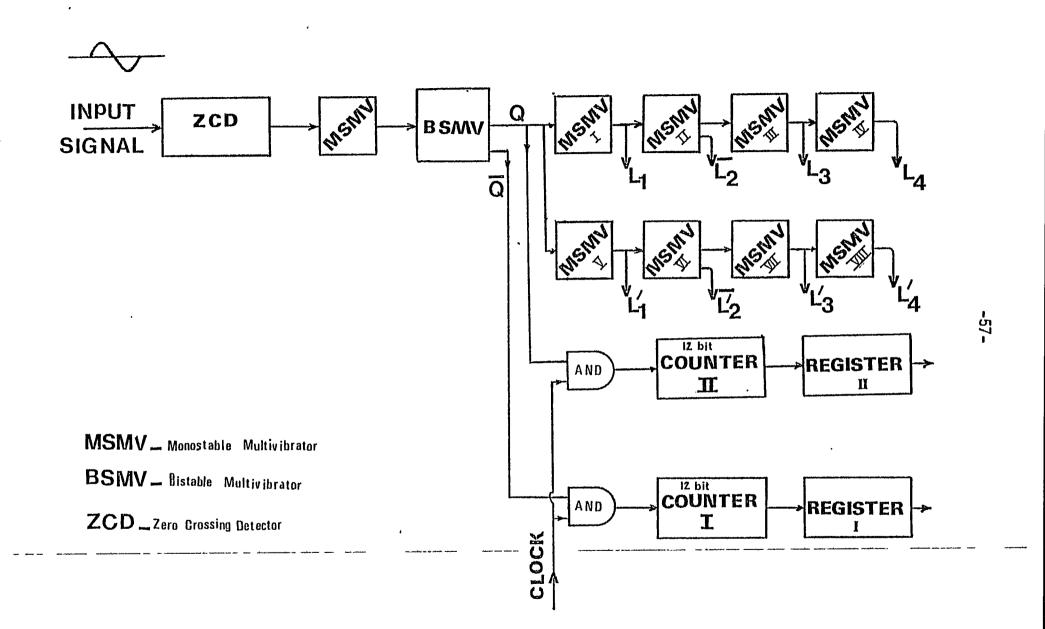

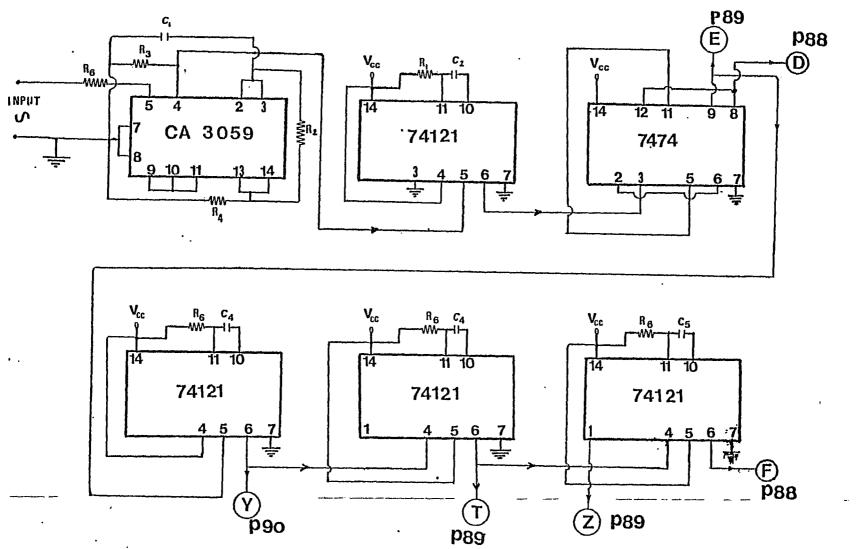

|    |      | 5.1.1   | Counter circuit                                                                                        | 55   |

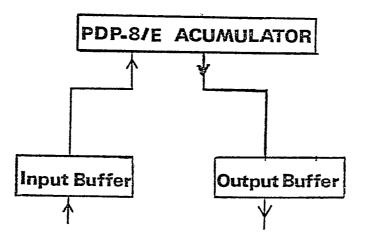

|    |      | 5.1.2   | Interprocessor buffer                                                                                  | 56   |

|    |      | 5.1.3   | Digital computer                                                                                       | 59   |

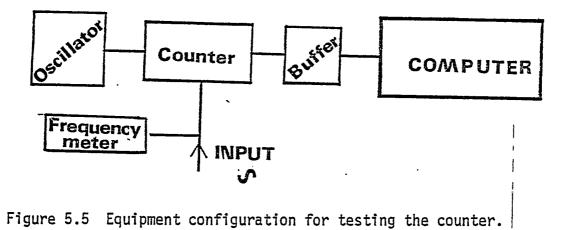

|    | 5.2  | Testin  | g the Counter Circuit                                                                                  | 60   |

|    | 5.3  | •       | e Measurements of the Rate of Change<br>equency                                                        | 61   |

|    |      | 5.3.1   | Simulation of the rate of change of frequency                                                          | 62   |

|    |      | 5.3.2   | On-line determination of the rate of<br>change of frequency by second order<br>approximation technique | 63   |

|    |      | 5.3.3   | On-line determination of the rate of change of frequency by curve fitting approach                     | 63   |

|    | 5.4  | Softwa  | re Program                                                                                             | 66   |

|    | 5.5  |         | g the Frequency-cum-Rate of Change of<br>uency Relay                                                   | 70   |

| 6. | CONC | LUSIONS |                                                                                                        | 73   |

| 7. | REFE | RENCES  |                                                                                                        | 76   |

| 8. | APPE | NDICES  |                                                                                                        | 78   |

|    |      | Append  | <pre>ix I - Effect of the Presence of a D.C.     offset on Frequency Measurements</pre>                | 78   |

|    |      | Append  | ix II - Counter Circuit                                                                                | 85   |

|    |      |         |                                                                                                        |      |

|                                                                    | Page |

|--------------------------------------------------------------------|------|

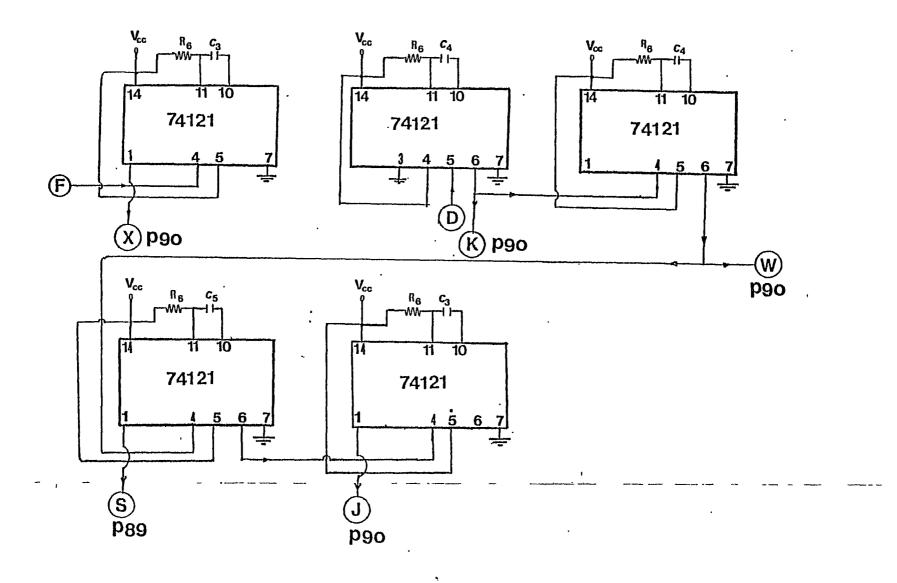

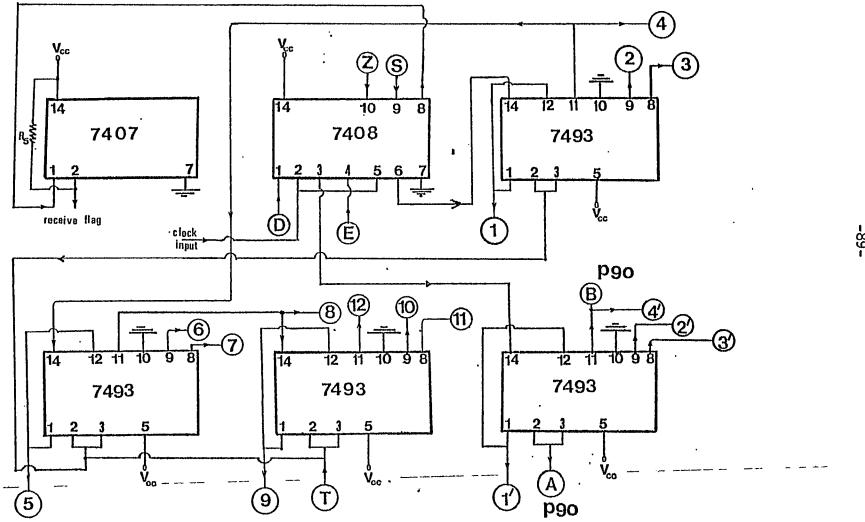

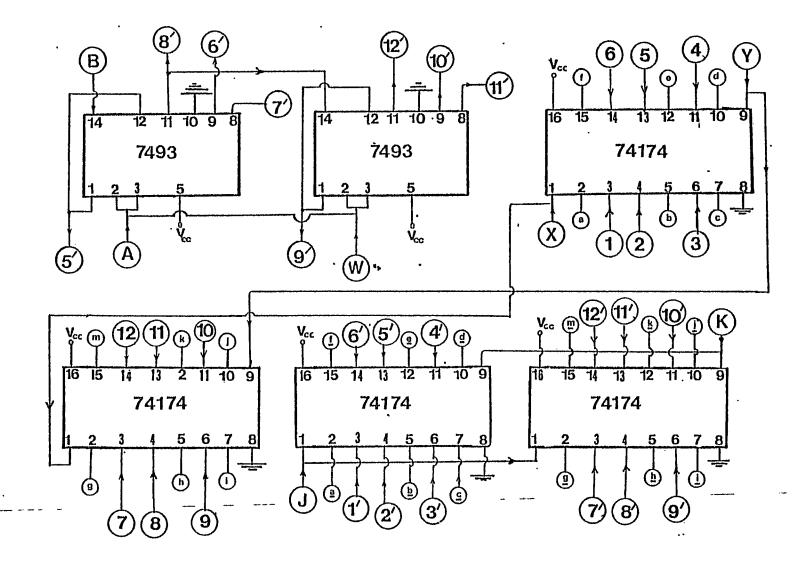

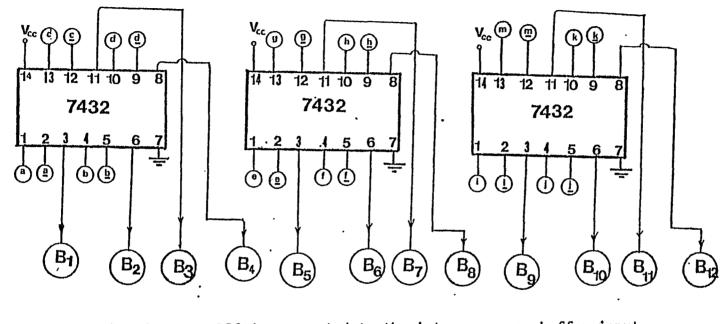

| Appendix II.1 - Description of the Circuit<br>Elements             | 85   |

| Appendix II.2 - Schemantic Diagram of the<br>Counter Circuit       | 87   |

| Appendix II.3 - Part List                                          | 92   |

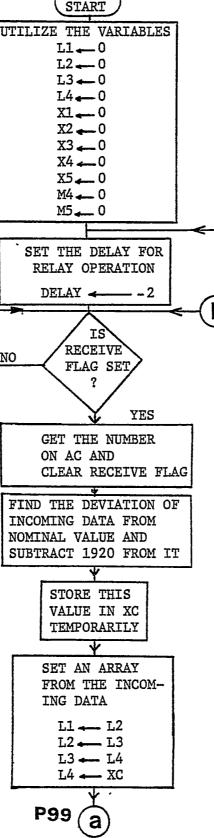

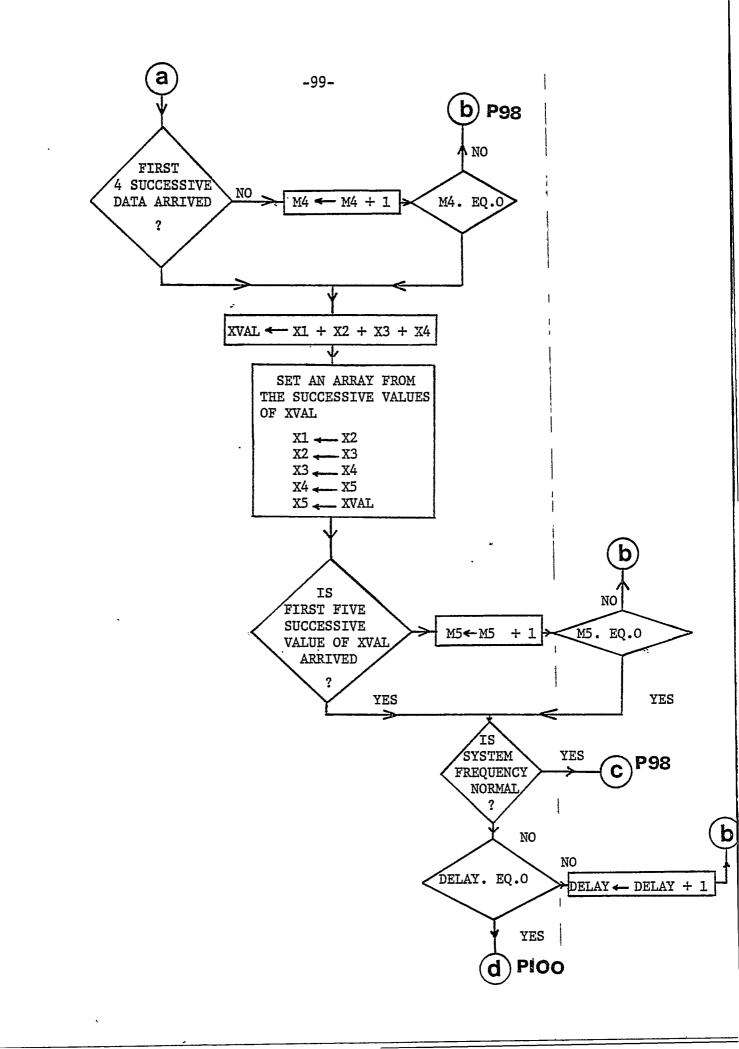

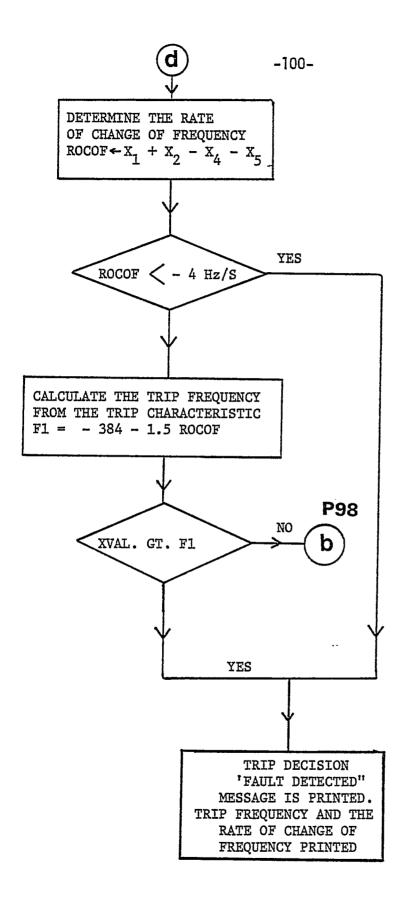

| Appendix III - Description of the Software<br>of the Digital Relay | 93   |

| Appendix III.l - Software Program                                  | 93   |

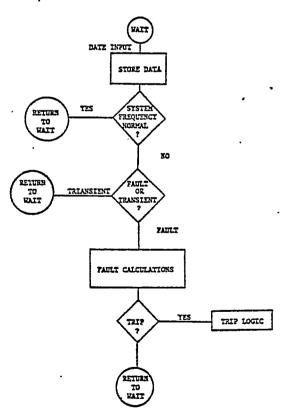

| Appendix III.2 - Flowchart of the Software<br>Program              | 98   |

| Appendix III.3 - Listing of the Software<br>Program                | 101  |

# LIST OF FIGURES

|             | ļ                                                                                                                                                                            | Page |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

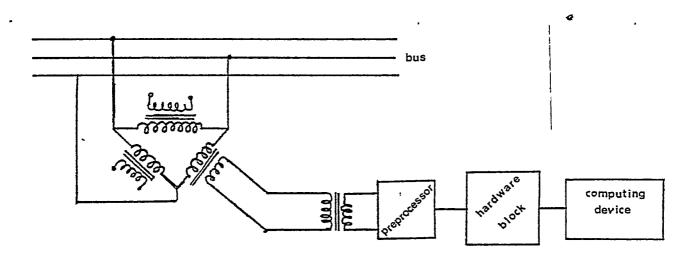

| Figure 1.1  | A conceptual arrangement of a software based frequency relay                                                                                                                 | 5    |

| Figure 2.1  | Characteristic of an induction cylinder frequency relay                                                                                                                      | 11   |

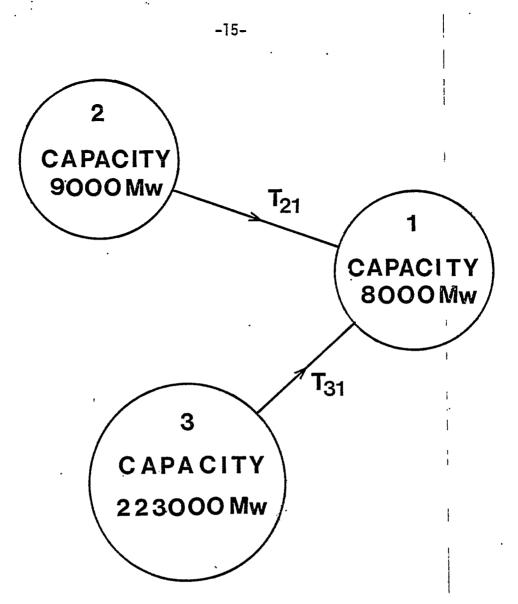

| Figure 2.2  | An interconnection of power systems                                                                                                                                          | 15   |

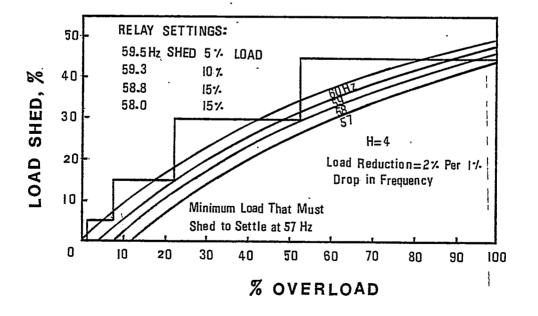

| Figure 2.3  | Four step load shedding program to protect up to 100% overload                                                                                                               | 16   |

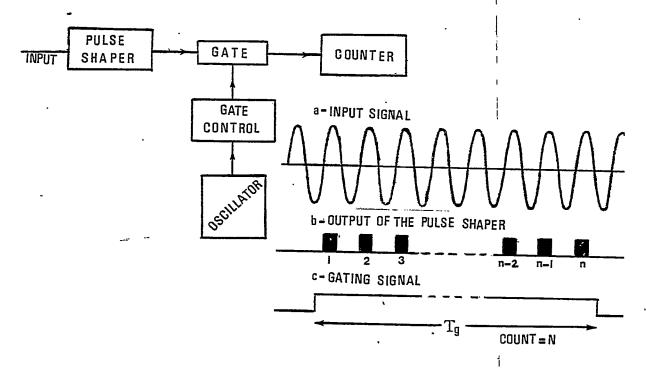

| Figure 3.1  | Simplified block diagram of a frequency counter                                                                                                                              | 19   |

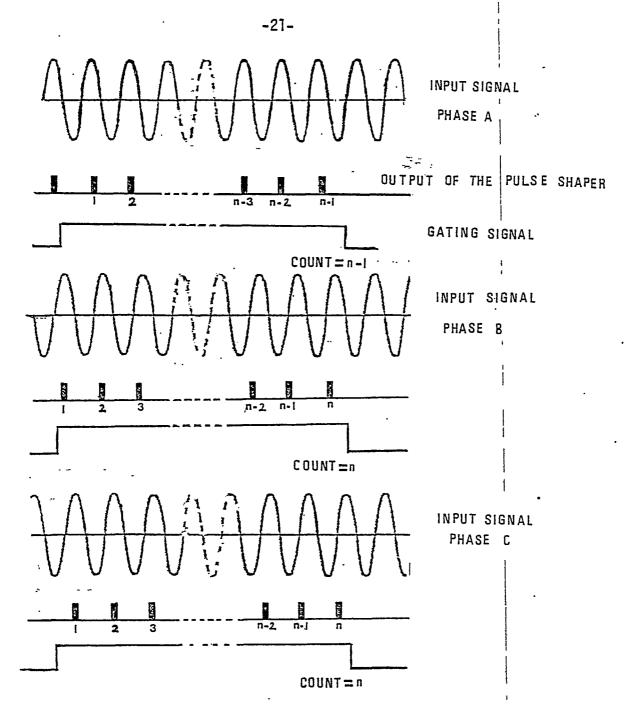

| Figure 3.2  | Voltages, pulsed information and gating signals for measuring the frequency of a three phase system                                                                          | 21   |

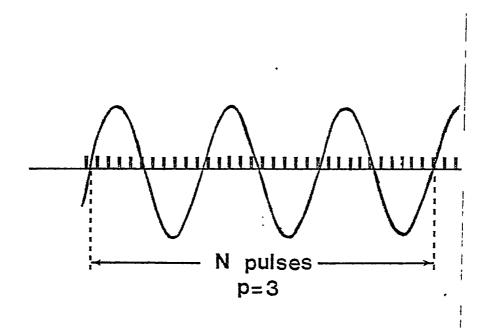

| Figure 3.3  | Measuring time duration of a single phase signal                                                                                                                             | 23   |

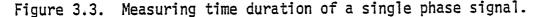

| Figure 3.4  | Measuring time durations of the three phase signals                                                                                                                          | 24   |

| Figure 3.5  | Gating error                                                                                                                                                                 | 25   |

| Figure 3.6  | Effect of noise on the zero-crossings of the signal                                                                                                                          | 26   |

| Figure 3.7  | Curve represents the error due to the neglected terms of the Taylor series expansion                                                                                         | 33   |

| Figure 3.8  | The curves represent the errors due to<br>random phasing of pulses during the<br>measurements, for different values of p<br>in the 100 kHz to 1 MHz clock frequency<br>range | 34   |

| Figure 3.9  | Error in the frequency calculated by<br>the first and second order equations<br>derived from Taylor series expansion                                                         | 35   |

| Figure 3.10 | The curves represent the error due to<br>random phasing of pulses during the<br>measurements, for different values of<br>p in the 100 kHz to 1 MHz clock<br>frequency range  | 36   |

ix

|              |                                                                                                                   | Page |

|--------------|-------------------------------------------------------------------------------------------------------------------|------|

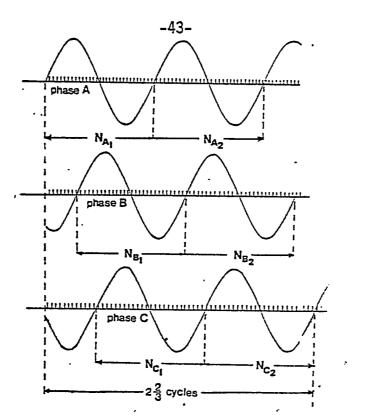

| Figure 4.1   | Pulses recorded in different phases of a three phase system                                                       | 43   |

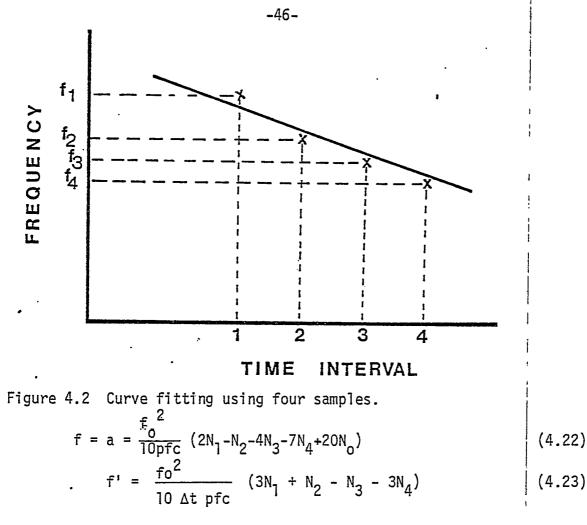

| Figure 4.2   | Curve fitting using four samples                                                                                  | 46   |

| Figure 5.1   | The conceptual arrangement of a digital counter and a digital computer                                            | 55   |

| Figure 5.2   | Logic block diagram of the counter circuit                                                                        | 57   |

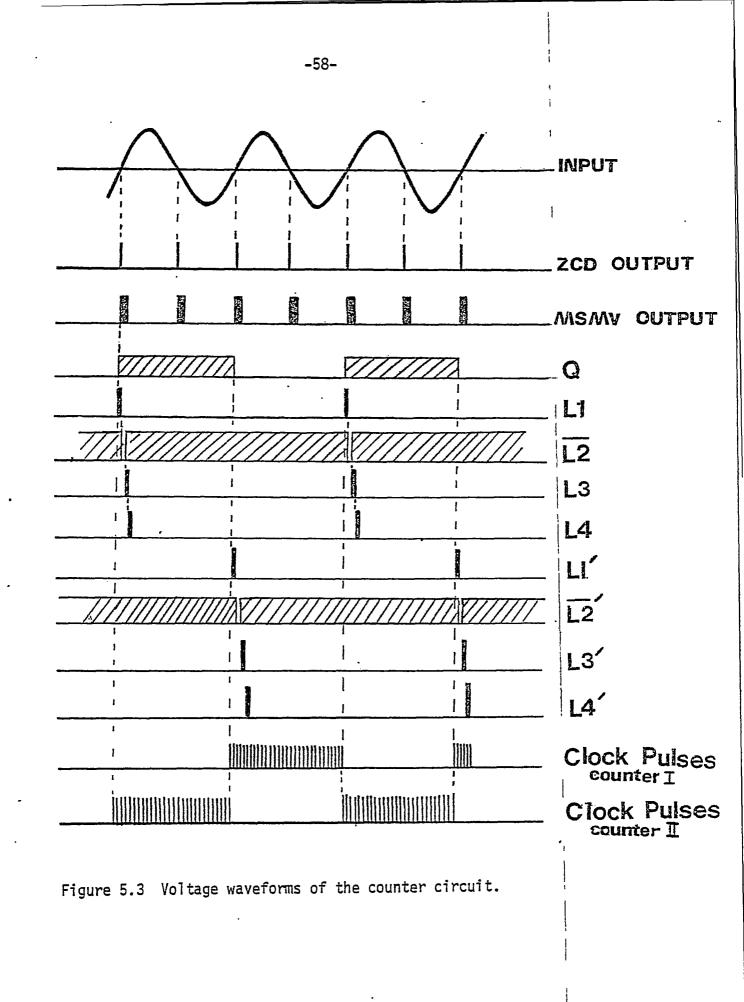

| Figure 5.3   | Voltage waveforms of the counter circuit                                                                          | 58   |

| Figure 5.4   | Block diagram showing the transfer of information between the computer and outside circuit                        | 59   |

| Figure 5.5   | Equipment configuration for testing the counter                                                                   | 61   |

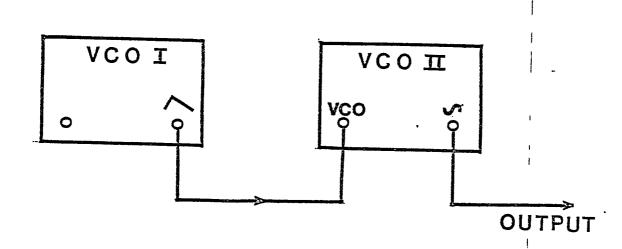

| Figure 5.6   | Equipment configuration for the simulation of rate of change of frequency                                         | 62   |

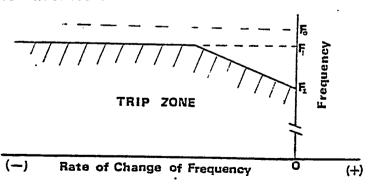

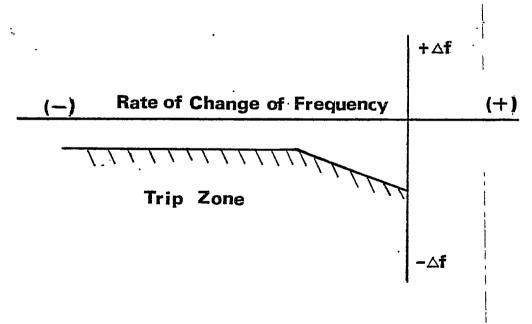

| Figure 5.7   | Proposed trip characteristic of the under-<br>frequency protection scheme                                         | 67   |

| Figure 5.8   | Trip characteristic                                                                                               | 68   |

| Figure 5.9   | A conceptual flowchart of the frequency cum rate of change of frequency relay                                     | 69   |

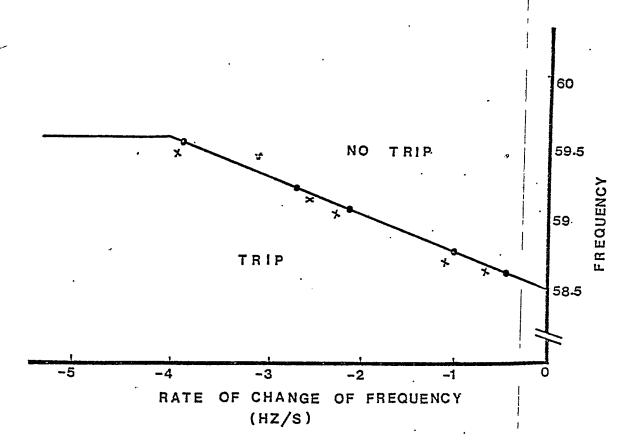

| Figure 5.10  | Under frequency cum rate of change of frequency relay characteristic and test results                             | 72   |

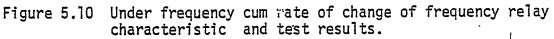

| Figure I.1   | A single phase faulted circuit                                                                                    | 79   |

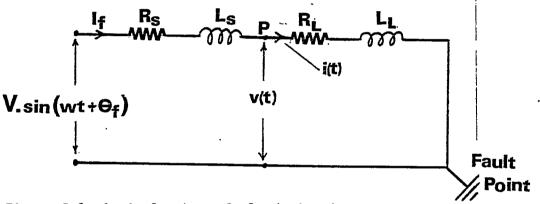

| Figure I.2   | One-line diagram of a transmission<br>system and its positive sequence diagram<br>2500 kVA and 5.5 kV base values | 80   |

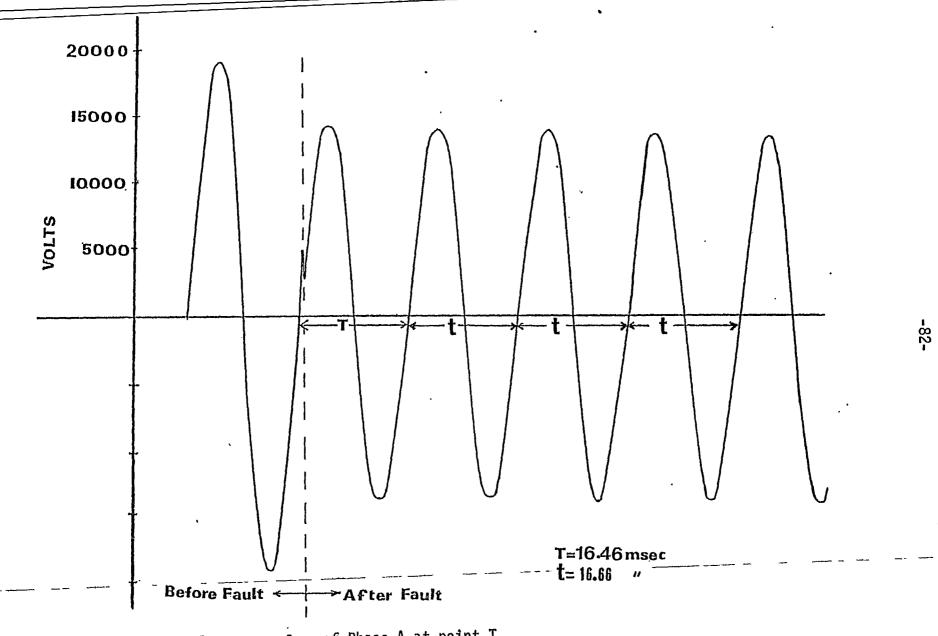

| Figure I.3   | Voltage waveform of phase A at point T                                                                            | 82   |

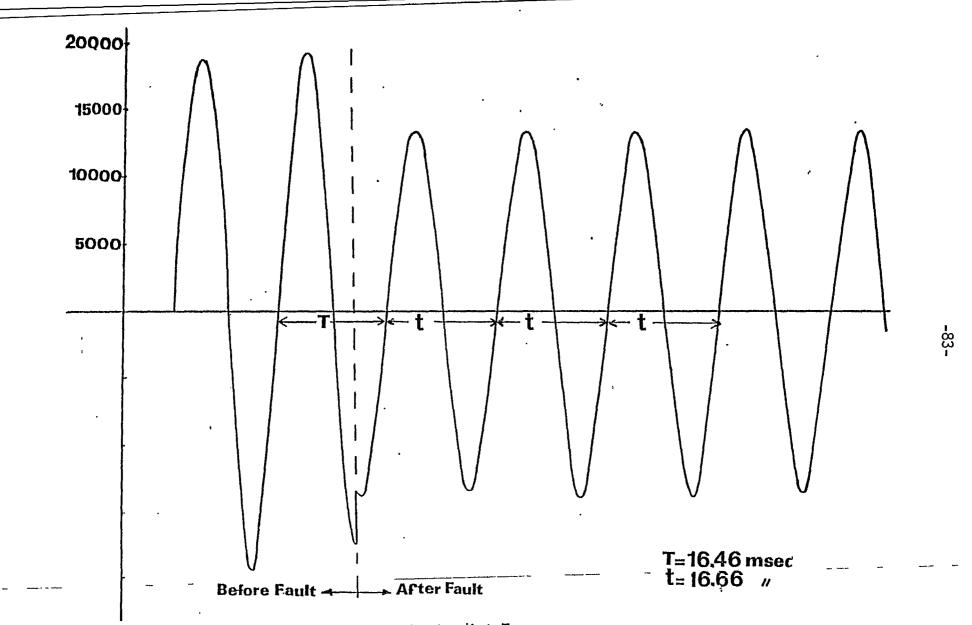

| Figure I.4   | Voltage waveform of phase B at point T                                                                            | 83   |

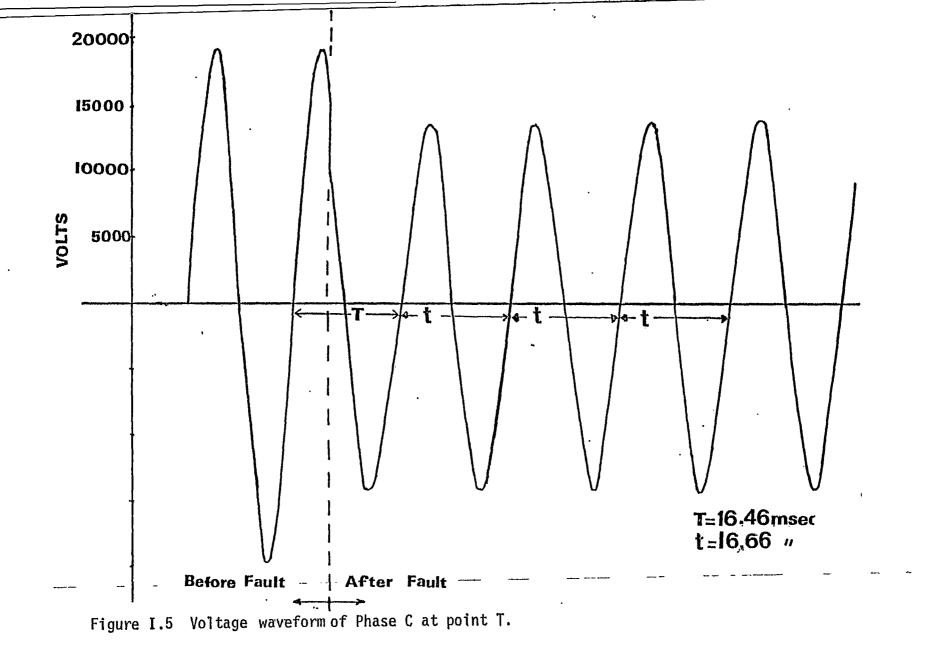

| Figure I.5   | Voltage waveform of phase C at point T                                                                            | 84   |

| Figure II.1  | Schematic diagram of the counter circuit                                                                          | 91   |

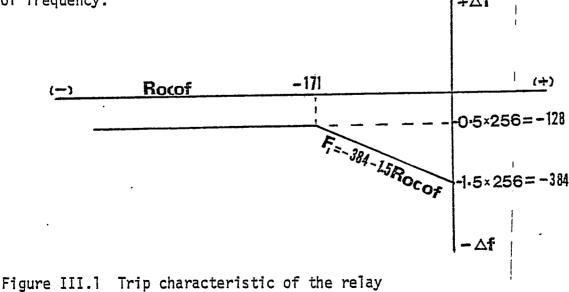

| Figure III.1 | Trip characteristic of the relay                                                                                  | 95   |

| Figure III.2 | Flowchart of the software program                                                                                 | 100  |

•

## LIST OF TABLES

| Table |                                                                                                                                                           | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Maximum Cumulative Operating Time at<br>Subnormal Frequencies                                                                                             | 9    |

| 3.1   | Maximum Errors Observed in the Frequency<br>Calculated by Equation 3.1 Using<br>Different Clock Frequencies and One Cycle<br>Measurement Duration (p = 1) | 31   |

| 3.2   | Maximum Errors Observed in the Frequency<br>Calculated by Equation 3.1 Using<br>Different Clock Frequencies and Measure-<br>ment Durations                | 32   |

| 4.1   | Maximum and Minimum Values of the Rate<br>of Change of Frequency Calculated by<br>Equation 4.2 for an Input Signal Chang-<br>ing at 2 Hz/sec              | 48   |

| 4.2   | Maximum and Minimum Values of the Rate of<br>Change of Frequency Calculated by<br>Equation 4.3 for an Input Signal Changing<br>at 2 Hz/sec.               | 48   |

| 4.3   | Maximum and Minimum Values of the Rate of<br>Change of Frequency Calculated by<br>Equation 4.8 for an Input Signal<br>Changing at 2 Hz/sec                | 49   |

| 4.4   | Maximum and Minimum Values of the Rate of<br>Change of Frequency Measured Using the<br>Information from all Three Phases                                  | 50   |

| 4.5   | The Maximum and Minimum Values of the Rate<br>of Change of Frequency Calculated by<br>Equation 4.15 for an Input Signal<br>Changing at 2 Hz/sec.          | 51   |

| 4.6   | Maximum and Minimum Values of the Rate of<br>Change of Frequency Calculated by<br>Equation 4.18 for an Input Signal<br>Changing at 2 Hz/sec               | 51   |

|       |                                                                                                                                                           |      |

,

хî

Table

| 4.7 | Maximum Errors in the Rate of Change of<br>Frequency Calculated by the Curve Fitting<br>Approach                                                           | 52 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1 | Results of Testing the Counter by<br>Measuring 60 Hz Frequency of a Signal<br>Using Different Clock Frequencies                                            | 61 |

| 5.2 | The Maximum and Minimum Values of the<br>Rate of Change of Frequency Determined by the Second<br>Order Approximation Using a Clock Frequency<br>of 100 kHz | 64 |

| 5.3 | The Maximum and Minimum Values of the<br>Rate of Change of Frequency Determined by the Second<br>Order Approximination Using a Clock Frequency<br>of 1 MHz | 64 |

| 5.4 | The Maximum and Minimum Values of the<br>Rate of Change of Frequency Determined<br>by the Curve Fitting Approach using a Clock Frequency<br>of 100 kHz     | 65 |

| 5.5 | The Maximum and Minimum Values of the<br>Rate of Change of Frequency Determined<br>by the Curve Fitting Approach Using a<br>Clock Frequency of 1 MHz       | 66 |

| 5.6 | Test Results Showing the Desired<br>Operating Values and Relay Operation                                                                                   | 71 |

|     |                                                                                                                                                            |    |

#### 1. INTRODUCTION

### 1.1 Background

The functioning of the society is presently dependent on the continuity of power supply. Partial or total blackouts usually have serious economic and social consequences. To ensure a continuous supply of electrical energy and to minimize damage to the equipment, a power system is protected against faults. Relays are used to detect intolerable and unwanted operating conditions and to then initiate actions to either correct the abnormality or to isolate the faulted section.

The first protective device developed and used to isolate faulted equipment in a power system is the fuse. They are quite effective in limiting the damage due to faults and are, therefore, widely used in distribution circuits. The major disadvantage of using fuses is that they have to be replaced before power supply can be restored. The early relay designs used the attracted armature structures Later designs used induction disc structures which are more flexible and reliable. Continuous development of networks dictated that relays have higher operating speeds and increased ability to select the faulted zone. In 1920's, induction disc inverse time and high speed differential relays were introduced<sup>1</sup>. Later, balanced beam and induction cup units were used in protective devices. These structures proved useful in designing devices and systems which can meet the protection requirements of the present day power systems of

-1-

large size and complexity.

Solid state (electronic) relays were introduced some years ago and have gradually become acceptable. Many forms of phase and amplitude comparators have already been developed and used. These devices generally use analog and digital integrated circuits in addition to discrete components. Advances in the technology of computing processors have made it possible to consider their use in the area of power system protection. Digital processor based relays attempt to perform the functions normally expected of electromechanical and static (solid state) relays. Because of their high operating speed, inherent flexibility and ability to perform conditional branches and storing data acquired over long periods of time,<sup>2</sup> computers can perform additional tasks which the previously designed relays can not. The use of digital computers for system protection was first suggested by Last and Stalewsky<sup>3</sup>. The feasibility of protecting a substation by a digital computer was then investigated and reported in 1968 by G. D. Rockefeller<sup>4</sup>. Mann and Morrison<sup>5</sup> demonstrated the feasibility of applying a digital computer for transmission line protection. Computerized transformer and generator protection have also been attempted<sup>6,7</sup>. Sachdev and Wind<sup>8</sup> demonstrated that ditigal computers can be used for differential protection of generators.

1.2 Underfrequency Protection and Frequency Relays

Frequency relays are generally used to automatically disconnect prespecified blocks of load in case of generation deficiency in a

-2-

system and, thus, restore the system frequency to normal levels.

Loads were shed manually by the operators before the frequency relays were used for this purpose. To detect sub-normal frequency conditions and take action in time is not easy for an operator especially when the frequency drops at a high rate. As the power systems increased in size and complexity, it became impractical to manually shed load without jeopardizing system operation. This difficulty was overcome by installing frequency relays at substations and having them trip breakers of selected feeders supplying loads.

Electromagnetic frequency relays were first developed and are widely used at present. These relays respond to a decrease in the frequency; a prespecified time delay is also incorporated. The delay in operation is not constant; it depends on the rate of change of frequency. Relays which respond to a combination of the frequency and rate of change of frequency have also been developed. A solid state relay developed by the Ontario Hydro<sup>3</sup> responds to the rate of change of frequency as the system frequency reduces to subnormal levels. Prespecified blocks of load are shed at various levels of rate of change of frequency after the system frequency decreases to a prespecified level. Durkin, Eberle and Zarakas<sup>10</sup> developed a frequency relay which responds to a combination of the frequency and its rate of change. This relay uses analog circuits in its design and its frequency vs rate of change of frequency characteristic is continuous. Widrevitz and Armington<sup>11</sup> developed a frequency cum rate of change of frequency relay using digital electronics.

-3-

## 1.3 Objectives of the Project

The objectives of the project are to design a computer based frequency cum rate of change of frequency relay. A conceptual arrangement of this relay is shown in Figure 1.1. A set of potential transformers reduce the voltage signals from the E.H.V. level to 110 Volts. These signals are reduced to 25 Volts peak to peak and applied to a preprocessor which is basically a low pass filter. The output of the processor is applied to a hardware block which measures the time durations of the cycles of the input signals. These measurements are in the form of counts of high frequency pulses counted in the duration of interest. The counts are then transferred to a computing device which calculates the frequency and the rate of change of frequency and then decides if any action to shed load is warranted or not.

This thesis presents a design of the hardware processor, evaluation of the methods of measuring frequency and the rate of change of frequency, a design of the frequency relay and results of the tests performed on this relay in the lab.

The philosophy of frequency relaying and the necessity of their use are examined in Chapter 2. The reasons for using both frequency and its rate of change for a frequency protection scheme are discussed. A basic form of an underfrequency protection scheme is also briefly presented.

Methods of determining frequency are presented in Chapter 3. Accuracy and suitability of these methods for digital relaying are examined. Two of these methods are found to be adequate for use in a software based relay.

-4-

Techniques of measuring the rate of change of frequency are presented in Chapter 4. The suitability of these methods are examined and reported in this chapter. Two of the four methods discussed in Chapter 4 are found to be suitable for determining the rate of change of frequency for digital relaying.

The hardware and software of the proposed digital frequency cum rate of change of frequency relay are described in Chapter 5. The performance of the relay was tested in the laboratory; the results of these tests are also given in this chapter.

Fig. 1.1 A conceptual arrangement of a software based frequency relay.

-5-

## 2. <u>PROTECTION PHILOSOPHY AND FREQUENCY</u> <u>RELAYING</u>

This chapter briefly describes the general philosophy of protecting power systems. The hazards of operating a system at subnormal frequencies and the necessity of frequency relaying are discussed. The advantages of relays which respond to a combination of the system frequency and the rate of change of frequency are enumerated. The commercially available frequency relays are also briefly described.

## 2.1 General Protection Philosophies

Relays are used to limit equipment damage and to maintain continuity of service in modern power systems. Protective relays detect the presence of faults, such as, short circuits between phases and to ground, and isolate the faulted equipment by opening appropriate circuit breakers. Some other relays, such as, automatic reclosing relays attempt to restore power on lines which may have been removed from service to isolate temporary flash overs to ground. To minimize the effects of disturbances, a protective system should be reliable and selective and should be capable of operating at high speeds. It is also desirable that the cost of a protective equipment be commensurate with the benefits derived by its use. These objectives can not usually be met and, therefore, some compromises are made to arrive at acceptable designs.

-6-

## 2.1.1 Classification of relays

ANSI Standard C.37.90(IEEE 313)<sup>12</sup> classifies relays by:

- i) the functions they perform.

- ii) their operating principles and the operating principles of their structures.

- iii) their operating characteristics.

- iv) the inputs which excite the relay.

The relays classified by their functional categories include monitoring relays, protective relays, programming relays, regulating relays and auxiliary relays. Percentage, thermal, solid state and electromechanical relays are some of the examples of relays classified by their operating principles or the operating principles of their structures. The relays classified by their performance characteristics include, among others, distance, directional, overcurrent, undervoltage and ground and phase comparison relays. Current, voltage, pressure, frequency and temperature relays are the examples of relays classified by the types of inputs which excite the relays.

2.1.2 Applying protective relays

Before the relays classified in the last paragraph are applied, the following aspects of the system and its operating experiences need to be considered.<sup>13</sup>

- i) System configuration.

- ii) Existing protective equipment and experiences of its maloperation or failure to operate.

- iii) Present operating procedures and practices; possible future expansion.

- iv) Desired degree of protection.

- v) Fault levels.

vi) Maximum load.

- vii) The ratios of voltage and current transformers.

- viii) Location of voltage transformers.

- ix) Parameters of generators, lines, transformers and loads.

Many of these aspects need to be considered for applying relays which respond to system frequency and its rate of change.

### 2.2 Frequency Relaying

Protection philosophy and classification of relays have been briefly given in the last section. One of the relays classified by the type of input quantity used is the frequency relay. The reasons for applying the relays of this type are discussed in this section.

An unbalance between generation and load tends to change the system frequency which should be maintained very close to its rated value. Frequency relays are usually used to detect changes in frequency, and to then initiate action to restore the frequency to its nominal value.

Frequency changes which can be generally tolerated in a system, are determined by the characteristics of the rotating equipment. For example, the blades of a steam turbine have resonance frequencies in the neighborhood of three percent below the rated frequency of the system. This resonance usually damages the blades seriously; the damage suffered is cumulative in nature.<sup>9</sup> To minimize the possibility of fatigue failure due to vibrations, operation at low frequencies is limited to the levels given in Table 2.1.<sup>14</sup> A perusal of this table suggests that normal frequency levels should be restored as quickly as possible.

-8-

| Operating Frequency-Hz                                                        | 59.4        | 58.8 | 58.2 | 57.6           | 56 |

|-------------------------------------------------------------------------------|-------------|------|------|----------------|----|

| Total Permissible<br>Operating Time<br>(minutes) over<br>the Life of the Unit | No<br>Limit | 90   | . 10 | <br> <br> <br> | 0  |

Table 2.1 Maximum Cumulative Operating Time at Subnormal Frequencies

The speed of generating station auxilaries, such as, fans, pumps and mills which are driven by electrical motors decreases as the system frequency reduces. A 10% reduction of speed of the auxiliaries can lower the plant output by up to 30%<sup>15</sup>. A decrease in frequency also requires that the operating flux must increase if the operating voltage level is to be maintained. This increases the magnetizing current of transformers, motors and other electromagnetic devices and, in turn, causes excessive heating of these devices and increases the reactive load of the system. Another effect of a drop in system frequency is the reduction of the reactive power generated by the capacitors, overhead lines and underground cables. The reactive power balance is, therefore, adversely affected if the system is allowed to operate at sub-normal frequencies. Operating time of most induction relays increases with a decrease in system frequency.<sup>9</sup> Accuracy of measuring instruments is also affected by frequency deviations.

### 2.3 Load Shedding

The frequency of a power system remains constant if the generated power is equal to the sum of all loads plus system losses.

An upset of this balance tends to change the system frequency. A decrease in available generation causes a decline in the frequency of a system if it is isolated from the interconnected network and sufficient spinning reserve is not available. In such cases, underfrequency relays should automatically shed some load to raise the frequency back to normal. This action involves deliberate interruption of power to some customers but is essential to prevent excessive damage to major equipment and subsequent major dislocation of services.

#### 2.4 Frequency Relays

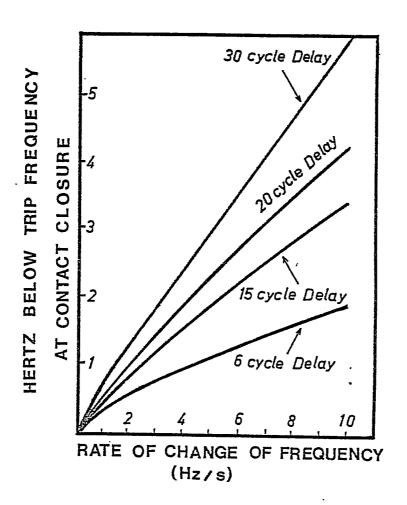

As discussed in the last section, frequency relays are used to shed load. Two types of relays generally used are the induction disc/induction cylinder and solid state types. The induction disc and induction cylinder relays are of the electromagnetic type whereas the electronic relays use analog and digital circuits. These relays respond to a decrease in frequency and have characteristics similar to those shown in Figure 2.1<sup>13</sup>. The relay operation is delayed by a specifid time after the frequency is detected to have declined below a set value. It is obvious that the frequency at the time of relay contact closure will be different from the set value. The difference will depend on the rate at which frequency has been declining.

-10-

Figure 2.1 Characteristic of an induction cylinder frequency relay.

## 2.5 Rate of Change of Frequency

It has been pointed out in the last section that the system frequency at the time of relay contact closure depends on the rate at which the frequency has been declining. This problem can be alleviated by modifying the criterion of tripping to include a rate of change of frequency feature which is discussed in this section.

Frequency of a power system declines at a rate inversely

ł

-11-

proportional to the system inertia and directly proportional to the difference between the generated power and system load. This can be mathematically expressed as:

$$\frac{\mathrm{df}}{\mathrm{dt}} = -\frac{\Delta P}{M} \tag{2.1}$$

where:

: f is the system frequency;

$\Delta P$  is the unbalance between generated power and load;

M is the inertia constant of the system. It is obvious from this equation that, for a given system, the rate of change of frequency indicates the unbalance between generation and load. A frequency cum rate of change of frequency relay is, therefore, likely to be more effective than a frequency relay.

Another advantage of including the rate of change of frequency feature in a frequency relay is a reduction of the dynamic error between the frequency setting and the supply frequency at the instant of relay operation. This advantage increases with an increase of the rate of frequency change.

2.6 A Load Shedding Scheme

The necessity of load shedding when a generation-load unbalance occurs has been discussed in the last section. For effective results, a load shedding scheme should be carefully designed. Some aspects associated with the design of such schemes are given in this section.

A load shedding scheme should decide when some load should be curtailed. It should also decide how much load needs to be shed and which circuit breakers should be opened to reduce the system load. These requirements are somewhat different in each case and, therefore,

-12-

load shedding schemes should be specifically designed for each system.

One of the features of a load shedding scheme is its upper and lower frequency limits. No load shedding is necessary if the system frequency is above the upper limit. Also, the system frequency is not allowed to fall below the lower limit. A number of load blocks are shed as the system frequency falls below the upper limit and approaches the lower limit.

The frequency of an interconnected system doesn't change appreciably if enough spinning reserve is available and the interconnections remain in operation. Maximum generation loss which can be tolerated without impairing the integrity of the system is calculated as demonstrated in the following example.

Consider an interconnected network of three systems as shown in Figure 2.2 and consider that a disturbance causes a deficiency of D<sub>1</sub> MWs in system 1. If the deficiency made up by each system is proportional to its capacity, additional power transfers between the systems will be given by

$$T_{21} = \frac{D_1 C_2}{C_1 + C_2 + C_3}$$

(2.2)

$$T_{31} = \frac{D_1 C_3}{C_1 + C_2 + C_3}$$

(2.3)

where:  $C_i$  denotes the capacity of the ith system. The remaining deficiency which is equal to  $\frac{D_1C_1}{C_1 + C_2 + C_3}$  will be made up by system 1. The decrease of frequency due to the loss

-13-

of generation is determined by the permanent droop of the governors and is given by:

$$\Delta f = \frac{\text{generation loss}}{\text{Capacity X Permanent droop}}$$

(2.4)

A 1000 MWs load over generation unbalance in system 1 will cause the intertie flows,  $T_{21}$  and  $T_{31}$ , to increase by 37.5 and 929 MW. If the normalized permanent droop is 1.0, the decrease of frequency for correcting the unbalance will be 0.25 Hz. The upper frequency of a load shedder for this system should, therefore, be 59.75 Hz if the maximum unbalance which can be absorbed by the system is 1000 MWs. In this case the system integrity will be maintained for frequencies above 59.75 Hz and there will be no danger of the frequency falling to unacceptable values if the load over generation unbalance is less than 1000 MWs.

If the tie line connecting areas 1 and 3 is not capable of transmitting the required additional power, the line will be disconnected leaving only systems 1 and 2 as a network with generation deficiency of 1000 MW. The frequency deviation in these areas will be 3.53 Hz which is unacceptable. This example reveals that a generation load unbalance causes large frequency deviations when the integrity of the system is upset.

The low frequency limit of a load shedding program is selected such that the frequency will never fall below the critical value. This limit is dictated by considering the operating problems of steam turbines and power plant auxiliaries. In general, steam turbines should be operated at speeds corresponding to frequencies above 59.5 Hz. Operation below 58.5 Hz is permitted for a limited

-14-

Figure 2.2. An interconnection of power systems.

time only. At this low frequency limit, the entire scheduled load relief process should be completed.

Between the high and low frequency limits a number of load shedding steps are usually introduced. Larger the number of steps selected, smaller is the load shed at each step. This makes the load shedding scheme more flexible but the coordination of the steps becomes more difficult. Experience has shown that, for most systems, three to five steps for load shedding are adequate.<sup>13</sup> The total load which should be shed depends on the maximum anticipated overload. Theoretically, there is no limit to the extent of load to be shed. Service can be restored much more rapidly if 100% load is shed instead of allowing a system to collapse.

A four-step load shedding program is shown in Figure 2.3<sup>16</sup> which is designed to protect up to 100% overload and settles at 57 Hz Load shedding curves for settling at 58,59 and 60 Hz are also included in this figure. The frequency at which the system will settle after a predetermined load is shed for specified overloads can be determined from this figure. For example, when the overload is 20%, the load is shed in two steps and the frequency will settle at approximately 59.5 Hz. For some overloads the frequency will rise above 60 Hz after load shedding because the shed load is more than the extent of overload.

Figure 2.3 Four step load shedding program to protect up to 100% overload.

-16-

2.7 Other Frequency Relay Applications

Frequency relays are used for many functions other than detecting under frequency and shedding load. Some of these functions are as follows 13.

- i) Frequency relays are also applied to protect generators from overspeed during start up and loss of load.

- ii) Frequency relays can be applied to isolate generating units when load shedding is not able to restore frequency to acceptable levels.

- iii) Frequency relays can also be used to disconnect interconnections between systems when load shedding is not able to restore frequency to acceptable levels.

A brief description of protection philosophy has been presented. The importance of frequency relaying and some applications of under frequency relays have been outlined. The basis of a load shedding program has also been discussed in this chapter.

## 3. TECHNIQUES OF MEASURING FREQUENCY\_

The importance of measuring frequency and the rate of change of frequency for protecting power systems has been discussed in Chapter 2. It has been demonstrated that, both the frequency and its rate of change need to be accurately measured for providing adequate protection. Methods of measuring frequency are examined in this chapter. The suitability of these methods is also investigated.

### 3.1 Classification of the Measurement Techniques

Until recently electromechanical devices were used to measure frequency. These devices have, however, been gradually replaced by electronic equipment using digital counters. The approach is simple and is more accurate than the electromechanical devices. The methods for determining frequency by digital techniques may be classified into the following categories:

- i) Direct method.

- ii) Measuring time for a specified number of periods and calculating frequency.

- iii) Measuring time for a specified number of periods and estimating frequency.

## 3.2 Direct Method

This approach consists of counting the number of cycles of the input signal during a specified time interval, Tg; called gating time. This interval is usually controlled by an internal reference

-18-

oscillator. The recorded count will be the frequency in Hz if the gating time is one second. By selecting intervals which are multiples or submultiples of one second, different resolutions of the measurement can be achieved. The basic approach is described by the block diagram of Figure 3.1. The input signal is applied to a pulse shaping circuit which converts the sinusoidal input to short duration pulses -one for each cycle. The output of the reference oscillator controls the gate and enables the counting of the pulse shaper output during a gating period. The accuracy of this approach depends on the maximum gating time available for measuring frequency. For example, the accuracy of the frequency measurements of a 100 Hz signal will be within  $\pm 1\%$  if the gating time is one second. Longer gating times are needed to obtain better accuracies; but large gating times cannot be permitted in power system protection applications.

Figure 3.1. Simplified block diagram of a frequency counter.

-19-

The accuracy of this approach can be improved by counting half cycles instead of full cycles. This approach reduces the error of measurement by 50%. In other words, the accuracy of measuring frequency by counting half cycles in a specified time, Tg, is the same as the accuracy obtained by counting full cycles in an interval equal to twice the specified time (2 Tg).

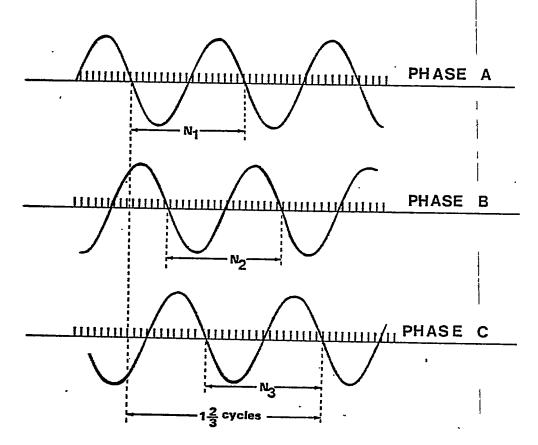

When measuring the frequency of three phase power systems, the accuracy of the direct method can be further improved by utilizing the information of all three phases. If the frequency is obtained by averaging the number of cycles of the three phases observed in a specified interval, Tg; the result will be similar to that obtained by using one phase and gating intervals of 3 Tg. In this approach, the three signals can be applied to pulse shaping circuits which convert the waveforms to short pulses for counting during each gating interval. Figure 3.2 depicts waveforms encountered in this approach. Should the gating waveform start just after a zero crossing of the Phase A, the counter of this phase will indicate n-1 cycles whereas the Phases B and C counters will record n cycles. The frequency will, therefore, be given by  $1/3 \cdot [(n-1) + n+n] = n-1/3$ . This measurement is much closer to the actual frequency than n-1 which would be obtained if only the Phase A signal was used. The averaging process eliminates most of the error caused by the missed count in Phase A; but the accuracy of measurements obtained by this method is also not adequate for power system protection.

-20-

Figure 3.2. Voltages, pulsed information and gating signals for measuring the frequency of a three phase system

The accuracy of frequency measurements can be further improved by using the 3 phase approach and counting half cycles of each phase. The improvement is, however, not adequate to make the approach suitable for measuring the frequency of power systems for protection purposes.

## 3.3 Measuring Time for a Specified Number of Periods and Calculating Frequency

Power system applications require that the frequency be measured in a few cycles and the accuracy be better than that of the techniques described in Section 3.2. An approach which satisfies this requirement consists of measuring the time duration of an integral number of cycles of the signal and calculating the frequency from this measurement. High frequency pulses produced by an oscillator can be counted during specified cycles of the input signal to measure the time duration. A 1 MHz oscillator provides a count of 10000 in a period of 100 Hz signal. The accuracy of this approach is at least an order of magnitude better than that obtained by the direct method using gating periods of 10 seconds. Moreover, the measurement is completed in 10 msec. This method makes use of the basic relation between the period and frequency; frequency is the reciprocal of the time of a period. If the time of an integral number of cycles, say p, is measured using a high frequency clock, the frequency of the signal can be calculated by using Equation 3.1.

$$f = \frac{pfc}{N}$$

(3.1)

where, fc is the frequency of the clock,

N is the number of high frequency pulses counted in p cycles. Random phasing of the clock pulses and pulses generated at the zero crossings of the input signal cause errors in measurements. These errors can be reduced by using longer gating periods (selecting p grater than one). This approach, however, slows the speed of completing

-22-

the measurement.

The present frequency measuring techniques use only one phase of the three phase power system. It has been demonstrated in Section 3.2 that information from all three phases can be used to improve the accuracy of frequency measurements by direct methods. A similar approach can be used in measuring time durations of all the three phases, and then calculating the system frequency. Advantages expected by utilizing information from all the three phases are explained in the following example. Consider that the frequency is determined by measuring the time duration of p cycles, p = 3, of a single phase signal as shown in Figure 3.3. The N pulses recorded during the measurement is the average information of three cycles. Now consider that the frequency is determined by measuring the time duration of one cycle of all the three phases of the system as shown in Figure 3.4.

-23-

Figure 3.4. Measuring time durations of the three phase signals. If the high frequency counts for a cycle of the three phases are  $N_1$ ,  $N_2$  and  $N_3$ , average count  $\frac{1}{3} \cdot (N_1 + N_2 + N_3)$  can be used to calculate frequency. The frequencies calculated from the time period of three cycles of a single phase signal and from the time durations of one cycle of all the three phases will have similar levels of accuracies. The measurement is completed in  $1\frac{2}{3}$  cycles in the three phase approach compared to three cycles of the single phase approach. This represents a 44 percent saving in the time required for measuring frequency.

The method of measuring period has basically three potential sources of error; gating error, high frequency clock errors and noise.<sup>17</sup>

-24-

3.3.1 Gating error

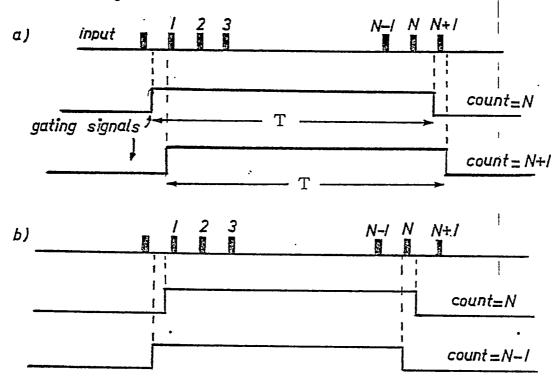

A random phase relationship exists between the gating and gated signals. This introduces an inherent error of  $\pm 1$  count as is obvious in Figure 3.5.

Figure 3.5 Gating error

If the gating waveform starts midway between the two input pulses, the recorded count will be correct, say n. Should the gate open just before or during an input signal pulse, the recorded count will be n+1. The recorded count will be n-1 if the gate opens just after an input pulse. The count error is, therefore, -1 or +1 and corresponds to a frequency error of approximately  $\pm \frac{1}{n}$  f.

## 3.3.2 High frequency clock errors

The accuracy of measurements also depends on the stability and accuracy of the high frequency clock which is usually a crystal oscillator. The accuracy of most crystal oscillators is temperature dependent. If frequency measurements are recorded at room temperature, no special measures, such as, using temperature controlled ovens will be needed.

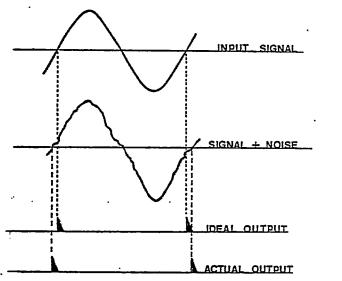

#### 3.3.3 Noise

Noise distorts the input waveforms and causes the trigger point to vary from cycle to cycle as shown in Figure 3.6. The time duration measurements are affected by changing the count n to  $n \pm \Delta n$ which changes the measured frequency from f to  $f \pm \Delta n f$ . The measurement errors can be reduced by increasing the interval over which the time is measured. The increase of the measurement interval also reduces the inaccuracies caused by the gating errors and noise. Using longer measurement intervals, however, slows the determination of frequency.

Effect of presence of D.C. offset on frequency measurements was also studied and it is given in Appendix I.

-26-

The method of measuring time for specified number of periods and calculating frequency using Equation 3.1 described in this section can not be conveniently used in digital relays which use computing devices, such as, microprocessors and minicomputer. This is because Equation 3.1 requires that a prespecified number, product of p and fc, be divided by a variable count, N. Approximate methods which avoid this division are discussed in the next section.

### 3.4 Measuring Time for a Specified Number of Periods and Estimating Frequency

As described in Section 3.2, the frequency of a signal can be measured by counting the number of cycles of the signal in a specified time interval. Another method which is described in Section 3.3 consists of counting high frequency pulses in the time of a specified number of cycles of the signal, then calculating frequency. This method involves a division of a pre-specified number by a variable count of the high frequency pulses. To avoid the division, modified approaches which estimate frequency without resorting to division can be used. These approaches are based on the first and second order approximations developed by using the Taylor series expansion of Equation 3.1. The essential features of these methods are discussed in this section.

## 3.4.1 First order approach

The Taylor series of a function y(x) in the neighborhood of  $x_0$  is expressed as:  $y(x) = y(x_0) + y^r(x) \begin{vmatrix} \cdot (x-x_0) + y^n(x) \\ x=x_0 \end{vmatrix} \begin{vmatrix} \cdot (x-x_0)^2 + \dots + y^n(x) \\ x=x_0 \end{vmatrix} \begin{vmatrix} \cdot (x-x_0)^n + \cdots \\ x=x_0 \end{vmatrix}$ (3.2) Using this equation,  $y = \frac{1}{f}$  can be expressed in the neighborhood of fo by the following equation.

$$\frac{1}{f} = \frac{1}{f_0} - \frac{(f-f_0)}{f_0^2} + \frac{(f-f_0)^2}{f_0^3} - \dots$$

(3.3)

Considering the first two terms of this equation and substituting for from Equation 3.1, the following equation is obtained.

$$f \simeq \frac{fo^2}{pfc} \cdot \frac{[2pfc] - N]}{fo}$$

(3.4)

In this equation, <u>pfc</u> is the number of high frequency pulses in p fo periods of nominal frequency, fo. Defining this high frequency count as No, Equation 3.4 can be rewritten as:

$$f \simeq \frac{fo^2}{pfc} [2No - N]$$

(3.5)

The clock frequency, fc, and periods of measurement, p, can be selected in such a manner that  $\frac{fo^2}{pfc}$  becomes a multiple of 2,2<sup>-k</sup>. A division by using a variable count,N, is now transformed to a subtraction and multiplication by 2<sup>-k</sup>. The subtraction is a simple operation and the multiplication by 2<sup>-k</sup> can be achieved by a bit shift operation which takes very little computation time. In this manner, a division by N is replaced by operations which are convenient to perform in digital computing devices. The estimated frequency is, however, somewhat inaccurate due to neglecting the second and higher order terms of the Taylor series.

3.4.2 Second order approach

It is also possible to use the first three terms of the Taylor series expansion of  $\frac{1}{\frac{1}{7}}$  (Equation 3.2) for expressing frequency

-28-

as a function of the high frequency count, N. Using this approach and a procedure similar to that used in the last section, the following expression is obtained.

$$f = \frac{3}{2} fo - \frac{fo}{2} \sqrt{\frac{4fo}{pfc} N - 3}$$

(3.6)

The accuracy of this approach is better than that of Equation 3.4; but a division by N in Equation 3.1 has been replaced by a square root of a function of N which increases the complexity and computation time instead of reducing these factors.

Another possible approach is to expand the function,  $f = \frac{pfc}{N}$ in the neighborhood of No using the Taylor series. This series for a function Ø (N) in the neighborhood of No is as follows:

$$\emptyset(N) = \emptyset(NO) + \emptyset'(N) \left| (N-NO) + \frac{\emptyset''(N)}{2!} \right| (N-NO)^2 + \cdots \quad (3.7)$$

Considering only the first three terms of this expansion provides the following equation.

$$\emptyset(N) = f = \frac{pfc}{No} - \frac{pfc}{No^2} \cdot (N-No) + \frac{2pfc}{No^3} \cdot \left(\frac{N-No}{2!}\right)^2$$

(3.8)

Substituting N-No =  $\Delta N$  frequency is given by

$$f = \frac{pfc}{No} - \frac{pfc}{No^2} \frac{\Delta N}{No^3} + \frac{pfc}{No^3} (\Delta N)^2$$

(3.9)

Dividing both sides of the Equation 3.9 by fo =  $\frac{\text{pfc}}{\text{No}}$ , the following equation is obtained.

$$\frac{f}{fo} = fpu = 1 - \frac{fo}{pfc} - \Delta N + \left(\frac{fo}{pfc}\right)^2 \cdot \Delta N \cdot \Delta N. \qquad (3.10)$$

This approach eliminates the square root operation. The terms  $\frac{10}{pfc}$  and  $\frac{fo^2}{p^2fc^2}$  are constants; p and fc can be selected such that these

terms are multiples of two,  $2^{-k}$ . This approach replaces a division by a variable, N, by three additions/subtractions, two bit shifts and a multiplication( $\Delta N. \Delta N$ ). Hardware multiplier can be used for this purpose. No hardware dividers are available at present. The accuracy of measurements is considerably improved as compared to the first order approach but the computation effort required by the second order approach is more than that for the first order approach. 3.5 Off-Line Testing of the Methods of Determining Frequency

The methods of measuring frequency have been presented in the previous sections of this chapter. These methods were tested to determine their effectiveness. The test results of the following methods are presented in this section.

- i) Measuring time for a specified number of periods and calculating frequency.

- ii) Measuring time for a specified number of periods and estimating frequency by using first order approach.

- iii) Measuring time for a specified number of periods and estimating frequency by using second order approach.

- 3.5.1 Measuring time for a specified number of periods and calculating frequency

This method has been explained in Section 3.3. The time for an integral number of cycles is measured from which frequency of the input signal is calculated using Equation 3.1. For the tests described in this section, sinusoidal signals of frequencies ranging from 50 to 70 Hz were simulated in a software program. Clock pulses of frequencies ranging from 10kHz to 1MHz were also simulated in this program. The frequencies of the signals were calculated using Equation 3.1. Time duration of one cycle was used in these studies. Maximum errors observed from amongst a large number of simulations are listed in Table 3.1. A perusal of this table reveals that, as expected, the observed errors depend on the clock frequency. Higher clock frequencies result in lower errors.

| Table 3.1 | Maximum Errors Observed in the Frequency Calculated by |

|-----------|--------------------------------------------------------|

|           | Equation 3.1 Using Different Clock Frequencies and One |

|           | Cycle Measurement Duration $(p = 1)$                   |

| Clock Frequency | Maximum Error |

|-----------------|---------------|

| 10 kHz          | ± 0.49        |

| 50 kHz          | ± 0.098       |

| 100 kHz         | ± 0.049       |

| 200 kHz         | ± 0.025       |

| 360 kHz         | ± 0.0136      |

| 500 kHz         | ± 0.0098      |

| 1 MHz           | ± 0.0049      |

The time period of each measurement was then increased from one to four cycles in steps of one cycle. Table 3.2 lists the calculated frequency for the selected measuring intervals. A study of this table reveals that the accuracy improves with an increase of clock frequency and with an increase of the duration of measurement. The disadvantage of increasing the measuring duration is that it slows the speed of measurement. A suitable combination of the clock frequency and the duration of measurement can, however, provide the desired accuracy when Equation 3.1 is used.

-31-

Table 3.2 Maximum Errors Observed in the Frequency Calculated by Equation 3.1 Using Different Clock Frequencies and Measurement Durations.

| Clock Frequencies | Maximum Error<br>p = 2 | Maximum Error<br>p = 3 | Maximum Error<br>p = 4 |

|-------------------|------------------------|------------------------|------------------------|

| 10 kHz            | 0.248                  | 0.165                  | 0.122                  |

| 50 kHż            | 0.049                  | 0.033                  | 0.024                  |

| 100 kHz           | 0.0245                 | 0.016                  | 0.0122                 |

| 200 kHz           | 0.012                  | 0.008                  | 0.006                  |

| 360 kHz           | 0.0068                 | 0.0045                 | 0.0034                 |

| 500 kHz           | 0.0049                 | 0.0033                 | 0.00245                |

| 1 MHz             | 0.00245                | 0.0016                 | 0.0012                 |

## 3.5.2 Measuring time for a specified number of periods and Estimating the frequency by first order approach

Equation 3.4 developed with the help of Taylor series expansion avoids the division by high frequency count N. This approach has, however, two sources of error. One of these sources is the terms of the Taylor series neglected while developing the equation. Random phasing of the high frequency and zero crossing pulses is the second source of the errors. The errors of first kind can be estimated from Equation 3.11 as follows:

$$fe = f - \frac{fo^2}{pfc} \cdot (2No-N) = \frac{(f-fo)^2}{f}$$

(3.11)

where, f is the system frequency,

fo is the nominal frequency of the system and

fe is the error in the estimated frequency.

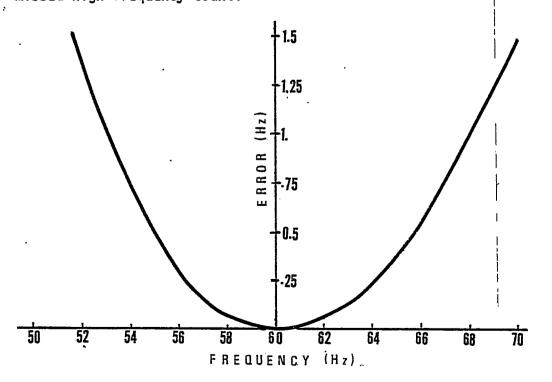

Figure 3.7 depicts the frequency error determined by Equation 3.11 as a function of the frequency. As expected, the errors are large for

frequencies substantially different from the nominal value. This is not a major concern because in power system applications frequency is usually not allowed to deviate by more than two or three percent and in this range the accuracy is quite good.

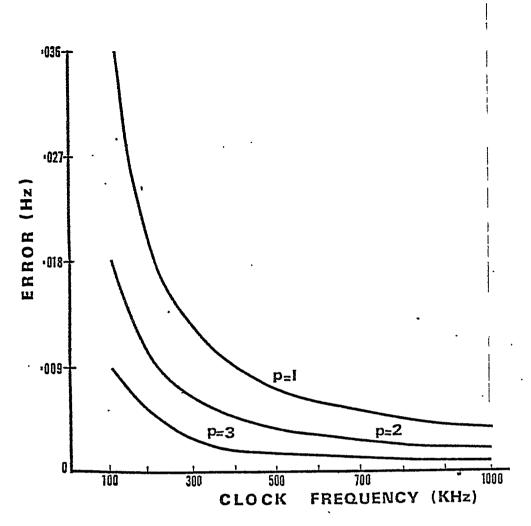

The errors of the second kind are caused by the fact that the observed high frequency count can differ from the true count by ±1. To examine the effect of this error on the measured time periods, sinusoidal signals of frequencies 50 to 70 Hz were simulated in a software program; clock pulses of frequencies ranging from 100 kHz to 1 MHz were also simulated in this program. The frequencies of the signals were determined by Equation 3.4. Time duration of one, two and four cycles were tested in these studies. Figure 3.8 depicts the errors in measuring frequencies ranging from 50 to 70 Hz due to the missed high frequency count.

# Figure 3.7 Curve represents the error due to the neglected terms of the Taylor series expansion.

-33-

Figure 3.8 The curves represent the errors due to random phasing of pulses during the measurements, for different values of p in the 100 kHz to 1 MHz clock frequency range.

3.5.3 Measuring time for a specified number of periods and estimating the frequency by second order approach

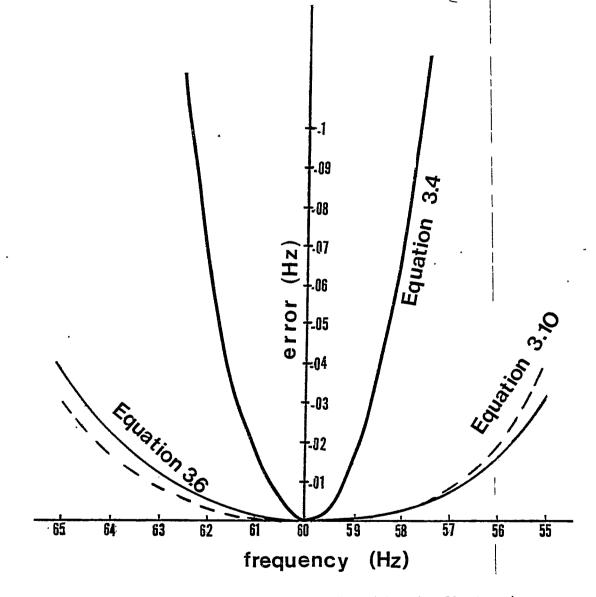

Equations 3.6 and 3.10 use the first three terms of the Taylor series expansion of  $\frac{1}{f}$  and f. The use of these equations do not provide true measurements of frequency. The errors are due to neglecting third and higher order terms of the Taylor series. These equations, however, provide measurements which are more accurate than those obtained by using the first order approach of Equation 3.4. For comparison the errors in measurements obtained by the first

-34-

order and second order approaches are plotted in Figure 3.9. This figure indicates that the measurements by the second order approaches are substantially more accurate than those obtained by the first order approach. A ten percent deviation of frequency causes less than 0.1% error in the frequency estimated by the second order approach.

Figure 3.9 Error in the frequency calculated by the first and second order equations derived from Taylor series expansion.

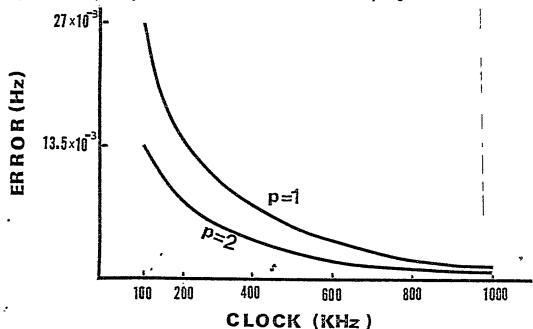

In addition to the error due to the neglected terms of the Taylor series, some error is also caused by the random phasing of high frequency pulses and the commencement of a cycle of the signal. Figure 3.10 represents this additional error when Equation 3.6 is used to estimate frequency. This information was obtained by simulating the frequency measurements in a software program.

Figure 3.10 The curves represent the error due to random phasing of pulses during the measurements, for different values of p in the 100 kHz to 1 MHz clock frequency range.

These errors are insignificant as compared to the errors depicted in Figure 3.8. The error of  $\pm 1$  count causes the measured frequency to be in error by  $\pm \frac{fo^2}{pfc}$  when the first order estimation approach is used. A similar error in the high frequency count causes the term inside the square root to be in error by  $\pm \frac{4fo}{pfc}$ . It is obvious that the count error affects the second order approach to a lesser degree than it affects the first order approach.

-36-

Techniques of measuring frequency have been presented in this chapter. The suitability of these approaches for use in relays based on digital devices has been discussed. The accuracy of these methods has also been examined.

#### 4. METHODS OF DETERMINING RATE OF CHANGE OF FREQUENCY

The importance of measuring frequency and rate of change of frequency and using them for saving a power system from collapse have been discussed earlier. Methods of measuring frequency have been presented in Chapter 3. Different methods of determining the rate of change of frequency are discussed in this chapter. The effectiveness of each method is also investigated.

#### 4.1 Classification of Methods

The methods of determining the rate of change of frequency can be classified in two groups as follows:

i) Measuring the time periods of successive cycles of the signal and calculating the rate of change of frequency.

ii) Measuring the time periods of successive cycles of the signal and estimating the rate of change of frequency. These methods use the Taylor series expansion and curve fitting technique to estimate the rate of change of frequency.

## 4.2 Measuring the Periods of Successive Cycles and Calculating the Rate of Change of Frequency

If the frequency at a power system bus changes from  $|f_1|$  to  $f_2$  in a small interval of time,  $\Delta t$ , the approximate value of the rate of change of frequency,  $f^1$ , may be calculated using Equation 4.1.

$$f^{1} = \frac{f^{2} - f_{1}}{\Delta t}$$

Hz/sec (4.1)

-38-

If  $N_1$  and  $N_2$  are the high frequency clock pulses recorded in two consecutive periods of p cycles,  $\Delta t$  may be approximated as  $(N_1 + N_2)/2f_c$ . As discussed in Chapter 3,  $f_1$  and  $f_2$  are approximately given by  $\frac{pf_c}{N_1}$  and  $\frac{pf_c}{N_2}$  respectively. Making these substitutions in Equation 4.1,

the following equation is obtained.

$$f^{1} = \frac{2pf_{c}^{2} \cdot (N_{1} - N_{2})}{N_{1} \cdot N_{2} \cdot (N_{1} + N_{2})} \quad Hz/sec$$

(4.2)

This form is not convenient for use in digital relays because it involves multiplications and divisions by variable numbers. To simplify this equation, linearized approximations of  $f_1$  and  $f_2$  may be used from Equation 3.4. Substituting  $f_1$  and  $f_2$  by  $f_0^2/pf_c.(2N_0-N_1)$  and  $f_0^2/pf_c.(2N_0-N_2)$ in Equation 4.1, the following expression is obtained.

$$f^{1} = \frac{f_{0}^{2}}{p} \cdot \frac{(N_{1} - N_{2})}{(N_{1} + N_{2})} \quad Hz/sec$$

(4.3)

This expression is simpler than Equation 4.2 but it still requires that a variable count be divided by another variable count.

4.3 Measuring the Period of Successive Cycles of the Signal and Estimating the Rate of Change of Frequency

The approach discussed in Section 4.2 is not suitable for use in digital relays because divisions by variable numbers are time consuming operations. This problem can be avoided by using a linearized approximation. Three linearized approaches which estimate the rate of change of frequency are presented in this section. These approaches are:

1) First order approximation,

- ii) Second order and

- iii) Curve fitting approach.

## 4.3.1 First order approximation

A simple expression for the rate of change of frequency can be obtained by using the Taylor series expansion of Equation 3.3 which is as follows.

$$\frac{1}{f} = \frac{1}{f_0} - \frac{(f - f_0)}{f_0^2} + \frac{(f - f_0)^2}{f_0^3} - \dots$$

The frequency f is given by  $\frac{pf_c}{N}$ . Making this substitution in Equation 3.3 and considering the first two terms of the series, Equation 4.4 is obtained.

$$\frac{N}{pf_{c}} = \frac{1}{f_{0}} - \frac{(f - f_{0})}{f_{0}^{2}}$$

(4.4)

Differentiating both sides of this equation, the following expression is obtained.

$$\frac{1}{pf_c}\frac{dN}{dt} = -\frac{1}{f_c^2}\cdot\frac{df}{dt}$$

(4.5)

This equation provides the following expression for the rate of change of frequency.

$$\frac{df}{dt} = -\frac{f_0^2}{pf_c} \cdot \frac{dN}{dt}$$

(4.6)

In this Equation  $\frac{dN}{dt}$  is the rate at which the number of recorded pulses change during the measurements and is approximately given by

$$\frac{dN}{dt} = \frac{N_2 - N_1}{\Delta t}$$

(4.7)

where:  $N_1$  is the number of pulses recorded in the first p cycles,  $N_2$  is the number of pulses recorded in the next p cycles and  $\Delta t$  is the time interval between the two successive measurements.

Substituting for  $\frac{dN}{dt}$  in Equation 4.6, the following equation is obtained.

$$f^{1} = \frac{df}{dt} = \frac{f_{0}^{2}}{pf_{c} \Delta t} \cdot (N_{1} - N_{2}) \quad Hz/sec$$

(4.8)

In Equation 4.8,  $\Delta t$  can be approximated as the measurement period at the base frequency  $(\frac{1}{f_0})$ .  $\frac{f_0^2}{pf_c \Delta t}$  is, therefore, a constant; p and f<sub>c</sub> can be selected in such a manner that this term is a multiple of two. In this manner, Equation 4.8 does not require any multiplications or divisions except by a factor of 2<sup>n</sup> which can be achieved by bit shifts in a digital device.

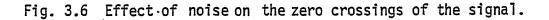

So far it has been assumed that the rate of change of frequency is obtained from the data of only one phase of a three phase system. In Chapter 3, advantages of measuring frequency from the data of all three phases were discussed. It is also possible to use information from all three phases for measuring the rate of change of frequency. The rate of change of frequency can be measured from the data of each phase separately, then the average of these measurements

-41-

can be calculated. This process reduces the inaccuracies caused by noise and gating errors. If  $f^1$  is measured from the time periods of two successive cycles, the three phase approach will take a total time of 2  $\frac{2}{3}$  cycles as is obvious from Figure 4.1. Achieving a similar averaging effect will require 6 cycles measurement time if data from only one phase is used. The calculation of the rate of change of frequency from three phase data can also be combined in a single equation as follows.

$$\left(\frac{df}{dt}\right)_{av} = \frac{1}{3} \cdot \left(\left(\frac{df}{dt}\right)_{A} + \left(\frac{df}{dt}\right)_{B} + \left(\frac{df}{dt}\right)_{C}\right)$$

(4.9)

The high frequency counts of different phases are identified by subscripts A, B and C. Substituting for the rate of change of frequency of the individual phases from Equation 4.8, the following equation is obtained.

$$\left(\frac{df}{dt}\right)_{av} = \frac{fo^2}{3 pf_c \Delta t} \left( (N_{A1} + N_{B1} + N_{C1}) - (N_{A2} + N_{B2} + N_{C2}) \right)$$

(4.10)

#### 4.3.2 Second order approximation

The first order approximation techniques have been presented in Section 4.3.1. These approaches use only two terms of the Taylor series expansion of  $\frac{1}{f}$ . A second order approximation can be similarly obtained by using the first three terms of the Taylor series. Taylor series expansion of  $\frac{1}{f}$  in the neighborhood of  $f_0$  as already given in Equation 3.3 is

$$\frac{1}{f} = \frac{1}{f_0} - \frac{(f - f_0)}{f_0^2} + \frac{(f - f_0)^2}{f_0^3} - \cdots$$

(4.11)

Figure 4.1 Pulses recorded in different phases of a three phase system.

Considering only the first three terms and substituting  $f = \left| \frac{pf_c}{N} \right|$ on the left hand side of this expansion, the following equation is obtained.

$$\frac{N}{pf_{c}} = \frac{1}{f_{0}} - \frac{(f - f_{0})}{f_{0}^{2}} + \frac{(f - f_{0})^{2}}{f_{0}^{3}}$$

(4.12)

Differentiating both sides of this equation with respect to t, provides the following equation.

$$\frac{1}{pf_{c}} \frac{dN}{dt} = -\frac{df}{dt} \cdot \frac{1}{f_{c}^{2}} + \frac{2f}{f_{0}^{3}} \frac{df}{dt} - \frac{2f_{o}}{f_{0}^{3}} \frac{df}{dt}$$

(4.13)

Solving for  $\frac{df}{dt}$  from Equation 4.13, provides the following expression for the rate of change of frequency.

$$\frac{df}{dt} = \frac{f_0^3}{pf_c} \cdot \frac{dN/dt}{(2f-3f_0)}$$

(4.14)

Equation 4.15 is obtained by substituting  $\frac{dN}{dt}$  with  $\frac{(N_2 - N_1)}{\Delta t}$  in the above equation.  $\Delta t$  can be approximated as the measurement period at the base frequency,  $\frac{1}{f_0}$ .

$$\frac{df}{dt} = \frac{f_0^4}{pf_c} \cdot \frac{(N_2 - N_1)}{(2f - 3f_0)} \quad Hz/sec$$

(4.15)

This equation is not computationally acceptable because it involves a division of a variable by another variable.

Another possible approach is to use the Taylor series expansion of function  $f = \frac{pfc}{N}$  in the neighborhood of N<sub>0</sub>. This expansion can be written as follows.

$$f = \frac{pfc}{N_0} - \frac{pfc}{N_0^2} (N - N_0) + \frac{2pfc}{N_0^3} \frac{(N - N_0)^2}{2!} - \cdots$$

(4.16)

Considering the first three terms of this series and differentiating both sides with respect to time, Equation 4.17 is obtained.

$$\frac{df}{dt} = -\frac{3f_0^2}{pf_c} \cdot \frac{dN}{dt} + \frac{2f_0^3}{p^2f_c^2} \cdot N_2 \cdot \frac{dN}{dt}$$

(4.17)

Substituting  $\frac{dN}{dt}$  with  $\frac{N_2 - N_1}{\Delta t}$  in Equation 4.17, the following equation is obtained.

$$\frac{df}{dt} = -\frac{3f_0^2}{pf_c \cdot \Delta t} \cdot (N_2 - N_1) + \frac{2f_0^3}{p^2 \cdot f_c^2 \cdot \Delta t} \cdot N_2 \cdot (N_2 - N_1) \quad (4.18)$$

In Equation 4.18,  $\Delta t$  can be approximated as the time period of the base frequency,  $\frac{1}{fo} \cdot \frac{3f_o^2}{pf_c\Delta t}$  and  $\frac{2f_o^3}{p^2f_c^2\cdot\Delta t}$  are, therefore constants; p and  $f_c$  can be selected in such a manner that one of these terms is multiples of two. In this form, Equation 4.18 is simpler than Equation 4.15.

### 4.3.3 Curve fitting approach

The measurements of frequency are subject to variations due to the presence of noise. Frequency and rate of change of frequency measurements can, therefore, be improved by an averaging procedure. Consider that the frequency of a signal has been measured at four regular intervals as shown in Figure 4.2. Assuming that the frequency is changing at a uniform rate, it may be expressed as a function of time as follows.

$$f = a + bt$$

(4.19)

The values of the coefficients a and b can be obtained by using the least error squares approach. The coefficient a is the frequency and the slope b is the rate of change of frequency. If four measurements are used and the measurements are assumed to have been obtained at equal intervals of time, the frequency and the rate of change of frequency are given by