### An Integrated Circuit for ECG Processing

A Thesis

Submitted to the College of

Graduate Studies and Research

in Partial Fulfilment of the Requirements

for the Degree of

Master of Science

in the Department of Electrical Engineering

University of Saskatchewan

by

Kirby Goulet

Saskatoon, Saskatchewan

August, 1987

Copyright (C) 1987 Kirby Goulet

#### Copyright

The author has agreed that the University of Saskatchewan Library shall make this thesis freely available for inspection. The author also has agreed that permission for extensive copying of this thesis may be granted by Professor R.J. Bolton of the University of Saskatchewan College of Engineering or, in his absence, by the Head of the Department of Electrical Engineering or the Dean of the College of Engineering.

Requests for permission to copy this thesis in whole or in part should be addressed to:

Head of the Department of Electrical Engineering University of Saskatchewan Saskatoon, Saskatchewan S7N 0W0

#### Copyright

The author has agreed that the University of Saskatchewan Library shall make this thesis freely available for inspection. The author also has agreed that permission for extensive copying of this thesis may be granted by Professor R.J. Bolton of the University of Saskatchewan College of Engineering or, in his absence, by the Head of the Department of Electrical Engineering or the Dean of the College of Engineering.

Requests for permission to copy this thesis in whole or in part should be addressed to:

Head of the Department of Electrical Engineering University of Saskatchewan Saskatoon, Saskatchewan S7N 0W0

#### Abstract

#### UNIVERSITY of SASKATCHEWAN

Electrical Engineering Abstract 87A284

# An Integrated Circuit for ECG Processing

Student: Kirby Goulet

Supervisor: R.J. Bolton

M.Sc. Thesis Presented to the College of Graduate Studies

and Reasearch

August 1987

#### 'Abstract

This thesis presents the design of an IC for use in the analysis of electrocardiograms (ECG's). This IC was developed because the pattern recognition technique used in the analysis requires a relatively large amount of computation, and custom hardware designed specifically for these calculations is necessary to achieve the desired ECG analysis speed.

In this report, the morphology recognition algorithm, which is based upon the Bhattacharyya distance measure, is explained and then modified into a form suitable for implementation in an IC. The major components of the IC are identified as a square-root extractor, a multiplier, a register file, and a system controller. A circuit description and an IC layout is developed for each of these components. The circuits are developed using two circuit simulation computer programs, SPICE and RNL, whose accuracy is checked by comparing their simulation results to measurements taken from a fabricated circuit. The NETLIST description of the complete IC design is checked through RNL simulation.

The resulting design has a computational rate which is 10 to 25 times faster than a design based upon a general purpose microprocessor performing identical computations.

## Acknowledgements

The author wishes to thank Professor R.J.Bolton for his assistance in completing this work.

Fabrication of integrated circuits was made possible by Northern Telecom Electronics and the Canadian Microelectronics Corporation.

Financial assistance was provided by the Natural Science and Engineering Research Council, and their support is gratefully acknowledged.

# Table of Contents

|      |                                                                   | 1        |

|------|-------------------------------------------------------------------|----------|

| 1    | 1.1. Background to ECG Processing                                 | 1        |

| 1    | 1.2. Integrated Circuit Design Approaches                         | 3        |

|      | 1.2.1. Gate-array Design                                          | 4        |

|      | 1.2.2. Standard Cell IC Design                                    | 4        |

|      | 1.2.3. Full Custom Design                                         | 8        |

|      | 1.2.4. A Comparison of Three IC Design Approaches                 | 9        |

|      | 1.3. Advantages and Disadvantages of Custom IC Design             | 10       |

|      | 1.4. Application of IC Technology to Computer-aided ECG Analysis  | 11       |

|      | 1.5. Project Objective                                            | 12       |

|      | 1.6. Outline of Thesis                                            | 13       |

| 2. N | Morphology Recognition of ECG Waveforms                           | 15       |

| . 2  | 2.1. The ECG Waveform                                             | 15       |

|      | 2.2. The Automatic Interpretation of ECG waveforms                | 19       |

| 2    | 2.3. The Hilbert Transform method for computer-aided ECG analysis | 20       |

|      | 2.3.1. The ECG Analysis Computer System                           | 20       |

|      | 2.3.2. The Hilbert Transform                                      | 23       |

|      | 2.3.3. The Recognition Matrix                                     | 25       |

|      | 2.3.4. Computing the Similarity between Matrices                  | 31       |

| 2    | 2.4. Summary                                                      | 35       |

| 3. J | Integrated Circuit Design                                         | 36       |

| :    | 3.1. IC Design Procedure                                          | 36       |

| •    | 3.1.1. Hierarchical abstraction                                   | 38       |

|      | 3.1.2. System timing                                              | 39       |

|      | 3.1.3. Design for testability                                     | 41       |

| ;    | 3.2. Software for IC Design                                       | 42       |

|      | 3.2.1. Simulation software                                        | 42       |

|      | 3.2.1.1. ISPS                                                     | 43       |

|      | 3.2.1.2. DABL                                                     | 44<br>44 |

|      | 3.2.1.3. Logician Design Editor                                   | 48       |

|      | 3.2.1.4. NETLIST-PRESIM-RNL                                       | 49       |

|      | 3.2.1.5. SPICE                                                    | 49       |

|      | 3.2.1.6. SIMPSIN 3.2.2. Layout Software                           | 54       |

|      | 3.2.2. Layout Software 3.2.3. Layout Circuit Extractors           | 55       |

|      | 3.2.4. The University of Saskatchewan Design System               | 56       |

|            | 3.3. Summary                                                  | 57         |

|------------|---------------------------------------------------------------|------------|

| <b>4</b> . | The Integrated Circuit Implementation of the Morphology       | <b>62</b>  |

|            | Recognition Unit                                              |            |

|            | 4.1. Architecture of the ECG Processor                        | 63         |

|            | 4.1.1. The Similarity Measure Algorithm                       | 63         |

|            | 4.1.2. The ECG Processor Interface                            | 64         |

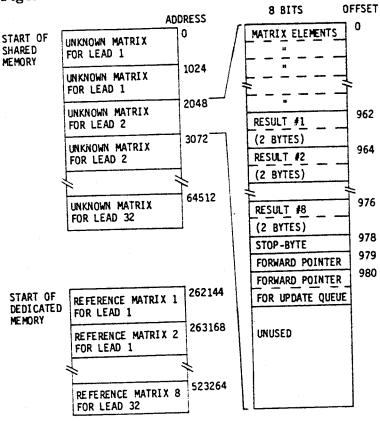

|            | 4.1.3. Data Structures                                        | 67         |

|            | 4.1.4. ECG Processor Timing                                   | 71         |

|            | 4.1.5. Summary of the ECG Processor Functions                 | 73         |

|            | 4.2. Function Blocks of the ECG Processor                     | 73         |

|            | 4.2.1. The Square-Root Extractor                              | 76         |

|            | 4.2.2. The Multiplier                                         | 83         |

|            | 4.2.2.1. The CSD Multiplier                                   | 83         |

|            | 4.2.2.2. The Pipelined Array Multiplier                       | 93         |

|            | 4.2.3. The Register File                                      | 96         |

|            | 4.2.4. The Update Adder                                       | 99         |

|            | 4.2.5. The Memory Address Unit                                | 101<br>104 |

|            | 4.2.6. The Control Unit                                       |            |

|            | 4.3. Support Hardware                                         | 109<br>114 |

|            | 4.4. Support Software                                         | 114        |

|            | 4.5. Test Patterns for the ECG Processor                      | 121        |

| _          | 4.6. Summary                                                  | 123        |

| <b>5</b> . | Circuit Design, Simulation, and Testing                       |            |

|            | 5.1. The Simulation Parameters                                | 124        |

|            | 5.1.1. The SPICE Simulation Parameters                        | 124        |

|            | 5.1.2. The RNL Simulation Parameters                          | 130        |

|            | 5.1.3. Simulation Results Versus Measured Values              | 134        |

|            | 5.2. Integrated Circuit Development                           | 138<br>138 |

|            | 5.2.1. The Library Cells                                      | 147        |

|            | 5.2.2. Special Purpose Cells                                  | 147        |

|            | 5.2.2.1. Static Memory Development                            | 150        |

|            | 5.2.2.2. PLA Circuit Development<br>5.2.2.3. Input Protection | 152        |

|            | 5.2.2.4. Output Pad Drivers                                   | 154        |

|            | 5.3. Test Results of Two Sub-circuits                         | 155        |

|            | 5.3.1. The 8-bit Accumulating Add/Subtract Unit               | 155        |

|            | 5.3.2. The 8-word Static RAM                                  | 159        |

|            | 5.4. Simulation Results for the ECG Processor                 | 161        |

|            | 5.5. The Expected Performance of the ECG Processor            | 163        |

|            | 5.6. Summary                                                  | 165        |

| 6          | Conclusion and Future Work                                    | 167        |

| υ.         | 6.1. Future Work                                              | 169        |

| ъ          |                                                               | 170        |

| К          | eferences                                                     | 200        |

| Appendix A. ECG Processor Circuit Diagram            | 174 |

|------------------------------------------------------|-----|

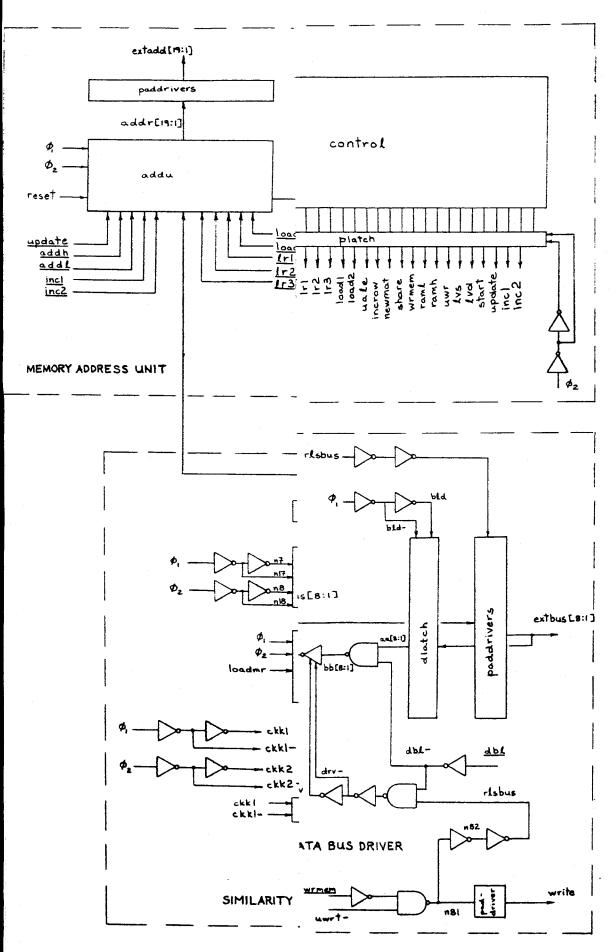

| A.1. Summary of the major circuit blocks             | 174 |

| A.2. Summary of the ECG Processor signals            | 176 |

| Appendix B. NETLIST Description of the ECG Processor | 181 |

| B.1. The NETLIST Circuit Description                 | 181 |

| B.2. Summary of the Directory Structure              | 206 |

# List of Figures

| Figure | 1-1:          | Floorplan of a gate array IC.                                     | 5         |

|--------|---------------|-------------------------------------------------------------------|-----------|

| Figure | 1-2:          | Layout of one gate array cell <sup>6</sup> .                      | 5         |

| Figure | 1-3:          | Two examples of a logic function created from a                   | 6         |

|        |               | gate array cell <sup>6</sup> .                                    |           |

| Figure | <b>1-4</b> :  | The economics of the different IC design                          | 10        |

|        |               | approaches <sup>10</sup> .                                        |           |

| Figure | 2-1:          | The electric circuit model of electrocardiography <sup>15</sup> . | 16        |

| Figure | <b>2-2</b> :  | Diagram of a normal ECG trace with labelled                       | 16        |

|        |               | $segments^{16}$ .                                                 |           |

| Figure | <b>2-3</b> :  | Examples of ECG traces <sup>17</sup> .                            | 18        |

| Figure | <b>2-4</b> :  | Block diagram of a clinical ECG analysis system <sup>5</sup> .    | 21        |

| Figure | <b>2-5</b> :  | Impulse response of the Hilbert Transformer.                      | 24        |

| Figure | <b>2-6</b> :  | Frequency response of a Hilbert Transformer.                      | 24        |

| Figure | 2-7:          | Generation of the Hilbert Transform representation.               | 26        |

| Figure | <b>2-</b> 8:  | An example of a recognition matrix.                               | 27        |

| Figure | <b>2-9</b> :  | A view of a recognition matrix as a histogram <sup>5</sup> .      | 27        |

| Figure | <b>2-10</b> : | The potential function used in this thesis.                       | 28        |

| Figure | 3-1:          | Levels of abstraction commonly used in IC design <sup>9</sup> .   | 38        |

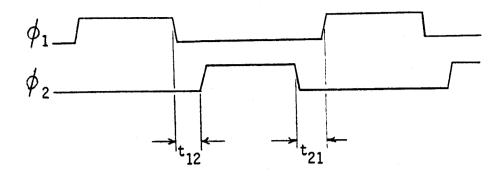

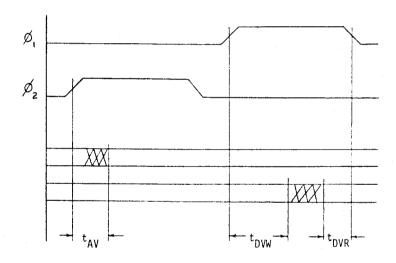

| Figure | <b>3-2</b> :  | A two-phase clock signal.                                         | 41        |

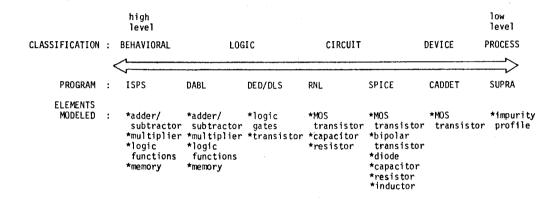

| Figure | <b>3-3</b> :  | Simulators of IC development ordered according to                 | 43        |

|        |               | the level of simulation.                                          |           |

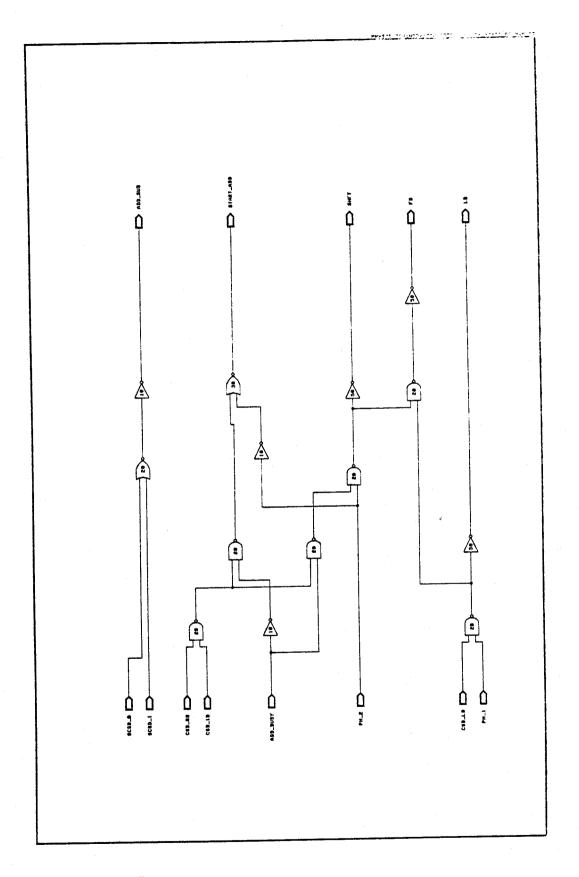

| Figure | <b>3-4</b> :  | DED schematic for an 8x8 bit signed multiplier.                   | 45        |

| Figure | <b>3-5</b> :  | The CONTROL unit schematic for the multiplier.                    | 46        |

| Figure | <b>3-6</b> :  | The multiplier simulation results.                                | 47        |

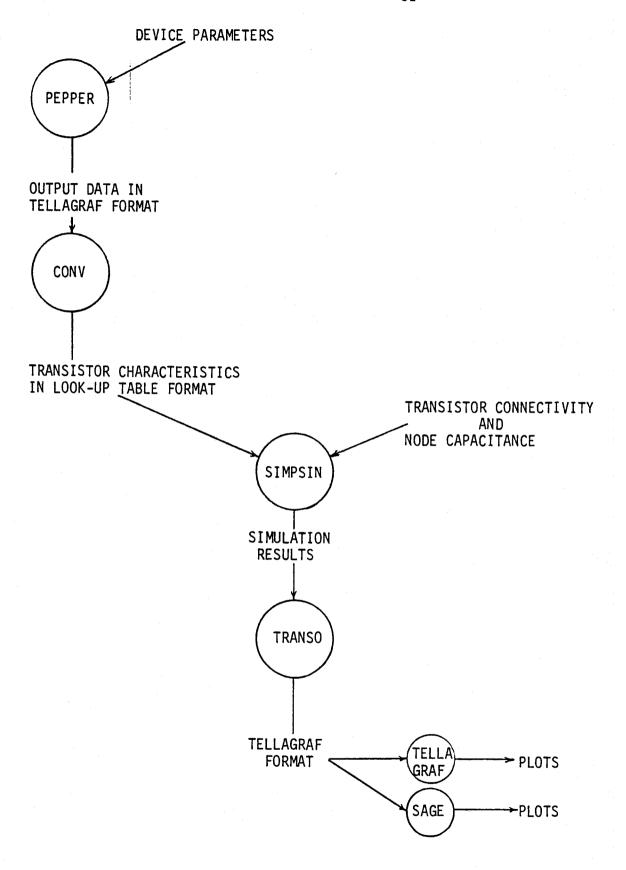

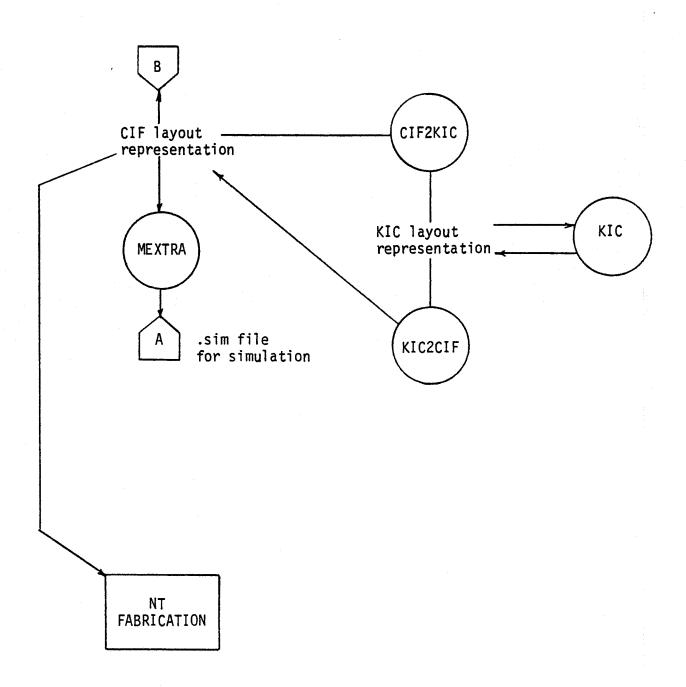

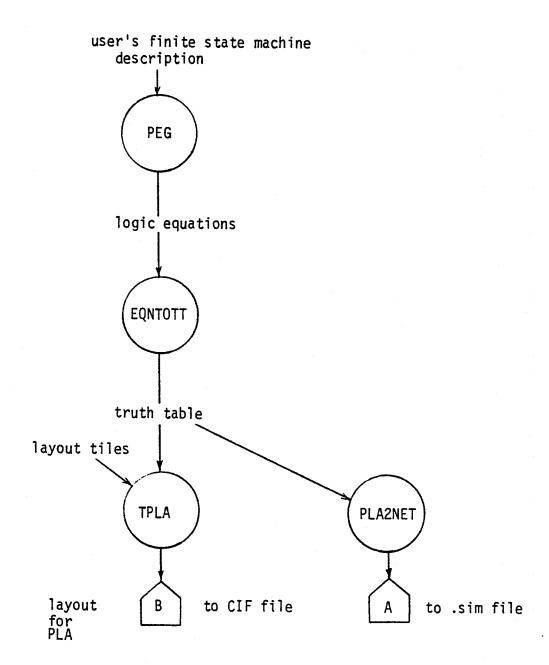

| Figure | 3-7:          | Programs for the SIMPSIN simulation package.                      | 51        |

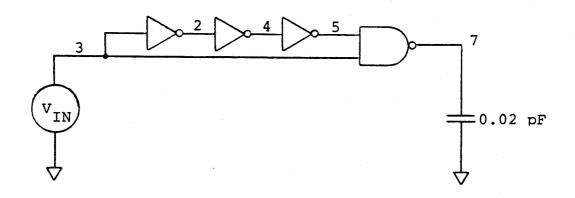

| Figure | <b>3-8</b> :  | Circuit for the SIMPSIN simulation test.                          | <b>52</b> |

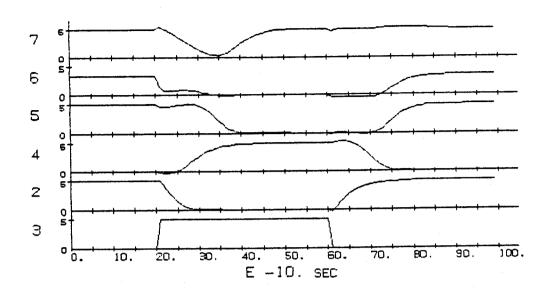

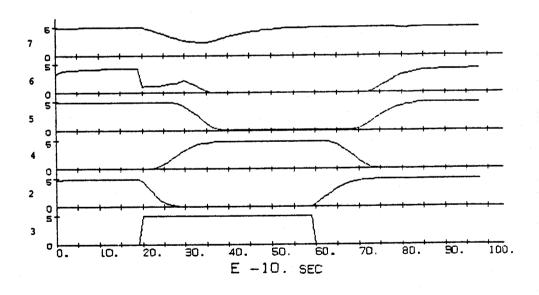

| Figure | <b>3-9</b> :  | SIMPSIN and SPICE simulation results.                             | 53        |

| Figure | <b>3-10</b> : | Programs used for the development of the ECG                      | 58        |

|        |               | processor.                                                        |           |

| Figure | <b>4-1</b> :  | The ECG Processor memory map.                                     | 68        |

| Figure | <b>4-2</b> :  | Memory read/write timing diagram.                                 | 72        |

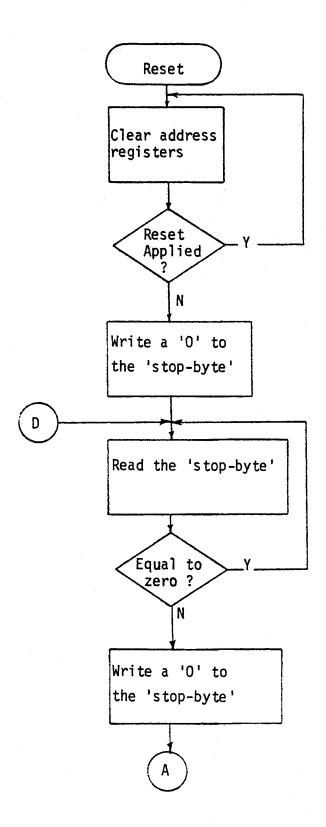

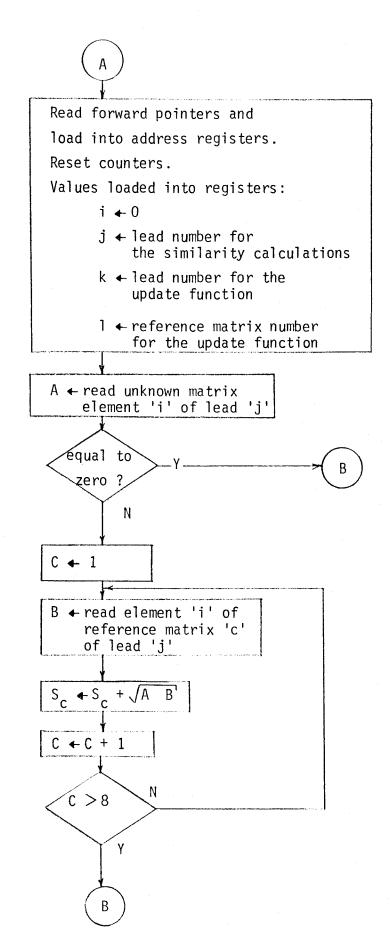

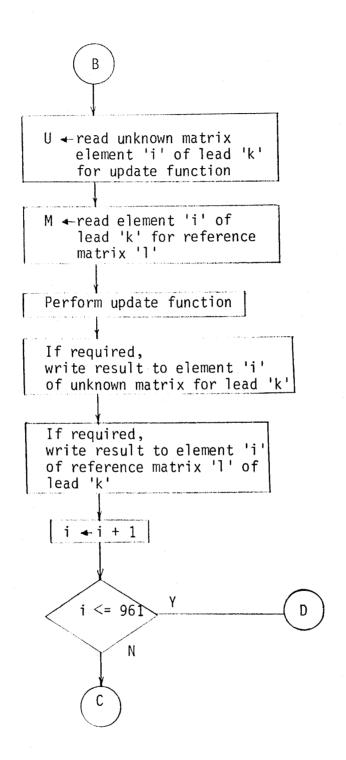

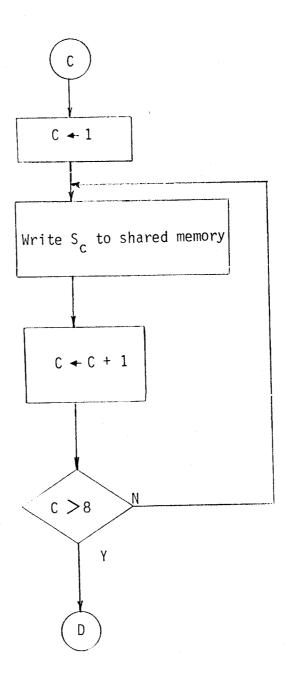

| Figure | <b>4-3</b> :  | Flowchart of the ECG Processor algorithm.                         | 74        |

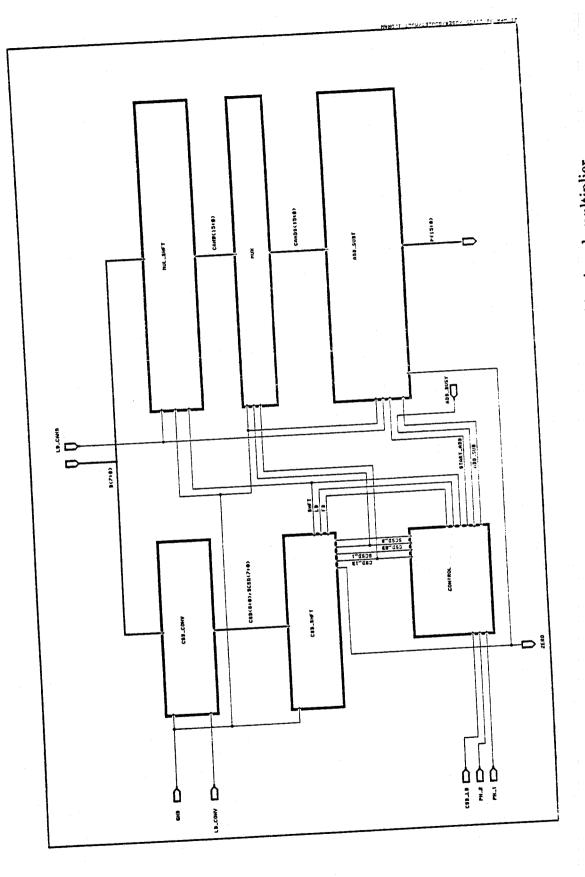

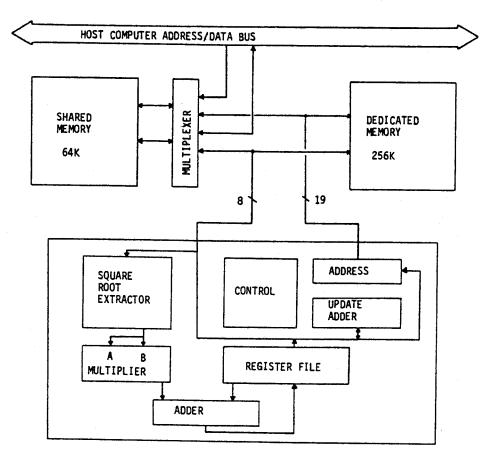

| Figure | <b>4-4</b> :  | The block diagram of the ECG Processor.                           | 75        |

| Figure |               | The square-root extraction algorithm.                             | 79        |

| Figure |               | A numerical example of square-root extraction.                    | 79        |

| Figure |               | A pipelined square-root extractor.                                | 81        |

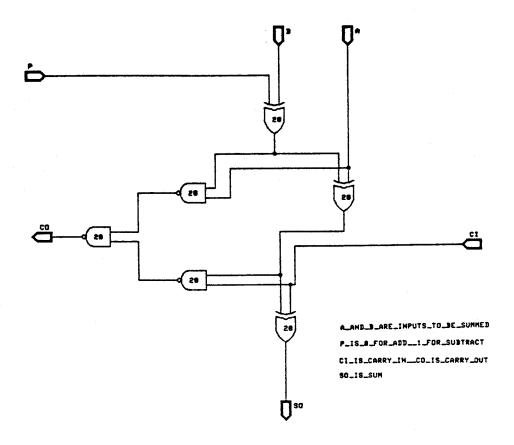

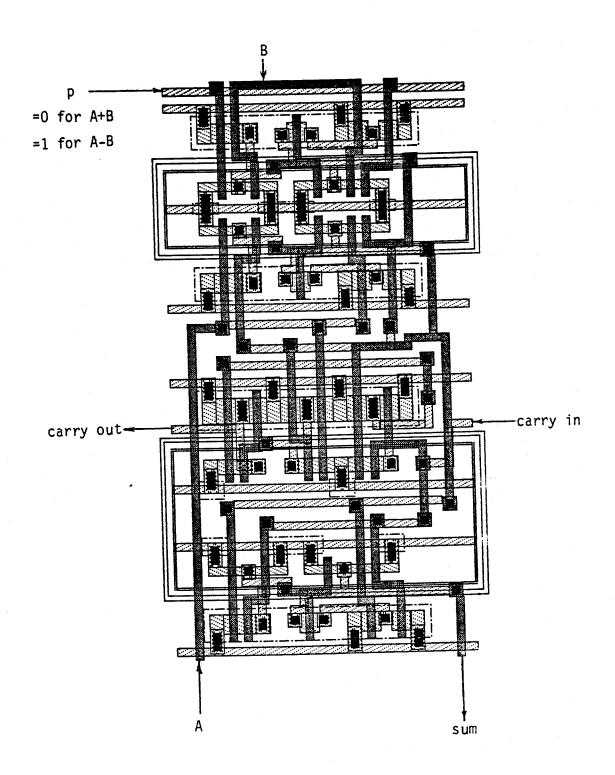

| Figure | <b>4-8</b> :  | The controlled add/subtract cell schematic.                       | 82        |

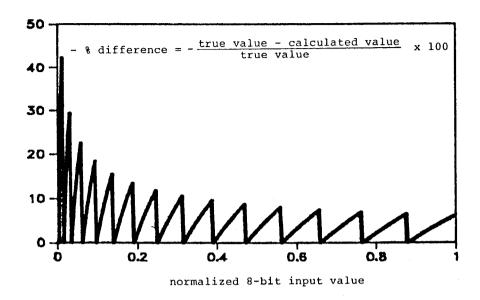

| Figure           | <b>4-9</b> :  | The error in a 4-bit square-root extractor.                      | 83  |

|------------------|---------------|------------------------------------------------------------------|-----|

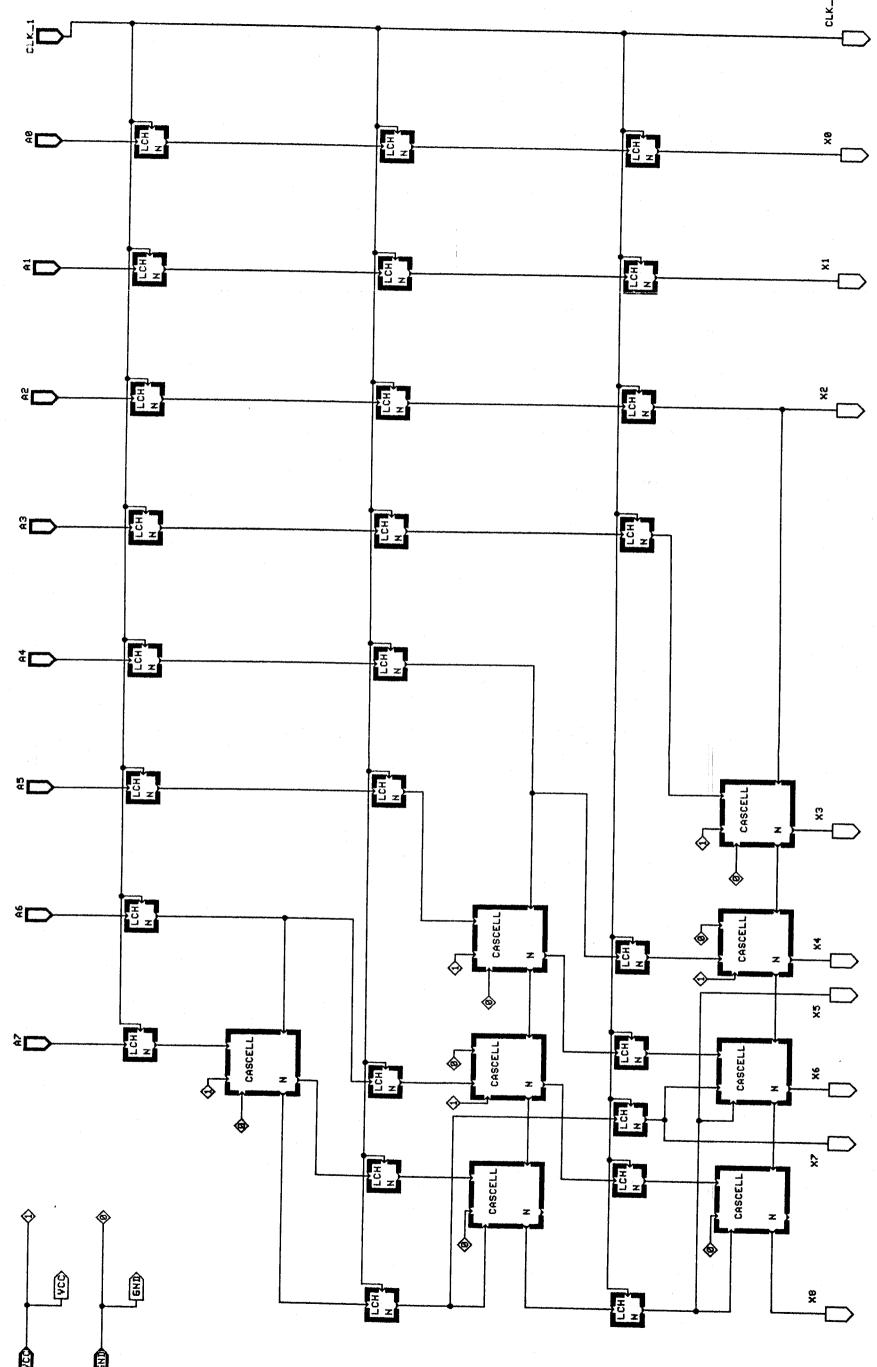

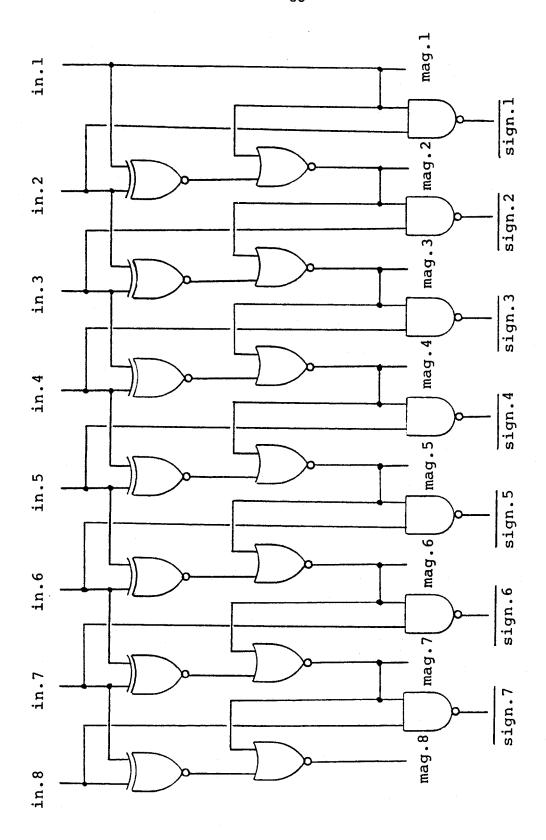

| Figure           |               | The schematic of the two's complement to CSD                     | 86  |

|                  |               | $ m code\ converter^{36}.$                                       |     |

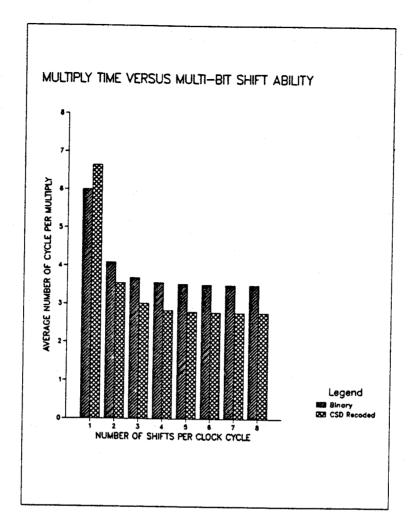

| Figure           | 4-11:         | Multiplication time versus multi-bit shift ability.              | 88  |

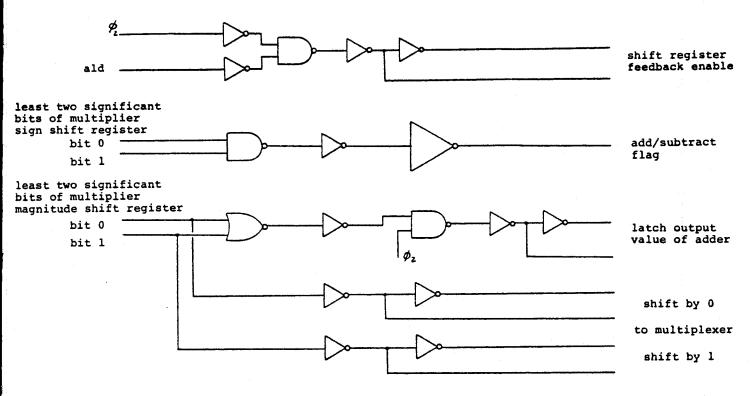

| Figure           | 4-12:         | The schematic diagram of the multiplier controller.              | 89  |

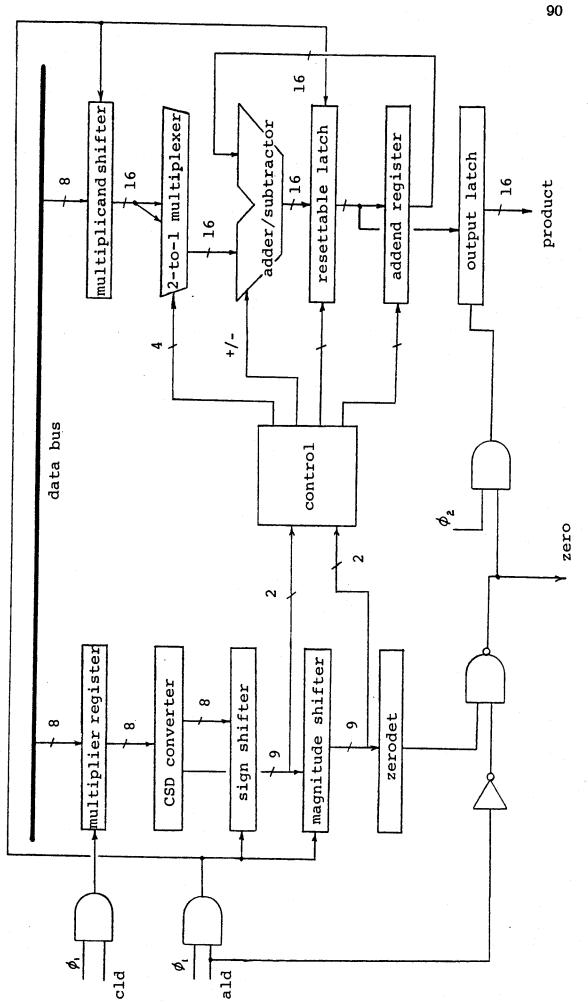

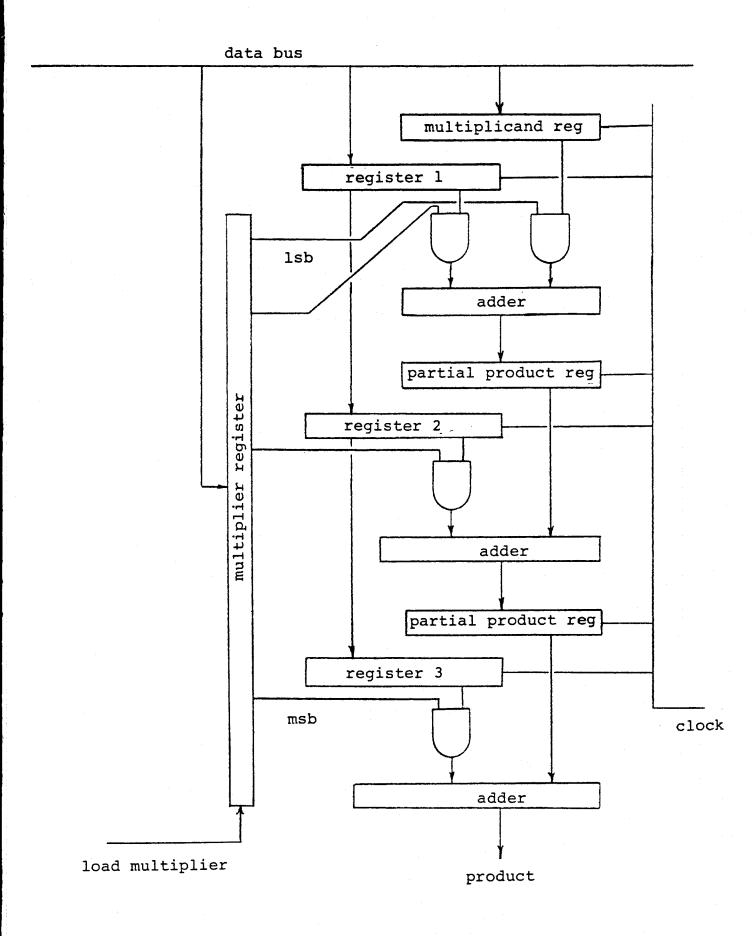

| Figure           | 4-13:         | The register diagram for the CSD multiplier.                     | 90  |

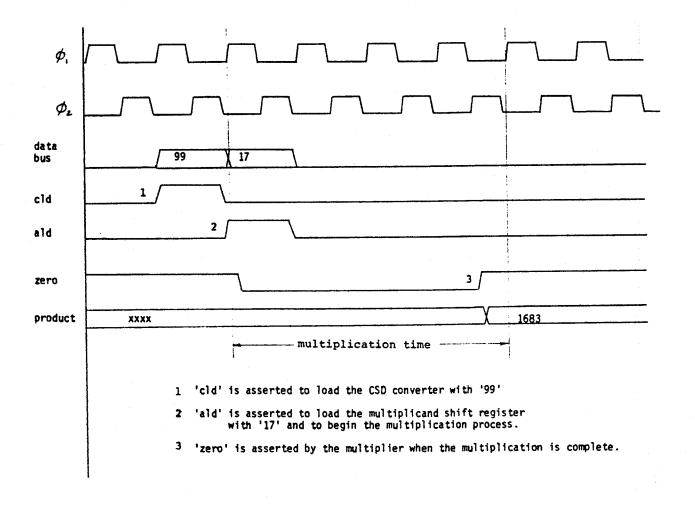

| Figure           | 4-14:         | The timing diagram for the CSD multiplier.                       | 91  |

| Figure           | <b>4-15</b> : | The register diagram for the array multiplier.                   | 94  |

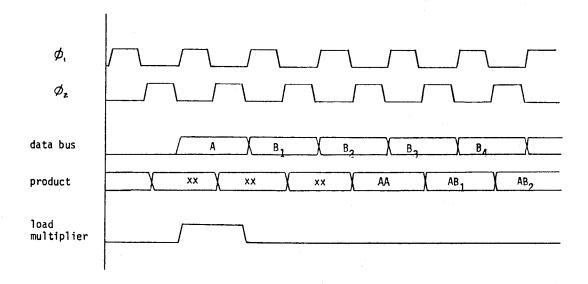

| Figure           | <b>4-16</b> : | The timing diagram for the array multiplier.                     | 95  |

| Figure           | 4-17:         | The register diagram for the register file.                      | 97  |

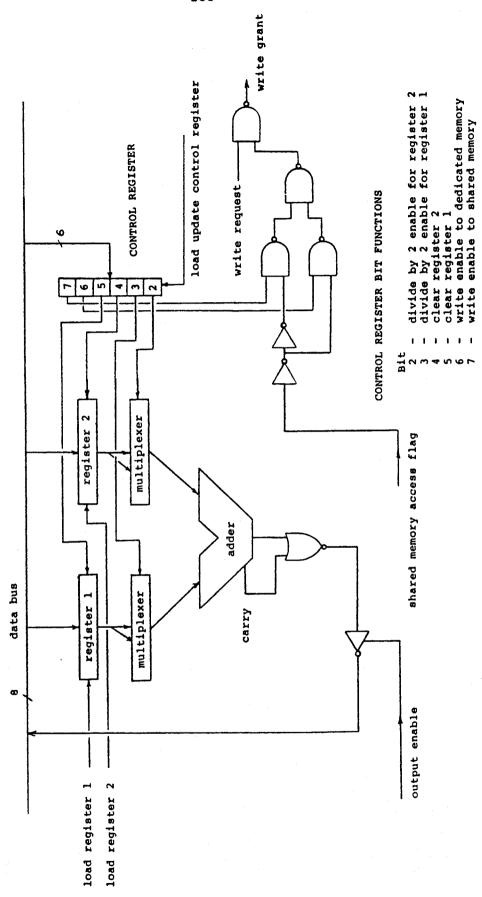

| Figure           | 4-18:         | The register diagram for the update adder unit.                  | 100 |

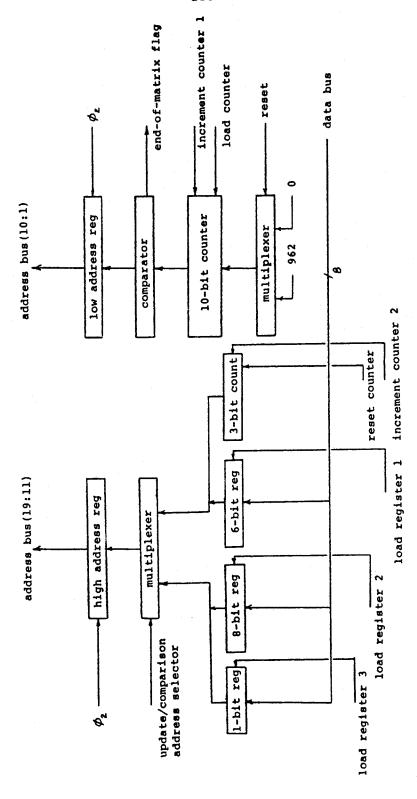

| Figure           | <b>4-19</b> : | The register diagram for the memory address unit.                | 103 |

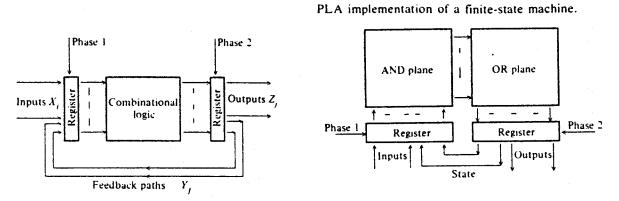

| Figure           | <b>4-2</b> 0: | The block diagram of a finite state machine 14.                  | 104 |

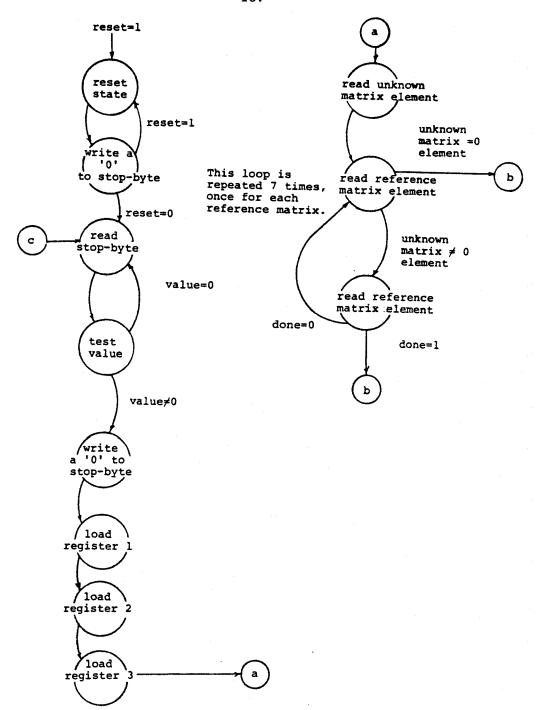

| Figure           |               | The controller state diagram.                                    | 107 |

| Figure           |               | A dual-port RAM circuit.                                         | 110 |

| Figure           |               | A CMOS arbiter circuit <sup>14</sup> .                           | 112 |

| Figure           |               | The arbiter circuit SPICE simulation results.                    | 113 |

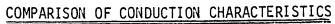

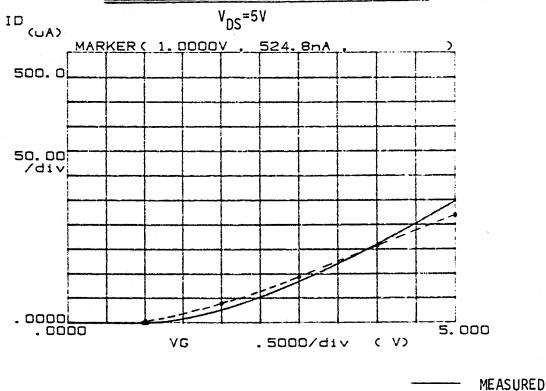

| Figure           | <b>5-1</b> :  | Comparison of simulated and measured DC                          | 129 |

|                  |               | characteristics.                                                 | 101 |

| Figure           | <b>5-2</b> :  | Voltage divider network for measuring static                     | 131 |

|                  |               | resistances.                                                     | 100 |

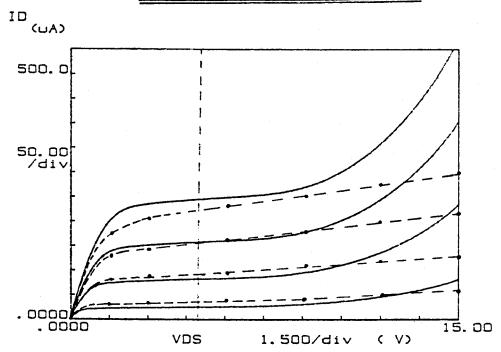

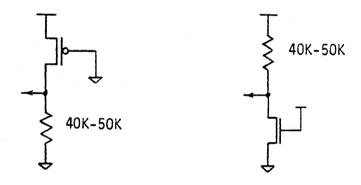

| Figure           |               | Circuits for measuring the dynamic resistances.                  | 132 |

| Figure           |               | The PRESIM configuration file.                                   | 133 |

| Figure           |               | Ring oscillator schematic.                                       | 135 |

| Figure           | <b>5-6</b> :  | Ring oscillator frequency versus power supply                    | 136 |

|                  |               | voltage.                                                         | 139 |

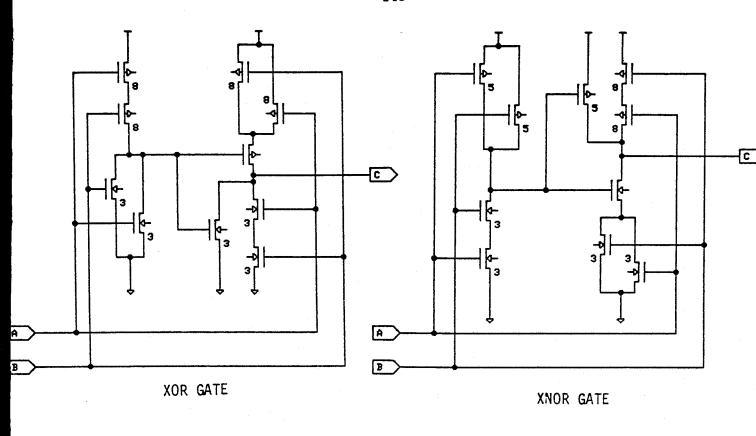

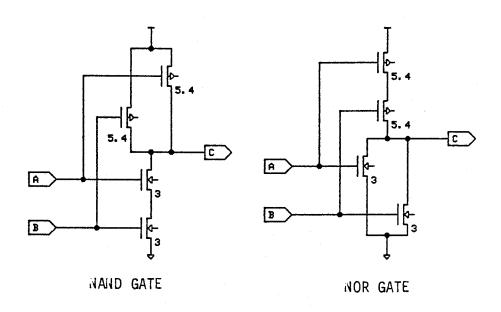

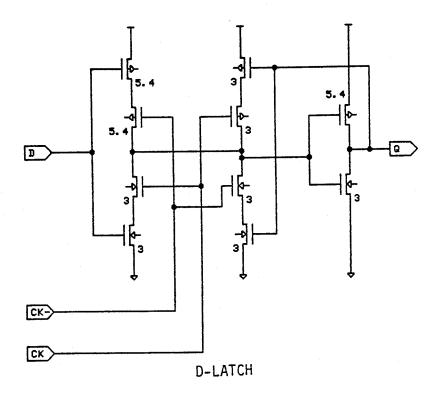

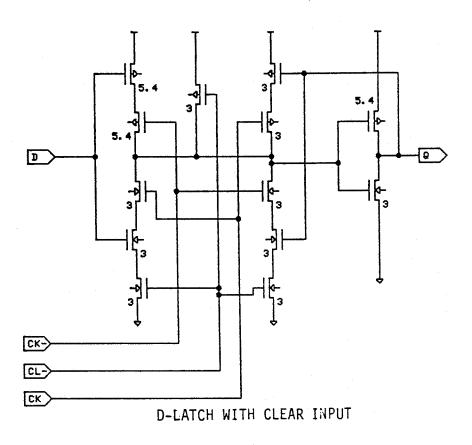

| Figure           |               | Schematic for inverter and tri-state inverter.                   | 140 |

| Figure           |               | Schematic for NAND, NOR, XOR, and XNOR gates.                    | 140 |

| Figure           |               | Schematic for D-latch and D-latch with Reset.                    | 142 |

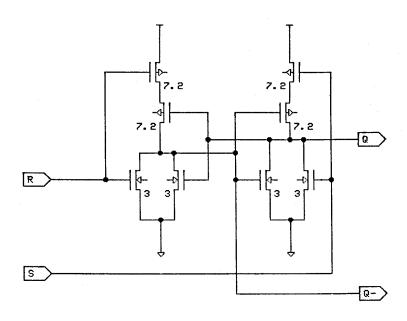

| Figure           |               | Schematic for SR latch.                                          | 143 |

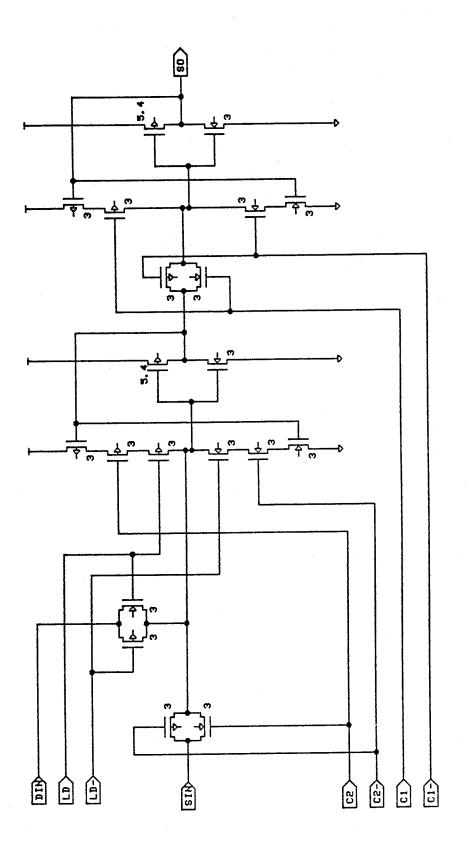

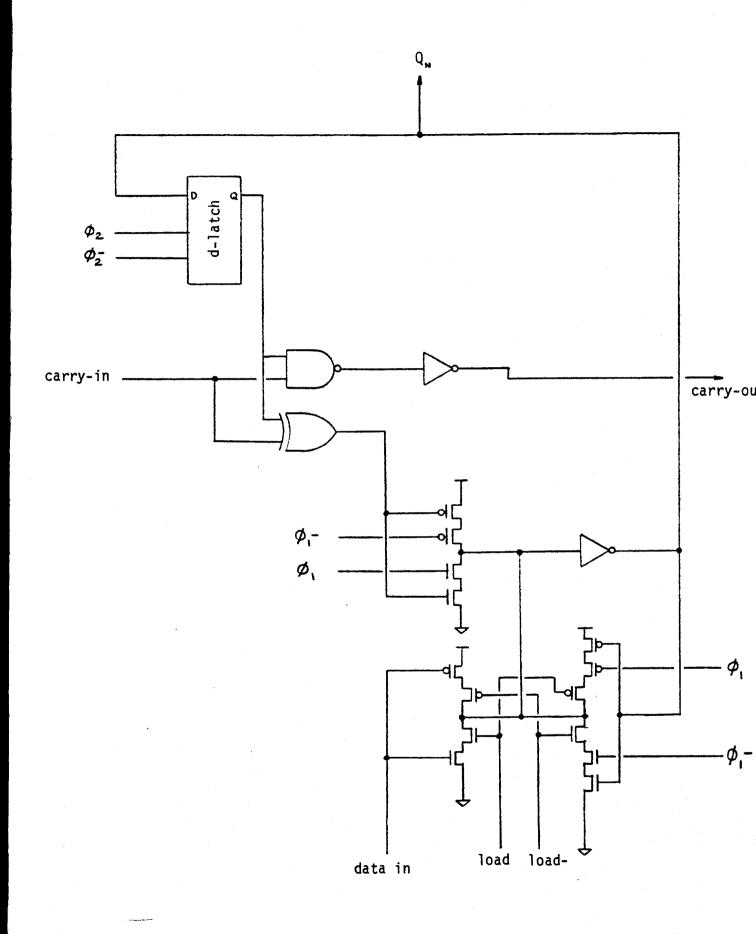

| Figure           |               | The shift register schematic.  Layout for the add/subtract cell. | 145 |

| Figure           |               | Schematic for the counter cell.                                  | 146 |

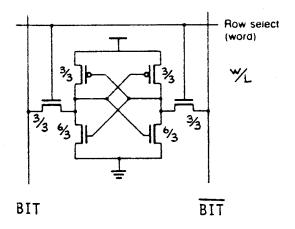

| Figure           |               | Schematic for the 6-transistor static RAM cell.                  | 147 |

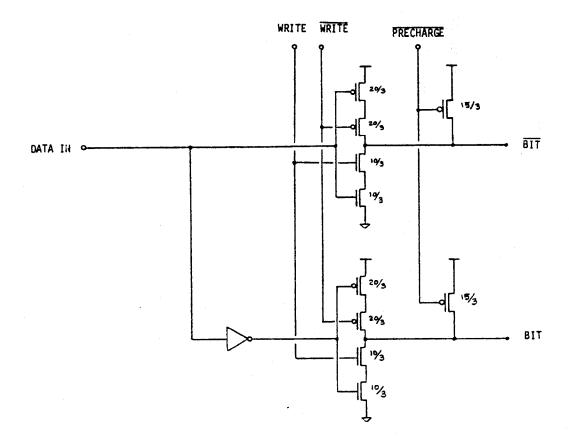

| Figure<br>Figure |               | Memory column driver circuit.                                    | 149 |

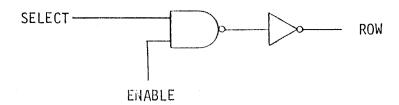

| Figure           |               | Memory row select circuit.                                       | 150 |

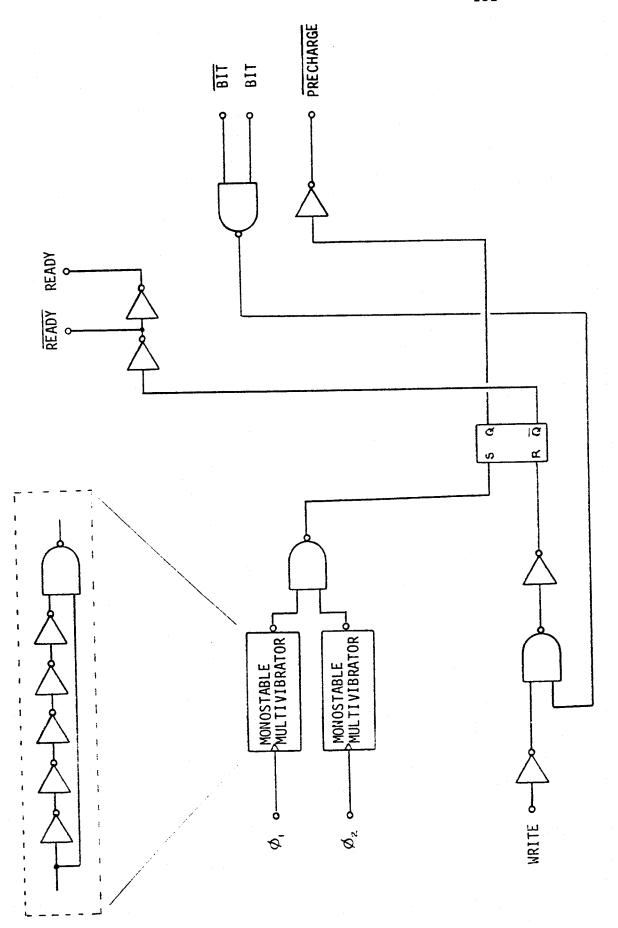

| Figure<br>Figure |               | Memory control circuit.                                          | 151 |

| 0                |               | PLA circuit model for simulation.                                | 153 |

| Figure<br>Figure |               | Input protection circuit.                                        | 154 |

| Figure           |               | Output pad driver.                                               | 154 |

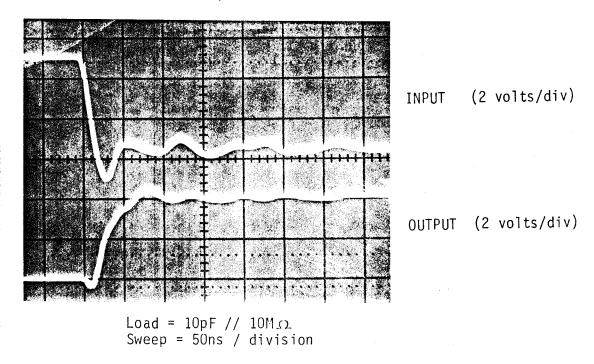

| Figure           |               | Pad driver output characteristics.                               | 156 |

| Figure           |               | Test circuit for the add/subtract IC.                            | 157 |

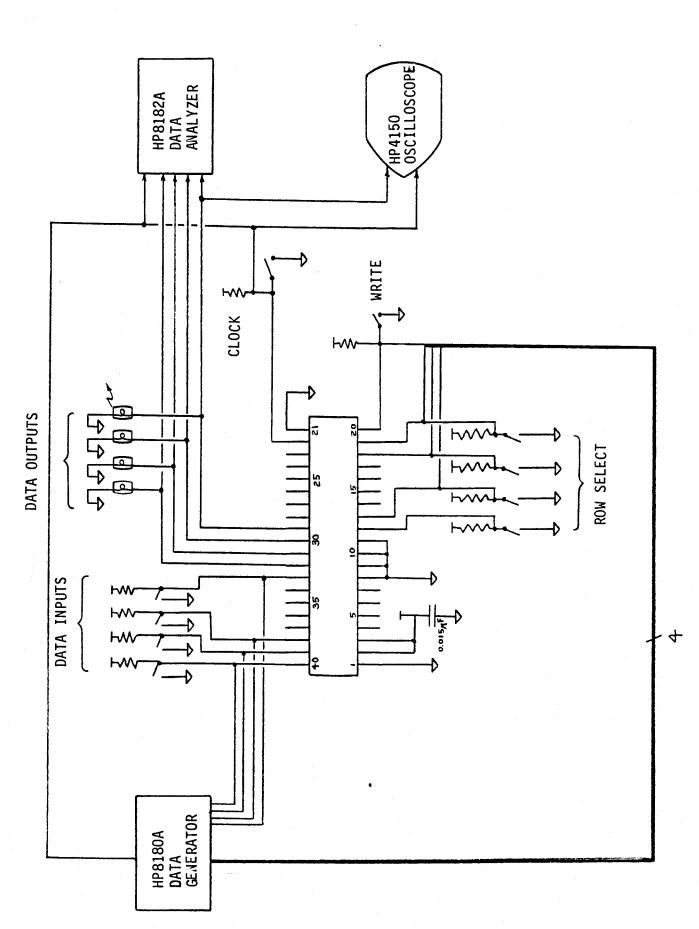

| Figure           |               | Test circuit for the static RAM.                                 | 160 |

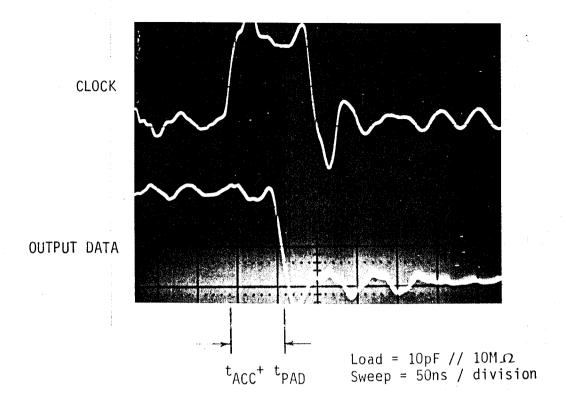

| Figure           |               | Memory read access time.                                         | 161 |

| Figure           |               | The ECG Processor block diagram.                                 | 175 |

| Liguic           | 17-1.         |                                                                  |     |

# List of Tables

| Table 1 | 1-1:         | A list of logic functions available to the gate array designer <sup>6</sup> .                    | 7   |

|---------|--------------|--------------------------------------------------------------------------------------------------|-----|

| Table 1 | 1-2:         | A comparison of the design time and efficiency for different IC design approaches <sup>9</sup> . | 9   |

| Table 3 | 3-1:         | Typical sources of chip fabrication failure for a $2\mu$ process <sup>22</sup> .                 | 37  |

| Table 4 | 4-1:         | Areas of the CSD multiplier components.                                                          | 92  |

| Table 4 | <b>4-2</b> : | Comparison of multiplier speed area characteristics.                                             | 93  |

| Table   |              | SPICE parameters for the CMOS3 process.                                                          | 124 |

| Table   |              | Sim2spice layer capacitance constants                                                            | 127 |

| Table   |              | Predicted and measured oscillator frequencies.                                                   | 136 |

| Table   |              | Node capacitances for various simulators.                                                        | 137 |

| Table   |              | The ECG performance versus microprocessors.                                                      | 165 |

| Table   |              | Major component areas and transistor counts.                                                     | 169 |

# Chapter 1 Introduction

This thesis investigates one application of integrated circuit (IC) technology to a problem in the computer-aided analysis of electrocardiograms (ECG's). The thesis objective is to design an IC which will improve the performance of a computer ECG analysis system.

#### 1.1. Background to ECG Processing

The purpose of computer analysis of ECG's is to assist medical personnel in the detection of heart disease. The computer does this by analyzing the shape of the ECG waveform; a normal healthy heart produces a regular and easily identifiable ECG waveform, but heart disease can cause either long term changes in the shape of the ECG waveform or occasional abnormal heartbeats which appear in the ECG as a wave shape notably different from the wave shape produced by a normal heartbeat.

commonly called heartbeats arrhythmias abnormal are These dysrhythmias, and in the 1960's, experience showed that in an unhealthy heart, a type of arrhythmia called ventricular depolarization could trigger the potentially fatal ventricular fibrillation (a state of the heart where the muscles of the ventricles twitch in a feeble and irregular manner which produces no useful pumping action) [1]. As a result, coronary care units were set up to monitor a patient's ECG for abnormal heartbeats, and if abnormal heartbeats occurred, drugs were administered to suppress them. These specialized coronary care units were successful in reducing the inhospital mortality of patients suffering myocardial infarctions (a blockage of a coronary artery) [2].

The key to the success of these coronary care units was the monitoring of the ECG signals for arrhythmias. To monitor the ECG signal, nurses or other trained personnel watched the ECG signals for abnormal heartbeats. However, this task was tedious and prone to errors, and computers were seen as a way of reducing these problems. Since the health of the patient could be affected by the performance of the computer ECG analysis system, it was important that the computer program accurately and reliably report ECG abnormalities. Developing a computer program which performed ECG analysis as well as a human proved to be difficult. As a demonstration of this, a comparison of the ability to diagnose heart disease through ECG's was made between a well-known ECG analysis program, the U.S. Veteran's Administration ECG analysis system, and hospital clinicians [3]. The results showed that clinicians did superior analysis of ECG's with a correct diagnosis of 59% versus the computer program's correct diagnosis rate of 50%.

These rates are low because there were many different heart diseases to consider. However, when classifying heart beats into only two classes, normal and abnormal, computer programs have been found to be more successful. In the detection of a class of arrhythmias called premature ventricular contractions (PVC's), computer programs have an accuracy of 95% [4], and while the use of automated ECG monitoring in the coronary care unit has not been proven to reduce patient mortality, there is agreement that automated arrhythmia analysis systems are more accurate than ECG monitoring by human surveillance [4, 1].

One disadvantage of the automated arrhythmia analysis programs, though, is the generation of false alarms. Due to electrical noise or movement of the patient connected to the ECG analysis system, the automated arrhythmia analysis system may indicate an otherwise normal heartbeat as an abnormal heartbeat. Such indications are called false positives. The false positive rate is usually one per hour per patient [4], which is not a problem unless several patients are being monitored, in which case, the high number of false alarms can demoralize the nursing staff [4].

R.J. Bolton has proposed an ECG analysis algorithm [5] which is not presently used in current ECG analysis programs. The proposed analysis algorithm is based upon the Hilbert Transform. This algorithm has been demonstrated to be useful in the detection of many ECG abnormalities, but one drawback of this method is the large number of computations required to perform the analysis. Over 7600 integer multiplications and 8600 square-root extractions must be performed every second to analyze ECG data from one lead, and if a microprocessor based ECG analysis system is to analyze several leads in real-time, hardware designed to speed up the ECG analysis calculations is required.

The hardware to do these calculations could be developed in a variety One way would be to add a second (and possibly a third) of ways. Another way would be to microprocessor to the ECG analysis system. provide functions currently which combine available IC's multiplication, data storage, and addition into a circuit that carries out the Yet another option which has recently become intended calculations. available to the electronics circuit designer would be to design an IC In order to learn about the specifically for morphology recognition. capabilities of IC technology in biomedical signal processing, the approach is taken in this thesis.

### 1.2. Integrated Circuit Design Approaches

The design of an IC involves the generation of a layout which is used to pattern the designed circuit onto the surface of a silicon chip. The generation of this layout may be performed by software or by human effort although ideally, the generation of the layout should be completely automatic in order to keep design costs to a minimum. However, automated IC layout usually produces IC layouts which are larger and slower than hand-crafted designs, and as a result of the trade-off between the lower design cost of automated design versus the efficient use of silicon by hand-crafted designs, three approaches to the generation of IC layout have evolved. They are gate-array designs, standard-cell designs, and full custom designs.

#### 1.2.1. Gate-array Design

Gate-array IC design begins with a chip where rows of transistors are fabricated except for the interconnecting metal layers. The customer customizes the chip for his application by designing the layout for the interconnecting metal layers.

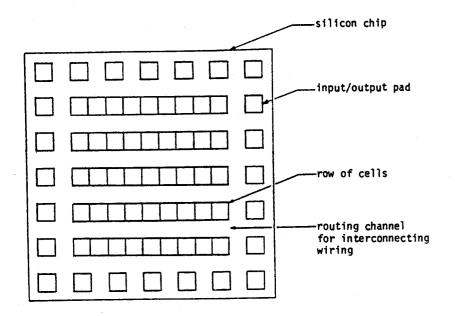

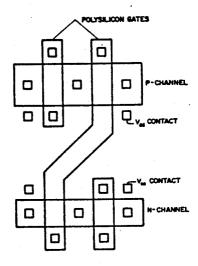

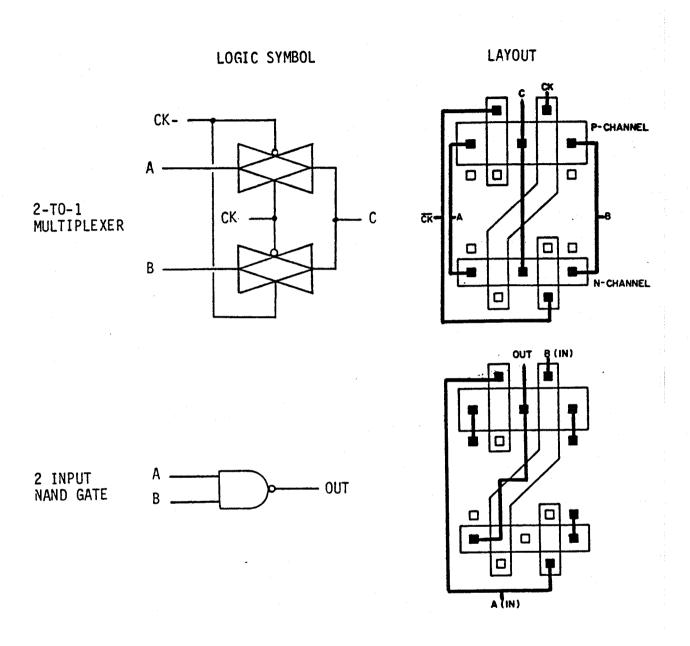

The transistors making up a gate-array IC are grouped into cells which in turn are placed in rows as depicted in Figure 1.1. A cell is made up of 4 to 16 transistors and the logic function which it performs is determined by the transistor inter-connections made when the metal layer is added. Figure 1.2 shows the layout for a simple 4 transistor cell, and Figure 1.3 shows how two functions can be made by changing the wiring of this basic four transistor cell.

To design a gate-array IC, the designer designs a logic circuit by specifying the inter-connection of logic functions either by schematic entry on a graphics terminal or by a text description called a net-list. Table 1.1 gives a list of logic functions typically available to the designer. From the designer's logic description, the generation of the layout of the interconnecting metal layers is almost completely automatic although it is possible that software cannot complete the inter-connections between the cells because the space available for cell inter-connection is fixed. Generally, though, if 80% of the cells are used, software can complete the layout without human intervention [6].

#### 1.2.2. Standard Cell IC Design

Standard cell IC design is based upon a function library. The function library contains a complete layout description (often referred to as a cell) for several logic functions. As with gate-array design, the designer specifies the circuit in terms of logic functions in schematic or net-list form, and software automatically generates the layout for the design. To generate the layout, the software selects the appropriate cells from the library, places them in a

Figure 1-1: Floorplan of a gate array IC.

Figure 1-2: Layout of one gate array cell [6].

Figure 1-3: Two examples of a logic function created from a gate array cell [6].

NAND. Triple 2-input NAND, Dual 2-input plus complement NAND. **Dual 3-input** NAND, Triple 3-input plus complement Triple 4-input NAND. NAND. 5-input NOR. Triple2-input Dual 2-input plus complement NOR, NOR, Dual 3-input NOR. Triple 3-input plus complement NOR, Triple 4-input NOR. 5-input XOR, 2-input AND-NOR, 2-2 with complement OR-NAND, 2-2 with complement Latch, 2-input NAND R-S with 2-I NAND Latch, 2-input NOR R-S with 2-I NOR D-flip-flop D-flip-flop with set & reset Invertor, Quad Buffer, Clock, triple Buffer, Dual tristate inverting Buffer. Tristate non-inverting MUX, 2-I

Table 1-1: A list of logic functions available to the gate array designer [6].

manner which minimizes layout area while keeping the routing problem as simple as possible, and then generates the interconnecting wiring to complete the layout of the chip. Unlike gate-array design where only the metal layer layouts are made by the customer, in standard cell design, the layout for all layers is specified by the customer. This makes initial production costs more expensive for standard cell design. However, standard cell design produces smaller designs than gate-array because unneeded functions are not included in the design. Performance is also better than gate-array designs because the layout for each function is optimized for that particular function.

#### 1.2.3. Full Custom Design

The most labour intensive IC design method is the full custom design; here, the designer can specify the size and placement of every transistor by using an interactive colour graphics program to draw the layout.

Even though the designer has the ability to layout every transistor, this does not mean that the full custom layout must be completely generated by hand. Because of the cost of human labour, attempts are made to automate as much layout generation as possible. For example, the program TPLA [7] was used for this IC design to produce the layout for a programmable logic array.

The ideal layout generator would be a silicon compiler. A silicon compiler produces layout from a high-level description that allows the user to specify the IC function in terms of operations like multiplication and addition while hiding circuit the timing constraints and electrical circuit One example of a silicon compiler is the FIRST silicon characteristics. compiler [8]. FIRST provides the designer with primitive functions such as MULTIPLY, DELAY, and MULTIPLEX. Once the designer describes the IC function in terms of these primitives, FIRST develops the layout for the primitives using composition procedures and a cell library, and then combines these primitive layouts with an algorithm which tries to minimize the overall layout area. After the primitive modules have been placed, routing algorithms complete the inter-connections.

Because the full custom design approach has not yet been completely automated and because the automated design tools which have been developed are not yet refined enough to generate layout as well as humans, the full custom design still requires a large amount of manual design. As a result of this large initial design effort, full custom designs have the highest start-up costs among the three design approaches presented.

#### 1.2.4. A Comparison of Three IC Design Approaches

Based upon an actual IC design, a general comparison of the layout area and design times of each of these three design approaches is given in Table 1.2.

|                |                          | Gate Array             | Standard Cell            | Hand-crafted<br>Full custom |

|----------------|--------------------------|------------------------|--------------------------|-----------------------------|

|                | Layout Area              | 100%                   | 75%                      | 40%                         |

| Design<br>Time | 2200 gates<br>6000 gates | 2.5 months<br>3 months | 4.0 months<br>4.5 months | 13.0 months<br>17.5 months  |

Table 1-2: A comparison of the design time and efficiency for different IC design approaches [9].

As expected, the gate-array design approach required the least design effort, but the resulting chip area consumes over two times the area of a hand-crafted design.

The true cost of an IC chip is [10]:

$$\frac{\text{COST}}{\text{IC}} = \frac{\text{development cost}}{\text{number of IC's}} + \text{unit production cost} + \text{unit test and packaging cost}$$

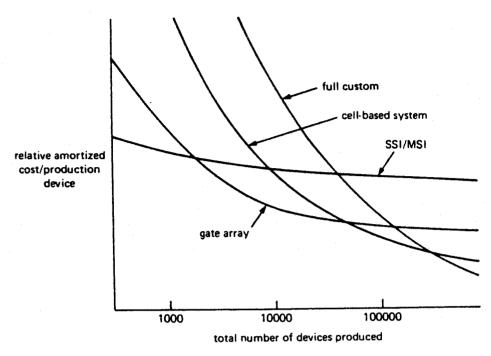

Therefore selection of the design approach depends on the volume of production as well as development time and performance requirements. The economics of the three different approaches to IC design, gate-array, standard cell, and full custom, are compared to a design based on standard IC's in Figure 1.4.

The approach selected for this thesis is the full custom design approach. At the time this project was initiated, this approach was the most well developed.

The positions of the abscissa scale points are the subject of constant debate. Those shown above are averaged from the literature.

Figure 1-4: The economics of the different IC design approaches [10].

## 1.3. Advantages and Disadvantages of Custom IC Design

Implementing a function in a custom designed IC has advantages and disadvantages over an implementation using standard off-the-shelf parts. One major advantage of a custom IC design is a reduced part count of the final product. Fewer parts means circuit assembly cost is reduced, the final product is more compact, and less power is consumed. Increased reliability is another reported advantage of custom IC design. Reference [11] reports that large scale IC's have a failure rate one seventh the failure rate of an equivalent number of circuits made from small scale IC's. On the other hand, one disadvantage of custom IC design is that once fabricated, changes

to the circuit are expensive and are not done except during the development stage where microsurgery techniques like cutting the metal layer wires with a trace cutting probe and a microscope can be used. This contrasts sharply with a design based on a microprocessor where software modifications are possible at any time.

# 1.4. Application of IC Technology to Computer-aided ECG Analysis

As mentioned earlier, ECG processing requires a large amount of This computation is highly repetitive; a few functions like square-root, multiplication, and addition are repeated 961 times for each two ECG patterns being compared. This computation can be performed using standard parts such as microprocessors, but such devices are general purpose machines and have a certain amount of overhead in terms of execution speed and hardware. One solution to this problem is to take the approach taken by many special purpose IC's such as direct memory access controllers, math co-processors, and input/output processors whose purpose is to off-load time consuming chores from the central processing unit. The proposed IC design has a similar purpose in that it would relieve the central processing unit of the computationally expensive part of ECG analysis. The proposed IC design would offer a significantly faster (in terms of number of ECG patterns analyzed per unit time) and smaller (as measured by circuit board area) product than one based on a general-purpose microprocessor. An application specific IC can offer these advantages because:

• The function to be performed is built into hardware. There is no need to fetch and decode instructions.

€----

£ ....

- The circuit can be designed to take advantage of concurrency in an algorithm. For example, one part of a circuit may be taking the square-root of a number, while another part is simultaneously doing a multiplication.

- IC packaging can occupy several times the area of the IC chip. By combining several standard parts into one IC, the area taken

by IC packaging is reduced. As well, the interconnecting wiring on a circuit board is scaled down when it is included on the IC.

#### 1.5. Project Objective

The objective of this thesis is to design an IC which performs the morphology recognition calculations in ECG waveform analysis. The algorithm for this morphology recognition has already been developed and tested in the form of a computer program. The requirements for this IC design are:

- Perform the morphology recognition in a manner described in [5]. This algorithm has already been tested; significant changes should be avoided otherwise further testing of the algorithm might be necessary.

- The ability to process several ECG waveforms (heart beats) in real time. No specific figures are given here because initially the capability of IC technology for this application was not well known. Instead, once the capability of the ECG processor is known, it will be compared to other methods of computing morphology recognition.

The design of this integrated circuit, called the <u>ECG processor</u>, involves the following steps:

Step 1) Learn the use of software tools necessary for IC design. The design of an IC is done almost entirely using computer software. NETLIST [12], RNL [12], and MAX [13] are a few of the computer programs used to design an IC. NETLIST is used to enter the circuit design at the transistor level while RNL is used to simulate the operation of the designed circuit. MAX lets the designer create the layout used to manufacture the IC. The layout produced by the designer using MAX is converted to CIF [14] code, and the CIF code is sent to the fabrication facility where it is used to make the IC.

Step 2) Develop the behavioural specifications of the IC. Behavioural specifications describe how the IC functions. The specifications include defining what outputs will appear for a given set of inputs, restrictions on

the timing of the input signals, and expected timing of the output signals. There are no formal rules for generating behaviour specifications, therefore it is possible to make specifications which cannot be realized due to limitations of the IC technology. Generating behavioural specifications involves some feedback from the following design step either in the form of the designer's experience, or in the form of modifications to the specifications as the design progresses.

Step 3) Design of the logic which performs the functions defined in the previous step. The design of the logic circuit usually involves the 'divide and conquer' approach where the circuit to be designed is divided into subcircuits which are either previously designed or can be designed with little effort.

Step 4) Develop the layout which is the actual physical plan used to fabricate the IC. The transistors and their inter-connections have been defined in the previous step, the designer must now draw the circuit in the form of the layout.

Step 5) Test the IC to verify its operation. For this project, the completed IC design is not tested, but two sub-circuits which were part of this design are tested. To test the IC's, a data generator is used to supply a set of user defined digital inputs to the IC, and the response to the applied inputs is recorded by a logic analyzer. The recorded data are then compared to the expected set of outputs.

#### 1.6. Outline of Thesis

This thesis is divided into six chapters. Aside from this introductory chapter, a brief overview of each of these chapters is given below.

Chapter 2 introduces the terminology of ECG analysis systems and provides the background information regarding the ECG analysis algorithm for which this IC is being developed.

Chapter 3 presents basic information useful for understanding the design and operation of an IC. It covers the procedure for designing large scale IC's as well as discussing the computer programs used for IC development.

Chapter 4 presents the development of the IC for the application in the ECG analysis system discussed in Chapter 2. It describes the flow of data in and out of the IC and the operations the IC performs upon this data. This chapter also provides a description of how the IC would be used as part of an ECG analysis system.

Chapter 5 covers the design of the logic and electrical circuits necessary to perform the functions presented in Chapter 4. It also includes the test results of two fabricated sub-circuits, a discussion of the simulation of the complete IC design, and a comparison of the proposed IC design's performance to a general purpose microprocessor.

The final chapter concludes the thesis and summarizes the results of the thesis work.

## Chapter 2

# Morphology Recognition of ECG Waveforms

This chapter introduces the reader to the topic of ECG analysis. It provides an explanation for the operation of a computer ECG analysis system as well as a description of the ECG analysis algorithm for which the proposed IC design is being developed.

The first section of this chapter discusses the origin of the ECG signal and provides a few ECG waveform examples. The second section discusses the general nature of computer ECG analysis, and the third section describes the ECG analysis algorithm which is to be implemented on a custom IC design.

#### 2.1. The ECG Waveform

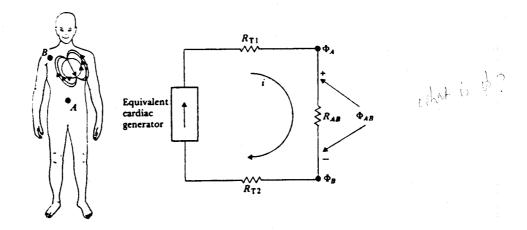

The electrocardiogram (ECG) is a recording of the electrical signals produced by the beating of the heart. Because muscle contraction is an electrochemical process, the contractions of large muscles like the heart induce small ionic currents throughout the body which can be detected by measuring the voltage between two electrodes placed on the skin of a patient. The simple electric circuit model in Figure 2.1 is an illustration of this process where the heart is considered a current source, and the voltage measured with the electrodes is generated by current flowing through the resistance that exists between two points on the body surface. When plotted along a time axis, this voltage traces a distinctive shape which provides useful information on how the heart is functioning.

Figure 2-1: The electric circuit model of electrocardiography [15].

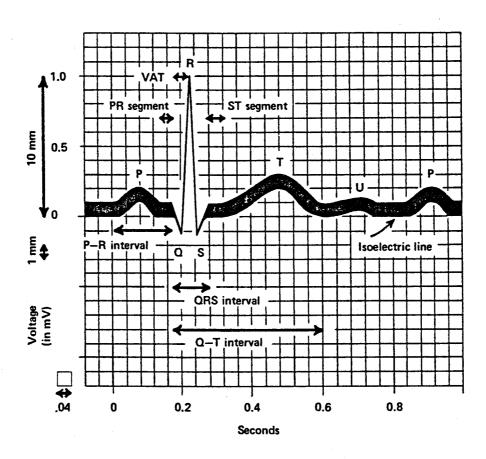

Figure 2-2: Diagram of a normal ECG trace with labelled segments [16].

The wave shape of an ECG signal is due to the fact that all heart muscle cells do not contract simultaneously; the contraction begins at one point on the heart, and through a complex network of conductive tissue, the muscle cells are stimulated and contract in a pre-determined order to produce the characteristic ECG waveform shown in Figure 2.2. This figure also shows the labels given by convention to the various segments of a normal ECG waveform. The P-wave corresponds to the contraction of the atria to pump the blood into the ventricles, and following the P-wave by about 0.07 seconds to allow blood to flow into the ventricles, the ventricle muscles contract to produce the highly visible QRS waveform. The repolarization of the heart muscles in preparation for the next beat causes the T wave.

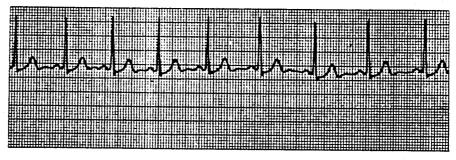

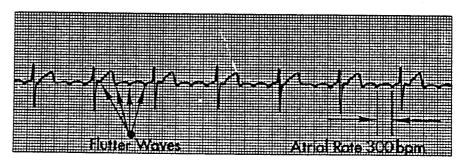

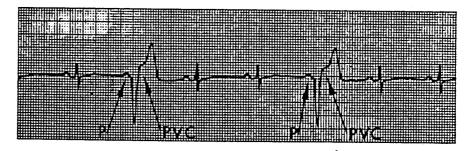

Deviations from the normal order of contraction will show up in the ECG trace as a waveform different from a normal waveform. Some examples of these abnormal heartbeats or arrhythmias are given in Figure 2.3. The atrial flutter in Figure 2.3b is the rapid beating of the atria (typically 300 beats per minute) while the ventricles continue to contract in an almost normal manner at a rate one half to one quarter of the atrial contraction rate. The premature ventricular contraction (commonly called a PVC) in Figure 2.3c is a common arrhythmia which even occasionally occurs in an undiseased heart. However, in a patient with heart disease, PVC's may be a warning sign of serious heart problems. Figure 2.3d is an example of ventricular fibrillation and is fatal if attempts to restore normal heart rhythm are not made immediately. These three examples are only a part of a list of several classes of arrhythmias. Besides the obvious shape or morphology which characterizes some arrhythmias, diagnosis of heart disease by ECG also includes measurements on the time delay between the P and R waves (the P-R interval), the height of the various waves, the duration of the QRS wave, the duration of the RS-T wave (the ST interval) and many other characteristics of the ECG waveform. Experienced physicians use this information from the ECG signal along with other patient data to determine the health of the heart.

a) ECG of normal sinus rhythm

b) ECG trace of atrial flutter

c) ECG trace of a PVC

d) ECG trace of ventricular fibrillation

Figure 2-3: Examples of ECG traces [17].

### 2.2. The Automatic Interpretation of ECG waveforms

The analysis of arrhythmias is based upon the observation that arrhythmias may occur frequently or rarely, but certain types of arrhythmias will give approximately the same ECG wave shape from one occurrence to the next. It is this property that ECG morphology recognition programs can take advantage of because once an abnormality is recorded, its next occurrence can be detected almost immediately by maintaining a list of the various waveforms which have occurred in an ECG recording.

One point, though, should be made about the repeatability of ECG waveforms. Gradual changes in the morphology of a normal QRS may occur due to changes in the patient's body position and changes in skin-electrode contact over time. These changes have to be accounted for by continuously updating the reference patterns being used in morphology recognition [18].

The first step in the analysis of ECG's is the detection of a heartbeat. This means locating the QRS waveform using methods such as a search for one or more slopes in the waveform which exceed certain timing and voltage thresholds [4].

Once a QRS waveform has been located, the waveform for that heartbeat must be characterized in a way that allows the separation of normal heartbeats from abnormal heartbeats and possibly the identification of the type of abnormal heartbeat. Two common techniques used to identify the ECG waveform are correlation methods and feature extraction methods. Feature extraction methods are based upon the measurement of certain properties of the ECG waveform such as the QRS duration, the QRS height, and the area under the QRS wave [4]. Correlation techniques, on the other hand, make a direct comparison of an unknown waveform with several different known waveforms called templates.

After the ECG waveform has been characterized, some procedure or set

of decision rules must be followed to obtain a classification of the unknown waveform and the results reported to medical personnel. The results are reported in a manner dependent upon the purpose of the ECG analysis system. For example, diagnosis programs may indicate several diagnoses and provide a probability for each diagnosis as does the U.S. Veteran's Administration ECG analysis system while a monitoring system would provide an alarm, an indication of the rate of occurrence of PVC's, and tracings of the waveforms which caused the alarms.

# 2.3. The Hilbert Transform method for computer-aided ECG analysis

This section introduces the Hilbert transform method for computer ECG analysis. First, an outline of the proposed ECG analysis system is given in the form of a block diagram. This shows which part of the ECG analysis algorithm is to be implemented on the IC and how it is to be connected to the ECG analysis system. Next, a brief summary of the properties of the Hilbert transform is given. In the last part of this section, two important aspects of the ECG analysis algorithm are presented: the recognition matrix and the measure of similarity between matrices. They are important because the recognition matrix is the data upon which the ECG processor is to operate on, and the similarity measure is the function to be performed by the ECG processor.

#### 2.3.1. The ECG Analysis Computer System

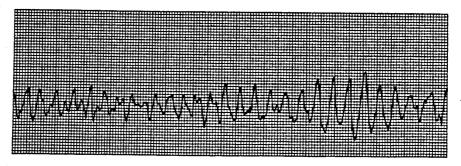

Figure 2.4 shows the block diagram for the proposed ECG analysis system based upon the Hilbert Transform method of morphology recognition. The host computer executes the ECG analysis programs and performs the data transfer to and from the peripherals. The graphics terminal displays ECG waveforms and the alphanumeric terminal interacts with medical personnel for the purposes of classifying or verifying unknown waveforms, providing information on the ECG's, and giving warnings of potentially

Figure 2-4: Block diagram of a clinical ECG analysis system [5].

plotter provide hard copies of requested information for documentation purposes. Two disk drives are used to speed up the ECG data storage; when the computer is switching between ECG analysis and other background programs, the use of two disk drives prevents delays due to disk read/write head movement. The analog to digital converter's resolution has not yet been specified, but 8 bits would be reasonable for this system. The sampling rate has not been defined, but a value of 500 samples per second is used in [5] and so it is the value used in this thesis. The pre-filter includes

ikn Judgod. an analog anti-aliasing filter and possibly a digital or analog filter to limit the input bandwidth and remove 60 Hz noise. The Hilbert transform processor, the QRS detector, and the VLSI morphology processor (the morphology processor is the ECG processor being designed) are functions which were performed in software in the research stage, but for a real-time system, they would be performed in hardware because their execution in software would be too slow. The Hilbert transformer (the Hilbert transform will be defined later) calculates the Hilbert transform of the ECG signal. The QRS detector locates the peak of the R-wave for each heartbeat using the Hilbert transformed signal. This signal is used to identify the R-wave peak because the Hilbert transformed signal makes a zero crossing at major inflection points like the peak of the R-wave in the ECG signal (this is true only if the peaks are well separated). The hardware for both the Hilbert Transform processor and the QRS detector are still under development. morphology processor is the ECG processor being developed in this thesis, and its purpose is to provide the host computer with measures of similarity between each newly recorded ECG waveform and a list of previously classified reference waveforms.

One issue in the computer analysis of ECG's is the selection of the leads used for the analysis. The position of electrodes on the body surface of the patient is important in ECG analysis because their position directly affects not only the morphology of the recording of a normal heartbeat, but also how well certain abnormalities appear in the ECG. For this reason, the number of electrodes used and their placement depends on the purpose of the ECG analysis. A diagnostic system which is used by a physician to help identify a specific heart disease uses 3 to 12 leads (the signal from one lead is the potential difference between two electrodes). Here, many leads are used for diagnosis since certain ECG abnormalities are more visible in one lead position over another lead position and the physician (or diagnostic computer program) wants as much information as possible before making a diagnosis. In contrast to the diagnostic system which does not necessarily

operate in real-time and allows computation time to be traded for diagnostic accuracy, a monitoring system must operate in real-time. hardware costs low for a monitoring system, only one or two leads are monitored per patient. Single lead monitors are the most popular, but dual lead monitors have two advantages. One advantage is a reduced sensitivity to artefact (artefacts are signals which appear in an ECG but are not generated by the heart) since artefacts may appear on one channel and not the other. In this case, analysis continues as long as one good waveform is available from either lead. The ARGUS monitoring system has been developed for both single and dual channel ECG analysis, and experience showed that the single channel version cannot analyze about 5% of the recorded ECG data while the dual channel system was unable to analyze about 2% of the ECG data [19]. This increased rejection of artefacts would be useful in reducing the number of false positive PVC detections. second advantage of the two lead monitoring system is the ability to recognize a greater variety of arrhythmias [1].

The ECG analysis system in [5] for which the ECG processor IC is being developed is based upon a research system which uses one lead per patient. However, the number of leads monitored per patient does not necessarily affect the similarity calculation between two waveforms and one consideration in the design of the ECG processor is that the number of leads used per patient should not affect the operation of the ECG processor.

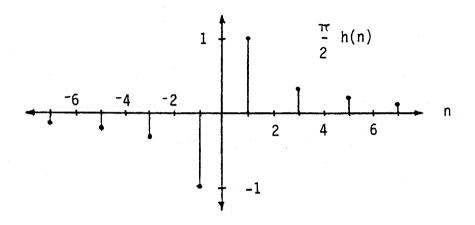

#### 2.3.2. The Hilbert Transform

The key function upon which this morphology recognition algorithm is based is the Hilbert transform. It is defined as:

$$h(t) = \frac{1}{\pi t} f(t)$$

(where \* denotes convolution) (2.1)

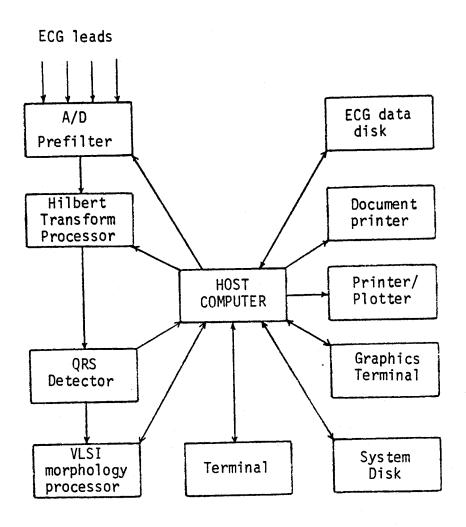

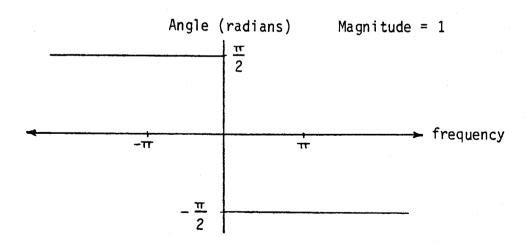

where f(t) is the input signal and h(t) is the Hilbert transform of f(t). The impulse response and the frequency response of a discrete Hilbert transformer are given in Figures 2.5 and 2.6. The ideal Hilbert transformer does not

## IMPULSE RESPONSE OF THE HILBERT TRANSFORM

Figure 2-5: Impulse response of the Hilbert Transformer.

#### Phase Plot of the Hilbert Transform

Figure 2-6: Frequency response of a Hilbert Transformer.

exist and practical circuits provide only approximations of the Hilbert transform. For the application of morphology recognition, no tests have been done to determine the tolerance of the morphology recognition algorithm to approximations of Hilbert transforms, however, the frequency response and the phase response should be as flat as possible in order to preserve the time independent representation feature provided by this algorithm.

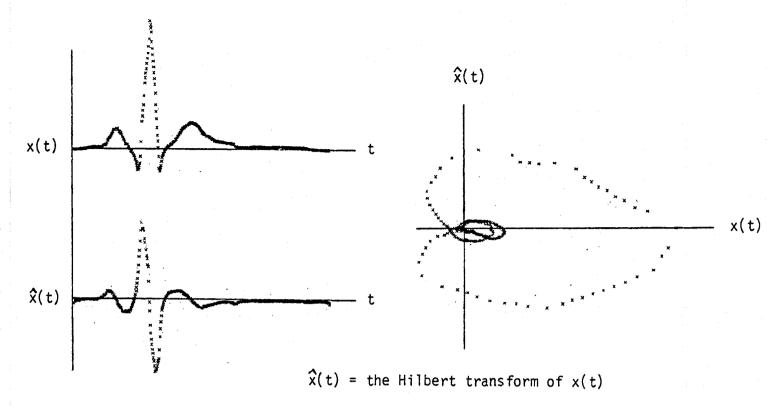

The unique feature of the Hilbert transform morphology recognition algorithm is the mapping of the input signal into a representation called the recognition matrix. Other morphology recognition algorithms usually isolate the waveform of one heartbeat and perform correlation calculations between it and several reference patterns called templates. One problem with this technique is that alignment along the time axis is necessary for correlation calculations and the correlation calculations are sensitive to even slight misalignments. Also, the alignment is difficult to do for waveforms of different shapes. The Hilbert Transform technique eliminates the problem of alignment along the time axis by representing the ECG waveform shape in a way that eliminates the time dependence of the data. The principle of this representation is demonstrated by plotting the Hilbert transform of the signal against the signal itself as shown in Figure The resulting plot has no time axis and is the same for two waveforms whose shape is the same, but whose durations may be different. example, two sinusoidal waves of the same amplitude, but of different frequencies both produce identical circles when plotted in a fashion similar to Figure 2.7.

#### 2.3.3. The Recognition Matrix

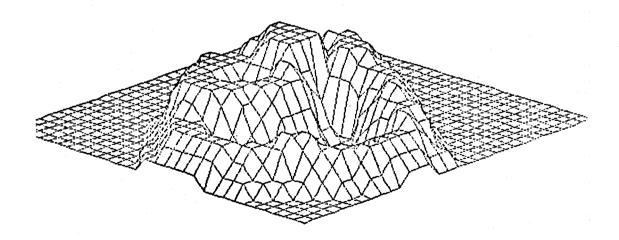

The plot in Figure 2.7 is just a demonstration and not the true representation used in the morphology recognition algorithm. The actual representation used by the Hilbert Transform morphology recognition algorithm is a 31 by 31 element matrix called the recognition matrix. An example of a recognition matrix is shown in Figure 2.8. Experiments carried

Figure 2-7: Generation of the Hilbert Transform representation.

out in [5] showed that the morphology recognition algorithm worked well for matrix sizes of 15 by 15 to 31 by 31 elements. The larger size matrices provided the greatest accuracy and so were selected for the IC design. It was also found that matrices should have an odd number of rows and columns to prevent dithering when the signal is on the baseline.

Another view of the recognition matrix of Figure 2.8 is that of a two-dimensional histogram as shown in Figure 2.9. In this view, each element of the histogram can be considered to correspond to the number of ECG signal sample points which were mapped into that particular area of the histogram. To create a histogram, all elements are initially set to zero. Then by taking one signal sample point at a time, the elements of certain locations of the histogram are incremented by user defined amounts. The finished histogram is the cumulative effect of the incrementing after all the sample points of one

Figure 2-8: An example of a recognition matrix.

Figure 2-9: A view of a recognition matrix as a histogram [5].

heartbeat have been processed. For a typical heart rate of 70 beats per minute and a 500Hz sampling rate, this is typically 430 sample points. The locations on the histogram to be incremented are determined by the value of the digitized ECG signal, the corresponding Hilbert transform value, and the mapping function. The amounts by which the elements are incremented by are given by the potential function shown in Figure 2.10.

COLUMN OF RECOGNITION MATRIX

|                                    |       | j-1 | j | j+1_ |

|------------------------------------|-------|-----|---|------|

| ROW<br>OF<br>RECOGNITION<br>MATRIX | i - 1 | 1   | 1 | 1    |

|                                    | i     | 1   | 2 | 1    |

|                                    | i+1   | 1   | 1 | 1    |

Figure 2-10: The potential function used in this thesis.

The mapping function is performed after all the sample points have been collected for one heartbeat. The mapping function as defined in [5] is based upon the following definitions and equations:

$$x(n) = n^{th}$$

sample point of ECG signal (2.2)

$$\chi(n) = n^{th}$$

sample point of the

Hilbert transformed signal (2.3)

$$x(n) + j\chi(n) = \text{pre-envelope of } x(n)$$

(2.4)

$$z(n) = \sqrt{x(n)^2 + \chi(n)^2} = \text{envelope or magnitude of } x(n)$$

(2.5)

$$z_{max}$$

= the maximum magnitude for one heartbeat (2.6)

$$\phi(n) = \operatorname{atan}\left(\frac{\chi(n)}{x(n)}\right)$$

$$= \operatorname{angle of the pre-envelope}$$

(2.7)

$$2N_x + 1$$

= number of rows in the recognition matrix (2.8)

$$2N_y + 1$$

= number of columns in the recognition matrix (2.9)

$$A_{i,i} =$$

$$\sum_{\text{all n}} K((N_x + 1 + N_x \frac{z(n)}{z_{max}} \cos(\phi(n))), (N_y + 1 + N_y \frac{z(n)}{z_{max}} \sin(\phi(n))))$$

The purpose of changing the ECG data and its Hilbert transform into the polar coordinates  $z(n) \angle \phi(n)$  is to scale the data by  $z_{max}$  and then convert the scaled polar coordinates into the rectangular coordinates of the recognition matrix.

While Equation 2.11 is useful for a research system, a system operating in real-time would benefit by a mapping procedure which did not use the sine or cosine functions. In order to provide a real-time implementation of Equation 2.11 two methods of mapping the ECG data into a recognition matrix are presented here: the first method will give the same results as Equation 2.11 while the second method will give approximately the same results and is faster than the first method.

#### Method 1.

- 1. Find the square of the maximum magnitude of the envelope,  $z_{max}^2$ , by finding the largest value of  $x(n)^2 + \chi(n)^2$ .

- 2. Calculate the scale factor

$$a = \frac{\text{maximum possible representation of } x(n)}{\sqrt{\frac{z_{max}^2}{4}}}$$

The maximum possible representation of x(n) depends on the number of bits used to represent x(n); if 8-bits are used, then the maximum value would be 255. The purpose of dividing  $z_{max}^2$  by 4 is to speed up the calculation of the square-root. If  $x(n)^2$  and  $\chi(n)^2$  are 8-bit values,  $z_{max}$  could be a 9-bit value (see Equation 2.5) which could require the use of 16-bit arithmetic on some microprocessors, but dividing by 4 permits the use of 8-bit hardware or software math routines for the scale factor calculations.

3. Multiply each sample point by the scale factor.

$$x_s(n) = a x(n)$$

$$\chi_s(n) = a \chi(n)$$

Each scaled sample point is now ready to be used as a pointer to the row and column of the recognition matrix to which potential functions are to be added.

4. For each sample point in the ECG waveform, add the potential function to the location determined by

row = 5 most significant digits of the scaled value x<sub>s</sub>(n)

column = 5 most significant digits of the scaled value  $\chi_s(n)$ .

The phrase 5 most significant digits is used because it does not assume to resolution of the sample points is known. It is another way of saying scale the highest value of the scaled values, say, for example 255, to the largest row or column of the matrix (that is 31 in this case). This method applies only to unsigned integers, and the system designer must take care when applying the above algorithm to two's complement numbers.

#### Method 2.

- 1. Find the maximum value of both x(n) and  $\chi(n)$  and call it  $x_{max}$ .

- 2. Calculate the scale factor

$$a = \frac{\text{maximum possible representation for } x(n)}{x_{\text{max}}}$$

3. Follow through steps 3. and 4. of method 1.

This method will scale all waveforms into the recognition matrix, but not in the same way as Equation 2.11. While method 1 scales according to the maximum magnitude of the envelope z(n), method 2 scales according to the maximum value of the sample points in x(n) and  $\chi(n)$ . The selection of these two mapping algorithms is the decision of the person programming the host computer, and does not affect the design of the ECG processor.

#### 2.3.4. Computing the Similarity between Matrices

Once a recognition matrix is created from newly acquired ECG data, it must be compared to several reference matrices in order to be classified. The function selected for the comparison is the Bhattacharyya distance function [20]:

min :

$$Q = -\log \left[ \int_{0}^{X} \sqrt{P_c(x) P_u(x)} dX \right]$$

(2.12)

where

Q = distance between the probability distribution  $P_{c}(x)$  and  $P_{u}(x)$

$P_c(x)$  = probability distribution for class c

$P_u(x)$  = probability distribution for class u

X = the pattern space or in this case the recognition matrix.

This distance function has been modified for use with recognition matrices. The first change is the elimination of the -log operator because it does not affect the decision on which two matrices are the best match. The new function is now a similarity measure:

$$\max : Q' = \int_{0}^{X} \sqrt{P_{c}(x)P_{u}(x)} dX$$

(2.13)

where Q' = the degree of similarity between class c and class u

The above equations are for continuous distributions; for this ECG processing application, a discrete form is required:

$$\max : Q_d = \sum_{i=1}^{2N_x+1} \sum_{j=1}^{2N_y+1} \sqrt{P_c P_u}$$

(2.14)

where

$Q_d$  = the degree of similarity between the unknown class u and the reference class c

$$\begin{aligned} \mathbf{P}_{\mathbf{u}} &= \frac{U_{i,j}}{N_{u}} \\ \mathbf{P}_{\mathbf{c}} &= \frac{M_{i,j}}{N_{c}} \end{aligned}$$

U = the unknown recognition matrix

M(c) = the reference recognition matrix for class c

$N_u =$ the number of points in the unknown matrix

N<sub>c</sub> = the number of points in reference matrix c.

$\mathbf{Q_d}$  is calculated for several reference matrices and the unknown matrix is assigned to the class which produces the largest value of  $\mathbf{Q_d}$  provided that a minimum level of similarity is met. If the unknown matrix does not fit any of the reference matrices to a reasonable degree, the unknown matrix itself may be stored as a reference matrix for future classification calculations.

Because at first the square-root function appears to be a complex function whose implementation in IC circuitry would consume a large area on the IC, other distance measures for the classification process were considered. One example that appears to require less computational effort than the Bhattacharyya distance measure is the Patrick-Fisher distance measure [20]:

$$\min : \quad Q^2 = \int^X [p_1 p_1(x) - p_2 p_2(x)]^2 dX \tag{2.15}$$

When modified for use with recognition matrices, this appears to require only one subtraction and multiplication for each matrix element. However, computational complexity depends on the number of bits being operated on

as well as the functions being performed, and consideration of this must be made when comparing these two distance functions. For example, the square-root function compresses the dynamic range of the input values whereas the square function of the Patrick-Fisher measure expands the dynamic range. This means that if the recognition matrix elements are 8-bits, their square-root will be 4-bits (more bits can be added to increase the precision, but the dynamic range is still covered by 4-bits). As the square-root is done first, all remaining functions need only operate on 4-bit data (for example, a 4 x 4 multiplier). The square function, on the other hand, will produce a 16 bit result which must later be operated on and stored. As the chip design progresses, it will be seen that the chip area required for the square-root extractor is offset by savings produced by the smaller data size of the square-root output.

One idea which was tested while looking for other similarity measures was simply to eliminate the square-root function and complete all other calculations as before. While no mathematical justification could be made for doing this, this test would ensure that the square-root extractor was a necessary part of the ECG processor. In one test, the similarity between various one-dimensional continuous probability distributions was computed. The test showed that in the worst case, the similarity between two obviously different distributions had a computed similarity measure equal to that of identical distributions.

Because this did not prove that eliminating the square-root function would always cause classification errors, another test closely resembling the ECG analysis application was made. In this second test, all combinations of 2x2 matrices and 3x3 matrices were compared to each other. The results of this test depended upon the sum of all elements in the matrices. If the sum of the elements was greater than two, there were misclassifications. If the sum of the elements was equal to two, then there were only ties, that is, the similarity between different matrices could equal that of a perfect match. A study of the matrices which were classified correctly and those which were

not showed that errors occurred when a sharply peaked distribution was compared to a more even distribution of numbers.

The results of these tests showed that under certain conditions, there is a possibility that the square-root extractor could be eliminated, but further tests on recognition matrices used in ECG analysis would be necessary before taking this step in the ECG processor design.

# 2.4. Summary

In the first section of this chapter, the origin of the ECG signal was presented along with a few examples of normal and abnormal ECG waveforms. Next, a brief description was given on the operation of a computer ECG analysis system. In the final part of the chapter, the Hilbert transform method for ECG analysis was discussed and the two main features of this algorithm, the recognition matrix and the similarity measure, were described in detail. This description included two methods for generating a recognition matrix and the development of a similarity measure from the Bhattacharyya distance function.

# Chapter 3 Integrated Circuit Design

This chapter covers two aspects of IC design. First, the techniques used to manage the complexity of the design of a large digital circuit are discussed, and then the computer programs used to design an IC are examined.

# 3.1. IC Design Procedure

VLSI design requires all of the complexity management discipline associated with complex software systems, but without the underlying simplicity of a single sequential machine. Not only must we deal with the problems of enormous concurrency, but we must map the entire design onto a physical medium, with constraints on space, time, and energy imposed by the laws of physics. [21]

As indicated by this quote, VLSI design requires some methodology to handle the large amount of data and the high number of decisions involved with IC design because for large IC's, the complete freedom to 'draw' anything on the silicon chip overwhelms the average human designer. This complexity of IC design arises from the number of factors which must be considered in IC design including:

1. Keep chip area to a minimum. Yield, defined as the number of good chips produced per total number of chips fabricated, decreases rapidly as area increases because particle contamination is the main cause of fabrication failure (see Table 3.1) and the probability of particle contamination is an exponential function of the chip area.

| Particle contamination                           | 30% |

|--------------------------------------------------|-----|

| Design margin                                    | 6%  |

| Photolithographic errors (e.g., alignment error) | 9%  |

| Material defects                                 | 6%  |

| Process variation                                | 9%  |

| Total die loss                                   | 60% |

| Die yield (100% - die loss)                      | 40% |

Table 3-1: Typical sources of chip fabrication failure for a  $2\mu$  process [22].

- 2. Design circuits with some tolerance of circuit parameters. Transistor characteristics can vary from wafer to wafer, from one point on a wafer to another, and even across a large chip. To improve yield, circuits should be designed to allow for variations from planned circuit speeds. Another advantage of allowing for parameter variations is the possibility of using more than one vendor to supply parts.

- 3. Design for testability. Testability is a measure of the fraction of the total number of transistors in the IC which can be tested in a reasonable length of time. Because yield is low, every chip must be tested to separate good chips from bad, but a complete test which provides 100% confidence in the final product is sometimes difficult. On the other hand, testing a circuit insufficiently could mean a field repair costing hundreds of times more than the cost of the IC.

- 4. Make the chip easy to use. Like a programmer using a subroutine written by another programmer, circuit designers using the chip want to know how to use the chip while having to learn as little as possible.

- 5. Balance between a complex design which provides every function the chip consumer wants, and a simple design which is easier to design and test, or in other words, the IC designer must decide what functions are a worthwhile part of the design and which are not.

Still ?

This section presents two common methods available to manage the complexity of IC design: the use of hierarchical abstraction, and the use of a global two-phase clock signal. Following this, another issue of IC complexity, the ability to test what has been designed, is discussed briefly.

#### 3.1.1. Hierarchical abstraction

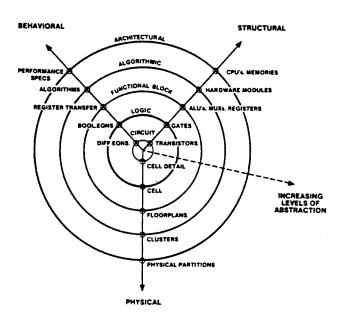

Abstraction means replacing an object with a simpler one that keeps only the most important information about the original object's interactions with the environment [23]. The value of abstraction is a data reduction which allows the designer to concentrate on the important aspects of the object during the design process. Since the average person cannot consider all the details of an IC design at one time, abstraction is important, and, as illustrated in Figure 3.1, it has been applied to three representations in IC design: the physical or layout description, the behavioural or functional description, and the structural or circuit description.

Figure 3-1: Levels of abstraction commonly used in IC design [9].

From this figure, it also can be seen that abstraction is not restricted to one level; it may be applied several times to obtain a hierarchical abstraction with the purpose of allowing the designer to comprehend all the necessary detail at each level in the design. For IC design, four or five levels of abstraction have been found sufficient.

Another name for this hierarchical design approach is 'divide and Although the idea of a hierarchy is clear, the procedure for 'dividing' or partitioning a problem is not obvious. For instance, suppose the problem is to design a circuit to calculate  $\sqrt{ab}$ . The first step, defining the inputs and outputs is not difficult; the inputs are a and b, and the output is  $\sqrt{ab}$ . Unless a circuit exists to calculate  $\sqrt{ab}$ , the designer would attempt to do the obvious, that is, build the circuit up from a multiplier and a square-root extractor. The designer then develops a circuit where two 8-bit inputs are multiplied to give a 16-bit result and the 8-bit square-root extracted from the intermediate 16-bit result. This achieves the desired value, however, the problem could have been divided into  $\sqrt{a}\sqrt{b}$ . case, two 8-bit square-root extractors provide two intermediate 4-bit results which are multiplied to give  $\sqrt{ab}$ . Though it was originally not obvious, this division yields a more compact design than the first approach at the expense of precision in the resulting output. This example demonstrates the problem of partitioning in a hierarchical design.

#### 3.1.2. System timing

Co-ordinating the flow of data through the various parts of the IC is another complex IC design problem. To help the designer organise the on-chip data communication, methods, such as 2-phase clocks, 4-phase clocks, and self-timed signalling [14] have been developed. Synchronous systems which are based upon a global clock signal are used extensively in IC design; every microprocessor known by the author requires some type of clock signal.

The 2-phase clocking scheme is selected for the IC design in this thesis.

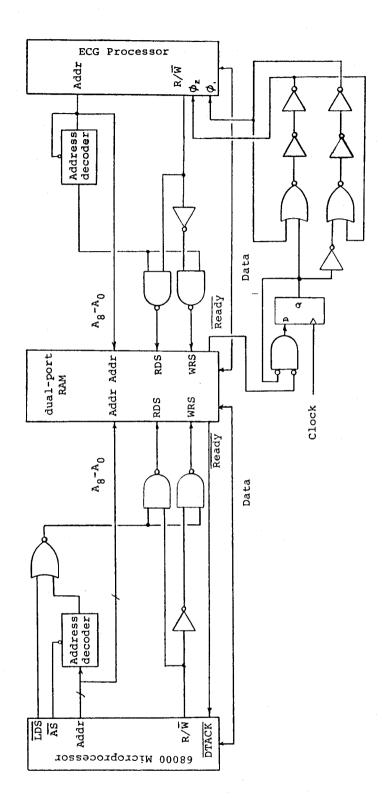

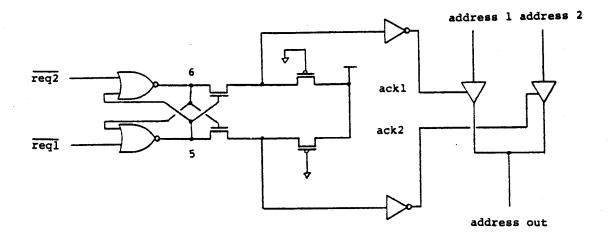

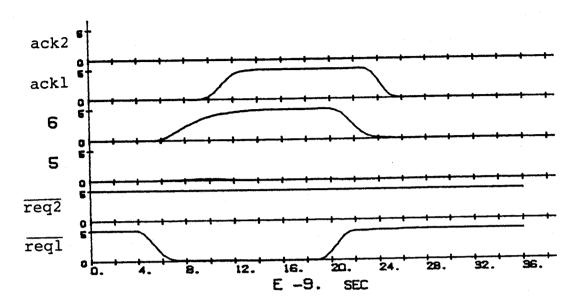

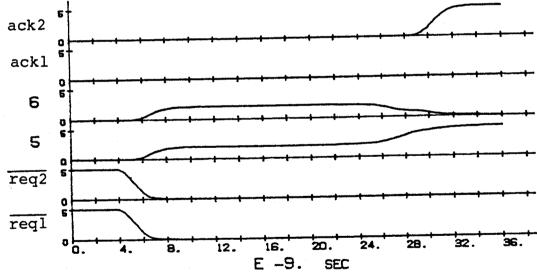

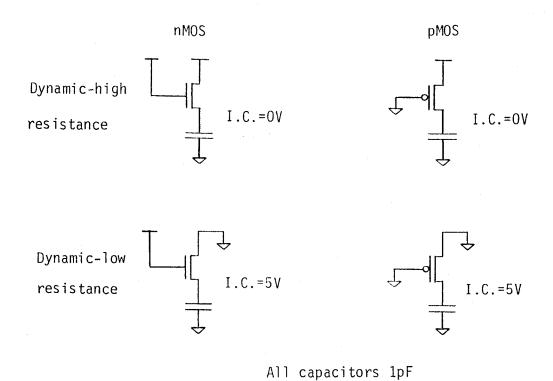

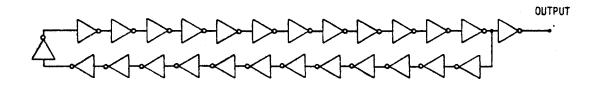

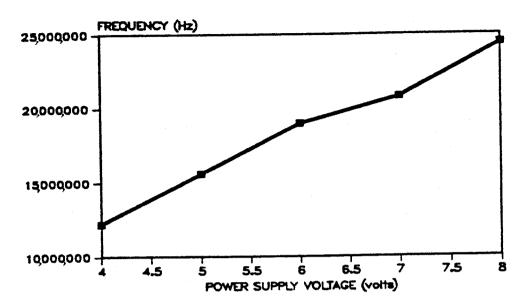

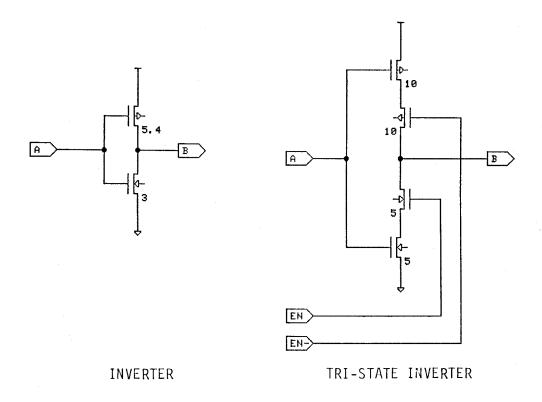

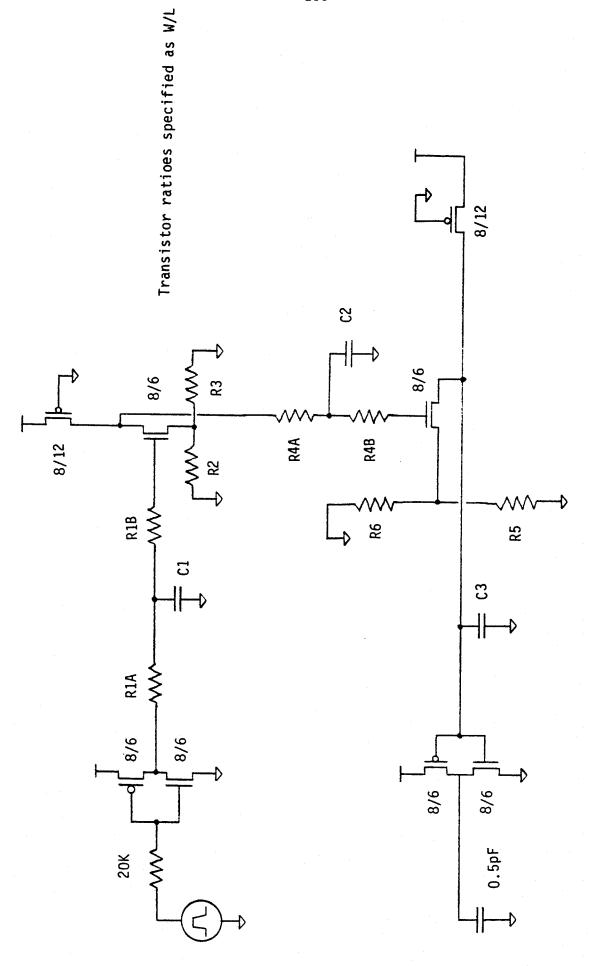

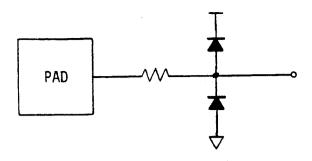

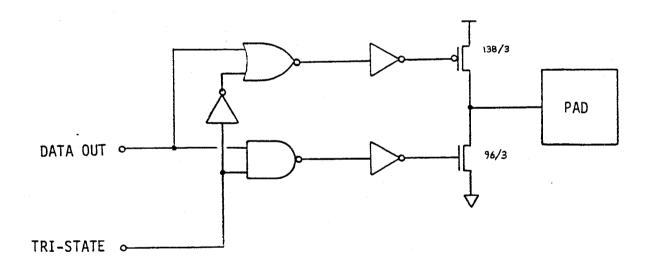

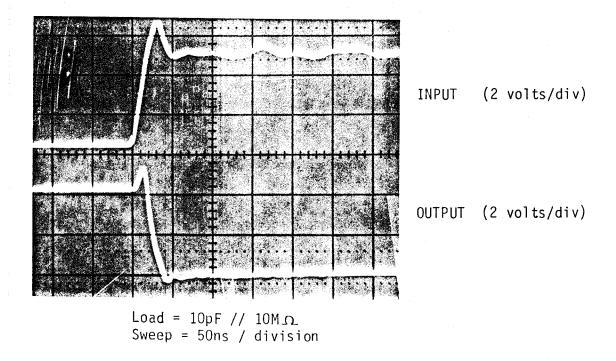

Its advantages include: it is a simple and easy-to-understand clock which means the designer should make few implementation errors, it prevents race conditions and closed feed-back loops, and it is useful for both static and But there are a few limitations of the two-phase clock. dynamic circuits. One problem is that the clock frequency is limited by the slowest circuit on For example, 99% of the logic functions may be complete within one tenth of a clock cycle, but a new clock cycle cannot begin until all logic Another problem is distributing the clock functions have been computed. throughout the chip so that the clock signal is the same everywhere in the This signal is used as a reference for on-chip data communication, and if the clock signal in one area on the chip is delayed relative to another area on the chip, communication problems may arise when data is being transferred between these two areas. One more problem, although minor, is synchronization failure which occurs when trying to read information into a synchronous system from an asynchronous source. This problem arises from the condition where it is possible for a flip-flop to exist in an unstable equilibrium or metastable condition for an indefinite length of time. In this state, circuit voltages are neither logic '1' nor logic '0', and although such a state has a small probability of occurring, in an example given in [14] a value of  $3x10^{-12}$  is given which translates into an error every three days at a data transfer rate of 1 MHz. The only solution to this problem is to detect the metastable state and wait for it to end before continuing with the data.