# SYSTEM ARCHITECTURE AND HARDWARE IMPLEMENTATIONS FOR A RECONFIGURABLE MPLS ROUTER

A Thesis Submitted to the College of

Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of Master of Science in the

Department of Electrical Engineering

University of Saskatchewan

By

Li Sha

**PERMISSION TO USE**

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate

degree from the University of Saskatchewan, I agree that the Libraries of this University

may make it freely available for inspection. I further agree that permission for copying

of this thesis in any manner, in whole or in part, for scholarly purposes may be granted

by the professor or professors who supervised my thesis work or, in their absence, by

the Head of the Department or the Dean of the College in which my thesis work was

done. It is understood that any copying or publication or use of this thesis or parts

thereof for financial gain shall not be allowed without my written permission. It is also

understood that due recognition shall be given to me and to the University of

Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in

whole or part should be addressed to:

Dept of Electrical Engineering

57 Campus Road

Saskatoon, Sask. S7N 5A9 Canada

Phone: (306) 966-5380

Fax: (306) 966-5407

i

#### **ABSTRACT**

With extremely wide bandwidth and good channel properties, optical fibers have brought fast and reliable data transmission to today's data communications. However, to handle heavy traffic flowing through optical physical links, much faster processing speed is required or else congestion can take place at network nodes. Also, to provide people with voice, data and all categories of multimedia services, distinguishing between different data flows is a requirement. To address these router performance, Quality of Service /Class of Service and traffic engineering issues, Multi-Protocol Label Switching (MPLS) was proposed for IP-based Internetworks. In addition, routers flexible in hardware architecture in order to support ever-evolving protocols and services without causing big infrastructure modification or replacement are also desirable. Therefore, reconfigurable hardware implementation of MPLS was proposed in this project to obtain the overall fast processing speed at network nodes.

The long-term goal of this project is to develop a reconfigurable MPLS router, which uniquely integrates the best features of operations being conducted in software and in run-time-reconfigurable hardware. The scope of this thesis includes system architecture and service algorithm considerations, Verilog coding and testing for an actual device. The hardware and software co-design technique was used to partition and schedule the protocol code for execution on both a general-purpose processor and stream-based hardware. A novel RPS scheme that is practically easy to build and can realize pipelined packet-by-packet data transfer at each output was proposed to take the place of the traditional crossbar switching. In RPS, packets with variable lengths can be switched intelligently without performing packet segmentation and reassembly. Primary theoretical analysis of queuing issues was discussed and an improved multiple queue service scheduling policy UD-WRR was proposed, which can reduce packet-waiting time without sacrificing the performance. In order to have the tests carried out appropriately, dedicated circuitry for the MPLS functional block to interface a specific

MAC chip was implemented as well. The hardware designs for all functions were realized with a single Field Programmable Gate Array (FPGA) device in this project.

The main result presented in this thesis was the MPLS function implementation realizing a major part of layer three routing at the reconfigurable hardware level, which advanced a great step towards the goal of building a router that is both fast and flexible.

#### **ACKNOWLEDGEMENTS**

The author wishes to thank Dr. Eric Norum and Dr. J. Eric Salt for their guidance and financial support throughout the course of this project. Especially, she would like to show her great appreciation for Dr. Norum's timely thesis reviewing after he left University of Saskatchewan. A wonderful work environment was setup at Trlabs. Jack Hanson, Garth Wells, and the rest of the staff at Trlabs, Saskatoon, are all thanked for their time and help. Also, the author would like to say thank you to Dr. Ronald J. Bolton and her first supervisor at University of Saskatchewan, Dr. Gul Khan.

The Department of Electrical Engineering, University of Saskatchewan and Dr. J. Eric Salt provided financial assistance. Their support is gratefully acknowledged.

Finally, the author would like to thank her parents, Li Xianlin and Zhang Xiurong for their much needed support and her husband, Hu Song for providing a great deal of patience and support during some difficult times.

# TABLE OF CONTENTS

| PERMISSION TO USE                            | i        |

|----------------------------------------------|----------|

| ABSTRACT                                     | ii       |

| ACKNOWLEDGEMENTS                             | iv       |

| TABLE OF CONTENTS                            | v        |

| LIST OF FIGURES                              | viii     |

| LIST OF TABLES                               | X        |

| LIST OF ABBREVIATIONS                        | xi       |

| Chapter 1 Introduction                       | 1        |

| 1.1 Motivation                               | 1        |

| 1.2 What is MPLS?                            | 3        |

| 1.3 Introduction to Reconfigurable Routers   | 6        |

| 1.3.1 Typical Router Architecture            | <i>6</i> |

| 1.3.2 Why Reconfigurability?                 | 7        |

| 1.4 Industrial MPLS Router Products Overview | g        |

| 1.4.1 Cisco 12000                            | 9        |

| 1.4.2 JUNOS M40                              | 10       |

| 1.4.3 Alcatel 7670 Routing Switch Platform   |          |

| 1.4.4 Marconi ASX4000                        |          |

| 1.4.5 Conclusion: New Products Desired       | 13       |

| Chapter 2 Multi-Protocol Switching           | 15       |

| 2.1 Main MPLS Components                     |          |

| 2.2 MPLS Operation                           | 23       |

| 2.3 Tunneling in MPLS                        | 26       |

| 2.4 Traffic Engineering and QoS              | 27       |

| 2.5 Protocol Architecture                    | 29       |

| Chapter 3 Reconfigurable MPLS Router Design Issues            | 31 |

|---------------------------------------------------------------|----|

| 3.1 Switch/Router evolution                                   | 31 |

| 3.1.1 The First Generation                                    | 31 |

| 3.1.2 The Second Generation                                   | 32 |

| 3.1.3 The Third Generation                                    | 32 |

| 3.1.4 The Fourth Generation To Be Developed                   | 33 |

| 3.2 System Design Strategy                                    | 35 |

| 3.2.1 Protocol software and hardware partition                | 35 |

| 3.2.2 Hardware Architecture of the Reconfigurable MPLS Router | 37 |

| 3.2.3 Single-chip RHFE design for Line Cards                  | 38 |

| 3.3 Dealing with Queuing Issues                               | 40 |

| 3.3.1. Background                                             | 40 |

| 3.3.1.1 Priority Queue Scheduling                             | 40 |

| 3.3.1.2 Multiple Per-Flow Priority-Queue Management           | 43 |

| 3.3.2 An Improved UD-WRR Policy                               | 45 |

| 3.4 RPS and UD-WRR Implementations in a MPLS System           | 53 |

| Chapter 4 Reconfigurable MPLS Hardware Implementation         | 56 |

| 4.1 Implementation Strategy Considerations                    | 56 |

| 4.2 Design and Implementation                                 | 57 |

| 4.2.1 Top Module Design                                       | 57 |

| 4.2.2 Second Layer Modules                                    | 58 |

| 4.2.3 Implementation Details of the Third-Layer Modules       | 61 |

| 4.2.3.1 State Machines                                        | 61 |

| 4.2.3.2 Receive Buffers                                       | 64 |

| 4.2.3.3 Label Removing                                        | 69 |

| 4.2.3.4 Lookup Table                                          | 71 |

| 4.2.3.5 Label Binding and Switching                           | 75 |

| 4.2.3.6 Transmit Buffers                                      | 76 |

| Chapter 5 Test Development and Procedure                      | 79 |

| 5.1 Introduction                                              | 79 |

| 5.2 Test Methodology Development                              | 80 |

| 5.3 The Test Equipment                            | 83  |

|---------------------------------------------------|-----|

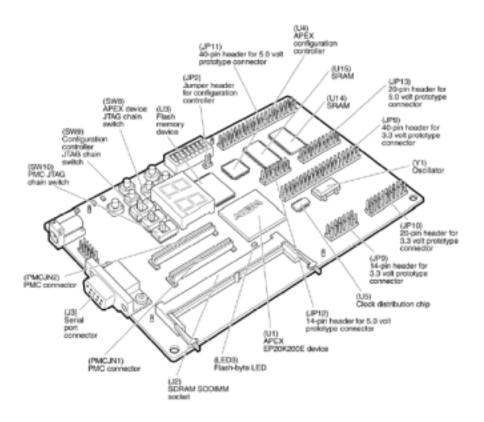

| 5.3.1 The Motherboard                             | 83  |

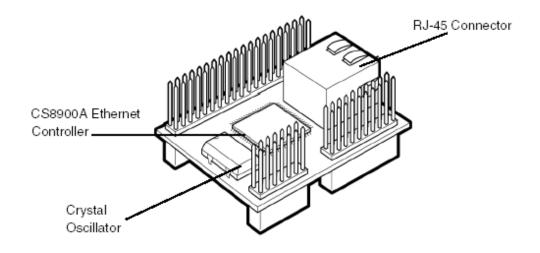

| 5.3.2 The Daughter Card                           | 84  |

| 5.3.3 Introduction to the CS8900A                 | 86  |

| 5.3.3.1 CS8900A Work Mode                         | 86  |

| 5.3.3.2 CS8900A Configuration                     | 88  |

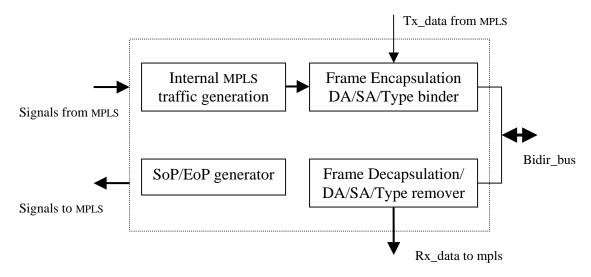

| 5.4 Interface design                              | 88  |

| 5.4.1 Functions to Be Performed                   | 88  |

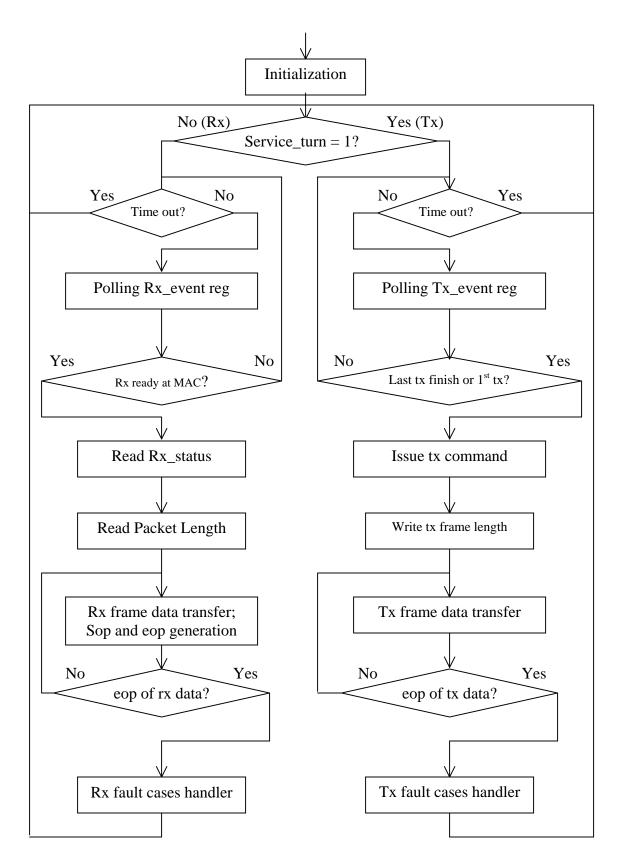

| 5.4.2 Flow Chart of Interface Functions           | 90  |

| 5.4.3 Input/Output Signal Description             | 93  |

| 5.5 The Tests                                     | 97  |

| 5.5.1 Test Configuration                          | 97  |

| 5.5.2 Real Testing Procedure                      | 102 |

| Chapter 6 Test Results and Analysis               | 103 |

| 6.1 Overview                                      | 103 |

| 6.2 Test Result Demonstration and Simple Analysis | 104 |

| 6.2.1 CS8900A Configuration                       | 104 |

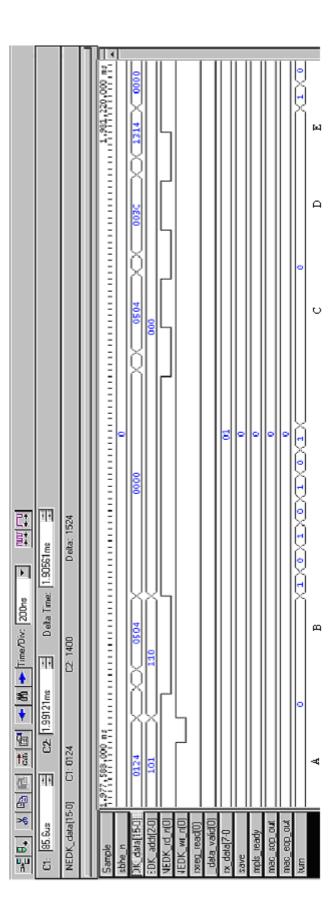

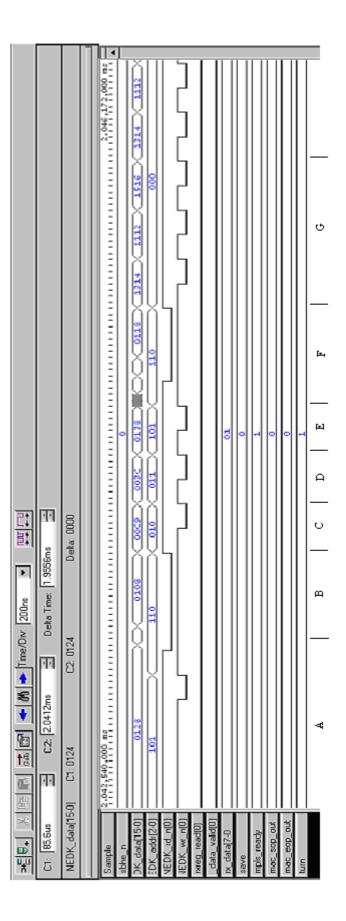

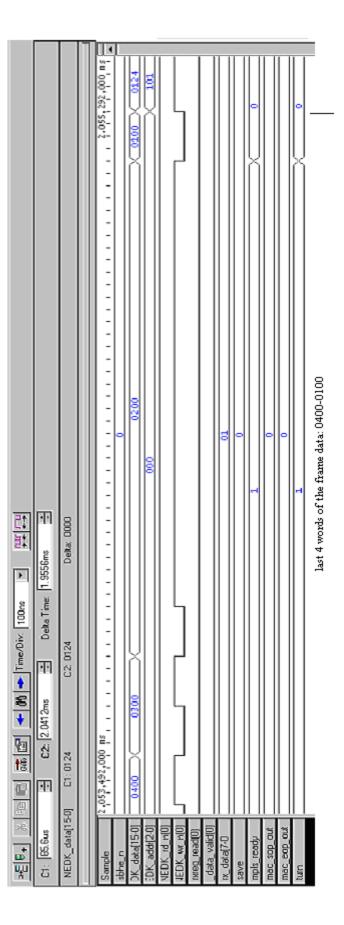

| 6.2.2 Packet Receiving and Label Swapping         | 106 |

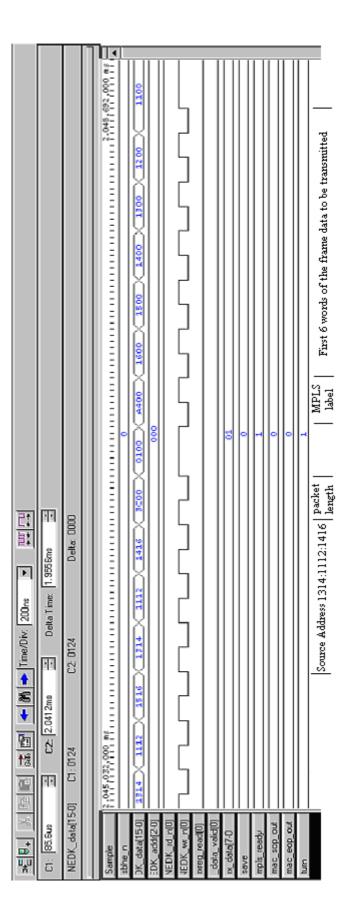

| 6.2.3 Label Binding and Packet Buffering          | 115 |

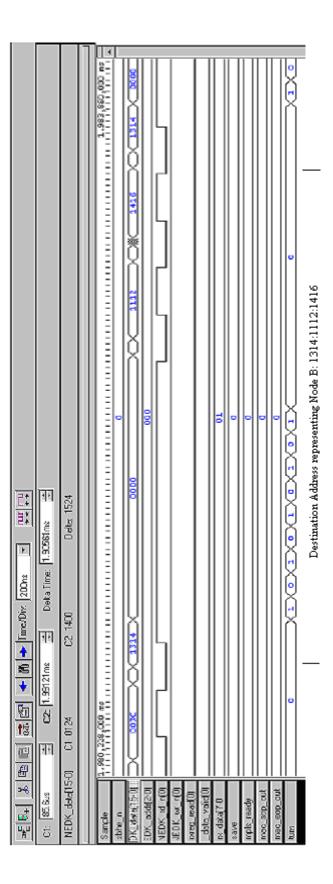

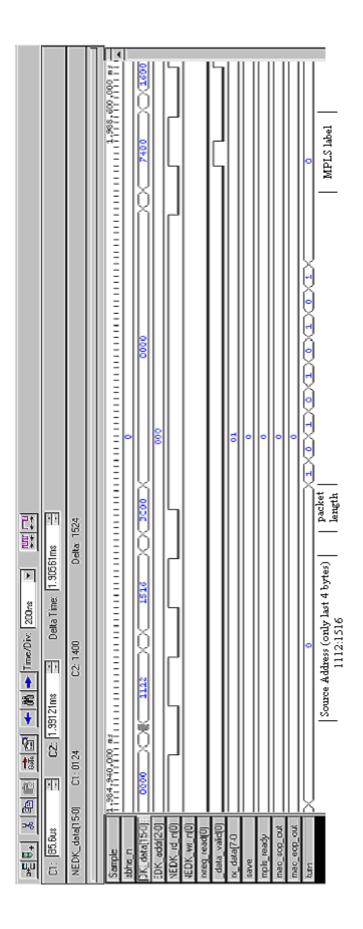

| 6.2.4 Packet Transmission                         | 119 |

| 6.3 Special Considerations                        | 127 |

| Chapter 7 Conclusions and Future Work             | 130 |

| 7.1 Conclusions                                   | 130 |

| 7.2 Future Work                                   | 132 |

| References                                        | 134 |

| MPLS                                              | 134 |

| Switch/Router                                     |     |

| Queuing Theory                                    |     |

| Queuing Implementation                            |     |

| Data Sheets                                       |     |

| Other                                             | 137 |

# LIST OF FIGURES

| Figure 1-1 Architecture of a Typical Router                             | 6    |

|-------------------------------------------------------------------------|------|

| Figure 1-2 Logical View of M40 Architecture                             | 11   |

| Figure 2-1 MPLS Generic Label Format.                                   | 17   |

| Figure 2-2 ATM as the Data Link Layer                                   | 18   |

| Figure 2-3 Frame Relay as the Data Link Layer                           | 18   |

| Figure 2-4 Point-to-Point (PPP)/Ethernet as the Data Link Layer         | 18   |

| Figure 2-5 LSP Creation and Packet Forwarding through an MPLS Domain    | 24   |

| Figure 2-6 Tunneling in MPLS                                            | 27   |

| Figure 2-7 MPLS Protocol Stack                                          | 30   |

| Figure 3-1 First Generation Switch/Routers                              | 31   |

| Figure 3-2 Second Generation Switch/Routers                             | 32   |

| Figure 3-3 Left: Third Generation Switch/Router; Top-Right: A Crossbar; |      |

| Bottom-Right: An 8x8 Banyan Fabric made of small 2x2 switch blocks      | s 33 |

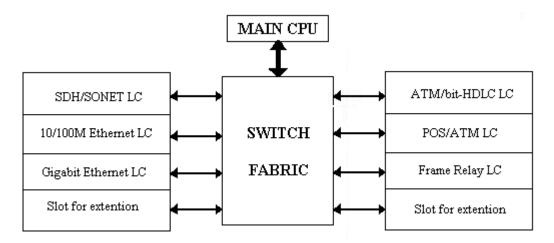

| Figure 3-4 Logical Architecture of the LSR                              | 37   |

| Figure 3-5 Hardware Architecture of a Reconfigurable MPLS Router        | 38   |

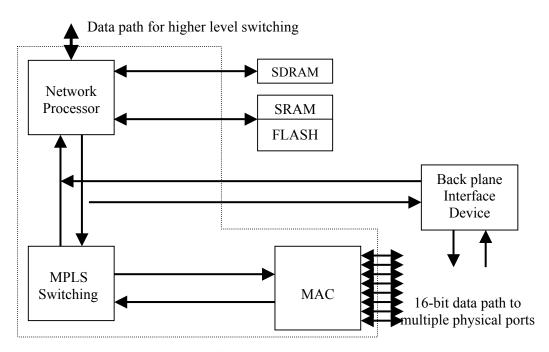

| Figure 3-6 Single-Chip RHFE Design for Line Cards                       | 39   |

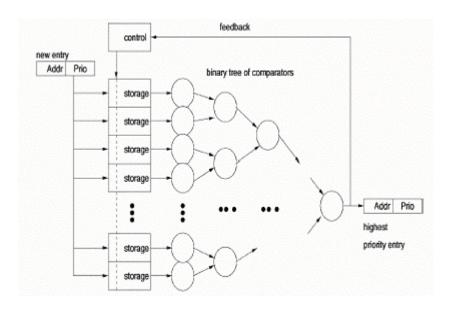

| Figure 3-7 Binary Tree of Comparators Priority Queue                    | 41   |

| Figure 3-8 Shift Register Priority Queue and Shift Register Block       | 42   |

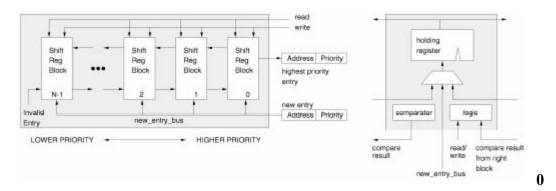

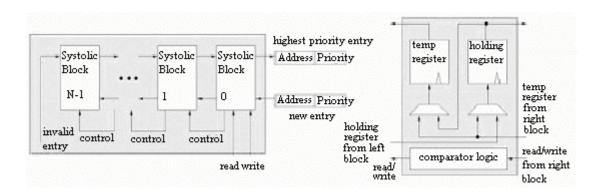

| Figure 3-9 Systolic Array Priority Queue and Systolic Array Block       | 42   |

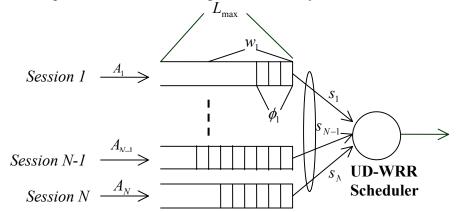

| Figure 3-10 UD-WRR Scheduling Policy                                    | 48   |

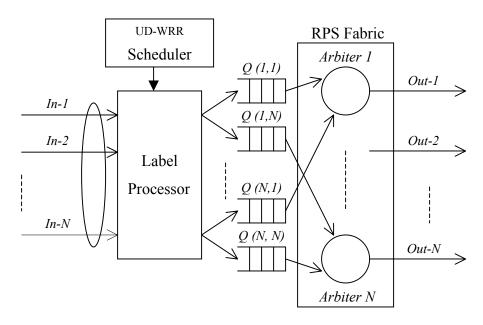

| Figure 3-11 $N \times N$ RPS Architecture Adopting UD-WRR               | 55   |

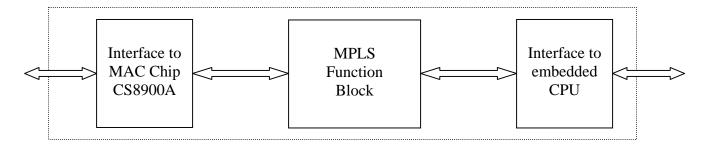

| Figure 4-1 Top Module Block Diagram                                     | 58   |

| Figure 4-2 MPLS Functional Block Diagram                                | 59   |

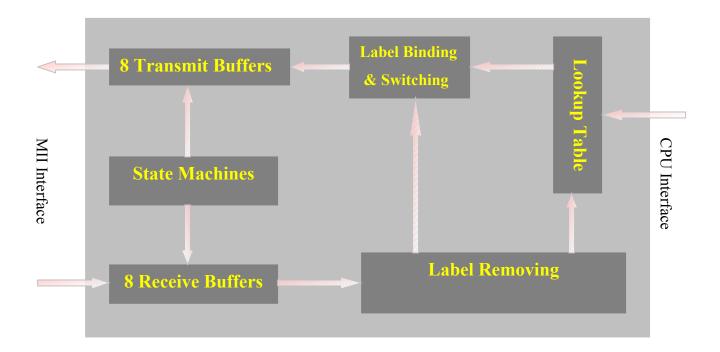

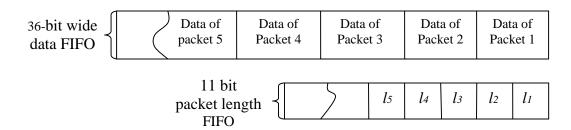

| Figure 4-3 State Machine Block Symbols, prototype names:                |      |

| a) polling_machine b) polling_machine0                                  | 62   |

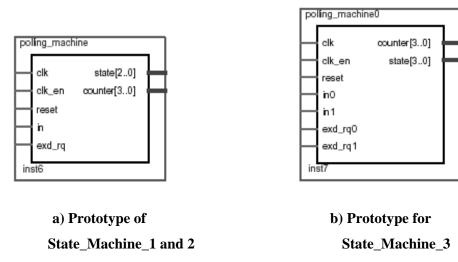

| Figure 4-4 Relationship Between the Data FIFO and Packet Length FIFO    | 65   |

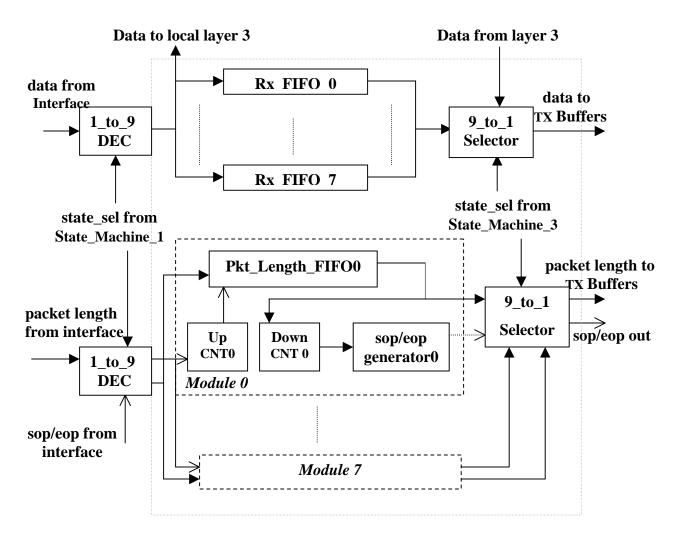

| Figure 4-5 Receive Buffers Block Diagram                                | 66   |

| Figure 4-6 Single Receive Buffer Block Symbol, Prototype name: rx_frame_reg                                                               | 67                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Figure 4-7 Label Remover Block Symbol, Prototype name: label_remover                                                                      | 70                                  |

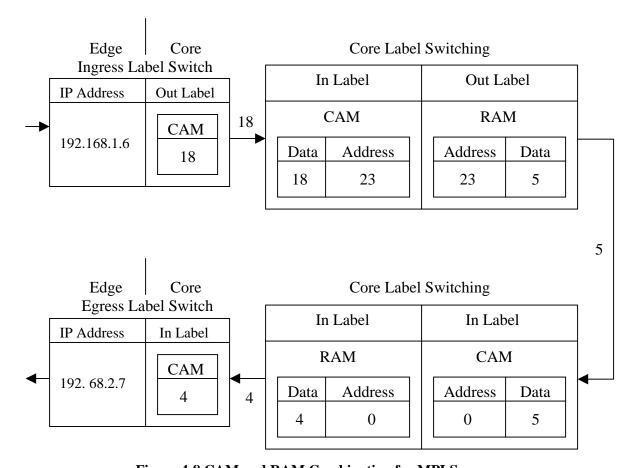

| Figure 4-8 CAM and RAM Combination for MPLS                                                                                               | 72                                  |

| Figure 4-9 Lookup Table Block Symbol, Prototype name: lookup_table                                                                        | 75                                  |

| Figure 4-10 Label Binder Block Symbol, Prototype name: label_binder                                                                       | 76                                  |

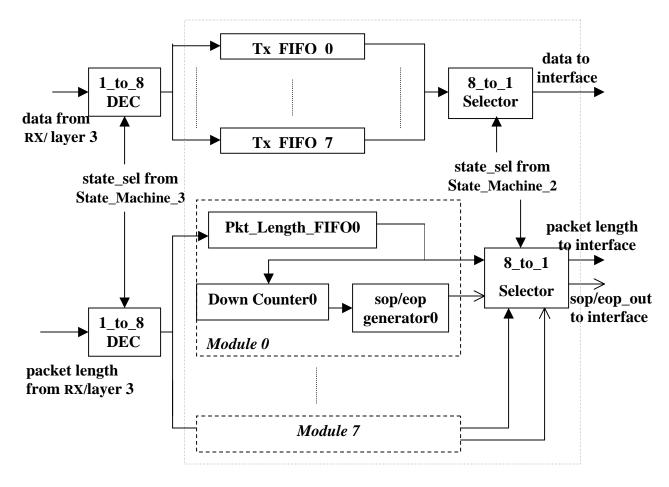

| Figure 4-11 Transmit Buffers Block Diagram                                                                                                | 77                                  |

| Figure 4-12 Single Transmit Buffer Block Symbol, Prototype name: tx_frame_reg                                                             | 78                                  |

| Figure 5-1 MPLS Edge Node Hardware Architecture                                                                                           | 82                                  |

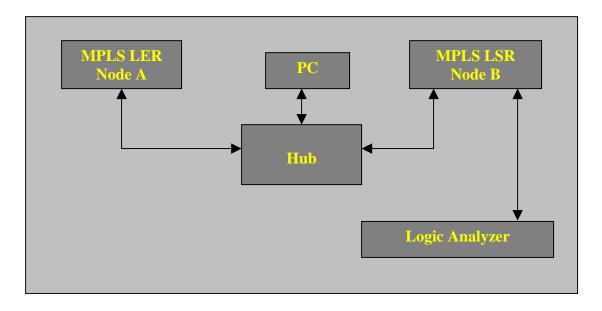

| Figure 5-2 Test Bed Architecture                                                                                                          | 83                                  |

| Figure 5-3 The Mother Board                                                                                                               | 84                                  |

| Figure 5-4 The Daughter Card                                                                                                              | 85                                  |

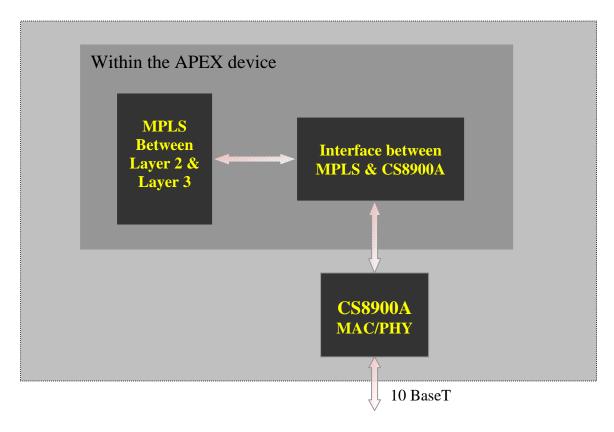

| Figure 5-5 Block Diagram of the Interface Between MPLS and MAC                                                                            | 89                                  |

| Figure 5-6 Flow Chart of Interface Functions                                                                                              | 91                                  |

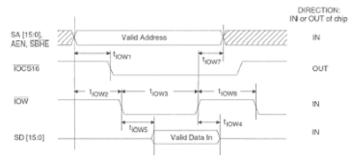

| Figure 5-7 16-bit I/O Write to the CS8900A                                                                                                | 93                                  |

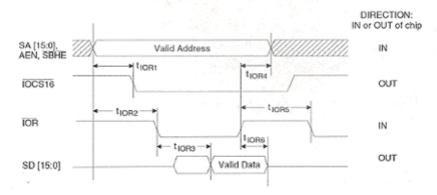

| Figure 5-8 16-bit I/O Read from the CS8900A                                                                                               | 94                                  |

| Figure 5-9 Interface Module Block Symbol, Prototype Name: mpls_mac_interface                                                              | 95                                  |

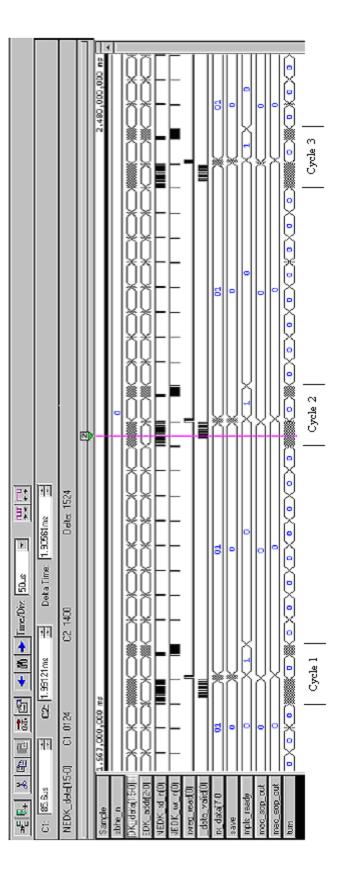

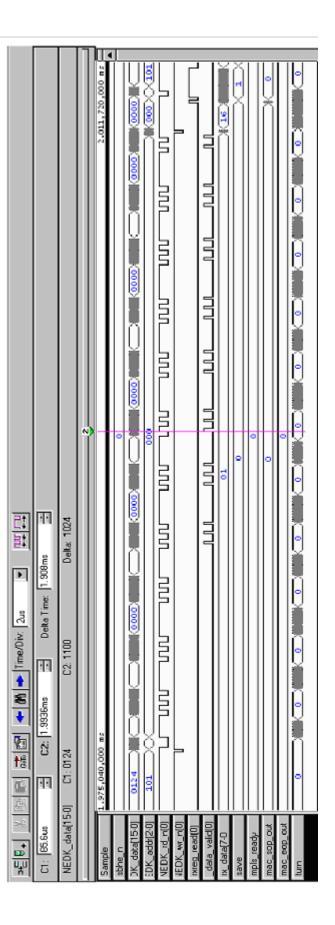

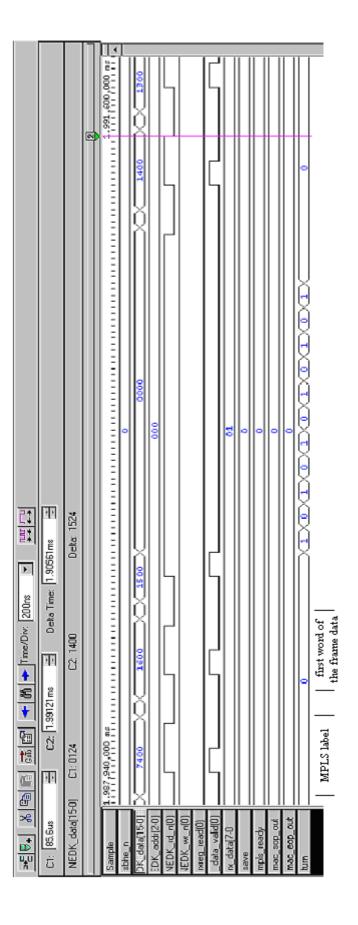

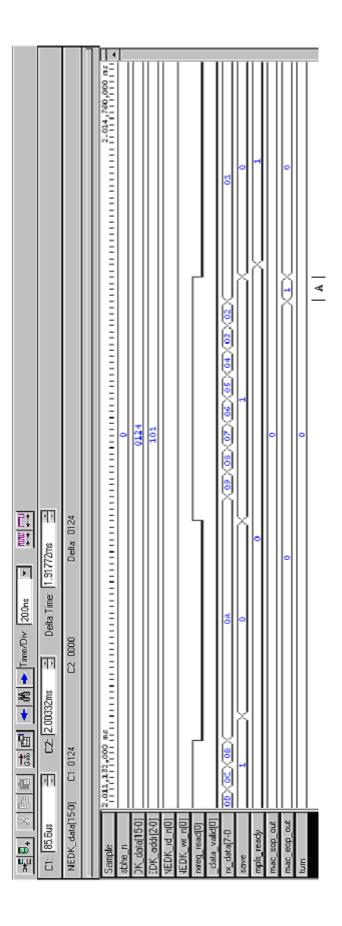

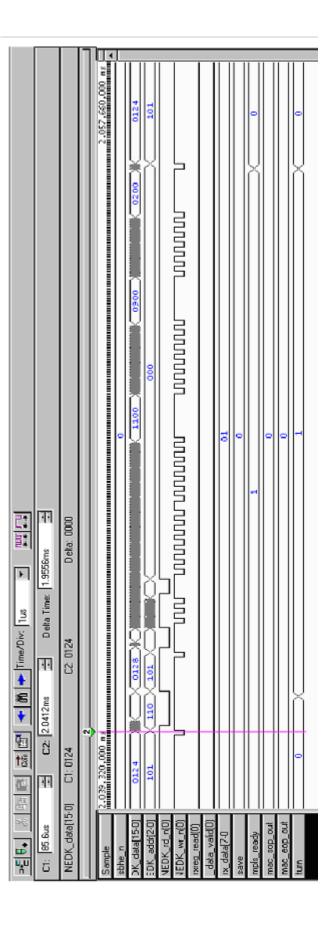

| Figure 6-1 Receive_&_Ttransmit.                                                                                                           | .106                                |

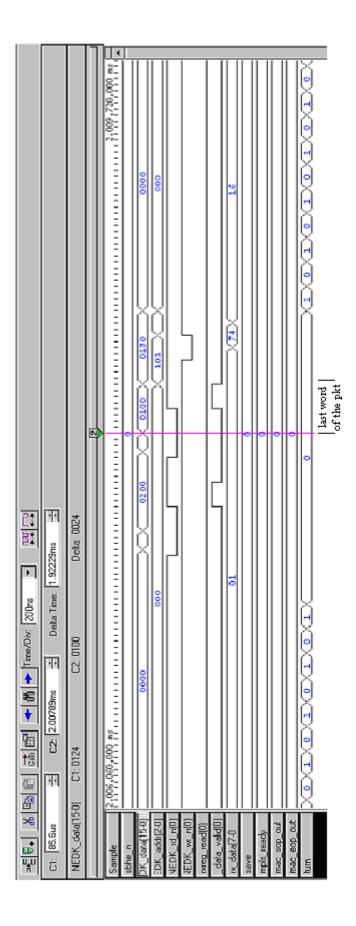

| Figure 6-2 Receive_Full.                                                                                                                  | 110                                 |

| Figure 6-3 Receive_0.                                                                                                                     | 111                                 |

| Figure 6-4 Receive_1                                                                                                                      | 112                                 |

| Figure 6-5 Receive_2.                                                                                                                     | 113                                 |

|                                                                                                                                           |                                     |

| Figure 6-6 Receive_3.                                                                                                                     | 114                                 |

| Figure 6-6 Receive_3.  Figure 6-7 Receive_4.                                                                                              |                                     |

|                                                                                                                                           | 115                                 |

| Figure 6-7 Receive_4.                                                                                                                     | 115<br>.117                         |

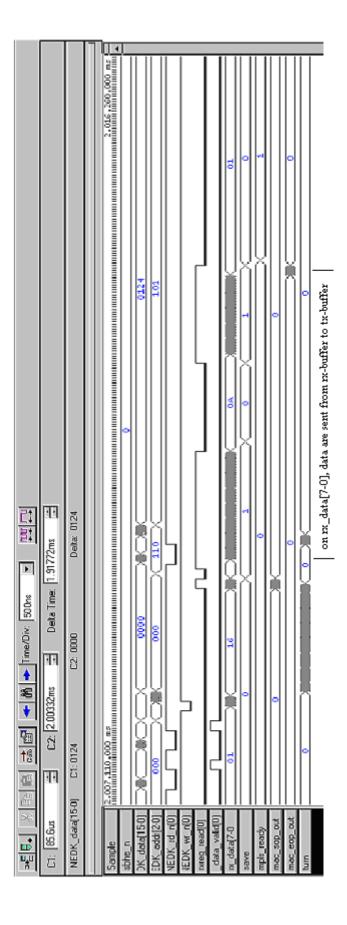

| Figure 6-7 Receive_4.  Figure 6-8 Save_to_MPLS_Full.                                                                                      | 115<br>.117<br>.118                 |

| Figure 6-7 Receive_4.  Figure 6-8 Save_to_MPLS_Full.  Figure 6-9 Save_to_MPLS_0.                                                          | 115<br>.117<br>.118                 |

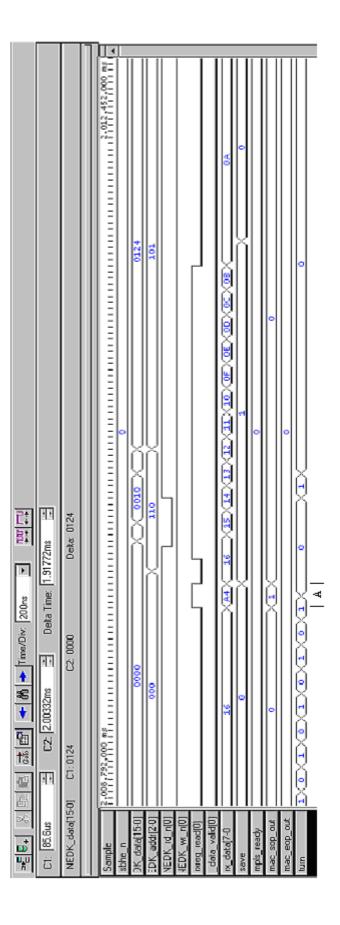

| Figure 6-7 Receive_4.  Figure 6-8 Save_to_MPLS_Full.  Figure 6-9 Save_to_MPLS_0.  Figure 6-10 Save_to_MPLS_1.                             | 115<br>.117<br>.118<br>.119         |

| Figure 6-7 Receive_4.  Figure 6-8 Save_to_MPLS_Full.  Figure 6-9 Save_to_MPLS_0.  Figure 6-10 Save_to_MPLS_1.  Figure 6-11 Transmit_Full. | 115<br>.117<br>.118<br>.119<br>.123 |

# LIST OF TABLES

| Table 5-1 CS8900A I/O Port Descriptions          | 87  |

|--------------------------------------------------|-----|

| Table 5-2 a) CS8900A Configuration for Node A    | 97  |

| Table 5-2 b) CS8900A Configuration for Node B    | 98  |

| Table 5-3 Network Setting                        | 99  |

| Table 5-4 a) Node A Test Path Selection          | 99  |

| Table 5-4 b) Node B Test Path Selection          | 99  |

| Table 5-5 a) Node A Lookup Table Configuration   | 100 |

| Table 5-5 b) Node B Lookup Table Configuration   | 101 |

| Table 6-1 Bit Definition for SelfStatus Register | 106 |

| Table 6-2 Bit Definition of RxEvent register     | 107 |

| Table 6-3 Bit definition of TxEvent Register     | 119 |

| Table 6-4 Bit definition of TxCommand Register   | 119 |

| Table 6-5 Bit definition of Bus Status Register  | 120 |

## LIST OF ABBREVIATIONS

ATM Asynchronous Transfer Mode

BGP Boarder Gateway Protocol

CoS Class of Service

CRC Cyclic Redundancy Check

CR-LDP Constraint-based Routing LDP

DA Destination Address

DiffServ Differentiated Services

DLCI Data Link Connection Identifier

DMA Direct Memory Access

ESB Embedded System Block

FEC Forward Equivalent Class

FPGA Field Programmable Gate Array

GPS General Processor Sharing

HDL Hardware Description Language

HDLC High Level Data Link Control

HOLB Head of Line Block

IETF Internet Engineering Task Force

IGP Interior Gateway Protocol

IP Internet Protocol

ISA Industry Standard Architecture

ISP Internet Service Provider

LDP Label Distribution Protocol

LER Label Edge Router

LFIB Label Forwarding Information Base

LIB Label Information Base

LSB Left Significant Bit

LSP Label Switched Path

MPLS Multi-Protocol Label Switching

OSI Open System Interconnection

OSPF Open Shortest Path First

PCI Peripheral Component Interconnection

PIM Protocol-Independent Multicast

PING A utility to determine whether a specific IP address is accessible. Often believed

to be short for Packet Internet Groper

PNNI Private Network-to-Network Interface

POS Packet Over SONET/SDH

PPP Point to Point Protocol

QoS Quality of Service

RHFE Reconfigurable Hardware Functional Element

RISC Reduced Instruction Set Computer

RPS Real Packet Switching

RSVP Resource Reservation Setup Protocol

SA Source Address

SDH Synchronized Digital Hierarchy

SONET Synchronous Optical Network

SOPC System-On-a-Programmable-Chip

TCP Transmission Control Protocol

ToS Type of Service

UDP User Datagram Protocol

UD-WRR Unit Data Weighted Round Robin

VCI Virtual Circuit Identifier

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VPI Virtual Path Identifier

VPN Virtual Private Network

WFQ Weighted Fair Queue

# **Chapter 1 Introduction**

#### 1.1 Motivation

Over the last ten years, the Internet has evolved into a ubiquitous network. New extranet services, network-enabled intranet applications, and much more powerful PCs are turning the Internet rapidly into an electronic agent for information retrieval, commerce, entertainment, and communication. As well, there is exponential growth in the number of users who have diverse demands for more reliable and differentiated services. Therefore, Class of Service (CoS) and Quality of Service (QoS) issues must be addressed in order to support the diverse requirements of the wide range of new applications and network users. Both large and small Internet Service Providers (ISPs) constantly face the challenges of adapting their networks to accommodate new services and meeting more diverse customer requirements. In many situations, software updates are not enough to achieve this goal. Meanwhile, due to extremely high costs, physically replacing or upgrading network infrastructure constantly is not feasible, either. As a result, Multi-Protocol Label Switching (MPLS) that can address all these issues was proposed.

MPLS [2, 3] is a direct and elegant industrial solution to improve the controllability, efficiency, and reliability of the current worldwide IP networks. It gives the network better extensibility and also provides more flexibility to routing services, which means that it allows the addition of new routing services without changing the original packet-forwarding mode. MPLS is not confined to any particular link layer technology; it can use any medium to transmit packets between any two entities of the network layer. However, though MPLS is now taken as a crucial standard technology that offers new capabilities for large-scale IP networks, the concept of label switching was originally proposed as a way of improving the forwarding speed of routers only.

Routers can easily become places where network bottlenecks are formed, and fast node processing speed is extremely important to avoid these bottlenecks to achieve good network performance. Meanwhile, from the industrial point of view, the flexibility that can reduce the cost when new services need to be added to the router later is of the same importance [7, 9]. Naturally, routers that are both fast and flexible are desired, but these two characteristics are generally considered a contradiction in terms. The reason is that maintaining high throughput requires fast but fixed-configuration application specific integrated circuits (ASICs) while flexibility requires slower though flexible configuration of general-purpose processors. Is there an ideal compromise? The answer is positive. The solution is a reconfigurable router that is fast and flexible at the same time, by integrating the best features of both hardware and software processing through the efficient use of Field-Programmable Gate Array (FPGA) technology, hardware description language, and hardware/software partitioning and scheduling technique. Detailed reasons for why FPGA instead of ASIC or software technologies are chosen in this project is fully described in section 1.3.2

In the project described by this thesis, a partial fulfillment FPGA for the next generation fully reconfigurable IP routers adopting MPLS is implemented. The thesis is organized as follows. Chapter 1 presents a general introduction to MPLS and typical router architecture, then clearly explains why a reconfigurable router is desirable and realizable, and ends with a brief overview of some current commercial router products. Chapter 2 gives a more detailed literature review on MPLS standards. Chapter 3 begins with a brief description of the switch/router evolution over the years, then talks about the software/hardware partitioning for MPLS implementation, finally presents the architecture design proposal for a fundamental reconfigurable MPLS router and an improved multiple queue scheduling policy, Unit Data Weighted Round Robin. Chapter 4 depicts the full details of the MPLS logic circuit design completed within a FPGA device in this project. Chapter 5 introduces the test equipment first, then presents the test methodology development and the interface design, finally presents the test parameter selection. Chapter 6 deals with practical test procedures and result demonstration and analysis. At the end of the thesis, conclusions for work having been done and suggestions for future work are given.

#### 1.2 What is MPLS?

MPLS [4, 5] provides a new technical foundation for today's multi-user, multi-service IP-based networks and can effectively address the bandwidth and quality of service requirements. According to the TCP/IP model, there are 4 layers: the transportation layer (layer 4), the network layer (layer 3), the logic link layer (layer 2) and the physical layer (layer 1). MPLS can be deployed directly over current ATM-based wide area networks without any hardware modification on ATM switches. Meanwhile, by inserting an MPLS shim layer between layer 2 and layer 3, MPLS can be used over different layer 2 protocols other than ATM to transport different Layer 3 protocols such as IPv6, IPX, or AppleTalk in addition to Ipv4 traffic.

With software or hardware implementation, MPLS supports service differentiation by using traffic-engineered path setup, helps achieve fine-grained service-level guarantees and incorporates provisions for constraint-based and explicit path setup. MPLS can improve and simplify packet-forwarding performance by enabling routing in Layer 2 switching that operates at wire-line speeds with hardware implementation. MPLS also helps in building interoperable networks due to its layer 2 independency and in building scalable Virtual Private Networks (VPNs) due to its traffic-engineering capability.

MPLS is significantly different from the hop-by-hop processing methods used by traditional networks. The essence of MPLS is the generation of a 'label' that acts as a shorthand representation of an IP packet's header. The MPLS ingress edge router selects the appropriate label that is to be inserted between layer 2 and layer 3 headers after it analyzes the contents of the packet's IP header. Part of the great power of MPLS comes from the fact that, compared to conventional IP routing, this analysis can be based on more than just the destination address carried in the IP header. The label is a short, fixed length, locally significant identifier, which distinguishes the route the packet should take to reach the required egress node of the MPLS-enabled network. Each label corresponds to a Forward Equivalence Class (FEC), which is a group of packets that are forwarded in the same manner (i.e., over the same path, with the same forwarding treatment). FECs can be defined at different levels of granularity. Each

Label Switching Router (LSR) must keep track of how packets should be forwarded by containing this FEC information in a Label Information Base (LIB) that includes FEC-to-label bindings. Conventional routing protocols, such as OSPF, BGP and PIM, provide the LSRs with the mapping between the FEC and the next hop addresses.

The basic operation of an MPLS network involves switching that is based on these labels, instead of the IP headers. Full IP header analysis occurs at every node in conventional IP routing, while in an MPLS cloud this analysis occurs only once at the network edge when the label is assigned. When a labeled packet is received at an LSR, the input port and label information are read and the output port is determined. Then an outgoing label in context for the next hop's label switching operation replaces the incoming label.

The MPLS standard allows for MPLS-enabled networks to be nested within each other. To accommodate this nesting, packets may have multiple labels, which form a label stack. The number of labels that need to be stored in a LSR depends on the type of label mapping policy that is used in the MPLS network.

A standard label distribution method is required when a LSR assigns a label to a particular FEC and conveys this information to its peers in the MPLS network. The MPLS standard does not dictate which signaling protocol should be used for such label distribution. The most popular protocol is called Label Distribution Protocol (LDP), which uses TCP and UDP over layer 4 to send messages; however, other signaling protocols do exist, such as the Resource Reservation Protocol (RSVP). In addition, extensions to LDP and RSVP have been created and are currently being considered to support traffic engineering. They are Constraint-based Routing LDP (CR-LDP) and RSVP Traffic Engineering (RSVP-TE) respectively.

In MPLS, a Label Switched Path (LSP) can be created by using different signaling protocols mentioned above, conforming to explicit network administrator's requirements. A LSP is functionally equivalent to a virtual circuit and is defined by a set of labels that are used from the ingress of the MPLS domain to the egress.

One of the most important advantages of MPLS is to allow traffic flows to be moved away from the shortest path calculated by say, the Interior Gateway Protocol (IGP), and onto potentially less congested physical paths across the network when necessary, which results in better utilization of the network.

Another advantage is that, MPLS is beneficial when realizing differentiated services (DiffServ). Users are motivated to use the Internet as a public transport for a number of different applications ranging from traditional file transfer to delay-sensitive services such as real time voice and video. To meet such diverse requirements, not only traffic engineering techniques but also traffic classification technologies have to be adopted. There are two approaches to support MPLS-based class of service forwarding. The first approach is that traffic flowing through a particular LSP can be queued for transmission on each LSR's outbound interface on the setting of the precedence bits carried in the MPLS header. The second approach is that an Internet Service Provider can provide multiple LSPs between each pair of edge LSRs. Each LSP can be traffic engineered to provide different performance and bandwidth guarantees. The head end LSR could place high-priority traffic in one LSP, medium-priority traffic in another LSP, best-effort traffic in a third LSP, and less-than-best-effort traffic in a fourth LSP. MPLS offers tremendous flexibility in the different types of services. The precedence bits are used to classify packets into one of several classes of service.

MPLS is also valuable in providing a more complete separation between inter- and intra-domain routing. This improves the scalability of routing processes and, in fact, reduces the route knowledge required within a domain because on some networks there may be a large amount of transit traffic. Meanwhile, with a clean separation between its control and forwarding functions, MPLS can evolve each part without impacting another part, which in turn enables the network evolution easier, less costly, and less prone to errors.

The last but not the least advantage of MPLS to mention here is providing a simple solution to VPN-related issues. VPN allows the public Internet to be used as a method for connecting various networks to form a private WAN. The VPN service provider must provide data privacy and support private IP addressing use where the IP address

space overlaps other network domains. Since forwarding decisions are based on MPLS labels and not destination IP addresses, traffic between (and even within) VPNs can be easily isolated.

On the whole, MPLS provides significant improvements in the packet forwarding process by simplifying the processing, avoiding the need to duplicate header processing at every step in the path, and creating an environment that can support controlled QoS and traffic engineering.

## 1.3 Introduction to Reconfigurable Routers

In this section an introduction to the typical router architecture and an overview of today's router products are given.

#### 1.3.1 Typical Router Architecture

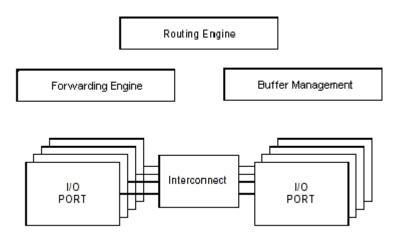

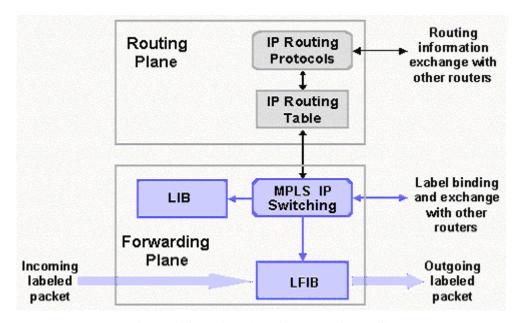

Figure 1-1 Architecture of a Typical Router

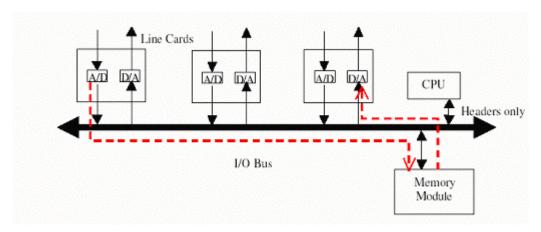

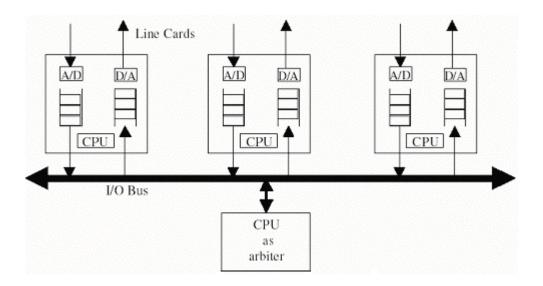

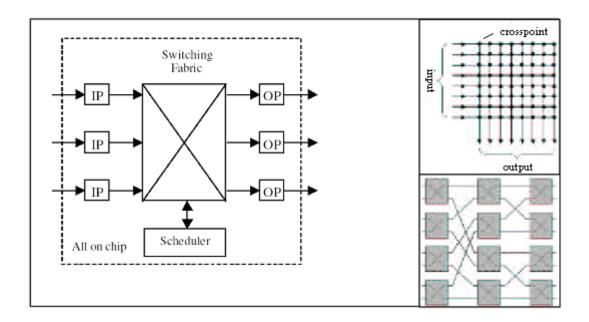

A typical router does three fundamental jobs [11, 14]. The first is to compute the best path that a packet should take through the network to its destination. This computation accounts for various policies and network constraints. The second job is to actually forward packets received on an input interface to the appropriate output interface for transmission across the network. Forwarding relies on the best-path information pre-computed in the route processor. The third job is to temporarily store

packets in large buffer memories to absorb the bursts and temporary congestion that frequently occur and to queue the packets using a priority-weighted scheme for transmission. Figure 1.1 shows the basic logical architecture of a router. The basic functional components carrying out these three jobs are named *the Routing Engine*, *the Forwarding Engine*, and *the Buffer Management system* respectively. A set of input and output ports is interconnected via some interconnection architecture.

The Routing Engine is dedicated to communicating with adjacent routers in order to build a comprehensive route database for the forwarding engine to send packets across optimum paths through the network. The routing engine runs software algorithms executing routing protocols, which enable the sharing of network status information among routers.

The Forwarding Engine examines the content of the packet's header, then searches for corresponding route information provided by the routing engine to find a match and finally direct the packet from the input port to the output port across the system's switching fabric.

If multiple packets arriving at different input ports simultaneously need to be forwarded to the same output port, a buffer must be available as a temporary waiting area in which packets queue up for transmission. The order in which they are transmitted is determined by the queuing scheduling policy pre-selected.

#### 1.3.2 Why Reconfigurability?

As a commercial infrastructure providing differentiated services, the Internet has to be constructed with routers that can meet the massive demand increases in both bandwidth and processing speed. It is very important that these core elements of any networks be extensible and reconfigurable to support the ever new, ever evolving protocols and be able to provide third-party software vendors or value-added service providers with opportunities to develop applications. While many powerful routers with high processing speeds and throughputs have been manufactured already, they are not flexible and thus make it impossible for potential new protocols and services to be added without incurring large costs.

It has been thought that the time spent to process a packet on an IP switch should not exceed 0.27 ms [39], which clearly shows that maintaining high-throughput is a problem. Some researchers (Keshav and Sharma in [8]) also note that the reduction of port cost is currently a tradeoff between application specific integrated circuits (ASICs) and general-purpose processors. In this dichotomy, the only solution that provides flexibility is the use of a general-purpose processor. However, new software technologies deployed within the router operating system with the potential of offering increased flexibility in the router may not increase its performance. Software instructions themselves ask for processing time. Thus it is not clear if these software technologies will be practical, especially considering the current problems with maintaining high port performance. As line speeds continue to rise and the upper bound on processing time continues to fall, as on-demand scheduling of hardware resources is required to assist in the development of flexible network, some solution to provide reconfigurability at the hardware layer has to be found.

One way of providing this low-level reconfigurability is through configurable computing technology. With suitable hardware-level configurable computational units, stream processing has the potential to allow packets to be processed at line speeds. It becomes more practical since reconfigurable hardware technology has made several compelling performance advances recently, identifying it as a possible solution to the reconfigurable network node problem. New reconfigurable hardware devices contain approximately 110K logic elements (millions of application logic gates), an internal clock about 420 MHz, and over 10MB of on-chip RAM.

Contemporary Field Programmable Gate Arrays, which serve as the flexible fabric in configurable computing platforms, are already being used to provide field-upgrades of firmware in some industrial and research switches ([35], [38]). FPGAs provide an intermediate operating point between the relative slowness, flexible configuration, and low cost of a general-purpose processor and the high-performance, fixed configuration, and high cost of an ASIC. A modular and configurable set of functional units can be strung together and implemented within FPGA devices quite easily. Also, it is relatively easy to add, remove, modify and interconnect modules since they can be developed

independently, which greatly simplifies the implementation of a design. It is true that the cost of modularity brings an increase in the number of gates required to implement a particular function while some computational resources available in the module may not be used at all. However, because of the significant increase in FPGA resources, this is not expected to be a problem. Before long, one could expect a reconfigurable router composed of FPGAs, custom ASICs, and custom general-purpose processors to obtain the optimal combination of performance, flexibility, and cost.

#### 1.4 Industrial MPLS Router Products Overview

The routers that power the Internet are evolving architecturally to keep pace with the escalating use of the Web and the requirement for a whole new generation of innovative, revenue-generating application services. Certain high-end router architectures that support ultra fast fiber-optic interfaces of up to 10 Gbps speeds and achieve system throughput in excess of 350 million packets per second (pps) already exist. Also, large router manufacturers claimed that they had implemented routers supporting MPLS, such as Alcatel IND, Cisco Systems, Juniper Networks, Marconi FORE Systems, etc. All these manufacturers stated that they had implemented or planned to implement both CR-LDP and RSPV-TE signaling protocols. In the following sections, these MPLS router products will be investigated according to product data sheets provided in [30] – [34].

#### 1.4.1 Cisco 12000

The major components of the 12000 Gigabit Switch Router (GSR) are the switch fabric, the gigabit route processor (GRP), and the line cards (LCs). The packet-forwarding functions are performed by each of the LCs. Each LC performs an independent lookup of a destination address for each datagram received on a local copy of the forwarding table, and the datagram is switched across a crossbar switch fabric to the destination LC.

At the heart of the Cisco 12000 GSR is a multi-gigabit crossbar switch fabric. The switch fabric includes two card types: switch-fabric cards (SFCs) and clock and scheduler cards (CSC). The CSC handles requests from LCs, issues grants to access the

fabric, and provides a reference clock to all the cards in the system to synchronize data transfer across the crossbar. The SFCs receive the scheduling information and clocking reference from the CSCs and perform the switching functions.

The GRP is dedicated to determining the network topology and calculating the best path across the network. It creates and maintains the routing table (up to one million route entries), also distributes and updates express forwarding (EF) tables on the LCs and maintains copies of the tables of each LC for card initialization.

Line cards connect the GSR to other devices via electrical or optical media. The LCs are designed for the transmission of IP packets over Dynamic Packet Transport (DPT), PPP, Frame Relay, Packet over Sonet/SDH (POS) or ATM interfaces. The features and functions of the LCs are interface-specific.

The system of this series delivers scalable traffic engineering features by adopting Multi-protocol Label Switching (MPLS). Meanwhile, the design of this series supports virtual output queues (VOQs) that eliminate head-of-line blocking (HOLB) and increase overall system efficiency. Micro programmable application-specific integrated circuits (ASICs)-based queuing provides line speed forwarding for unicast and multicast traffic that fills SONET/SDH transmission facility.

#### 1.4.2 JUNOS M40

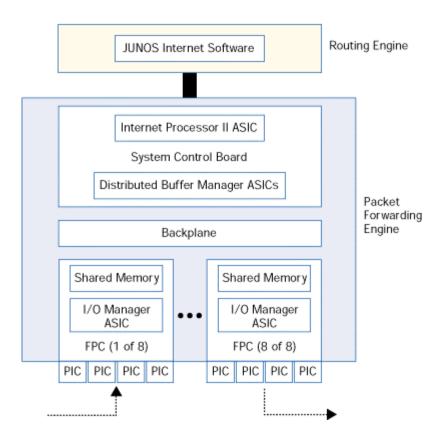

As shown in Figure 1-2, there are two key components of the M40 architecture: the packet forwarding engine (PFE) and the routing engine. The PFE is responsible for packet forwarding performance. It consists of the flexible PIC concentrators (FPCs), physical interface cards (PICs), system control board (SCB), and state-of-the-art ASICs. The routing engine maintains the routing tables and controls the routing protocols. It consists of an Intel-based PCI platform running JUNOS software.

The M40 ASICs deliver a comprehensive hardware-based system for packet processing, including route lookups, filtering, sampling, rate limiting, load balancing, buffer management, switching, encapsulation, and de-encapsulation functions. To

ensure a non-blocking forwarding path, all channels between the ASICs are oversized, dedicated paths.

The Internet Processor II ASIC delivers high-speed forwarding performance with advanced IP services, such as filtering and sampling, enabled. The distributed buffer managers ASICs allocate incoming data packets throughout shared memory on the FPCs.

Each FPC is equipped with an I/O Manager ASIC that supports packet parsing, packet prioritizing, and queuing. The media-specific ASICs perform physical layer functions, such as framing. Each PIC is equipped with an ASIC or FPGA that performs control functions tailored to the PIC's media type.

Figure 1-2 Logical View of M40 Architecture

The packet-forwarding engine (PFE) provides Layer 2 and Layer 3 packet switching, route lookups, and packet forwarding. The PFE supports ASIC-based features, for example, class-of-service features include rate limiting, classification and priority queuing, etc.

The enhanced flexible PIC concentrators (FPCs) house PICs and connect them to the rest of the PFE. Each FPC supports up to four PICs in any combination. Each FPC contains shared memory for storing data packets received. The physical interface cards (PICs) provide a complete range of fiber optic and electrical transmission interfaces to the network. The system control board (SCB) performs sampling, filtering, and packet forwarding decisions. It processes exception and control packets, monitors system components, and controls FPC resets.

The routing engine maintains the routing tables and controls the routing protocols, as well as the JUNOS software processes that control the router's interfaces, the chassis components, system management, and user access to the router. These routing and software processes run on top of a kernel that interacts with the PFE.

#### 1.4.3 Alcatel 7670 Routing Switch Platform

The Alcatel 7670 Routing Switch Platform (RSP) is an MPLS-enabled ATM core switch designed for networks, integrating ATM multi-service capability and MPLS/IP switching into a unified scalable platform.

Per-VC queuing and shaping at ingress and egress, and buffer management with frame discard are adopted. All ATM service categories and most IP routing features are supported. To provide MPLS/IP, the switch platform can act as both edge LSR and core LSR and support Permanent LSP (P-LSP) and signaled LSP (S-LSP). The switch supports point-to-point and point-to-multipoint PVCs and SVCs, point-to-point SPVCs. Since Alcatel 7670 is an ATM switch, line cards are designed mainly for optical interfacing.

#### 1.4.4 Marconi ASX4000

The ASX-4000 is a backbone switch that features the architecture to support low speed multi-service connections including ATM, Frame Relay DSL, Circuit Emulation and Ethernet. With the IP routing (IPR) module, the ASX-4000 can also operate as an MPLS gateway device.

#### 1.4.5 Conclusion: New Products Desired

All the products mentioned above were designed to have redundancy in all key system components---processors, switch fabric, line cards, and power---to minimize network disruption in the event of a failure. This provides some kind of flexibility since components can be added or removed without service disruption.

All of these companies claimed that MPLS was supported. However, most of them stated this with only one or two sentences in their product data sheets, just as when they stated they could of course support software implemented BGP and OSPF, etc. No description of streamlined hardware dedicated for label switching was provided. This vagueness might due to the companies' confidential policy, but might also due to the more likely fact that most of them implemented MPLS in software. Only Marconi described very briefly that MPLS was supported by an IP routing module and this simple function description certainly led to the conclusion that it was implemented in software. With a powerful microprocessor, it may be realistic and meaningful to implement MPLS in software, providing both flexibility and better QoS guarantees. However, software implementation cannot take full advantages of what MPLS brings for layer 3 routing, which is critical to gain the overall faster processing speed at network nodes.

Some ATM switch products seemed to have fulfilled MPLS in hardware. But MPLS hardware implementation over ATM is quite straightforward and totally different from the implementation done over other layer 2 protocols. There is no need to do label binding or removing physically over an ATM based network when realizing MPLS, since the labels can reside in VPI and VCI fields that already exist in the ATM frame structure. However, a shim layer to hold MPLS labels is necessary if MPLS is to be deployed over PPP, Ethernet and Frame Relay networks in hardware, because their

frame structures contain no or not enough existing fields for MPLS labels to reside in correspondingly.

Finally, these companies all based their router design on powerful ASICs, which could not adopt new system parameters when needed, such as buffer space, routing table scale, etc; let alone the extensibility for potential protocols or other value added features that people want the routers to support in the future without any hardware modification or replacement. Generally speaking, routers existing in today's market are not reconfigurable at all.

Since almost all router manufacturers tend to stress the MPLS features of their products to make their routers look more competitive in the market, it can be inferred that MPLS routers are really the trend. By implementing the MPLS functions in hardware and making the router architecture reconfigurable, this project is meaningful.

# **Chapter 2 Multi-Protocol Switching**

### 2.1 Main MPLS Components

An MPLS node can obtain all the information it needs to forward a packet as well as determine resource reservations needed by a class of traffic using a single memory access through its specially designed software and hardware components. In this section the main MPLS components are introduced.

#### • LSRs and LERs

There are two categories of node equipments that participate in the MPLS working mechanisms. One is called the Label Switching Router (LSR), which is a high-speed MPLS-enabled router in the core of an MPLS domain; the other is the Label Edge Router (LER), which operates at the boundary between access networks and the MPLS domain. LERs can perform all the functions executed by LSRs besides handling issues of packets' entering and leaving the MPLS domain.

With the aid of an appropriate label signaling protocol, LSRs cooperate to establish Label Switched Paths (LSPs) and perform high-speed switching of the data traffic according to MPLS labels attached to packets. A fundamental step in label switching is that LSRs have to agree on the MPLS labels they use to forward traffic. They come to this common understanding by using the dedicated Label Distribution Protocol (LDP), Constraint Routing-Label Distribution Protocol (CR-LDP) or extensions to other protocols, such as PIM, BGP, RSVP. Since the current Internet consists of all kinds of networks which may not support MPLS traffic but only traditional IP traffic, to make the backbone MPLS router backwards compatible with other ordinary routers, LSRs are also able to forward native Layer 3 packets and routing packets without MPLS labels.

LERs support multiple ports connected to dissimilar networks (such as frame relay, ATM, and Ethernet). A LER can act as an ingress node or an egress node or both, for the MPLS domain. When acting as an ingress node, the LER forwards the traffic on to

the MPLS network after establishing LSPs using the label signaling protocol; when acting as an egress node, the LER distributes the traffic back to the access networks. The two very important MPLS functions, the label assignment and removal as traffic enters or exits an MPLS domain, take place at ingress LERs and egress LERs respectively. Like all LSRs, LERs can also perform a conventional IP forwarding function.

#### • Forwarding Equivalent Class (FEC)

A forwarding equivalent class is defined for a set of packets that receive the same treatment during transmission. In the context of MPLS, a packet is assigned to a FEC when it enters the MPLS network. The ingress router may use, in determining the FEC assignment, any information it has about the packet, even if that information cannot be gleaned from the network layer header, which is why labels that represent corresponding FECs contain considerably more information than just destination/source addresses for longest prefix match in IP routing. For example, a packet that enters the network at a particular router can be labeled differently than the packet from/to the same source/destination entering the network at a different router.

Insofar as the forwarding decision is concerned, different packets that get mapped into the same FEC are indistinguishable. All packets that belong to a particular FEC and travel from a particular node will follow the same path (or if certain kinds of multipath routing are in use, they will all follow one of a set of paths associated with the FEC).

#### Labels and Label Bindings

Since each FEC has associated labels according to some policy, once a packet is classified as a new or existing FEC, the associated fixed length labels are assigned to the packet. The events that result in such label assignments can be either *data-driven bindings* or *control-driven bindings*. The latter one is preferable because of its advanced scaling properties that can be used in MPLS.

Policies according to which label assignment decisions are made may be based on forwarding criteria such as destination unicast routing, traffic engineering, multicast, virtual private network (VPN), and QoS. Under some circumstances identifiers for underlying data link layers (such as frame relay or ATM) can be used directly as MPLS labels, such as Data Link Connection Identifiers (DLCIs) in the case of frame-relay networks or Virtual Path Identifiers (VPIs)/Virtual Channel Identifiers (VCIs) in case of ATM networks.

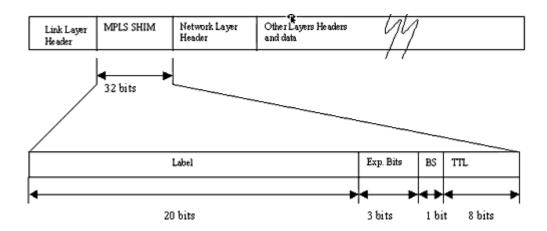

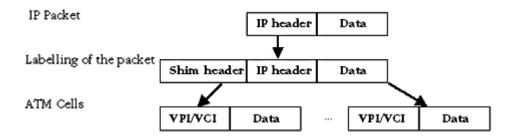

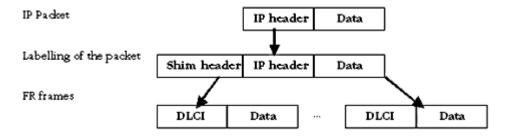

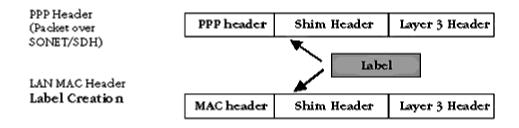

The generic label format is illustrated in Figure 2-1. Figures for different label formats are shown in next page. If layer 2 is ATM, the label is placed into the VPI/VCI field of the ATM cell header, as shown in Figure 2-2. Similarly, if layer 2 is frame relay, the label can be placed into the data link connection identifier (DLCI) field in the frame header, as shown in Figure 2-3. If Ethernet or point-to-point protocol (PPP) is running in layer 2, a shim header is inserted between the layer 3 header and the layer 2 header. The shim header contains the MPLS label, as shown in Figure 2-4. Support for the shim header requires that the sending router have a way to indicate to the receiving router that the frame contains a shim header. This is facilitated differently in various technologies.

Figure 2-1 MPLS Generic Label Format [1]

A set of labels, in its simplest form, identifies the path a packet should traverse. Once a packet has been labeled, the rest of the journey of the packet through the backbone is based on label switching. At the edge router, the MPLS label will be

attached to the front of layer-3 header before the packet is transferred to Layer-2 for data link layer header encapsulation. Then each of the flowing receiving LSRs examines the packet for its label content to determine the next hop and then assigns a new label to replace the old one. The label values are of local significance only, which means they pertain only to hops between neighboring LSRs.

Figure 2-2 ATM as the Data Link Layer [1]

Figure 2-3 Frame Relay as the Data Link Layer [1]

Figure 2-4 Point-to-Point (PPP)/Ethernet as the Data Link Layer [1]

MPLS defined two categorized label scopes for the uniqueness of different FEC-label bindings at each LSR. When a LSR can tell which peer-LSR adopts the particular

label value, it can use the "per-interface label space", which indicates from the name "per-interface" that the label ranges are associated with interfaces. Multiple label pools are defined for interfaces, and the labels provided on those interfaces are allocated from the separate pools. The label values provided on different interfaces could be the same. Otherwise, the labels must be unique over the LSR that has assigned them, and the LSR is said to use a "per-platform label space". The labels are allocated from a common pool and no two labels distributed on different interfaces have the same value.

#### Label Creation and Control

MPLS defines several methods to create labels: topology-based method uses normal processing of routing protocols (such as OSPF and BGP); request-based method uses processing of request-based control traffic (such as RSVP); traffic-based method uses the reception of a packet to trigger the assignment and distribution of a label. The topology- and request-based methods are examples of control-driven label bindings, while the traffic-based method is an example of data-driven bindings.

Also, there are two ways to control the label creation. In the *independent* mode, an LSR recognizes a particular FEC and makes the decision to bind a label to the FEC independently to distribute the binding to its peers. The new FECs are recognized whenever new routes become visible to the router. In the *ordered* mode, an LSR binds a label to a particular FEC if and only if it is the egress router or it has received a label binding for the FEC from its next hop LSR. This mode is recommended for ATM–LSRs.

#### Label Stack

More than one label header can be attached to a single packet and are managed by the label stack mechanism that allows for hierarchical operation in the MPLS domain. There is a stack bit in a standard MPLS label helping to implement label stacking. The label is indicated to be at the bottom of the stack if the stack bit contained within it is 1. All stack bits in other labels are set to 0. In packet-based MPLS, the top of the stack appears right after the link layer header, and the bottom of the label stack appears right before the network layer header. Packet forwarding is accomplished using the label

values of the label on the top of the stack. The stack bit becomes one when the corresponding label moves to the top of the stack.

Basically, tunneling operation can be facilitated by adopting the label stack mechanism, which allows MPLS to be used simultaneously for routing between individual routers both within an Internet service provider (ISP) and at a higher domain-by-domain level. Each level is indicated by a label in the stack that pertains to some hierarchical level.

#### Label Merging

Resource usage can be increased if different traffic flows can be merged together and switched at a LSR when possible. This is known as stream merging or aggregation of flows. It can be done when the incoming streams of traffic are from different interfaces but toward the same final destination; or when traffic streams have to travel a same period of journey before they can reach their different final destinations separately. Label merging can be achieved by using a common outgoing label for several different incoming labels.

If the underlying transport network is an ATM network, LSRs could employ virtual path (VP) or virtual channel (VC) merging. In this scenario, cell-interleaving problems, which arise when multiple streams of traffic are merged in the ATM network, need to be avoided.

#### Label Retention

There are two modes defined in MPLS for the treatment of label bindings received from LSRs that are not the next hop for a given FEC. They are *liberal* mode and *conservative* mode.

In the former mode, the bindings between a label and an FEC received from LSRs that are not the next hop for a given FEC are discarded. This mode requires an LSR to maintain fewer labels and thus is recommended by IETF.

In the latter mode, the bindings between a label and an FEC received from LSRs that are not the next hop for a given FEC are retained. This mode allows for quicker adaptation to topology changes and switching of traffic to other LSPs in case of such changes, but it requires larger memory at each MPLS node.

#### Label Forwarding Algorithm

Label swapping is the base on which packet switching is performed in a MPLS domain. MPLS uses only a label swapping based forwarding algorithm to do packet switching for all traffic types such as unicast, multicast, and unicast packets with ToS bits set, which conventionally require multiple forwarding algorithms.

Each MPLS node maintains a Label Information Base (LIB). Most frequently used labels are formed into a smaller Label Forwarding Information Base (LFIB) for actual packet switching. Label values are extracted from the label field found in incoming packets and used as an index in the LFIB. After a match is found, the MPLS node replaces the label in the packet with the outgoing label from the subentry and sends the packet over the specified outgoing interface to the next hop specified by the subentry. If the subentry specifies an outgoing queue, the MPLS node places the packet in the specified queue. If the MPLS node maintains multiple LFIBs for each of its interfaces, it uses the physical interface on which the packet arrived to select a particular LFIB, and then performs label swapping according to this LFIB.

#### • Label-Switched Paths (LSPs)

Through an MPLS network, a traffic path along which packets belonging to a certain FEC travel is specifically defined over a set of LSRs prior to data transmission and is named the Label-Switched Path. MPLS allows a hierarchy of labels known as the label stack. It is therefore possible to have different LSPs at different levels of labels for a packet to reach its destination. The LSP setup for an FEC is unidirectional in nature, which means the return traffic must take another LSP. MPLS provides the following two options to set up an LSP

Hop-by-hop routing/Independent control--- This methodology is similar to that currently used in IP networks. Each LSR uses any available routing protocols, such as OSPF or ATM PNNI (Private Network-to-Network Interface), to independently select the next hop for a given FEC.

Explicit routing (ER)/Ordered control--- This methodology eases traffic engineering throughout the network, and differentiated services can be provided using flows based on specific service level policies or network management methods. The ingress LER specifies the list of nodes through which the ER–LSP traverses and then propagates such information to other nodes contained in the list. This kind of LSP could be non-optimal, say, not the shortest, because its primary goal is to ensure QoS to the data traffic through appropriate resources allocation and reservation along the path.

The hop-by-hop routing method provides faster convergence and establishment of LSPs due to the fact that label bindings can be established and advertised at any time by the LSR, while explicit routing method introduces the delay of waiting for messages to propagate in order across the network before the LSP can be established. However, the latter provides a better traffic engineering control and better loop prevention capabilities. And the good thing is, these two types of LSP establishments may coexist on the same network without any special considerations for architecture or interoperability issues.

#### • Label Distribution Protocol

For label distribution, MPLS architecture allows several signaling methods, which are either stemmed from existing routing protocols or newly proposed ones. For example, Border Gateway Protocol (BGP) has been enhanced to piggyback the label information within the contents of the protocol for external (like between VPNs) label exchange. Another currently used protocol RSVP has also been extended to support piggybacked exchange of labels and becomes RSVP-TE. Meanwhile, IETF has defined a new protocol known as the label distribution protocol (LDP) dedicated for MPLS label signaling and label space management. As well, extensions captured in the constraint-based routing LDP definition have also been defined to support explicit routing based on QoS and CoS requirements. Here the LDP is introduced briefly.

LDP has a set of signaling messages destined for the distribution of label binding information to LSRs in an MPLS network. LDP peers in the MPLS network, adjacent or not, establish LDP sessions between them and exchange certain LDP messages to map FECs to labels, which, in turn, create LSPs. There are basically 11 types of LDP messages, among which the most important ones are shown as below.

DISCOVERY--- used for finding LSRs and maintaining their existence.

ADJACENCY--- initialize, maintain, and shut down LDP sessions between LSRs.

LABEL ADVERTISEMENT---distribute label-binding, binding reverse and label release information by using *Label Mapping*, *Label Withdrawal and Label Release* messages respectively.

NOTIFICATION--- used for advisory and error signaling.

Due to the critical nature of the information being transferred, LDP runs on transmission control protocol (TCP) in order to ensure reliable data transport between LSRs, except for DISCOVERY messages that are run on UDP.

There are two types of label distribution strategies allowed in the MPLS architecture: *Downstream-on-Demand Mode* and *Unsolicited Downstream Mode*. The first mode allows an LSR to explicitly request a label binding for a particular FEC from its next hop. Label Request messages are used to request label mappings from downstream LSRs. Label Request Abort messages are used to abort the Label Request message during or prior to the completion of the request. The second mode allows an LSR to distribute bindings to LSRs that have not explicitly requested them.

# 2.2 MPLS Operation

When routing a packet, choosing the next hop can be thought of as a composition of two functions. The first function classifies the entire set of possible packets into a set of "Forwarding Equivalence Classes (FECs)". The second function maps each FEC to its corresponding next hop. In MPLS, the assignment of a particular packet to a particular FEC is done just once as the packet enters the network. The FEC to which

the packet is assigned is encoded as a short fixed length value known as a "label". Each data packet is "labeled" before they are forwarded. At all subsequent hops, further analysis of the accompanied label instead of the network layer header, is used to decide the next hop until the packet reaches its destination. Indicated by a sequence of labels, LSPs are established either prior to data transmission (control-driven) or upon detection of a certain flow of data (data-driven). High-speed switching of data occurs on such LSPs is possible because the fixed-length labels are inserted at the very beginning of the packet or cell and can be used by hardware to switch packets quickly between links.

MPLS brings the advantage that, not all of the traffic between a certain pair of source and destination is necessarily transported through the same path within an MPLS domain. Depending on the network congestion status and specific traffic characteristics, different LSPs could be created for packets with the same source and destination addresses but with different QoS or CoS requirement.

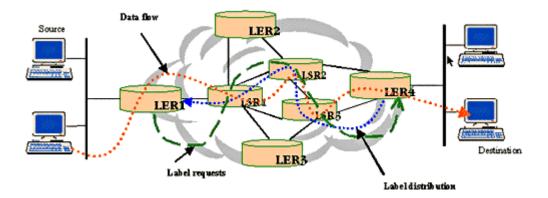

Next, the step-by-step MPLS operations that occur on the data packets as the packet is transported across the MPLS domain to its destination are illustrated with reference to Figure 2-5. The LSP is set up between LER1 (the ingress LSR) and LER 4 (the egress LSR) through two inner nodes LSR1 and LSR3. The broken red lines indicate the actual data path followed by the packet.

Figure 2-5 LSP Creation and Packet Forwarding through an MPLS Domain [3]

Step 1 Label creation and label distribution

The ingress router LER1 does not always have a label for a packet, as it may be the first occurrence of the FEC to which this packet belongs. Thus the ingress router requests labels for this FEC from its downstream peer to build a label information table. This has to be done before any traffic begins. In LDP, downstream routers initiate the distribution of labels and the label/FEC binding. In Figure 2-5, LSR1 is the next hop for LER1, thus LER1 initiates a label request toward LSR1. This request will propagate through the network as indicated by the broken green lines. The reliable and ordered transport protocol, TCP, should be used for the signaling protocol LDP. In addition, traffic-related characteristics and MPLS capabilities are negotiated and CR–LDP may be used in determining the actual path setup to ensure the QoS/CoS requirements are complied with.

#### Step 2 Table creation

Each intermediary router will then receive a label from its downstream router starting from LER2 and going upstream till LER1. On receipt of label bindings each LSR creates entries in the label information base (LIB) specifying all the mapping between a label and an FEC, that is, mappings between the input port and input label table to the output port and output label table. The entries are updated whenever renegotiation of the label bindings occurs. Another table named LFIB, which is a subset of the labels extracted from the LIB, will also be created for actual packet forwarding.

#### Step 3 Label switched path creation

As shown by the dashed blue lines in Figure 2-5, the LSPs are created using LDP or any other signaling protocol in the reverse direction to the creation of LIB entries. More detailed establishing procedure has been introduced in the first section.

## Step 4 Label insertion/table-lookup

The ingress router LER1 inserts the label corresponding to a specific FEC to the packet and then forwards the packet to its next hop LSR. Subsequent LSRs use their LFIB tables to find the next hop for the packet. As shown in Figure 2-5, LSR2 and LSR3 examine the label in the received packet, replace it with the outgoing label and forward

it on. The label is removed once the packet reaches the egress LSR (LER4) because it is departing from the MPLS domain. Then the packet is supplied to the destination.

# 2.3 Tunneling in MPLS

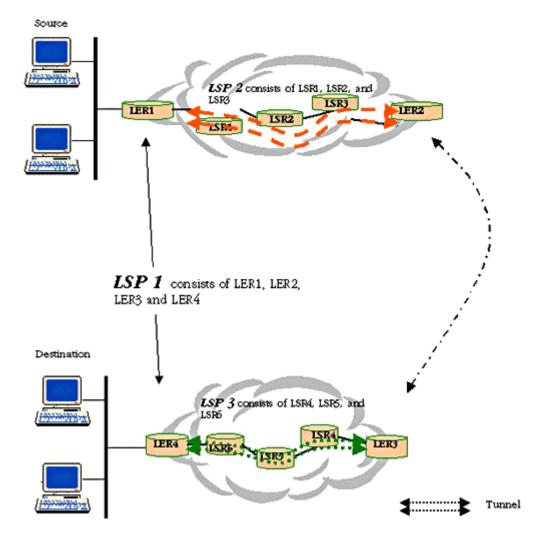

By adopting the label stack to create tunnels through the intermediary routers that can span multiple segments, a great unique feature of MPLS used in provisioning MPLS-based VPNs can be achieved. The entire path of a packet can be controllable without explicitly specified intermediate routers.

Consider the scenario in Figure 2-6. BGP is used between all the LERs (LER1, LER2, LER3, and LER4), and a first level LSP, LSP1, is created between them. These LERs will use the LDP to receive and store labels from the egress LER (LER4 in this scenario) all the way back to the ingress LER (LER1).

For LER1 to send its data to LER2 (one segment of the LSP1), it must go through several LSRs, in this case there are three. Therefore, a separate second level LSP, LSP 2, is created between these two LERs, LER1 and LER2, that spans LSR1, LSR2, and LSR3. This, in effect, represents a tunnel between LER1 and LER2 in the view of level 1 LSP. The labels for this LSP2 are different from the labels that the LERs created for LSP1. The same holds true for the LSP1 segment between LER3 and LER4 as well. Thus a second level LSP, LSP 3, can be created for this segment. Note that in this scenario, LER2 and LER3 are communicating directly, which means there is no tunnel between LER2 and LSR3. In more complicated scenarios, there can be even more levels of LSP between the source and destination LERs.

When the packet is transported through more than one network segments, the concept of the label stack is the foundation on which tunneling is realized. Take the scenario in Figure 2-6 as the example. Since a packet must travel through LSP 1, which contains two tunnels, LSP 2 and LSP 3, it has to carry two complete labels at a time. The pair used for each segment is (1) pair for the first segment, labels for LSP 1 and LSP 2 and (2) pair for the second segment, labels for LSP 1 and LSP 3. When the packet exits the first network segment and is received by LER3, it will remove the label for LSP 2 and replace it with LSP 3 label, while swapping LSP 1 label within the packet

with the next hop label. LER4 will eventually remove both labels before sending the packet to the destination.

Figure 2-6 Tunneling in MPLS [3]

# 2.4 Traffic Engineering and QoS

In normal IP routing, the data path is calculated from some measurement of efficiency. The common metrics for IP routing and forwarding decisions, including next hop, hop count, and cost, are useful in predicting the "shortest path" through the network. However, those metrics cannot be assumed to be reliable at all times, or to be the best for a given flow that requires some fixed or guaranteed amount of bandwidth.

Traffic engineering is a process that enhances overall network utilization by attempting to create a uniform or differentiated distribution of traffic throughout the network. TE enables the network to quickly and automatically re-route traffic when failure or congestion conditions are detected by ensuring that all available network resources are optimally used. A network that maximizes its resources and capacity during normal operation is thus achieved through avoiding network hot spots and areas of hyper-aggregation, which means that traffic engineering does not necessarily select the shortest path between two devices. It is possible that packets may traverse completely different paths even though their originating node and the final destination node are the same. In this way, the less-exposed or less-used network segments can be used and differentiated services can be provided. Links between any two points in a network are relatively fixed and quantifiable, and the cost to increase that capacity, in many cases, is high, so effective traffic engineering and higher utilization of available links can provide both long- and short-term cost savings.

"Constraint-based" and "congestion-aware" routing are terms used to describe networks that are fully aware of their current utilization, existing capacity and provisioned services at all times. While traditional IP routing protocols, including OSPF, IS-IS and BGP, are not inherently congestion-aware, and have to be modified to enable such awareness, CR takes into account parameters, such as link characteristics (bandwidth, allocation multiplier, current bandwidth reservation, resource class, packet loss ratio, and link propagation delay, etc.), hop count, and QoS, etc. And the resulting data path can also ensure that none of the constraints that have been set are violated along the path. Once connections have been configured (either by dynamic signaling or by static provisioning), the Layer 2 and Layer 3 network becomes fully aware of the amount of bandwidth being consumed, as well as the parts of the network being used to route the connections. This information can then be propagated to the accompanying IP routing protocols that are exchanged by all IP routers, creating a truly congestion-aware view of the network and its current topology. Then, all future network requests can be directed to their destination by not only the "shortest path first" (as defined by OSPF), but by a path that will guarantee the bandwidth requirements of the IP application or service. This means when using CR, it is entirely possible that a longer (in terms of cost) but less loaded path is selected. And there is another side effect that while CR increases network utilization, it adds more complexity to routing calculations, as the path selected must satisfy the QoS requirements of the LSP.

CR-LSPs set up with explicit hops or QoS requirements can be realized easily in MPLS architecture. Explicit hops dictate which path is to be taken. QoS requirements dictate which links and queuing or scheduling mechanisms are to be employed for the flow. A CR-LDP component to facilitate constraint-based routes has been defined by the IETF and its more detailed description has been introduced earlier in this chapter.

In MPLS, traffic engineering is inherently provided using explicitly routed paths. The LSPs are created independently, specifying different paths that are based on user-defined policies. However, this may require extensive operator intervention. RSVP and CR–LDP are two possible approaches to supply dynamic traffic engineering and QoS in MPLS.

RSVP-TE and CR-LDP are now two competing protocols used for MPLS that perform CR. RSVP is an existing protocol, standardized by the IETF, which has been extended to RSVP-TE. Similarly, CR-LDP is an extension of LDP, which has been designed for MPLS especially. There are advantages and disadvantages to both protocols. One side, CR-LDP sits on top of TCP to ensure reliability. For RSVP, refreshing that must occur in the steady state is required to ensure reliability while refreshing consumes bandwidth and processing resources. Also, TCP requires some handshaking before an LDP session can begin and results in a moderate amount of overhead while RSVP does not require connection establishment before label distribution occurs. Because of such advantages and disadvantages of RSVP-TE and CR-LDP, designers need to keep their systems flexible enough to accommodate future changes to the protocols.

### 2.5 Protocol Architecture

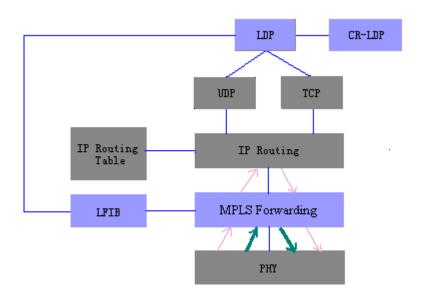

Figure 2-7 depicts the protocols that can be used for operations on a MPLS node. The LDP module utilizes transmission control protocol (TCP) for reliable transmission of control data from one LSR to another during a session. But the LDP uses the user

datagram protocol (UDP) during its discovery phase of operation. In this phase, the LSR tries to identify neighboring elements and also signals its own presence to the network. This is done through an exchange of hello packets.

There are two tables relevant to MPLS forwarding at an MPLS node: the LIB and the LFIB maintained by LDP. The LIB (not indicated in Figure 2-7) contains all the labels assigned by the local MPLS node and the mappings of these labels to labels received from its MPLS neighbors. The LFIB uses a subset of the labels contained in the LIB for actual packet forwarding.