### COMPUTERIZED GENERATOR DIFFERENTIAL PROTECTION

### A Thesis

Submitted to the Faculty of Graduate Studies

in Partial Fulfilment of the Requirements

for the Degree of

Master of Science

in the Department of Electrical Engineering

University of Saskatchewan

by

David W. Wind

Saskatoon, Saskatchewan

May, 1972

The author claims copyright. Use shall not be made of the material contained herein without proper acknowledgement, as indicated on the following page.

The author has agreed that the Library, University of Saskatchewan, may make this thesis freely available for inspection. Moreover, the author has agreed that permission for extensive copying of this thesis for scholarly purposes may be granted by the professor or professors who supervised the thesis work recorded herein, or, in their absence, by the Head of the Department or the Dean of the College in which the thesis work was done. It is understood that due recognition will be given to the author of this thesis and to the University of Saskatchewan in any use of material in this thesis. Copying or publication or any use of the thesis for financial gain without approval by the University of Saskatchewan and the author's written permission is prohibited.

Requests for permission to copy or make use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical Engineering

University of Saskatchewan

Saskatoon, Canada

#### **ACKNOWLEDGEMENTS**

The author wishes to express his gratitude to the many individuals and organizations who made this work possible. Particularly, he wishes to thank Dr. M.S. Sachdev for his advice and assistance in the preparation of this thesis and to all other members of the faculty of the Electrical Engineering Department for their helpful comments. The author is also grateful to Mr. W. D. Pickering and the staff of the Controls Laboratory for their valued contribution to the work. Thanks are extended to the Canadian Armed Forces for their permission to complete post graduate studies at the University of Saskatchewan and to the National Research Council for their financial assistance. Special thanks are extended to Miss. D.N. Metz for her patient and diligent efforts in preparing the manuscript.

### University of Saskatchewan

### Electrical Engineering Abstract 72A146

#### "COMPUTERIZED GENERATOR DIFFERENTIAL PROTECTION"

Student: D. W. Wind

Supervisor: M. S. Sachdev

M.Sc. Thesis presented to the College of Graduate Studies

May, 1972

#### **ABSTRACT**

This thesis presents a computerized scheme which detects the presence of phase to ground and phase to phase stator faults on power system generators. The fault/no-fault decisions are based on the amplitude ratio of the "fault" and "average-through" currents from a selected generator phase. Techniques for fast amplitude extraction from sampled inputs are evaluated. The proposed protection scheme is amenable to a time-shared digital computer approach.

An analog input data pre-processor, used to reduce the sampling requirements of the digitizer, is described. An input data monitor is included to activate the more sophisticated software only when required. Fast acting software is included to restrict subsequent calculations to the data from the faulted phase. Special attention is directed towards making valid amplitude comparisons during the transient period immediately following fault incidence. A data logging function, which retains and returns information from any conditions analyzed by the software, is included to permit reconstruction of the pre-fault and post-fault currents. The operation of the hardware and software is also reported. The results of extensive tests, performed on single and three phase versions, were used to evaluate the performance of the scheme. Approximately 800 case studies including internal and external faults using a three phase generator, are presented.

This research was financed by a National Research Council bursary and grant No. A7249.

# TABLE OF CONTENTS

|      |                                                                                                                                                                          | Page             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| COPY | RIGHT                                                                                                                                                                    | ii               |

| ACKN | NOWLEDGMENTS                                                                                                                                                             | iii              |

|      | FRACT                                                                                                                                                                    | iv               |

| Abol | I KACI                                                                                                                                                                   |                  |

| TABL | LE OF CONTENTS                                                                                                                                                           | V                |

| LIST | r OF FIGURES                                                                                                                                                             | vii              |

| 1.   | INTRODUCTION                                                                                                                                                             | 1                |

| 2.   | PRESENT PROTECTION TECHNIQUES                                                                                                                                            | 5                |

|      | 2.1 Protection Philosophy                                                                                                                                                | 5                |

| ·    | 2.2 Generator Protection 2.2 a) Ground fault protection 2.2 b) Unbalanced faults                                                                                         | 7<br>7<br>8<br>8 |

|      | <ul> <li>2.2 c) Overload protection</li> <li>2.2 d) Overheating protection</li> <li>2.2 e) Overspeed protection</li> <li>2.2 f) Loss-of-excitation protection</li> </ul> | 9<br>9<br>10     |

|      | 2.2 g) Protection against motoring of a generator 2.2 h) Field ground protection                                                                                         | 10<br>10         |

|      | 2.3 Differential Protection of Generator Stators                                                                                                                         | 12               |

|      | 2.4 Transient Characteristics of the Fault Current                                                                                                                       | 15               |

|      | 2.5 Percent Differential Relay Response                                                                                                                                  | 17               |

| 3.   | ON-LINE COMPUTER PROTECTION TECHNIQUES                                                                                                                                   | 24               |

|      | 3.1 Cycle to Cycle Comparison                                                                                                                                            | 24               |

|      | 3.2 Computation of Peak Values                                                                                                                                           | 26               |

|      | 3.3 Evaluation of Computation Technique                                                                                                                                  | 27               |

| 4.   | ON-LINE COMPUTER PROTECTION DESIGN CONCEPTS                                                                                                                              | 32               |

|      | 4.1 Digital Computer Characteristics                                                                                                                                     | 32               |

|      | 4.2 Multi-Purpose Computer Rationale 4.2 a) Executive program                                                                                                            | 33<br>34         |

|      | <ul><li>4.2 b) Fault monitors</li><li>4.2 c) Zone and phase allocation</li><li>4.2 d) Fault verification</li></ul>                                                       | 34<br>34<br>36   |

|      | 4.3 The Hybrid Computer Rationale                                                                                                                                        | 36               |

|      | 4.4 Design Concepts Applied to Differential Protection 4.4 a) Fault monitor 4.4 b) Phase allocation sequence                                                             | 37<br>37<br>41   |

|      | 4.4 b) rhase attocacton sequence                                                                                                                                         | 41               |

|          |                                                                                | Page     |

|----------|--------------------------------------------------------------------------------|----------|

|          | 4.4 c) Fault verification                                                      | 41       |

| 5.       | DIGITAL PROTECTION SYSTEM DESCRIPTION                                          | 46       |

|          | 5.1 Digital Computer Facility                                                  | 46       |

|          | 5.2 Analog Pre-Processing System                                               | 46       |

|          | 5.3 Digital Fault Monitor                                                      | 49       |

|          | 5.4 Phase Allocation Sequence                                                  | 51       |

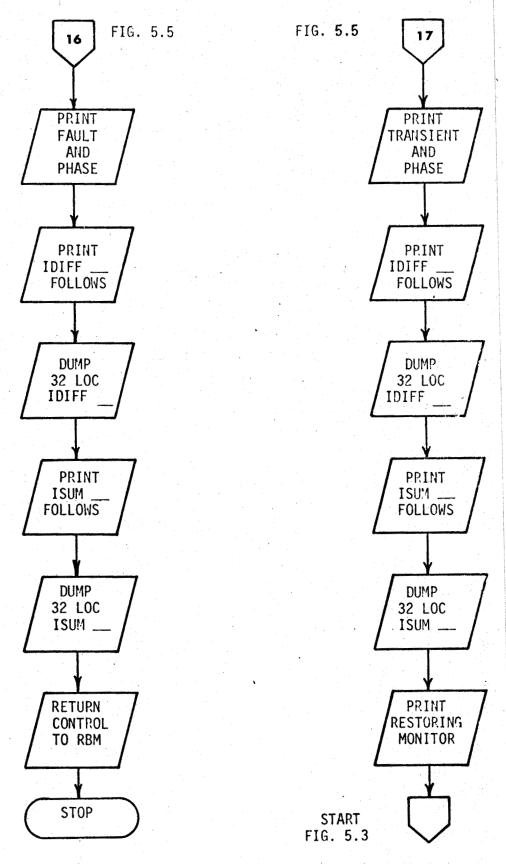

|          | 5.5 Fault Verification Sequence                                                | 52       |

| <u>.</u> | TESTING OF THE DIGITAL PROTECTION SCHEME                                       | 58       |

| 6.       |                                                                                | 58       |

|          | 6.1 Single Phase Version 6.1 a) D.C. tests                                     | 58       |

|          | 6.1 b) A.C. tests                                                              | 59       |

|          | 6.2 Three Phase Version                                                        | 66       |

|          | 6.2 a) D.C. tests                                                              | 66<br>68 |

|          | 6.2 b) A.C. tests - analog model                                               |          |

|          | 6.3 System Tests - Selection of Equipment                                      | 69<br>69 |

|          | <ul><li>6.3 a) The generator</li><li>6.3 b) The current transformers</li></ul> | 70       |

|          | 6.3 c) The tape recorder                                                       | 73       |

|          | 6.4 System Tests - Results                                                     | 7.4      |

|          | 6.4 a) Type (i) faults                                                         | 77<br>85 |

|          | 6.4 b) Type (ii) faults                                                        | · 88     |

|          | 6.4 c) Type (iii) faults                                                       | 91       |

|          | 6.4 d) Type (iv) faults                                                        |          |

| 7.       | GONCLUSIONS                                                                    | 95       |

| 8.       | REFERENCES                                                                     | 99       |

| 9.       | APPENDICES                                                                     | 103      |

| -        | I Program Listing for Peak Squared Evaluation                                  | 103      |

|          | II Program Listing for Protection Scheme Software                              | 105      |

|          | III Test Machine Data                                                          | 117      |

|          | 111 lest rachine bata                                                          |          |

# LIST OF FIGURES

| FIGL | JRE      | Pa                                                                                                        | ge |

|------|----------|-----------------------------------------------------------------------------------------------------------|----|

| 2.   | <u> </u> | The protective zones commonly employed in power systems.                                                  | 6  |

| 2.2  | 2        | A field ground fault detector using an unbalanced bridge technique.                                       | 11 |

| 2.3  | 3        | A differential current protection scheme for one phase of a generator.                                    | 14 |

| 2.4  | •        | Connection diagram of one phase of a percentage differential protection scheme.                           | 15 |

| 2.5  | 5        | Typical current describing functions encountered during a fault.                                          | 18 |

| 2.6  | 5        | Percentage differential protection characteristics illustrating the effect of spring restraint.           | 21 |

| 2.   | 7        | Percentage differential protection characteristic including the faulted stator transient current effects. | 23 |

| 3.   | l        | A typical segment of an input parameter and its first difference.                                         | 27 |

| 3.   | 2        | The maximum percentage error of the computed first derivatives verses sampling frequency.                 | 28 |

| 3.   | 3        | Equipment configuration to compute the peak squared value of a 60 Hz sinusoid.                            | 29 |

| 3.   | 4        | Correlation diagram of the 60 Hz input sinusoid and the computed peak squared values.                     | 30 |

| 4.   | 1        | The logic organization of a digital protection scheme in a time shared mode.                              | 35 |

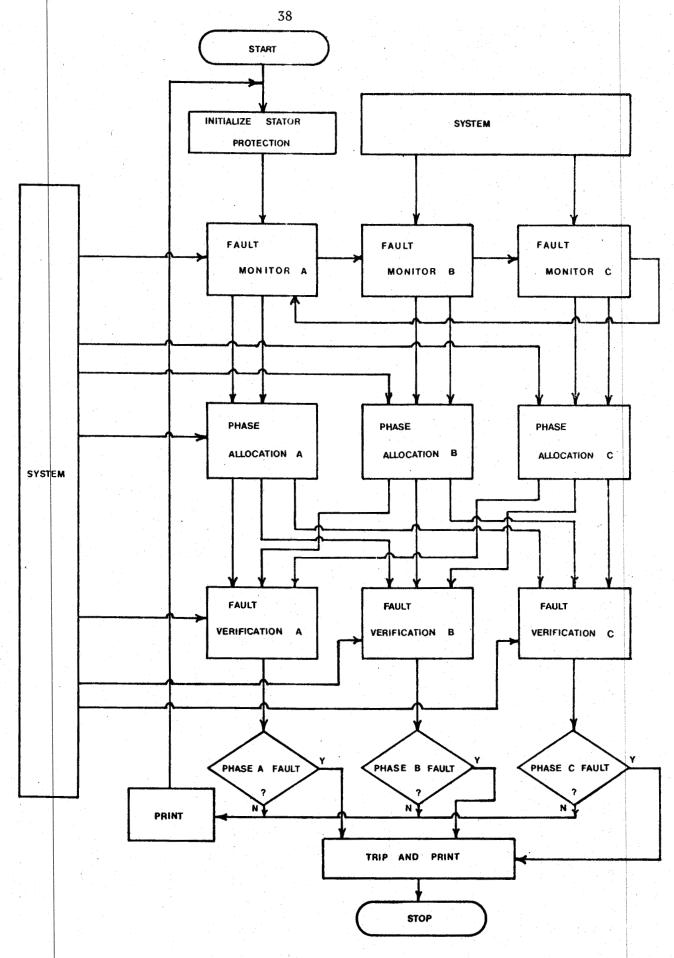

| 4.   | 2        | The logic organization of the proposed digital percentage differential protection scheme.                 | 38 |

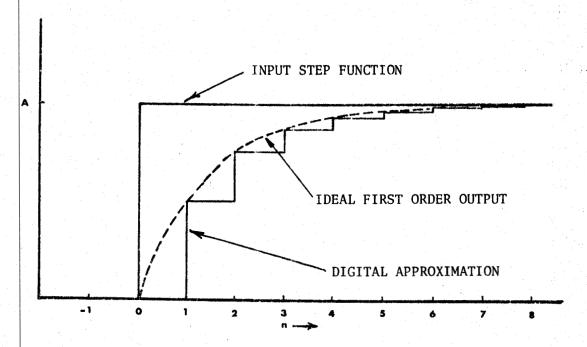

| 4.   | 3        | The digital and ideal outputs of the first order system for a step input.                                 | 43 |

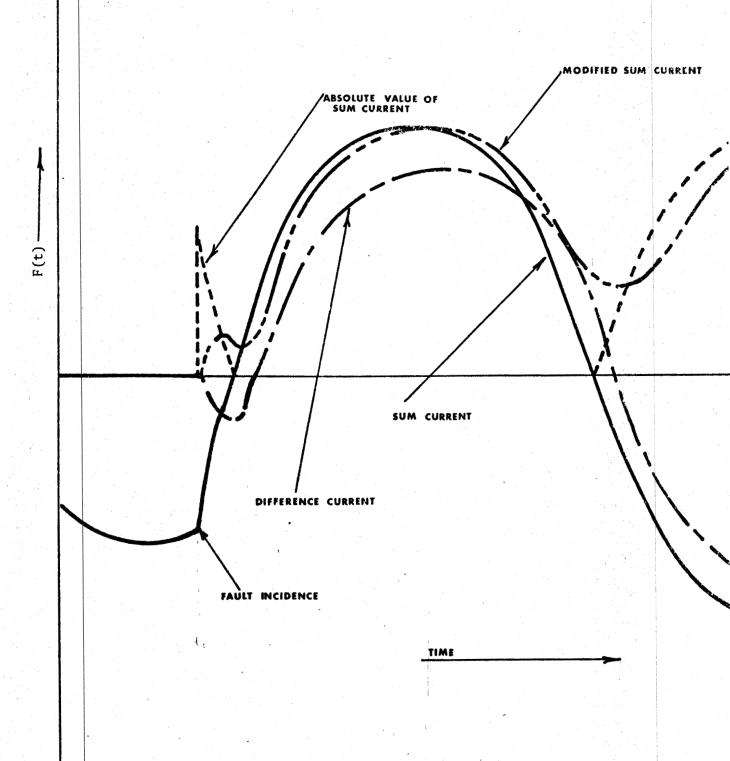

| 4.   | 4        | Sampled and derived functions for a faulted stator as used by the protection scheme.                      | 44 |

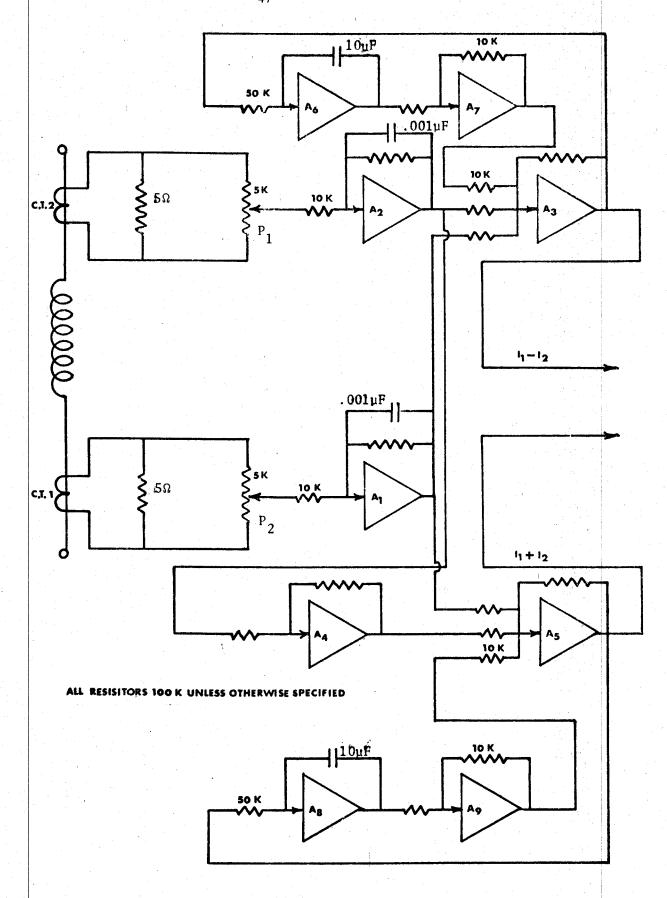

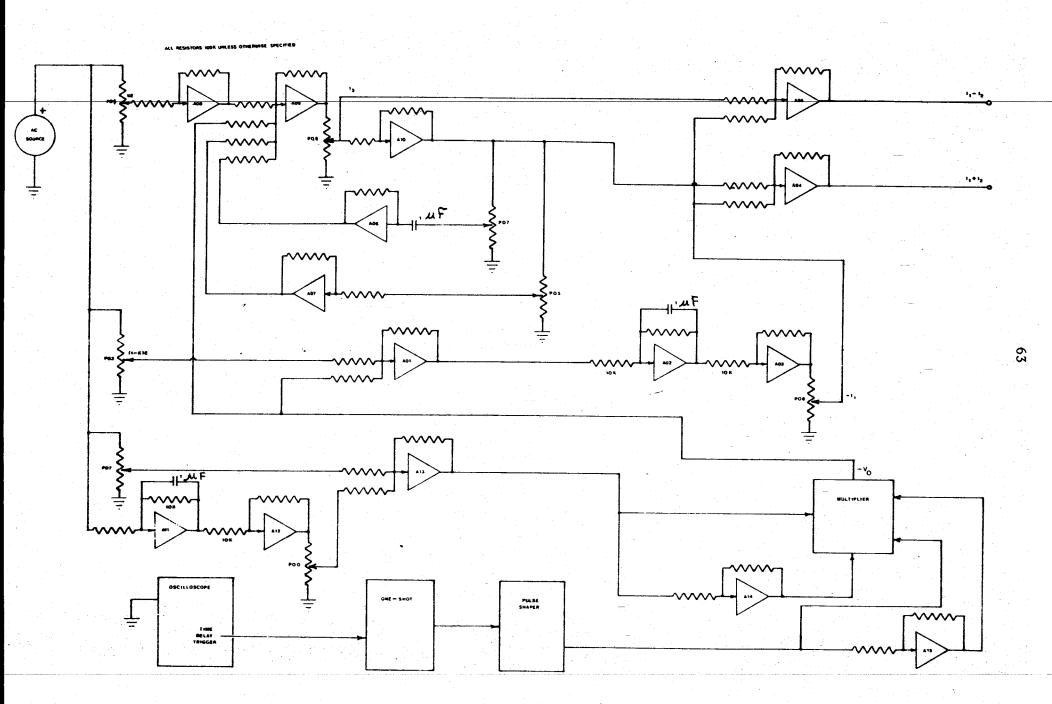

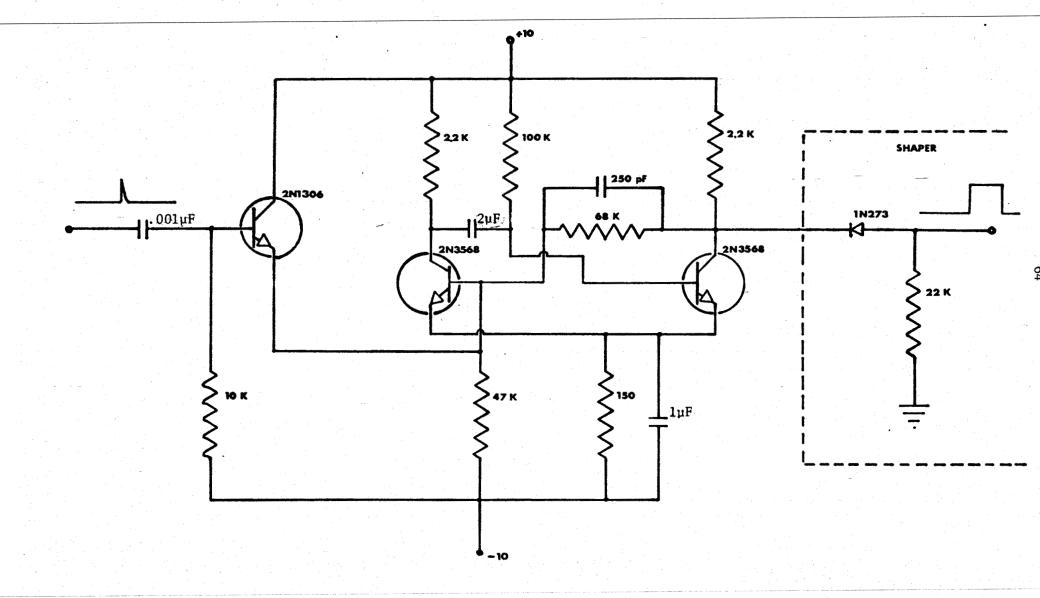

| 5.   | 1        | Analog pre-processor schematic diagram.                                                                   | 47 |

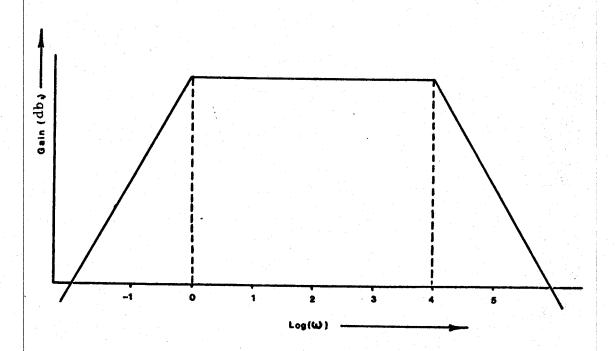

| 5.   | 2        | Analog pre-processor linearized frequency response.                                                       | 48 |

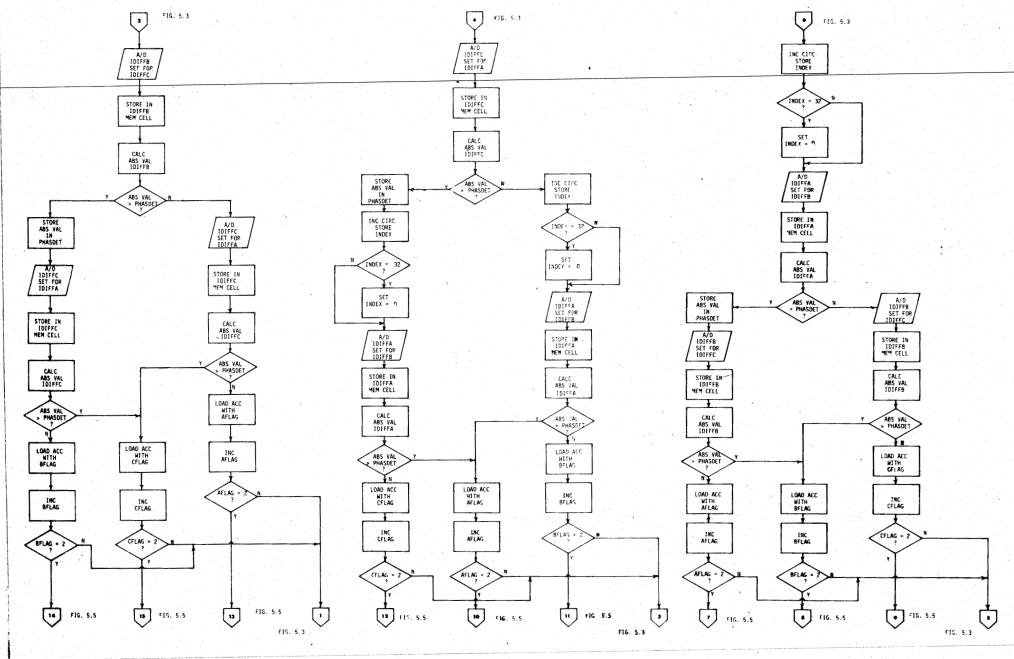

| 5.   | 3        | Digital logic flow chart of the three phase fault monitor sequence.                                       | 50 |

| FIGURE |                                                                                                                                              | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

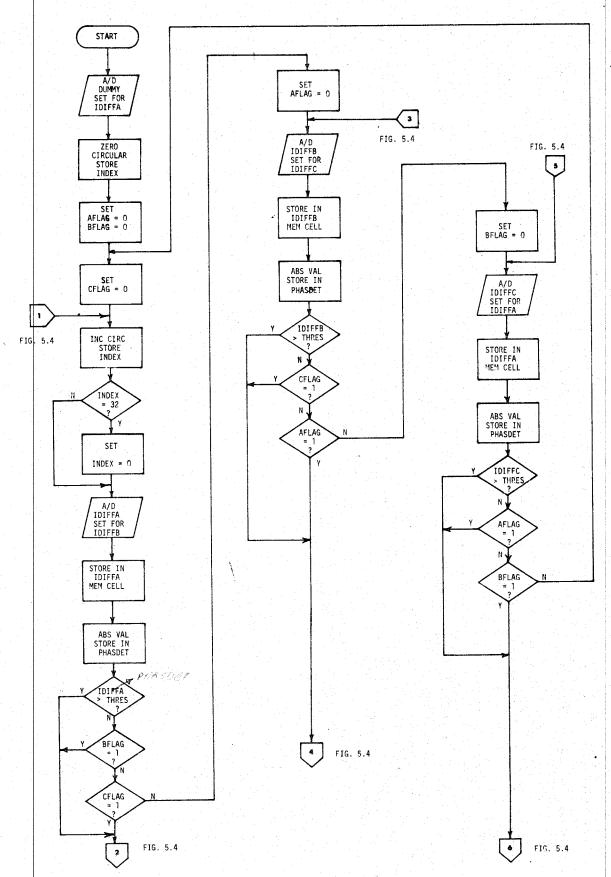

| 5.4    | Digital logic flow chart of the phase allocation sequence.                                                                                   | 52   |

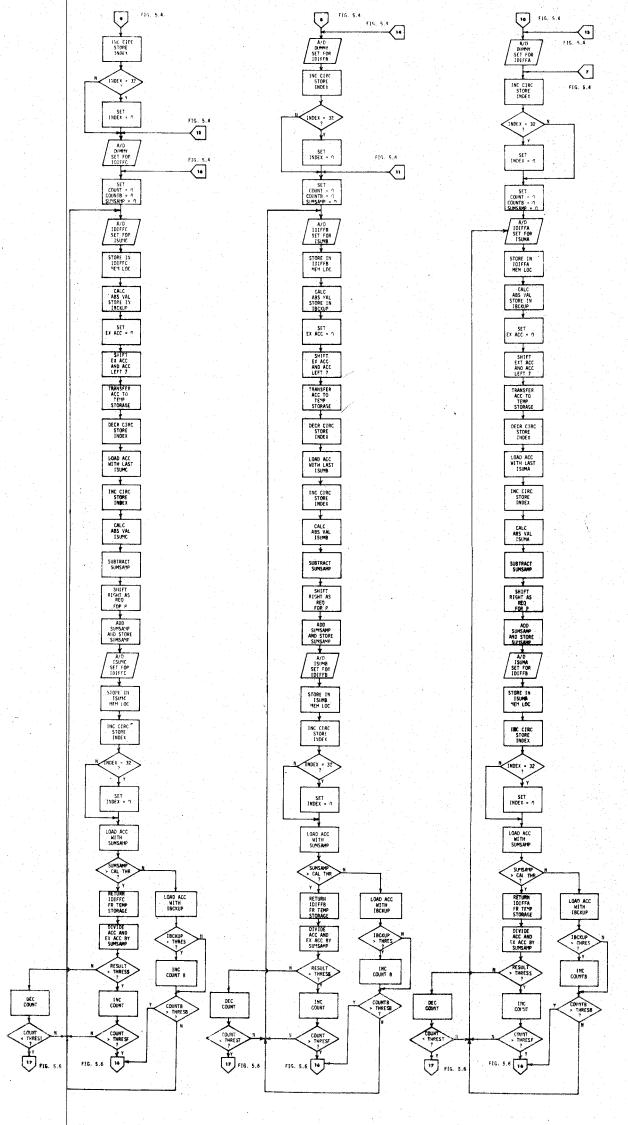

| 5.5    | Digital logic flow chart of the fault verification sequences.                                                                                | 54   |

| 5.6    | Digital logic flow chart of printing action following verification.                                                                          | 55   |

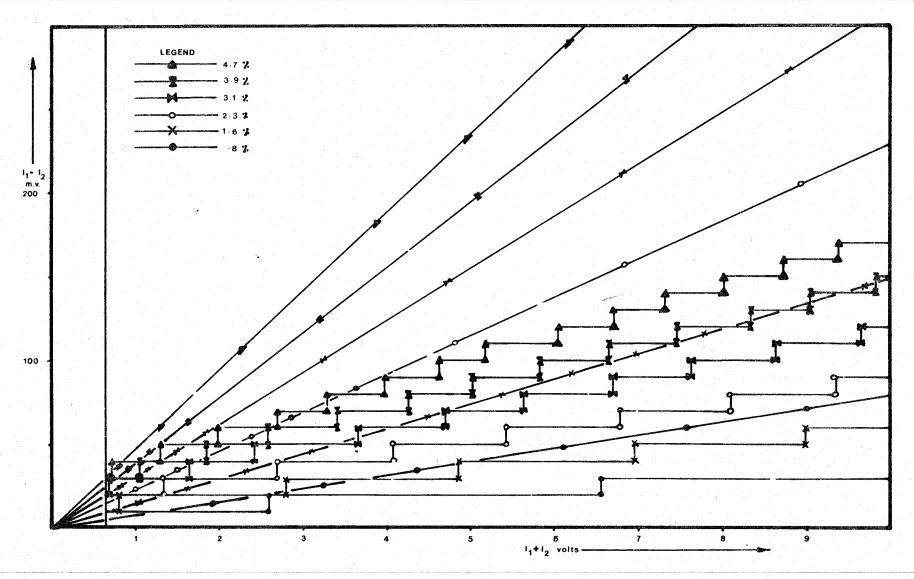

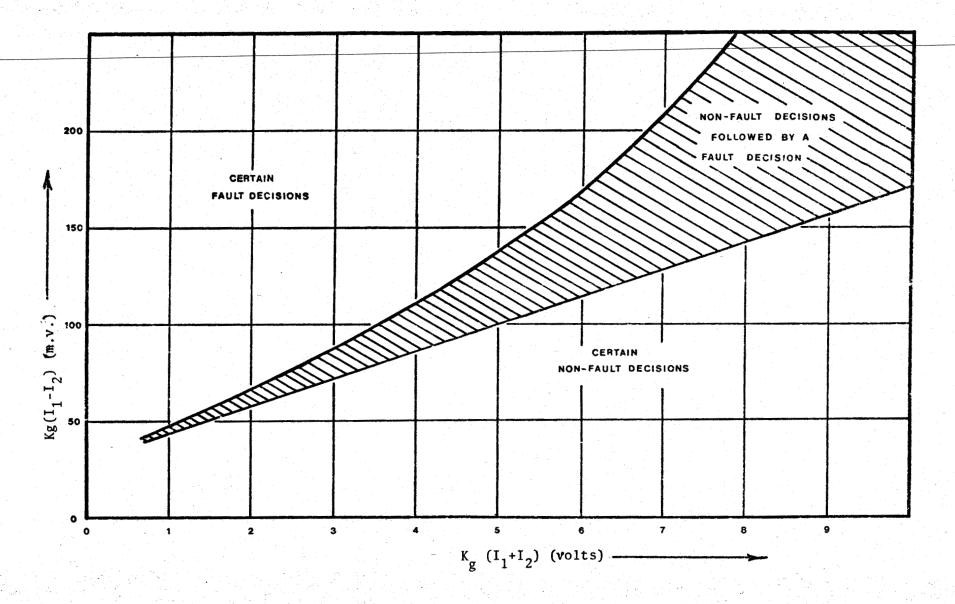

| 6.1    | Ideal and measured relay characteristics for various sensitivity settings.                                                                   | 60   |

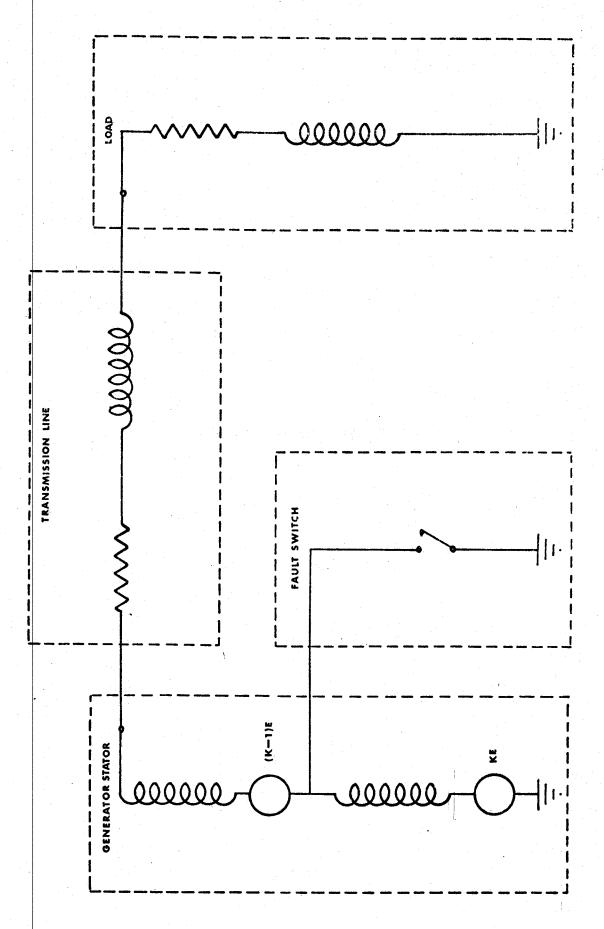

| 6.2    | The representation of a single phase stator and its connected system as used by the analog fault simulator.                                  | 62   |

| 6.3    | Analog fault simulator.                                                                                                                      | 63   |

| 6.4    | Synchronized fault gating function multivibrator.                                                                                            | 64   |

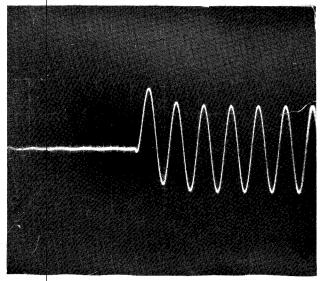

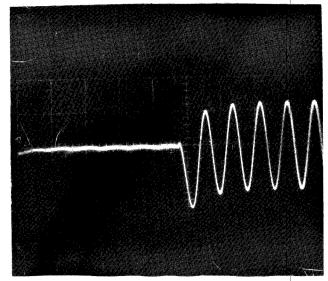

| 6.5    | Difference current generated for fault incidence during (a) the negative half cycle and (b) the positive half cycle of the prefault current. | 65   |

| 6.6    | Characteristic response of the single phase version to A.C. excitation at 4.7% sensitivity setting.                                          | 67   |

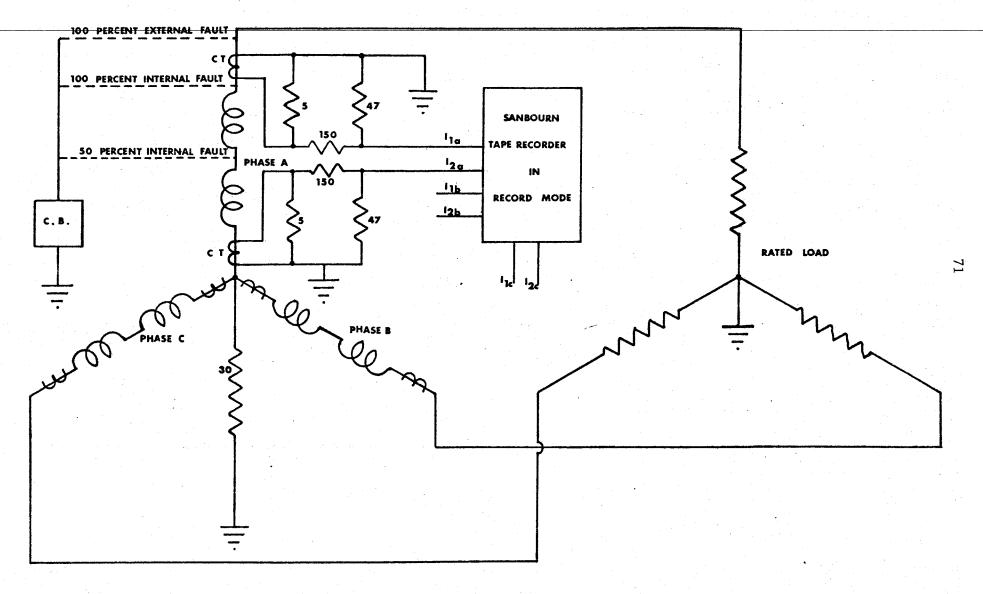

| 6.7    | Test equipment configuration for fault simulations.                                                                                          | 71   |

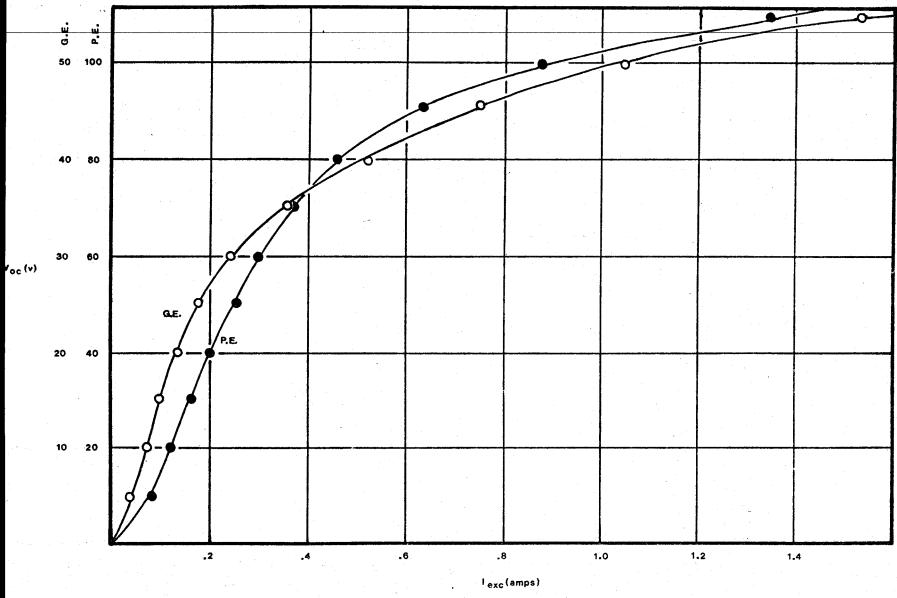

| 6.8    | Excitation characteristics for both the Packard Electric, P.E., and the General Electric, G.E., C.T.'s.                                      | 72   |

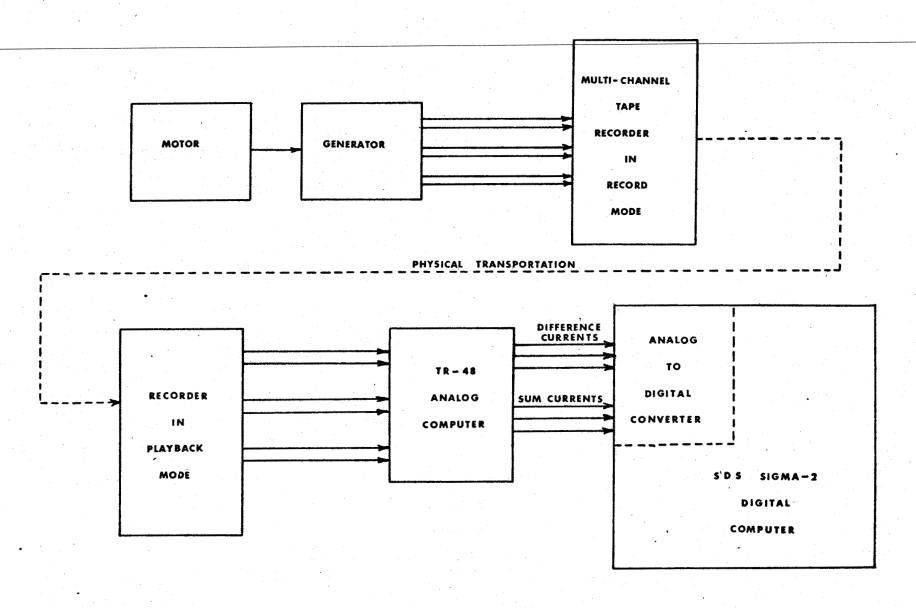

| 6.9    | Test equipment configuration for the machine tests of the digital protective system.                                                         | 76   |

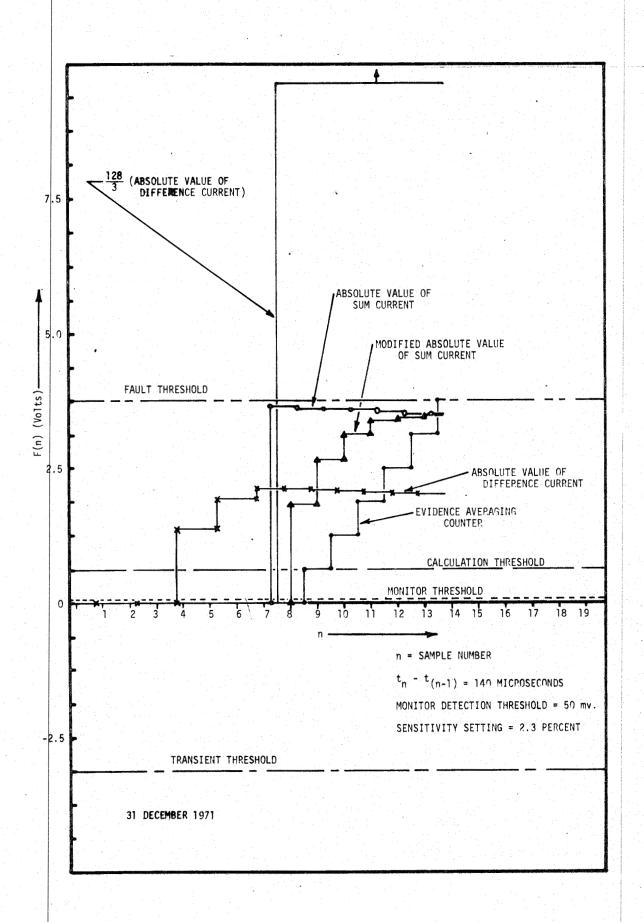

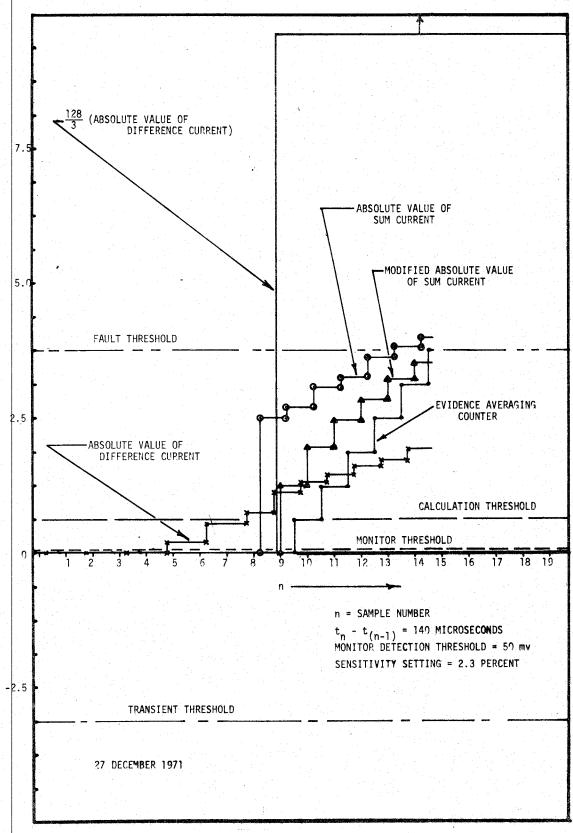

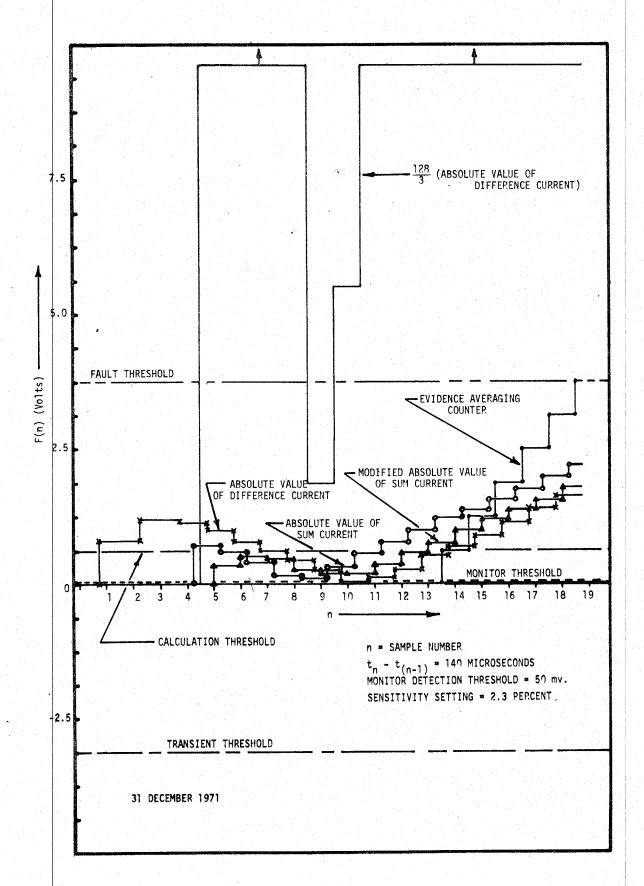

| 6.10   | Reconstructed protection system reaction to a type (i) fault without incidence control.                                                      | 78   |

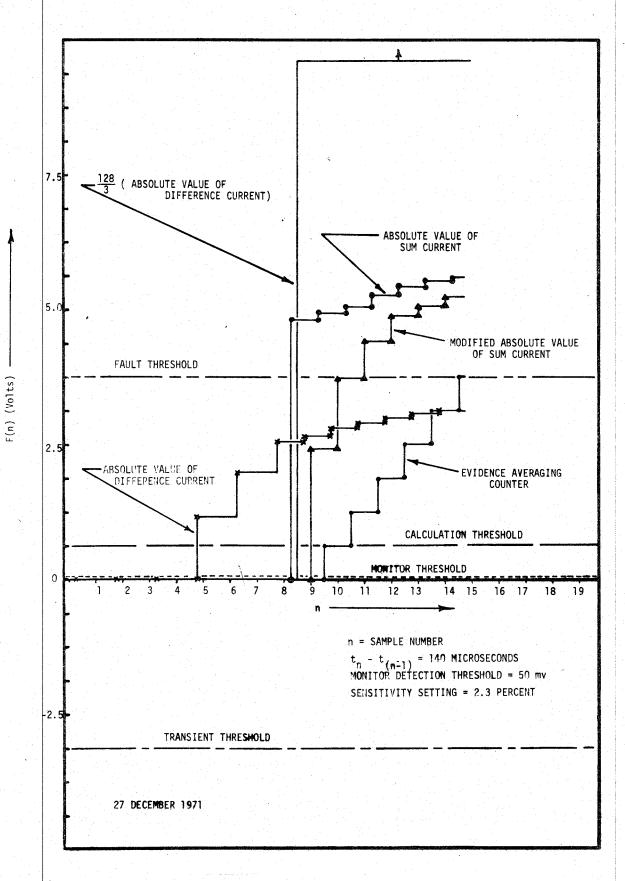

| 6.11   | Reconstructed protection system reaction to a type (i) fault with incidence at $0^{\circ}$ .                                                 | 81   |

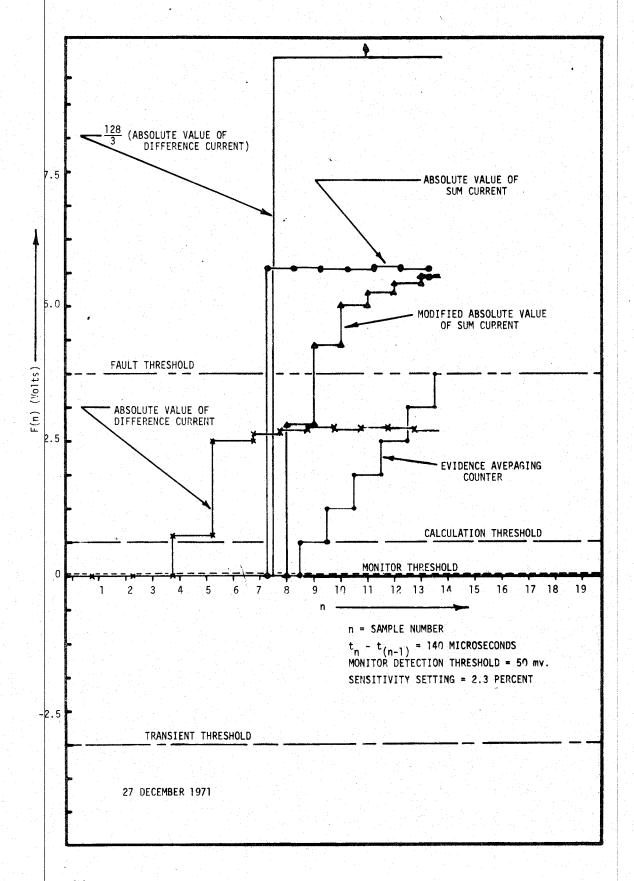

| 6.12   | Reconstructed protection system reaction to a type (i) fault with incidence at $30^{\circ}$ .                                                | 82   |

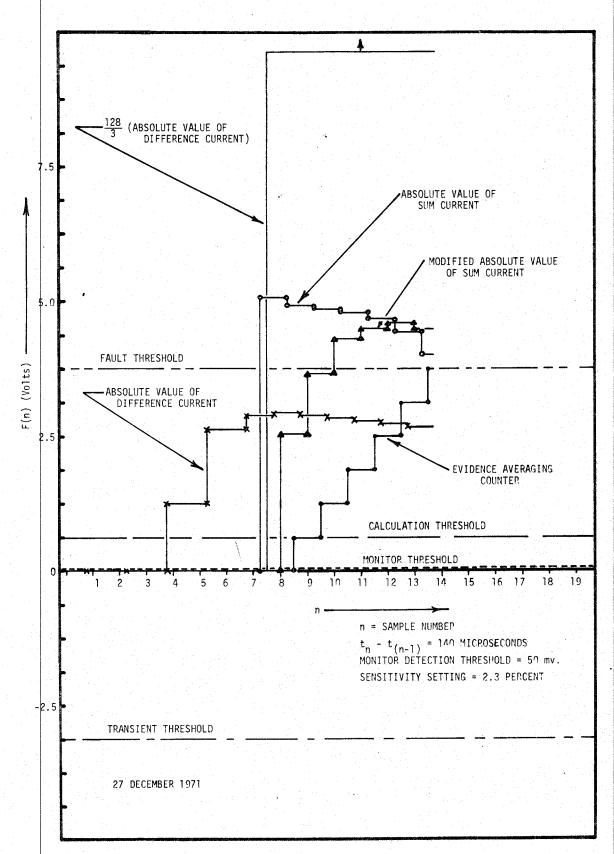

| 6.13   | Reconstructed protection system reaction to a type (i) fault with incidence at $60^{\circ}$ .                                                | 83   |

| 6.14   | Reconstructed protection system reaction to a type (i) fault with incidence at $90^{\circ}$ .                                                | 84   |

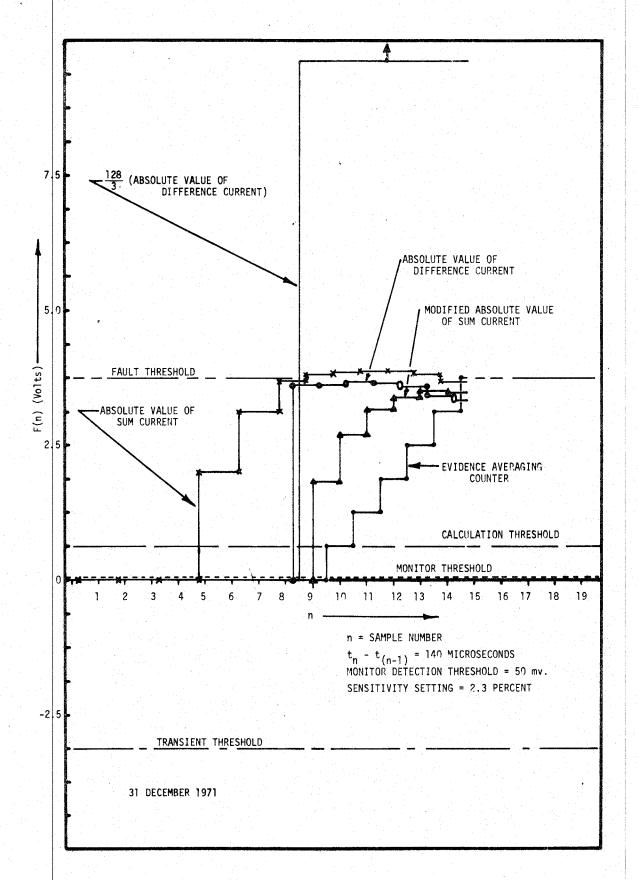

| 6.15   | Reconstructed protection system reaction to a type (ii) fault with incidence just prior to current zero crossing.                            | 86   |

| IGURE |                                                                                                                    | Page |

|-------|--------------------------------------------------------------------------------------------------------------------|------|

| 6.16  | Reconstructed protection system reaction to a type (ii) fault with incidence near current maximum.                 | 87   |

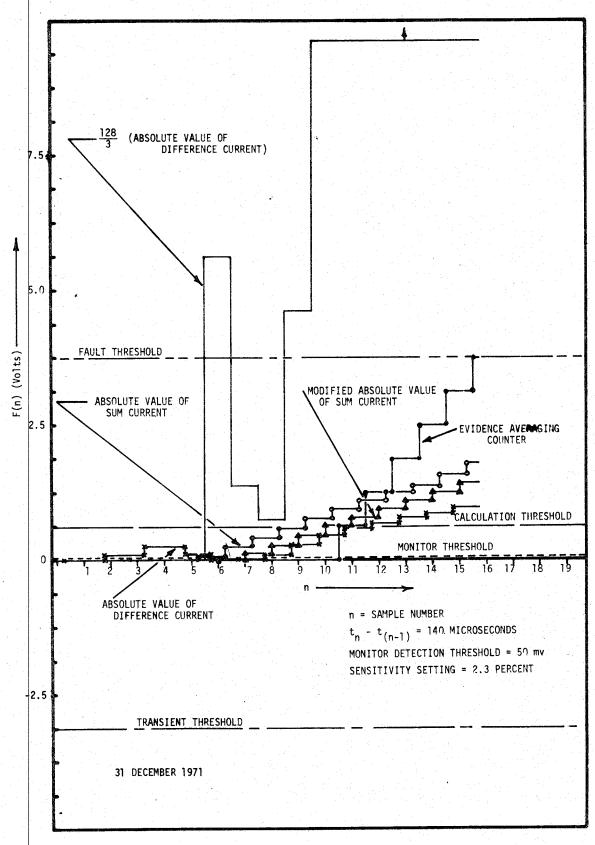

| 6.17  | Reconstructed protection system reaction to a type (iii) fault with incidence just prior to current zero crossing. | 89   |

| 6.18  | Reconstructed protection system reaction to a type (iii) fault with incidence near current maximum.                | 90   |

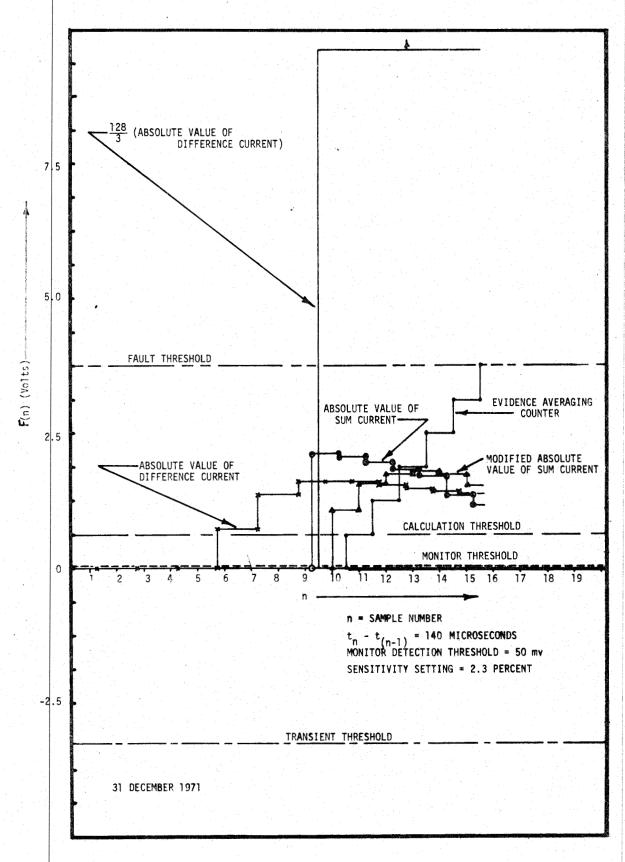

| 6.19  | Reconstructed protection system reaction to a type (iv) fault.                                                     | 92   |

#### 1. INTRODUCTION

Protective devices, as used by electrical utilities, avert further deterioration of the system which might be caused by a prolonged deviation from the expected behaviour of its components. 25,43,45 The history of automatic protection began with the development of fuses.

These isolate the source from its load when an abnormality, current in excess of the rated value, is present. In power system applications, fuses have been supplanted by improved devices. This can be attributed to the inability of fuses to discriminate between various malfunctions and their (the fuses') required replacement before the isolated element can be restored to service.

The first major improvement on fuses was provided by automatic circuit-breakers with trip coils energized by system currents and voltages.

Soon afterwards, the selective functions of automatic switchgear were transferred from the breakers to separate protective relays, whose contacts initiated tripping. The first relays, designed to respond to short-circuit conditions, were attracted armature devices. Some of these operated only after a time delay provided by a pre-set dashpot mechanism. As power systems increased in size and complexity, relays with more precise operation and inverse-time characteristics (operating time inversely proportional to fault severity) were developed. Relays based on the induction disc principle, commonly used in watt-hour meters, provided a viable solution in the early 1920's. As requirements for greater sensitivity, selectivity and speed increased further, a trend towards the use of fast differential relays for primary protection developed. By the late 1920's, the induction disc relays had been replaced with balanced beam and induction cup types.

Since these pioneering developments, many improvements have been selectively incorporated but power system relaying has, until recently, been slow to implement electronic fault sensing equipment. In their early stages of development, electronic protection schemes relied on the operation of vacuum tubes as comparators, amplifiers, logic switches and pulse generators. Designs incorporating thermionic emission devices could not be extensively implemented, in practice, due to their fragile construction and unreliable operation. The advent of solid state (semiconductor) devices enabled the present trend towards electronic relays. Many designs of phase and amplitude comparators have since been developed for use in power system protection. The demand for improved protection and control techniques has continued to increase. This is due to the growth of generating capacities and interconnections of individual systems to form regional power pools.

Continuing rapid advances in digital computer technology have prompted a re-evaluation of protective devices and techniques. The use of real-time digital computers for system protection was advocated in 1966 by last and Stalewski. In 1967, Rockefeller discussed the use of on-line digital computers for substation protection. Mann and Morrison demonstrated the feasibility of the digital computer application to transmission line protection in a laboratory environment. Rockefeller and his associates have subsequently applied a digital computer to protect the Tesla-Bellota, kV line. Computerized transformer protection has also been proposed.

The digital computer protection of generator stators, as reported in this thesis, is a new application in the power systems area. The project was undertaken to realize two distinct but closely related aims. First,

the work was to provide much needed experience in digitizing and processing power system variables. Secondly, it was to demonstrate the feasibility of providing generator differential protection using a real-time computer.

The dynamic behaviour of a generator stator, while it is experiencing a fault, must be understood to appreciate the operation of both the conventional electromechanical relays and the proposed alternative. A suitable qualitative examination of stator fault currents and the resulting relay response are presented in chapter 2. Other generator faults are also briefly described to relate percentage differential current relays to overall plant protection philosophy.

Two digital techniques, advanced by other researchers and used to accelerate power system data processing, are examined in chapter 3. The analysis for both, the cycle to cycle comparison of input parameters and the instantaneous sample to peak value conversion, are presented. These processing techniques are examined, with particular emphasis on the requirements of the digital protection scheme described in this thesis; the analysis is generally applicable to other digital protection and control problems in power systems.

The general characteristics of digital computers, which might be advantageously used in protection schemes, are outlined in chapter 4.

Analog pre-processing of input data is proposed to alleviate analog to digital conversion problems. The advantages of the multi-use digital computer approach are discussed. Several alternative design concepts for the proposed scheme are also explained. Included in the descriptions are, (i) parameter selection and data processing considerations for the fault monitor, (ii) the requirement for and a description of, software to

determine the most probable originating phase of the fault symptoms and (iii) a method to modify input parameters to permit evaluation of data in the immediate post inception period.

Implementation of these and other concepts, to obtain a viable digital percentage differential protection scheme, is described in chapter 5. Relevant characteristics of the hardware selected are outlined. The operation of the analog pre-processor, and the fault monitor, phase allocation and fault verification segments are described in detail.

The performance of the digital percentage differential protection scheme is evaluated in chapter 6. The reactions of a single phase and a three phase software version to controlled D.C. and A.C. inputs from an analog computer are described. A three phase generator was deliberately faulted in the laboratory to provide the data required to evaluate the performance of the complete protection scheme. Some 800 case studies of both internal and external faults were examined. The reaction of the protection scheme has been reconstructed for typical examples of each type of fault. Important details, concerning scheme's reaction to the fault data, are explained with the aid of these examples.

### PRESENT PROTECTION TECHNIQUES

This chapter is included to acquaint the reader unfamiliar with power system protection to the philosophy and techniques commonly applied. Generator protection is discussed with particular emphasis on differential current relaying. The transient characteristics of stator fault current and differential relay response are qualitatively examined.

## 2.1 Protection Philosophy

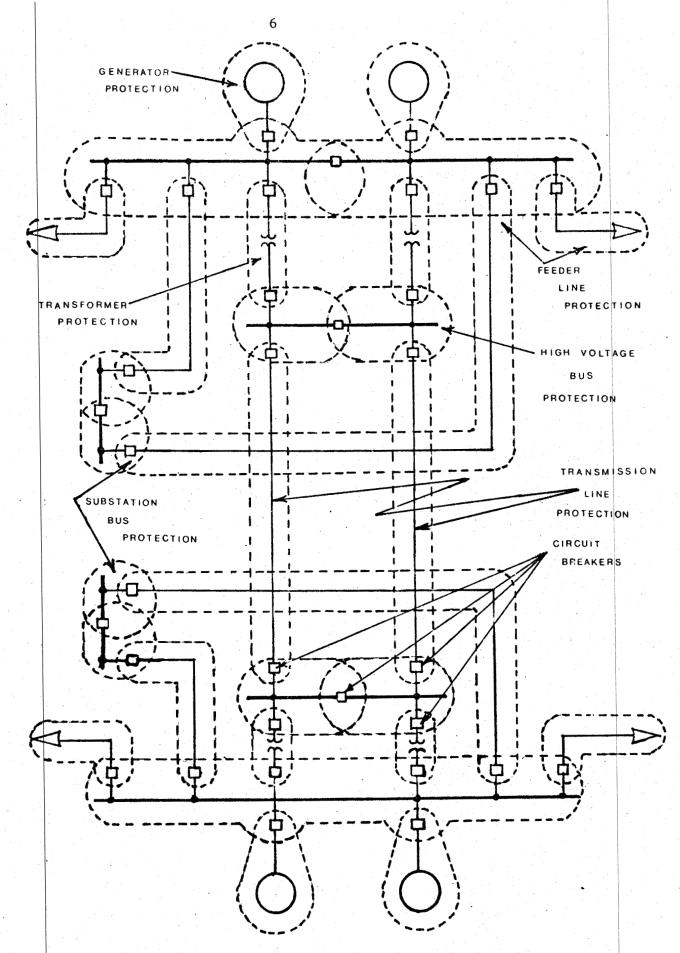

Switching and fault sensing devices are provided in a power system to limit equipment damage during faults and overloads, and to minimize their effects on the remainder of the system. 25,43,45 is accomplished by dividing the system into protective zones separated by circuit breakers as shown in Fig. 2.1. The protective equipment is deployed such that a faulted zone is isolated from the serviceable system elements. This divides the protection problem into two components. One is the problem of circuit-breaker selection which primarily consists of specifying its performance characteristics for proper application at each location. The second component is the application of relays which detect a fault in a protective zone and initiate appropriate measures ranging from alerting an operator to isolating the faulted equipment. The relay's decision making criteria are provided by currents, voltages and their derived functions. Relays based on power, power factor, current comparison, power comparison, impedence, reactance, modified reactance, current ratio, and sequence components are available. Relays may incorporate time delays before initiating breaker operation. An auxilliary source provides the energy required to initiate circuit-breaker operation. power systems, the continuity of supply is an important consideration and

Fig. 2.1 The protective zones commonly employed in power systems.

under no circumstances can excessive unwarranted isolation of system elements be permitted.

#### 2.2 Generator Protection

Alternators employed by electrical power utilities are provided with separate protective zones as indicated in Fig. 2.1. The equipment in these zones is protected for all contingencies likely to cause serious damage to either the generator or the system to which it is connected. Adequate measures must be employed to protect alternators which are susceptable to many types of faults. In this respect the generator protective zones are rather more complex than other zones such as transmission lines, transformer, motors, and bus bars. Two types of conflicting demands must be balanced to achieve the aim stated previously. The expected damage to the machine, caused by operating under adverse conditions, must be balanced against the disturbance which its immediate removal from the system might cause. To achieve the most favourable trade off, various techniques have been adopted which allow continued operation at reduced system capability in contingency situations. 9,45 This variability in operating configuration leads also to variety in the protection schemes employed to detect these contingencies. The situation is further complicated by the different types of prime movers presently available. An attempt will be made to describe the more usual situations with the realization that the situation will vary in particular applications.

### 2.2 a) Ground fault protection

Many electrical faults involve ground return loops. Generators are, therefore, provided with protective devices sensitive to the flow of current in the ground path. These relays are also sensitive to some ground faults outside the protective zone. <sup>25</sup> In addition, third harmonic currents could

also cause undesireable relay operation. Where discrimination between in zone and out of zone ground faults is not inherrent in the system, the ground current relays are provided with an adjustable delay so that they may be used as back-up protection in conjunction with primary protective schemes. High frequency filtering is employed to limit the relay's response to the third harmonic currents. In addition, the time delays also reduce their tendency to operate during fast transients. In many European installations, where lightly grounded generators are used, ground fault currents are allowed to flow for considerable periods of time. The relays warn an operator of the presence of the condition. The affected generator is disconnected from the system with minimal disturbance after its load is transferred to other units. Though no serious malfunction is expected while operating with this contingency, the development of a second ground fault could cause serious damage.

#### 2.2 b) Unbalanced faults

Negative sequence currents flow in the alternator windings for considerable time when the protective relays in other zones fail to operate for an asymmetrical fault. These currents induce a second harmonic component in the rotor causing its temperature to rise. If the unbalance persists, the rotor may deform due to excessive heating. Because asymmetrical faults are normally due to conditions external to the generator, protection against these faults is provided as a back-up function. Relays, whose operation is based on the negative sequence current component, are employed. Suitable time delays are incorportated to coordinate the breaker tripping with the operation of protective equipment in other zones.

#### 2.2 c) Overload protection

Current-overload protection is also required as back-up for the

failure of protective equipment in other zones. AIEE Standard specifies that "a machine shall be capable of withstanding without injury a 30 second three phase short circuit at its terminals when operating at rated kva and power factor and with fixed excitation at 5 percent overvoltage". Voltage regulators increase the excitation to maintain the terminal voltage, and significantly higher currents are experienced during a fault. An inverse time, overcurrent relay, set at 120 percent of rated full load, can be employed. The terminal voltage collapse, which is inherent in overloads due to faults, is quite often used as an additional criteria for relay operation. The voltage controlled, inverse time, overcurrent relays allow operation when overcurrent and undervoltage conditions are simultaneously present. The time delays, incorporated in these relays, are also coordinated with the other protective elements.

### 2.2 d) Overheating protection

Many factors can contribute to overheating of the generator windings. Thermocouples and thermistors, imbedded in the stator, give a reasonable indication of the winding temperature. The output from these devices is arranged to indicate the temperature, actuate an alarm and/or operate a relay.

## 2.2 e) Overspeed protection

Two types of overspeed protection are available. A detector based on the centrifugal action of a rotating device, mechanically coupled to the shaft, may be provided. Alternatively, an overfrequency device excited by the generator terminal voltage, may perform the same function. These relays can be adjusted to operate at different overspeed levels, and protect the rotating equipment from mechanical damage.

### 2.2 f) Loss-of-excitation protection

Loss of excitation (either partial or complete) of synchronous machines increases the reactive power drawn from the system. Since the prime mover continues to supply power at the pre-fault level, the generator power output remains essentially the same. The reduction in excitation is compensated by the reactive power drawn from the system. The machine will continue to operate as an induction generator if the system is large and able to supply the required reactive power. This mode of operation is inherently hazardous. Depending on the system, either the machine may be taken out of service through operator intervention or it may be tripped by a loss of excitation relay.

### 2.2 g) Protection against motoring of a generator

Motoring results from the inability of the prime mover to supply even the losses of the generating unit and the deficiency is then supplied by the system. In many cases, serious damage to the prime mover may result. For example, in diesel engines an explosion hazard may exist due to unburned fuel in the exhaust while in hydraulic turbines the reverse power flow can result in serious cavitation of the turbine blades. Motoring of an alternator is detected by a relay which operates on reversal of power flow. Limit switches and temperature sensors are used for back up protection.

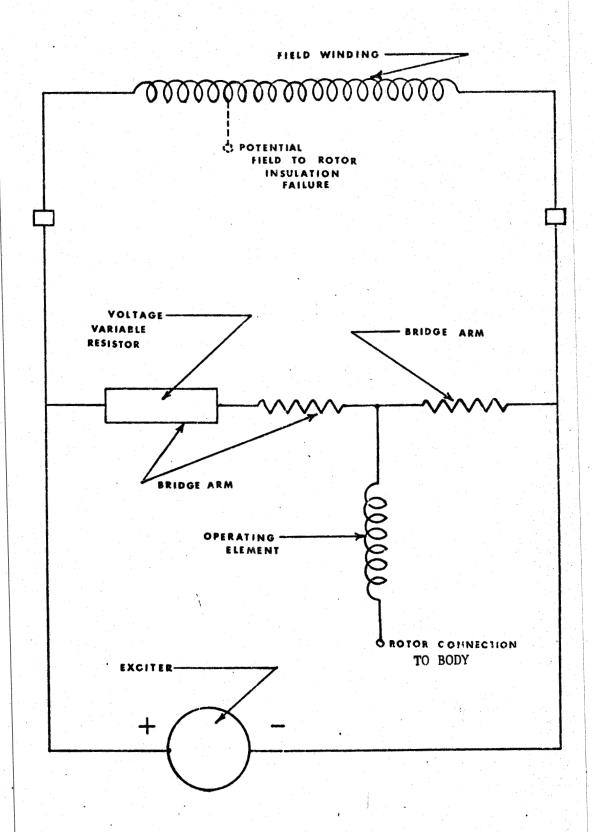

### 2.2 h) Field ground protection

A serious fault condition exists when two or more rotor insulation failures are present. Such faults cause local heating due to the flow of current in the core and excessive vibrations due to the resulting magnetic asymmetries. A balanced bridge technique, depicted in Fig. 2.2, is used to detect the presence of the first insulation failure in the field

Fig. 2.2 A field ground fault detector using an unbalanced bridge technique.

circuit. The excitation for the bridge is provided by the field supply itself. The bridge, as such, does not exist until the first insulation failure. When it does occur, the bridge will only be balanced if the failure is located at the electrical center of the field winding. This is not a likely occurrence and the resulting imbalance manifests as a difference in potential across the detector. An alarm warns the operator who takes remedial action in due course.

### 2.3 Differential Protection of Generator Stators

The generator stator consists of three individual windings which deliver power to the system. The three phases are identical except that they are symmetrically displaced around the rotor of the machine. All other differences are usually incidental and of negligible consequence to the electrical characteristics of the individual stator phase. stator winding consists of a number of turns of conductor, electrically insulated from, but physically imbedded in an iron core which is, under normal circumstances, connected directly to ground. Should the insulation between a conductor and the iron core fail, a serious fault condition will exist on the generator. 9,25,43,46 This fault establishes a new current path from the stator winding, through the iron core to ground. The new current loop is closed through any neutral point grounding impedance, which may be present, to the shorted stator winding. Significant amounts of this current, flowing for a given period of time, will result in localized heating of the stator core. This can cause irreparable damage to the generator. An obvious method, to detect the fault, is to sense the presence of current in the described fault loop. This approach has been successfully employed for many years as a matter of standard practice. The problems associated with measuring the current flowing in

the fault loop, which is not directly accessable, have been solved.

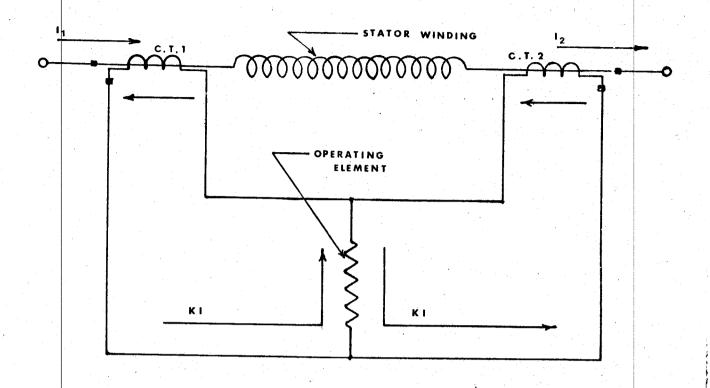

The method used, in effect, treats each phase of the stator winding as a node with three branches. Any difference between the currents entering and leaving the node by the two established routes is taken to be the amplitude of the current flowing in the fault loop. Most relays react to significant amounts of this current at speeds which make the action dependent on its root mean squared value.

The severity of the stator ground faults, as previously described, tends to increase with time and may eventually involve additional phases. The most effective protection afforded against irreparable damage, caused by such faults, is differential current protection.  $^{25,43,45}$  In these schemes, current entering and leaving a winding is compared in a differential circuit and the difference is used to operate a relay. Differential protection as applied to one phase of a generator is depicted in Fig. 2.3. During normal operation, or for faults outside the two current transformers, the current,  $I_1$ , entering the winding is equal to the current,  $I_2$ , leaving the winding if leakage and transducer mismatch is neglected. The operating current, which is proportional to  $(I_1-I_2)$ , is small and the restraint may be adjusted such that this difference does not operate the relay. When an in-zone fault occurs, one of the currents will increase while the other will decrease. The increase of the relay operating current will depend on the severity of the fault.

External faults produce an increase of the same magnitude in both  ${\rm I}_1$  and  ${\rm I}_2$ , but the asymmetries in the differential circuit and the transducers produce a considerable change in the magnitude of the difference current. Undesirable tripping may still be avoided by increasing the

Fig. 2.3 A differential current protection scheme for one phase of a generator.

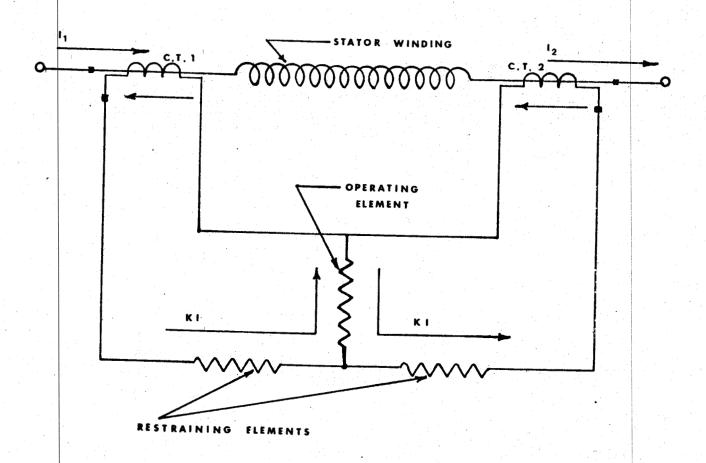

mechanical restraint of the relay. This desensitizes the protection scheme, a consequence which is quite undesirable. To overcome this disadvantage, a method of electrical restraint, whereby the restraining torque is provided by the currents, I<sub>1</sub> and I<sub>2</sub>, is employed. The restraining windings are polarized to provide torque proportional to the vector sum of the two currents, I<sub>1</sub> and I<sub>2</sub>. As the amount of current passing through the stator winding increases, either due to changing load conditions or external faults, the magnitude of the restraint increases proportionally. This type of protection is referred to as percentage differential protection and a single phase connection of the relay elements and current transformers is given in Fig. 2.4. Two types of percentage differential protection schemes are available. One is a fixed percentage type, while

Fig. 2.4 Connection diagram of one phase of a percentage differential protection scheme.

the other is of variable percentage <sup>45</sup> (greater percentage at higher currents). The fixed percentage type is slower and is able to overide the d-c transients in all but the most extreme cases. The variable percentage relay is, due to its greater speed, inherrently more susceptable to misoperation caused by d-c transients. Specific measures, such as including high-pass filters, are therefore employed to overcome this difficulty.

### 2.4 Transient Characteristics of the Fault Current

An understanding of the transient behaviour of the fault current is essential to appreciate the dynamic performance of a percentage differential relay. The analysis of a short circuited generator is well under-

stood and documented. 43 The following can be assumed to obtain a describing function for the fault current:

- the capacitive components of the difference current are negligible,

- ii) the speed of the generator remains essentially constant during the interval being considered,

- iii) the mutual inductive effects are balanced,

- iv) the excitation remains constant during the interval being considered.

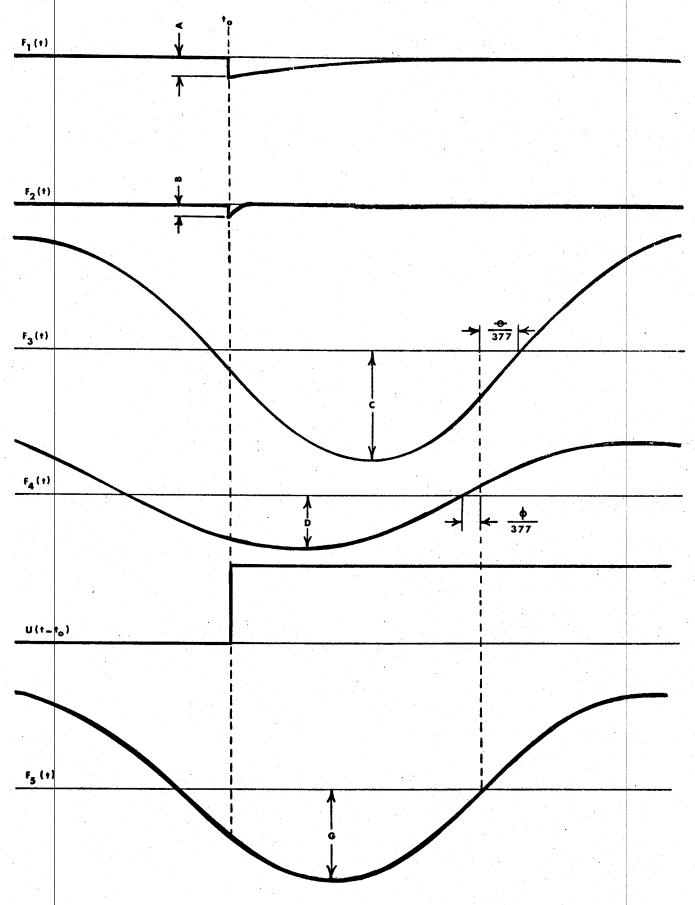

This describing function, I<sub>f</sub>, may be written as:

$$I_f = (F_1(t) - F_2(t) + F_3(t) - F_4(t)) U(t-t_0);$$

(2.1)

where

$$-\frac{t-t_0}{T_1}$$

$= A e$  ;  $F_2(t) = B e$

$$F_3(t) = C \sin(\omega t - \phi)$$

;  $F_4(t) = D \sin(\omega t + \theta)$

and

A = G Sin(

$$\omega t_0$$

) - C Sin( $\omega t_0$ - $\phi$ ); B = G Sin( $\omega t_0$ ) - D Sin( $\omega t_0$ + $\theta$ )

$t_0$  is the time of fault incidence

$$F_{s}(t) = G \sin(\omega t)$$

The restraining current I may be similarly described as:

$$I_r = (F_1(t) + F_2(t) + F_3(t) + F_4(t)) U(t-t_0)$$

(2.2)

The function  $F_1(t)$  is the exponentially decaying offset component of the current in one portion of the shorted stator;  $F_2(t)$  is the exponentially decaying component of current in the other portion of the shorted stator;  $F_3(t)$  is the alternating current in the first portion of the stator;  $F_4(t)$  is the alternating current flowing in the other portion of the stator; and  $F_5(t)$  is the pre-fault steady state current in the

stator. These currents are exemplified in Fig. 2.5.

Both the time constants and phase angles of the post fault stator currents depend upon the inductance to resistance ratios of the stator and the system. The current in the shorted portion of the stator will usually exhibit the longest time constant and the greatest deviation in phase from the prefault stator current except for marginal fault conditions. During marginal faults, when only a very small portion of the stator is shorted or when a large impedance (usually resistive) exists somewhere in the fault current loop, the time constant of the offset in the shorted stator winding is quite small. In addition, practically no change would be experienced in the load current and the fault current will be nearly in phase with it.

### 2.5 Percent Differential Relay Response

A qualitative analysis of a percentage differential relay will establish its deviation from the ideal response due to the transient behaviour of the stator.

As was previously indicated, present relay schemes rely on the fault current to produce the operating torque and on the through current to provide the restraining torque. An additional torque may also be provided by a spring to slightly bias the relay in the restraint direction. The torque equation may be expressed as:

$$T_0 = T_f - T_s - T_r$$

(2.3)

where T<sub>o</sub> is the net operating torque and T<sub>f</sub>, T<sub>r</sub> and T<sub>s</sub> are the torques due to the fault current, restraining current and spring respectively.

Although a certain amount of variation exists from one manufacturer to another, the torques acting are normally derived either as a direct or as a second order proportionality to the currents indicated. A qualitative

Fig. 2.5 Typical current describing functions encountered during a fault.

first order proportionality treatment is presented to permit comparison between the schemes used at present and the one proposed in this thesis.

In relays employing first order proportionality, a relatively uniform magnetic field in which the other elements may act is provided.

Full wave rectifier circuits are provided in series with the relay elements to remove the polarity characteristics from the applied currents. The operating torque given by equation 2.3 may be expressed as a function of time in the following form:

$$T_o(t) = K_1 | I_f(t) | - K_2 | I_r(t) | - T_s$$

(2.4)

$K_1$  and  $K_2$  are constants of proportionality relating the currents and torques.  $I_{\mathbf{f}}(t)$  and  $I_{\mathbf{r}}(t)$  are the fault and restraining currents respectively. These currents are defined in equations 2.1 and 2.2 and may be expressed as:

$$I_{f}(t) = (Ae^{-\frac{t-t_{o}}{T_{1}}} - Be^{-\frac{t-t_{o}}{T_{2}}} + Csin(\omega t - \phi) - Dsin(\omega t + \theta)) U(t-t_{o}) (2.5)$$

$$I_{\mathbf{r}}(t) = (Ae^{-\frac{t-t_{o}}{T_{1}}} + Be^{-\frac{t-t_{o}}{T_{2}}} + C\sin(\omega t - \phi) + D\sin(\omega t + \theta)) U(t-t_{o}). (2.6)$$

The sinusoidal portion of these functions may be reduced to a single sinusoid. Equations 2.5 and 2.6 may be modified as follows:

$$-\frac{t-t_{o}}{T_{1}} - \frac{t-t_{o}}{T_{2}}$$

$$I_{f}(t) = (Ae + Be + R_{1} \sin(377t + \alpha_{1})) U(t-t_{o})$$

(2.7)

$$I_{\mathbf{r}}(t) = (Ae^{-\frac{t-t_{o}}{T_{1}}} + Be^{-\frac{t-t_{o}}{T_{2}}} + R_{2} \sin(377t + \alpha_{2})) U(t-t_{o})$$

(2.8)

Several approximations are customarily made to determine the operating characteristic of a percentage differential protection relay.

The transient portion of the driving function and the restraining torque

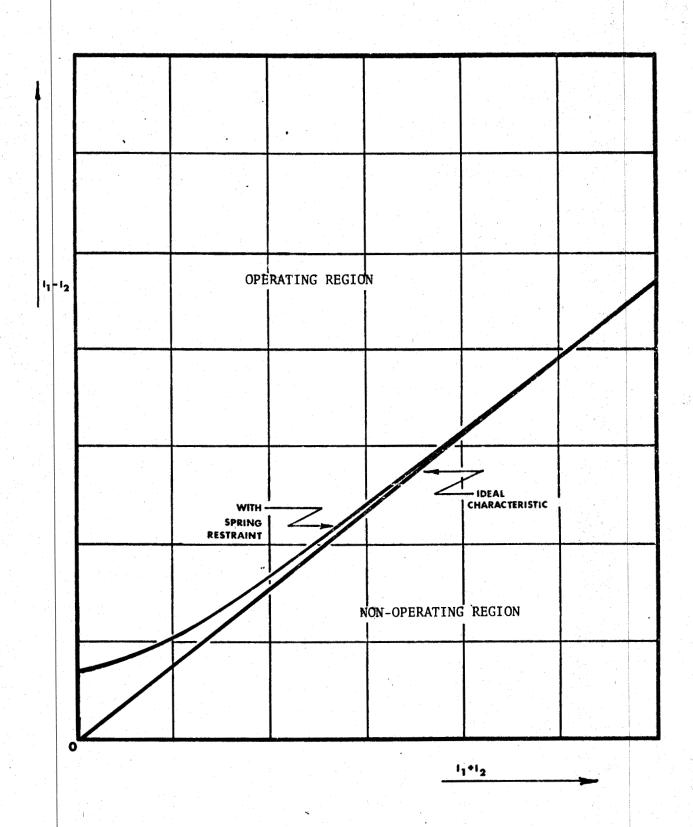

of the spring are usually neglected. The remaining sinusoidal functions define the long term tendency of the relay. The following balancing equation gives the ideal relay characteristic:

$$\frac{1}{T} \int T_{f}(t) dt = \frac{1}{T} \int T_{r}(t) dt.$$

(2.9)

or

$$\frac{\omega K_1}{2\pi} \sum_{t=0}^{t} |I_f(t)| dt = \frac{\omega K_2}{2\pi} \sum_{t=0}^{t} |I_s(t)| dt$$

(2.10)

This equation indicates that the operating characteristic is defined by "the ratio of the steady-state average values of  $I_f$  and  $I_r$  is constant." This ideal characteristic is depicted as in Fig. 2.6. Had the restraining spring constant been included in the equation, the characteristic would have to be modified as also shown in Fig. 2.6. This approach, however, neglects the presence of the transients and the phase displacements between the operating and restraining sinusoidal currents.

The transient, if it is slow enough, may be described as a variable D.C. added to the sinusoidal cycle. The absolute value of the resulting function may be used to describe the generated torque for any cycle as follows:

$$T(\theta) = K \mid \sin(\theta) + x \mid.$$

(2.11)

where

K is proportionality constant including the amplitude of the sinusoid, x is the ratio of the D.C. offset to the amplitude of the sinusoid, x < 1.

An average value of this torque is given by:

Fig. 2.6 Percentage differential protection characteristics illustrating the effect of spring restraint.

$$T(\theta) = \frac{K}{2\pi} \int_{-\Psi}^{\pi} \frac{\Psi}{(\sin(\theta) + x)} d\theta - \frac{K}{2\pi} \int_{\pi}^{2\pi} \frac{\Psi}{(\sin\theta + x)} d\theta. \qquad (2.12)$$

where  $\Psi = arc \sin(x)$

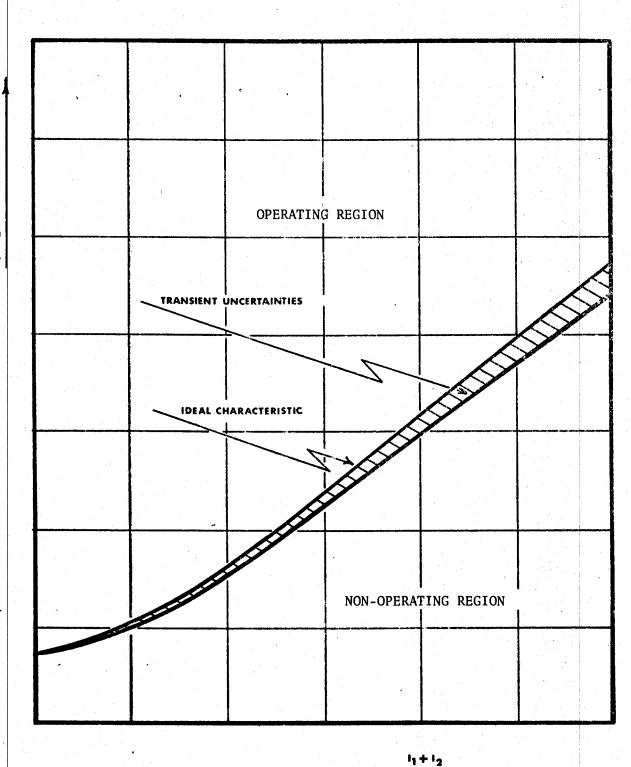

This indicates that the transients always provide additional torque. With the realization that the fault current must always start from zero, and that for marginal fault conditions the fault current transient will always be relatively more significant than the transient on the through current, it is evident that the transient will reduce the criteria required for relay operation. Further, the effect of the transient is not consistant. Fig. 2.7 illustrates the reduction in the precision with which the relay characteristic can be defined when the transient and other effects are included. One factor, which makes the operating characteristic even more obscure, arises from the difference in phase which may exist between the fault current and the through current. Any phase displacement will introduce another element of inconsistency of relay operation. The effect of the transients on relay operation is small in cases where averaging movements are used. In fast acting schemes, these effects can be quite significant.

A brief survey of the important protection requirements of generators with the traditional relay solutions has been presented. Differential current relay operation is particularly stressed to provide a reliable means of demonstrating the results contained in chapter six. In addition, the qualitative analysis of the stator fault current's transient behaviour will provide background information useful for understanding the principles on which the operation of the digital protection scheme, presented in this thesis, relies.

Fig. 2.7 Percentage differential protection characteristic including the faulted stator transient current effects.

-12

### 3. ON-LINE COMPUTER PROTECTION TECHNIQUES

Practical application of on-line digital computers has been confined to data logging 7,24, distance protection of transmission lines 12,22,23,28 and differential protection of transformers 41. System protection by on-line digital computers requires that sufficient information, which is available in the analog form, be digitized and used in decision making. The systems adopted by Mann and Morrison 22,23 and Gilcrest, et al, 12,28 consist of estimating the peak squared values from the samples of instantaneous voltages and currents. The presence of a system fault is detected by cycle to cycle comparison. These techniques, used for extraction of information from sampled parameters, form the core of the protection schemes developed to date and are examined in this chapter.

### 3.1 Cycle to Cycle Comparison

Mann and Morrison<sup>23</sup> utilized this technique to provide distance protection for a three phase transmission line using a digital computer. In this scheme, voltage and current data is sequentially sampled fifteen to forty times per cycle and is stored in the computer memory for at least one electrical cycle. The sampled values of the line current are compared with those stored during the previous cycle. Any deviations of sufficient magnitude cause the program to enter a mode where it suspects the existence of a possible fault. The program attempts to classify the fault while the computer continues to update the transmission line parameter information. Suitable calculations then determine the validity of the suspected fault condition and an appropriate action is initiated.

The technique appears attractive but it does have several drawbacks for differential protection applications. For adequate differential

protection sensitivity, the protection scheme must be able to distinguish between faulted and non-faulted conditions with cycle to cycle differences in the order of one percent. To achieve this sensitivity, the sampling must either be carried out at high speed or it must be synchronized to the system frequency. For instance, in a non-synchronized data sampling system, the reciprocal of the maximum rate of change of the sampled parameter, multiplied by the maximum allowable error in absolute terms, will yield the maximum permissible time between samples. For an accuracy of one percent on a sixty Hz sine wave, the time between samples should not exceed thirty microseconds. Because this sampling rate is excessive for practical systems, a synchronized scheme should be considered.

The emphasis now shifts to the problem of accurately determining the zero crossings of a parameter for synchronized sampling. The data may be sampled at any rate and suitable corrections computed to relate its value to fixed times with respect to the zero crossings of the parameter. Alternatively, suitable synchronized sampling would insure that each sample retains a fixed orientation to the zero crossing. This method will make no additional demands on the computer if the required sampling control is provided externally. In either case, synchronization would have to be applied to each parameter separately, especially where unbalanced fault conditions may be experienced.

For the system under consideration, the fault current has such ill-defined zero crossings as to render it unsuitable for synchronized data aquisition. The stator current would generally include a D.C. transient component and any synchronized sampling scheme would be susceptible to serious error. On these grounds the synchronized sampling scheme is not suitable for differential protection.

# 3.2 Computation of Peak Values

Gilcrest, Rockefeller and Udren<sup>12</sup> and Mann and Morrison<sup>22,23</sup> estimate the peak values from the samples of instantaneous voltages and currents. The technique is based on the trigonometric algorithm,  $\sin^2\theta + \cos^2\theta = 1.$  This equation may be expressed as  $(A\sin(\omega t))^2 + (A\cos(\omega t))^2 = A^2$  in terms of amplitude, frequency, and time variables. The sampled value of the sinusoid at time,  $t_1$ , provides the term,  $A\sin(\omega t_1)$ . The term,  $A\cos(\omega t_1)$ , is computed from the rate of change of the sinusoid at  $t_1$  and the angular velocity,  $\omega$ . The technique relies on the computer's ability to generate the derivative of a given parameter.

In theory, the algorithm works fine except that the accuracy of this technique depends on the sampling rate. This aspect is not fully reported in the published literature. The accuracy of the generated time derivative and the computed peak squared values were investigated.

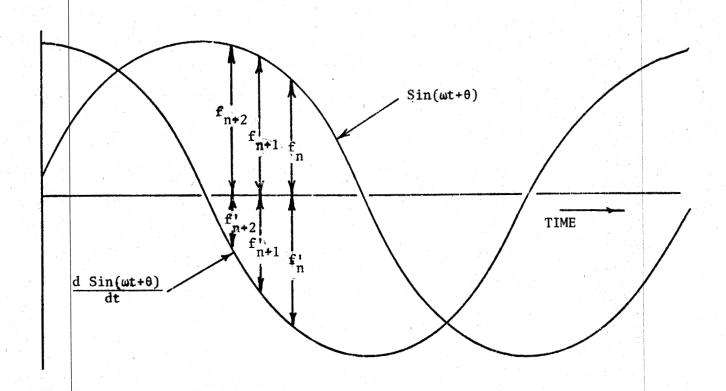

The following assumptions were made for computing the time derivative of an input sinusoid:

- i) The sampling frequency,  $F_s$ , is constant.

- ii) The input function is an undistorted, constant amplitude and frequency sinusoid.

The samples are subscripted such that the lowest subscript denotes the latest sample as illustrated in Fig. 3.1.

The algorithm used to calculate the latest value of the first differential,  $f_n^{\prime}$ , was based on the equation,

$$f'_{n} = (f_{n} - f_{n+1})F_{s} + 0.5((f_{n} - f_{n+1})F_{s} - (f_{n+1} - f_{n+2})F_{s})$$

$$= (1.5f_{n} - 2.0f_{n+1} + 0.5f_{n+2})F_{s}.$$

(3.1)

Fig. 3.1 A typical segment of an input parameter and its first difference.

### 3.3 Evaluation of Computation Technique

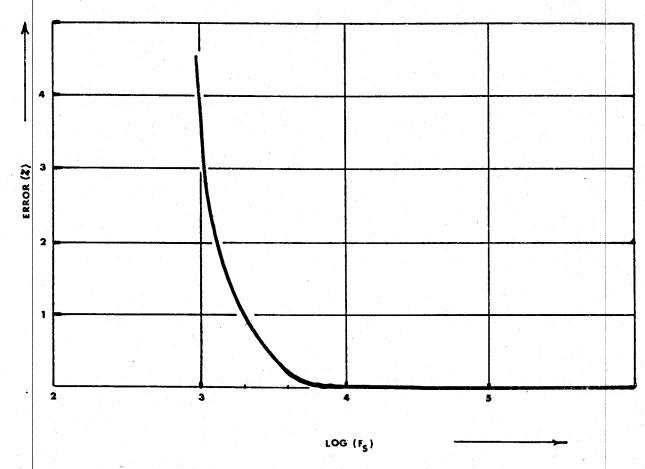

An input function, 10 sin 377t, was generated in the digital computer. The sampling frequency was increased from 100 Hz to 10 kHz and equation 3.1 was used to compute the first derivative at each sampling time. The first derivative of the input, (3,770)Cos 377t, was also generated. For each sampling frequency, the computed and generated first derivatives were compared and percentage errors were calculated. The maximum percentage error as a function of sampling frequency is shown in Fig. 3.2. This study indicates that sampling frequencies of 2 KHz or higher should be employed.

Fig. 3.2 The maximum percentage error of the computed first derivatives versus sampling frequency.

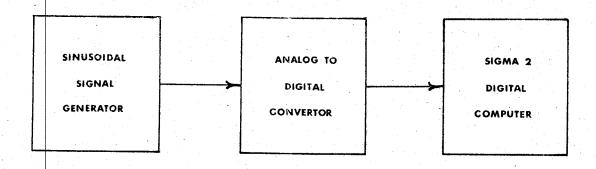

The accuracy of the peak values computed from sampled data was then examined. An input of 0.5 Sin 377t volts was applied to the computer through an analog to digital (A/D) convertor as shown in Fig. 3.3. The peak squared value of the input was calculated using equation 3.2.

$$A^{2} = (f_{n})^{2} + (\frac{f_{n}^{2}}{\omega})^{2}$$

(3.2)

Substituting the value of  $f_n^*$  from equation 3.1, equation 3.2 becomes

$$A^{2} = (f_{n})^{2} + (1.5f_{n} - 2.0 f_{n+1} + 0.5 f_{n+2})^{2} (\frac{f_{s}}{\omega})^{2}.$$

(3.3)

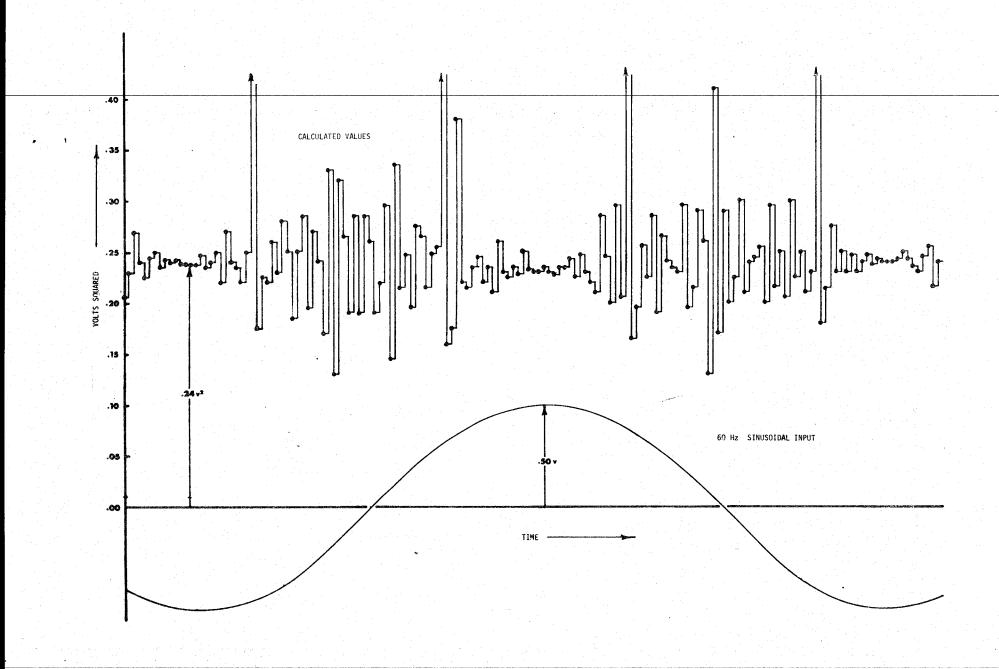

A sampling frequency of 8.5 kHz was used to make  $(\frac{F}{\omega})^2$  equal to  $2^9$ , a mathematical software convenience. The peak squared values were calculated at each sampling time for about two cycles of the input voltage. These

Fig. 3.3 Equipment configuration to compute the peak squared value of a 60 Hz sinusoid.

values were stored in the computer memory and printed at the end of the test period. The calculated peak squared values are plotted as a function of time in Fig. 3.4. The input wave form is also shown to correlate the errors with the sampling points on the wave. The digital computer program written in extended-symbol is given in Appendix I for reference.

The excessive errors, those ploted off scale in Fig. 3.4, resulted from missed samples. This was attributed to the sampling frequency being too fast for the digital computer to handle at times. The missing sample caused a pseudo-discontinuity in the input function, which illustrates a serious inadequacy of the technique. This method is based on the assumption that the input is a single frequency function which, of course, is not true for most power system parameters, especially during fault transients. The technique may be used in cases where the frequency components can be separated and handled individually, or where action

Fig. 3.4 Correlation diagram of the 60 Hz input sinusoid and the computed peak squared values.

can be delayed until all the undesirable frequency components have attenuated. In view of these difficulties, this technique was not used for differential protection of generators.

The perusal of Fig. 3.4 shows that the errors are of two levels of significance. The smaller errors are due to the inaccuracies of the A/D convertor used. The error associated with the least significant bit is two percent of the peak value of the applied input voltage. It is noticed that the errors of the calculated peak squared values are relatively greater when the rate of change of the input signal is maximum. This is due to the input signals being quite small near the zero crossings when the error associated with the least significant bit becomes increasingly important. The solution to this problem lies in optimizing the conversion rates and in using a more accurate A/D convertor.

The cycle to cycle comparison concept for fault detection has been examined. A method for calculating the peak squared values from sampled information has been presented and investigated. Both techniques proved to be unsuitable for differential protection of generators.

#### 4. ON-LINE COMPUTER PROTECTION DESIGN CONCEPTS

Several possibilities were examined to efficiently harness the inherent digital computer characteristics. Those important to power system protection applications, are outlined. A time shared concept is presented as an alternative to a dedicated digital protection approach. Advantages of analog pre-processing of input information are also discussed. The adopted organization of the stator protection scheme is presented along with various conceptual options applicable to on-line digital computer protection design.

#### 4.1 Digital Computer Characteristics

A digital computer is a device which manipulates numbers according to established rules. Recent developments have increased the data handling speed and it is now possible to process a large number of parameters as they are generated. A system may be controlled by an on-line digital computer using outputs derived from these parameters. The input information handling capability and the control function generation is limited by the computation and conversion speeds. Although there is no basic difference between the digital computers used on-line and those used off-line, variations do exist in the form of number and types of input devices provided, the relative sizes of the direct access memory, and the speed and flexibility of the central processor.

The major advantage of modern electronic digital computing machines is their inherent flexibility which arises from an ability to perform conditional branches. Conditional branching, based on the comparison between two numbers, enables the computer to change the sequence or priorities in executing different functions in a plant. Digital computers are also able to choose the events for analysis based on decisions made

using the criteria provided. A digital computer is not limited only to performing manipulations on numbers according to established algorithms based on conventional mathematics. It may, therefore, be able to generate control functions which may not be realizable in analog devices. Another advantage of considerable importance is the computer's ability to selectively store information and subsequently reproduce it in various hard and/or soft copy forms. Off-line analysis may also be incorporated to provide a more sophisticated output.

The computation and conversion speeds, as already mentioned, are finite and it is, therefore, impossible to generate all conceivable control functions within the time available in an on-line application.

However, a very simple technique may often be used to approximately generate an otherwise complicated function to reduce the computation requirements.

The computer may have to be located away from the plant to provide a stable operating environment. Some means of communication between the computer and the plant is required. The information processing rate is now also governed by the communications facility provided. Also, the exclusive use of a digital computer for power system protection may not be economically justifiable and a time shared approach has, therefore, been advocated.

# 4.2 Multi-purpose Computer Rationale

Protection systems are required to operate only occasionally. The flexibility of digital computers enables their application to power system protection in a time shared mode. A considerable amount of computing capability is required during faults. On other occasions, a major part of this capability could be assigned to other on-line and/or off-line applications. Also, communication between the various computer tasks could be advantageously implemented to improve system operation. The

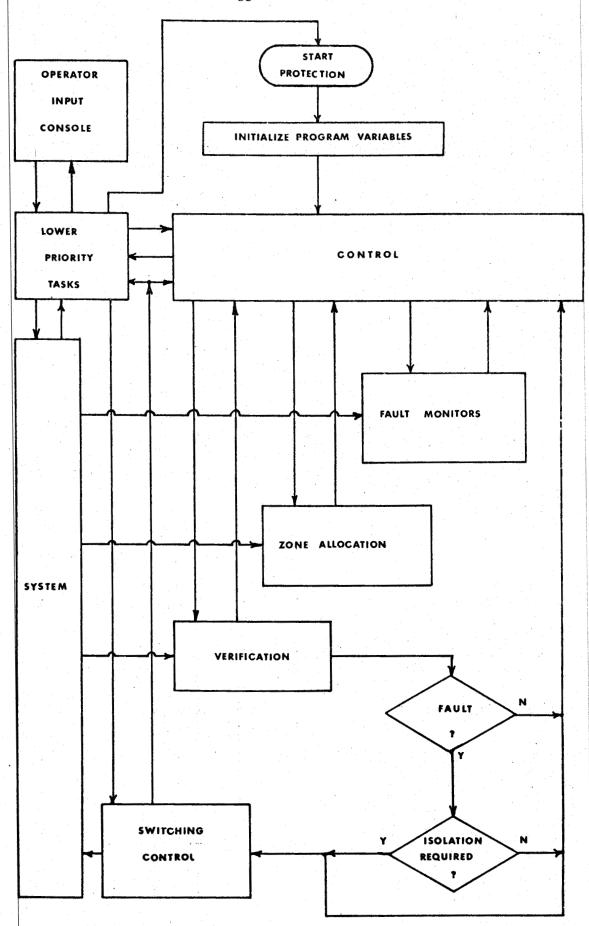

design of the protection scheme should, therefore, be such that it can be adapted to a time shared computer. Fig. 4.1 shows a protection scheme based on this multi-purpose concept.

#### 4.2 a) Executive program

The primary element linking a protection program to the computer software will be a control sequence. It should select the various tasks on the basis of their importance to improve the system performance. The decisions should be made by considering the information, provided by an operator, calculated by the computer and/or provided by the protected system. Since the protection function will, of necessity, be the highest priority in the computer hierarchy, the control sequence must be closely linked to the various fault monitors.

#### 4.2 b) Fault monitors

The monitors should be continually called upon to examine pertinent parameters to determine the possibility of the system being abnormal. If so detected, the controller would execute the required fault determining routines. This technique would be modified to adopt a system's approach as the technology develops. The controller should also communicate useful information between the monitor and the other programs in the computer memory. In addition, it must save the data which may be required by the monitor on a subsequent pass.

### 4.2 c) Zone and phase allocation

In case of an abnormality, a routine to localize the fault condition would be initiated. The zone allocation routines should determine the most likely involved element and the affected phases. These routines can receive data from the system at much higher rates than would be advisable

Fig. 4.1 The logic organization of a digital protection scheme in a time shared mode.

for the monitor. The allowable decision making time will be the main criteria for this speed. Allocation routines should simplify the fault monitors and improve the overall computer efficiency. While the disturbance is being allocated a zone, the protection of other system elements should not be completely neglected. The allocation should be indicated to the control which will then activate the appropriate fault verification routines.

#### 4.2 d) Fault verification

The fault verification routine must establish whether the condition warrants any action. A large variety of verification routines will have to be incorporated to provide for all possible faults. The routines relating to severe faults should reside in core memory while others could be stored on magnetic tape and/or disc for transfer to the active memory as and when required. The continuity of protection provided for all elements must be ensured while a particular possible fault is being verified.

# 4.3 | The Hybrid Computer Rationale

Employing analog computing techniques could simplify the overall protection scheme. This would be an especially important consideration in monitor design. The operating functions of protection schemes should be derived from the available system parameters. For example, the relay operating current in a differential protection scheme may either be computed or derived using analog methods. If it is digitally generated, some error will result. On the assumption that the system is operating without a stator fault, the line and neutral end currents, of a particular stator phase, have the same amplitude and phase angle. The minimum error is similar to that due to sequential sampling of a single sinusoid. The maximum error will occur as the function passes through zero. The

better than one percent. The percentage differential protection schemes have operating characteristics which demand such accuracies. Using sampling rates of this order will not leave sufficient time for computation. A sample and hold circuit used in conjunction with the A/D convertor is one possible solution while a parallel A/D conversion system is another. An analog device could also be used to process the line and neutral end currents in parallel. The phase delays are similar for both channels and as such do not result in significant errors. Analog devices may, therefore, be used to reduce the sampling frequency requirements.

## 4.4 Design Concepts Applied to Differential Protection

The digital stator protection scheme was adapted to a time shared approach by structuring the organization as shown in Fig. 4.2. Various operating alternatives ranging from parameter selection to data processing were examined for the fault monitor, the phase allocation and fault verification sequences. The explanations, which accompany the selected alternatives form the theoretical framework for the digital protection scheme.

# 4.4 a) Fault monitor

As already discussed, the monitor sequence execution time should be as small as possible. Several options were available when the monitor was being designed. The most basic option was the choice between parameters on which to base its operation. Only two parameters, stator currents and terminal voltages, were readily available on which a simple monitor could be based. Several different combinations of both the current and voltages were also possible. For example, either the terminal voltage of each individual phase could be checked periodically or the instantaneous sum

Fig. 4.2 The logic organization of the proposed digital percentage differential protection scheme.

of the three terminal voltages could have been used in a detection scheme. The generator terminal voltages will include a zero sequence component during unbalanced faults. A sample to sample comparison technique or an amplitude threshold detection system might be employed. Balanced faults and faults involving only a small percentage of the winding will have only a small zero sequence component. In addition, external unbalance would have similar effects. The individual phase voltage variation would also be experienced due to internal and external changes. Also, using voltages as the detecting parameters would involve digitizing more signals. This parameter was therefore rejected for fault incidence detection.

The methods using the stator currents for detecting the incidence of a fault were then examined. Using the currents at the line and neutral end of the generator winding which are both available, the following options are possible for the monitor design.

- i) The instantaneous sum of the three phase currents (equal to zero for normal balanced conditions) at the line end, the neutral end, or their sum could be monitored as one parameter.

- ii) The currents in each phase either at the line end, the neutral end, or their sum, could be periodically examined.

- iii) The instantaneous difference between the line and neutral end currents, in each phase, could be checked.

- iv) The instantaneous sum of the three difference currents measured in option iii) could be periodically examined.

Both i) and ii) above are sensitive to changes internal and external to the generator. This could be used when a monitor is required to detect external as well as internal disturbances. In this application, the monitor will initiate checking even when the system load changes. To avoid this, the detection criteria will have to be increased thereby compromising the sensitivity of the scheme. Method iii), employed in percentage differential protection schemes, overcomes this difficulty and is more suited to

protect against stator faults. The principles of this scheme have already been discussed in Chapter 2. Its basic operation is similar to that of a differential amplifier. The principle of instantaneous summation of the three difference currents, iv), has some merit because it is as sensitive to stator ground faults as is method iii). In addition, the monitor requires only one operating parameter instead of three as for iii): but it is insensitive to faults not involving the ground loop. This problem might be solved by making the currents of each phase artificially different from other phases. While most faults will involve ground, a distinct possibility exists that the generator may experience a two phase fault. For these reasons, method iii) was implemented in the monitor design.

A cycle to cycle comparison technique was discussed in paragraph 3.1. It was noticed that, though it has been used in transmission line protection, it is not suited to stator differential protection. The change of difference current between consecutive samples could be an alternate detection principle. The increase of this current at the inception of a fault may be quite small. Should the terminal voltage be passing through zero at the time, the change in the initial difference current will be difficult to detect. The condition is alleviated somewhat because the parameter will undergo its maximum rate of change four milliseconds later. The technique was tested to examine its ability to detect the onset of a fault. The detection time was found to be variable and depends on the incidence angle and fault severity.

The monitor could also be based on the amplitude of the difference current being in excess of a software threshold. This technique is also subject to delays due to the nature of the stator fault current describing function presented in Chapter 2. However, these delays are significant

only for marginal fault conditions. The estimated maximum delay would be similar to that in the operation of a monitor based on the first difference of the fault current. The software threshold technique is simpler and was therefore adopted for the monitor design.

# 4.4 b) Phase allocation sequence

In generators, capacitive coupling exists between the stator phases. At the inception of a fault, high frequency leakage currents flow in all stator phases while the capacitors discharge. These currents bear a proportional relationship to the severity of the fault and the first evidence of a severe fault may, therefore, appear on a healthy phase. By simply allowing the first sample which exceeds the monitor threshold, to indicate the possible faulted phase, verification may commence incorrectly.

A fault allocation sequence was included in the protection package to improve the utilization of computer time by increasing the probability of correctly selecting the faulted phase. This sequence, beginning with the first sample of difference current that exceeds the monitor threshold, compares consecutive samples from the three phases. In each set of three, the largest sample is taken as an indication that its originating phase is faulted. The first phase to indicate the largest difference current on two occasions is selected as the phase most seriously involved in the fault.

#### 4.4 c) Fault verification

As indicated in paragraph 4.2, the fault verification sequence executes the sampling and calculations necessary to adequately determine the existence of a fault. The difference current, which represents the fault current, and the restraint proportional to the average through current were used to verify the presence of stator faults in view of the advantages

of this approach discussed in Chapter 2. While designing the computerized percentage differential protection scheme, techniques to minimize the errors due to fault transients were incorporated. In addition, the decision time for serious faults was reduced as much as possible. It was, therefore, essential to process as much of the frequency spectrum of a fault signal as possible.

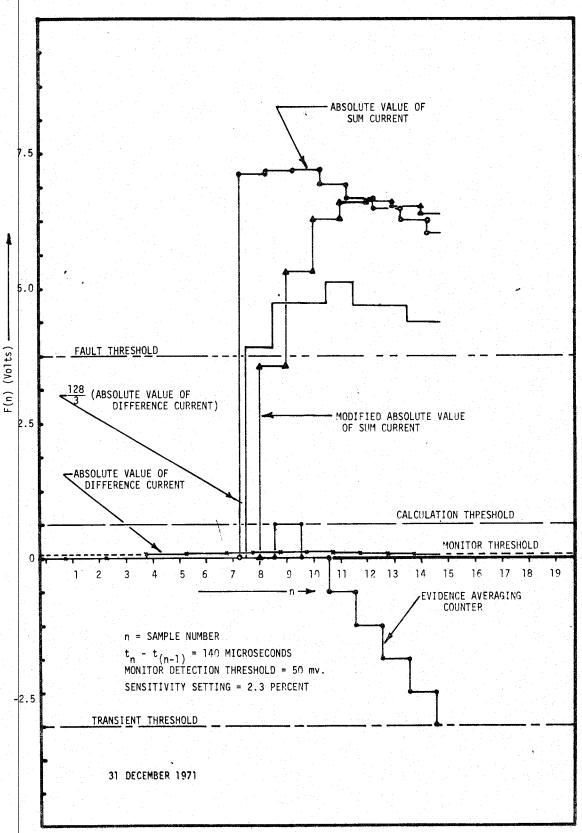

The transient response analysis of the fault current, also presented in Chapter 2, indicates that, while the difference current must rise from zero with a rate restricted by machine and fault parameters, the sum current ( $I_1$  +  $I_2$  of Fig. 2.4) does not. A modified function was generated from the sum current to match the transient response of the difference current. This function enables a comparison of the operating and restraining currents even during the transient period. An approximate first order transfer function was used to generate the modified sum current parameter. The desired transfer function may be written as  $G(s) = \frac{1}{1+Ts}$ . For a given sampling rate, R(n), the sum current modified by the transfer function at the end of the nth sampling interval, for the input, I(n), is given by:

$$R(n) = R(n-1) + K(I(n) - R(n-1))$$

$n = 0, 1, 2, 3, \dots$

= 0 ;  $n < 0$  ;  $0 < K < 1$  (4.1)

If a step input of amplitude A, is applied at n = 0, the output, R(n), may be expressed as:

$$R(n) = \frac{A + (P-1) R(n-1)}{P}$$

;  $P = \frac{1}{K}$ ;  $P > 1$  (4.2)

This function is depicted in Fig. 4.3 for a sampling interval of s seconds and for P = 2. It is apparent that the output approximates the exponential,

Fig. 4.3 The digital and ideal outputs of the first order system for a step input.

$A(1-e^{-\frac{SR}{T}})$ . The time constant, T, depends on the sampling rate and the value of P used. It may be derived by equating the output at n=1 and the value of the exponential at t = s and is given by

$$T = \frac{s}{\ln(\frac{P}{P-1})}$$

The generated transfer function is very easy to implement and its accuracy is governed by the sampling rate and the time constant required. The difference current accuracy is also governed by similar factors. Errors in the difference current and the simulated function tend to cancel because they are of the same type and are governed by the same factors.

The technique, advanced above, will allow the processing of stator input data without waiting for the transients to attenuate. Fig. 4.4 illustrates the modified sum and the difference currents for a marginal fault. The sum current is also shown for comparison with the modified function. The modification of the sum current is provided to overcome the

Fig. 4.4 Sampled and derived functions for a faulted stator as used by the protection scheme.

difficulties presented by transients generated during marginal fault conditions. For more severe faults, the fault current transients do not influence the computer's decision.

Time sharing the facilities, either among the various protection functions, required by a power system, or among on-line protection and control functions, may economically justify the application of computers to system protection. Analog pre-processing the input information may still be needed to reduce the digitizing capability of computers applied in this area. A judicious blend of both types of information handling will ultimately provide an attractive computer package for on-line power system protection and control. The proposed organization for the stator protection sqheme is conveniently adaptable to the time shared hybrid concept. adopted fault monitor design is simple yet efficient. Its sampling rate and detection threshold may be adjusted to meet the eventual needs. design principles of the phase allocation and fault verification functions will commit more computation capability to the protection function as the In addition, these sequences have been conceived to take advantage of digital computer data processing speeds to ascertain the existence of stator faults faster than conventional relays.

## 5. DIGITAL PROTECTION SYSTEM DESCRIPTION

The purpose of this project was to examine the feasability of using general purpose computers for percentage differential protection of alternators. Secondly, it was to provide experience in digitizing and processing power system parameters for future on-line computer applications. The SDS Sigma 2/AEI TR-48, situated in the Control Engineering Laboratory, was employed and is described in this chapter. Concepts, presented in Chapter 4, are explained in terms of the hardware and software used in their implimentation.

# 5.1 Digital Computer Facility