# REDUCTION OF CO-SIMULATION RUNTIME THROUGH PARALLEL PROCESSING

A Thesis Submitted to the

College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the degree of Master of Science

in the Department of Computer Science

University of Saskatchewan

Saskatoon

Ву

Jason Coutu

©Jason Coutu, October 2009. All rights reserved.

# PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Computer Science

176 Thorvaldson Building

110 Science Place

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

S7N 5C9

## ABSTRACT

During the design phase of modern digital and mixed signal devices, simulations are run to determine the fitness of the proposed design. Some of these simulations can take large amounts of time, thus slowing down the time to manufacture of the system prototype. One of the typical simulations that is done is an integration simulation that simulates the hardware and software at the same time. Most simulators used in this task are monolithic simulators. Some simulators do have the ability to have external libraries and simulators interface with it, but the setup can be a tedious task. This thesis proposes, implements and evaluates a distributed simulator called PDQScS, that allows for speed up of the simulation to reduce this bottleneck in the design cycle without the tedious separation and linking by the user. Using multiple processes and SMP machines a simulation run time reduction was found.

# ACKNOWLEDGEMENTS

Dwight, David, Doug, Andrew, my wife and kiddies... They have all had much more patience with this than I deserve, Thank you!

This thesis is dedicated to my wife. When this thesis started, we had one wonderful toddler in the house. During this thesis we had two more wonderful, busy children. My wife has been blessed with patience as she has raised these kids and stayed sane while I worked away on my thesis. Thank you dear.

# CONTENTS

| Pe            | ermis                  | ssion to Use                                         | i    |  |  |

|---------------|------------------------|------------------------------------------------------|------|--|--|

| $\mathbf{A}$  | bstra                  | act                                                  | ii   |  |  |

| A             | Acknowledgements       |                                                      |      |  |  |

| Co            | onter                  | nts                                                  | iv   |  |  |

| $\mathbf{Li}$ | $\mathbf{st}$ of       | Tables                                               | vi   |  |  |

| Li            | $\operatorname{st}$ of | Figures                                              | vii  |  |  |

| Li            | $\operatorname{st}$ of | Abbreviations and Glossary                           | viii |  |  |

| 1             | Intr                   | roduction                                            | 1    |  |  |

|               | 1.1                    | Definitions                                          |      |  |  |

|               | 1.2                    | Motivation and Thesis Statement                      |      |  |  |

|               | 1.3                    | Thesis Outline                                       | 6    |  |  |

| 2             | Ba                     | ckground and Related Work                            | 7    |  |  |

|               | 2.1                    | System Design                                        | 9    |  |  |

|               |                        | 2.1.1 Co-Design environments and Co-Design languages | 13   |  |  |

|               | 2.2                    | Simulation                                           | 18   |  |  |

|               | 2.3                    | Partitioning                                         | 21   |  |  |

|               |                        | 2.3.1 Partitioning for Simulation                    | 22   |  |  |

|               |                        | 2.3.2 Partitioning for System Configuration          | 24   |  |  |

|               | 2.4                    | Parallel Processing                                  | 26   |  |  |

|               | 2.5                    | Distributed Simulations                              | 30   |  |  |

|               | 2.6                    | Summary                                              | 34   |  |  |

| 3             | $\mathbf{Pr}$          | ototype and experiment design                        | 36   |  |  |

|               | 3.1                    | Supporting Evidence                                  | 37   |  |  |

|               | 3.2                    | Modifications to SystemC                             | 38   |  |  |

|               | 3.3                    | Research Methodology                                 | 41   |  |  |

|               |                        | 3.3.1 Design Under Simulation                        | 43   |  |  |

|               | 3.4                    | Selection of experimental systems                    |      |  |  |

|               | 3.5                    | Summary                                              |      |  |  |

| 4 | ${ m Re}$ | m sults                                        | 48 |

|---|-----------|------------------------------------------------|----|

|   | 4.1       | Motivating experiments                         | 48 |

|   | 4.2       | PDQScS                                         | 53 |

|   |           | 4.2.1 Development process results              | 54 |

|   |           | 4.2.2 Performance results                      | 56 |

|   |           | 4.2.3 Analysis of Processing vs. Communication | 63 |

|   | 4.3       | Comparison to Parallel SystemC                 | 64 |

|   | 4.4       | Summary                                        | 65 |

| 5 | Cor       | nclusions and Future work                      | 66 |

|   | 5.1       | Conclusions                                    | 66 |

|   | 5.2       | Future Work                                    | 67 |

# LIST OF TABLES

| 2.1 | Reviewed Distributed Simulators | 33 |

|-----|---------------------------------|----|

| 4.1 | Motivating experiment machines  | 49 |

| 4.2 | Results Summary                 | 65 |

# LIST OF FIGURES

| The traditional design path                                                                            |

|--------------------------------------------------------------------------------------------------------|

| The boundary between hardware and software                                                             |

| Systems configuration solution space                                                                   |

| Partitioning steps of a single element of a Co-design, from Kalavade and Lee's partitioning paper [30] |

| Code partitioning example [34]                                                                         |

| Design under simulation                                                                                |

| Testbench setup                                                                                        |

| Motivating Experiment Run Times                                                                        |

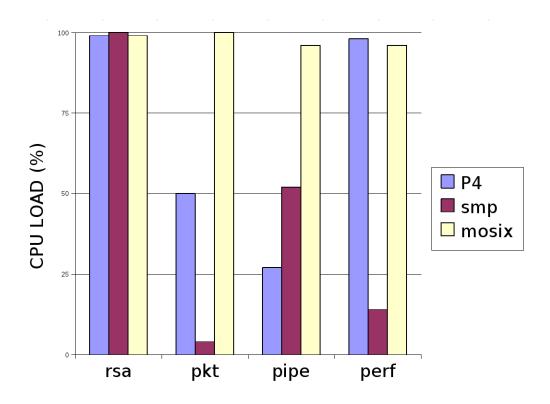

| CPU Load for Motivating Experiments                                                                    |

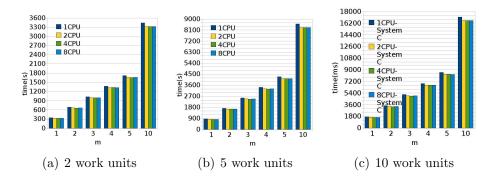

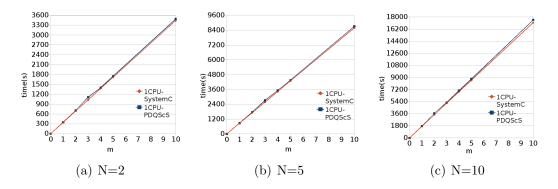

| Unmodified SystemC Simulator Run Times                                                                 |

| PDQScS 1 CPU Run Times                                                                                 |

| Run Times with No Simulation Loop 60                                                                   |

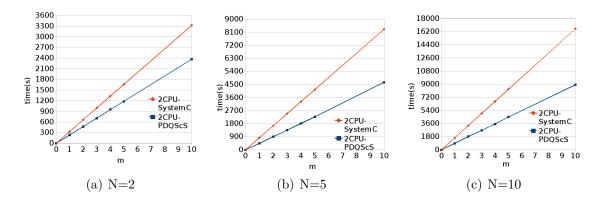

| PDQScS 2 CPU Run Times                                                                                 |

| PDQScS 4 CPU Run Times 61                                                                              |

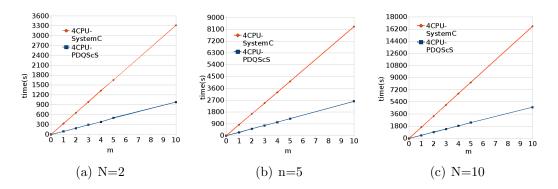

| PDQScS 8 CPU Run Times                                                                                 |

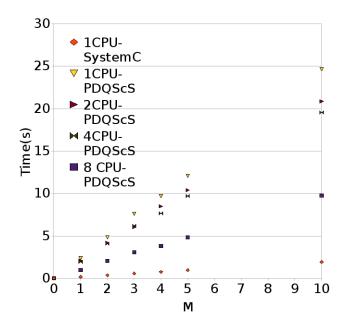

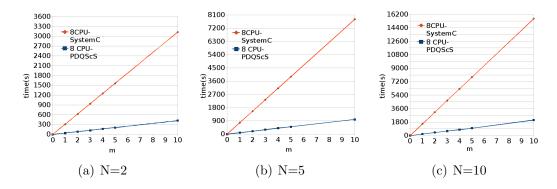

| Speed increase vs work units                                                                           |

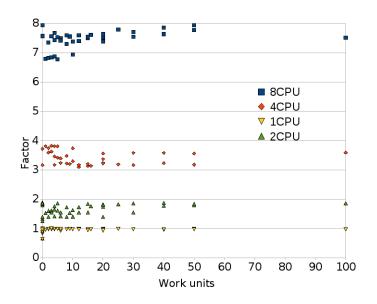

| Communication vs processing                                                                            |

|                                                                                                        |

## LIST OF ABBREVIATIONS AND GLOSSARY

SMP Symmetric shared Memory multi-Processing

DMP Distributed Memory multi-Processing API Application Programming Interface

MPI Message Passing Interface

IPC Inter-Process Communication

HDL Hardware Description Language

PLI Programming Language Interface

IDE Integrated Development Environment

IP Intellectual Property

DUS Design Under Simulation, used to differentiate the testbench

from the design in the simulation

Co-Designed systems The end result of the Co-Design process

Time quantum the smallest unit of time to be simulated by a discrete event

simulator

Process a single running instance of a program; a program may spawn

multiple processes, but each process has its own memory space

Thread a single line of execution of a program, programs may have

many threads which all share the same memory

#### Chapter 1

#### Introduction

Modern electronic systems are composed of both hardware and software components. These systems range from network routers and sensors to control systems in cars and complete microprocessor environments that include operating systems. These new systems have more functionality and complexity than the previous generations of systems. Hardware die sizes are continually decreasing, and transistor gate counts are increasing with every new generation of devices. The range of functionality and complexity of these new systems has increased continually. In 2004 when this thesis began, the International Technology Road-map predicted that over the next 15 years, memory in devices continue to double every 3 years, and chip functionality will continue to increase by 50% every three years[13]. In their 2008 report [14], these trends have held up and are predicted to continue to hold true for the next 15 years.

The designers of these systems must ensure that the Design Under Simulation (DUS) meets various functional and performance requirements. Simulations are done at various levels of detail to predict how the systems will perform if manufactured as designed. As these systems become more complex, the simulations that verify them have to become more complex, and thus, consume more resources. There are two resources related to the run time of a simulation: 1) Time - how long the simulation takes to run, and 2) Processor - how much computational effort is available to the simulation. Additionally the level of detail has an effect on the run time. A simulation at the same level of detail for a more complex simulation will take longer to run. The resource that takes no conceptual effort to consume more of is time. If the designer simply uses the same computer, with the same simulator at the same

level of detail for a more complex design, it will take longer to simulate. This can create a costly delay in the development of new systems.

The simulations that are used in the current design are numerous and time consuming [16]. Some simulations can take days or weeks to complete. This delay of waiting for the results of a simulation can be costly, as more refined design cannot take place until the simulation results have been analyzed. Additionally, there can be large numbers of simulations that need to be run to evaluate possible design alternatives. Thus, reducing simulation time will help reduce design time for new systems.

There are several ways to reduce the simulation run time. Two possible solutions are mixed level simulation, and distributed simulation. Mixed level simulators only use complex models for sections of the simulation when necessary, the remainder of the simulation is run at a higher (more abstract) level that completes faster [1]. Distributed simulations take advantage of parallelism in the system and use multiple CPUs to run the simulation.

Mixed level simulations allow portions of the simulations to run at differing levels of detail, allowing some speed up when some sections of the DUS are run at a more abstract level. Some sections/modules that have already been proven to function as necessary, or represent IP of other companies, can be run as a high level simulation. This allows for reduced simulation run time for these elements of the design, while new sections can be simulated in a more detailed fashion. This can be taken to an extreme where all modules are simulated at a high level and only the intercommunication and connections are simulated in detail.

The strategy for reducing simulation time that this thesis examines is to have portions of the simulation run separately in parallel with a unified simulation clock. Distributed simulations are not new to computer science, or to hardware design. There has been previous conjecture that distributed simulations can reduce run time in complex computer system design simulations [23, 34, 51].

Partitioning of modules into groups for evaluation is nessasary for a distributed simulation. This partitioning can automated or manual. Automatic partitioning

can create modules more quickly than manual partitioning, but this partitioning often creates overhead and the simulation still needs to be explicitly created as a distributed simulation. The simulation can also slow down due to increased overhead and poor partitioning. Manual partitioning results in faster simulations, but makes the designer choose where the simulation is split up and partitioning may take longer. The solution proposed in this thesis looks at enabling the designer to have the maximum number of distributed partitions in a single simulator without having to explicitly create the partitions. Distributing the computing load will allow for faster run times.

Distributing a simulation does not guarantee a faster run time. Communications cost is often a limiting factor in distributed simulations. The communications could take longer than the time to run the simulation on a single processor. Balancing communications cost and distribution is central to an effective solution. The largest component of the communications cost is transfer of the data between the distributed parts. Some solutions will not need the information to be transfered as it is used in place, while other solutions will require the data to be replicated to every location that it is needed. A distributed grid will require the data to be synchronized between machines, while a SMP machine could use shared or local memory and thus not need any data transfer.

Using current simulation techniques, the units that the simulations are broken into for distributed simulation tend to very coarse. This is because the partitioning of the system design for simulation purposes needs to be done by hand, if the benefits of reduced simulation time are to be realized [19]. Often, the partitioning is done solely to use two different simulators because of simulator limitations. One simulator may not be able to deal with a type of design, so the design is partitioned and one portion is run on a specialized simulator. This can speed up the simulation, but the manual partitioning reduces the number of partitions due to the amount of designer work involved.

Several areas need to be examined in any project that wishes to address the run time speed issues in Co-Simulation with a distributed solution. These include how much speed up is possible due to the structure of the system being simulated, and how the software interacts with the hardware in the Co-Designed system. The main problem is how much can be done in parallel due to the way the hardware and software of the DUS interact.

#### 1.1 Definitions

For the purposes of this thesis, the following terms are used as defined below:

- Co-Design: The design of a system in which the hardware and software are codependent, and some modules may be either software or hardware in the final design.

- Co-Simulation: Simulation of a system that requires the simulation of both the hardware and the software running on the hardware and/or the simulation of the hardware and external systems that communicate with the hardware system.

- Distributed simulation: simulations that use multiple processing units.

- Simulation: A step of verifying the functionality and validating the correctness of a design in a controlled environment. Often used before a devices is created to validate the design.

- Monolithic simulator: A simulator that uses one large process to do all of the work for a simulation.

- Partitioning: The division of a device into modules for separation into hard-ware/software components or for distributed simulation.

- Concurrency: The ability of a computer program to perform multiple operations simultaneously. One instance of concurrency is a pipeline where each stage is always executing on a piece of data, but every stage operates continuously. After completion of processing, an individual piece of data is handed to the next concurrent process, while new data is received.

- Parallelism: The ability of a set of related tasks to be completed at the same time without affecting each other.

- Design Under Simulation (DUS): The portion of the simulation that is specification for the new system, device or component.

- Testbench: The portion of the simulation that provides the framework for setup, testing and running the simulation to test the DUS

#### 1.2 Motivation and Thesis Statement

As systems get more complex, the partitioning of systems into software and hardware components, especially co-designed systems, becomes a large and tedious task. There are two types of partitioning that are done. The first form of partitioning determines what will be done in software and what will be done in hardware with respect to the target system. The second type of partitioning is an artifact of distributing the simulation. In this case the partitions determine on which computational node each portion of the simulation will run.

Partitioning for the hardware/software division is done repeatedly during the design cycle of a new system. The partitioning can determine the cost, speed, extensibility and whether the device meets its timing constraints. Each time a module is chosen to be placed in either hardware or software, each of these aspects of partitioning is affected. Balancing the partitions so that the system configuration is optimal is a repetitive task that requires multiple simulations. This makes the simulation time an important factor in the design cycle.

When a distributed simulator is used, partitioning the system into modules to run on each computational node is also done. There is a need to reduce the communication between the modules so that communication does not dominate the simulation. Careful partitioning, often done by hand, can affect the simulation speed.

An improper or poor choice in either or both of these types of partitions can create performance issues in either the simulation or the final device. The problem of partitioning circuits into sets with minimal links across each cut has been found to be NP-Complete [4], while the partitioning of hardware/software without respect to the communication issue has been found to be NP-Hard [30]. A lot of work has been done to try to approximate a viable solution or solve a constrained version of the problem [33, 39, 40].

The number of simulations required to find a system configuration that is in the optimal solution space can be larger than it is possible to explore. Simulating to find the correct hardware/software partition is central to the design cycle for new devices. There are too many simulations that take too long for an exhaustive search of the solution space. This thesis demonstrates a methodology and its implementation to reduce simulation time through the use of distributed simulations. Experiments will be conducted to verify that a distributed SystemC simulator, called Parallel Distributed Quick SystemC Simulator (PDQScS), is capable of reducing the time required to perform Co-simulation.

#### 1.3 Thesis Outline

Chapter 2 covers background material and previous research in Co-Design and Co-Simulation. This review covers papers on the design process of integrated circuits and larger systems, the software for these systems, partitioning problems in hardware/software systems, distributed simulations, and parallel computing. This material includes reviews of current and past Co-Design systems and Co-Simulations. Chapter 3 details the design of the experimental system. It provides an overview of the tasks involved in the experimental system, and how each task was completed. It also examines the research methodology that was used. Chapter 4 discusses the three results of the research for this thesis. The results are described in stages: 1) the original motivating experiments that were done to determine if the solution proposed by this thesis could work. 2) the development of a proof of concept simulator for the thesis. 3) performance results from the proof of concept prototype. Chapter 5 contains conclusions and a discussion of possible future work.

#### CHAPTER 2

## Background and Related Work

The Co-Simulation of hardware and software systems involves many related topics. The context and previous work of each of these must be explored to enable the reader to see the inherent difficulties in Co-Simulation and explain the motivation for possible improvements. The related topic areas are the following: design path, simulation of new systems, division of new systems into hardware and software, communication and techniques for parallel processing, and techniques for distributing simulations. The domain specific interpretation of terms are explained in this chapter. Further definitions can be found in the glossary.

The design path for new systems has multiple stages and has always been time consuming. One of the stages of the design path is simulation. As processors are able to do more work with advances in CPU chip technology<sup>1</sup>, the simulation time should fall. However, systems have become more complex, and simulation has taken more of the design time and not less [42]. Part of this complexity is the interaction between software and hardware components. These new more complex systems require that the software and hardware components both be simulated at the same time. The design of these systems is called Co-Design, and the simulation of these systems is called Co-Simulation.

New techniques and languages to describe co-designed systems were developed along with new simulation tools to work with them. In some cases, hardware description languages (HDLs) were extended to include the ability to attach external

<sup>&</sup>lt;sup>1</sup>Moore's law states that the number of transistors on a complex integrated circuit doubles every two years. It has been shown to hold over the past decades, and is predicted to continue to hold for the next 15 years.

<sup>&</sup>lt;sup>2</sup>The ITRS reports are available at http://public.itrs.net/

software module simulators [37]. In other cases, entirely new languages and methodologies were developed to try to deal with the new complexities in Co-Design and Co-Simulation [31]. In contrast to these, some programming languages have been extended to become HDLs [7].

The general partitioning problem describes the complexity of finding optimal groupings of N objects into M groups. This problem requires that every combination be tested, or  $N^M$  combinations, to find the optimal configuration. Optimal is defined by the version of the partitioning problem under investigation. In Co-Design, the grouping of modules across the hardware/software boundary is part of the partitioning problem. Optimal in this case is defined by the designer of the codesigned system. The partitioning problem in distributed simulations also deals with allocating portions of the simulation to separate computational nodes. Optimal in distributed simulation is the configuration that will provide the best possible speed up for the available resources. These partitioning problems in systems design and distributed simulation are constrained versions of the general problem, but they still have a high degree of computational complexity.

Modern systems have large amounts of parallelism inherent in the design [46]. Parallel processing techniques should be able to use this target system parallelism to reduce simulation time. Parallel processing can be achieved in many ways. Multiprocessor machines, cluster computing, and grid networks all allow applications to run more then one process at a time, thus achieving parallel computation. Symmetric shared-memory multi-processor (SMP) machines offer the ability to use one memory bank and several processors to complete a job that has tasks that can be done in parallel. Cluster computers require dedicated hardware and communications. An alternative to clusters is grid computing. Grid computing often requires the use of special communications methods and software to control the system.

In the past, attempts at distributed simulations of hardware have been tried. TyVis [47] and Ptolemy [31] are examples of major previous attempts. They were unable to do both the high level and low level simulations within their frameworks. As systems required more and more simulations to be done outside of the framework,

distributed simulations were dropped. Non-distributed simulation frameworks were created that were capable of simulating at all levels.

The rest of the chapter covers five topics of background information and related work undertaken with respect to that topic. The first section covers the design and Co-Design process for new systems and the differences. The second section details how and why new systems are simulated, and the problems that Co-Simulation adds over simple simulation. The third section covers the two partitioning problems: hardware/software partitioning, and module distribution partitioning during simulation. The fourth section examines parallel processing systems. The final section looks at techniques for and previous work regarding distributed simulation.

### 2.1 System Design

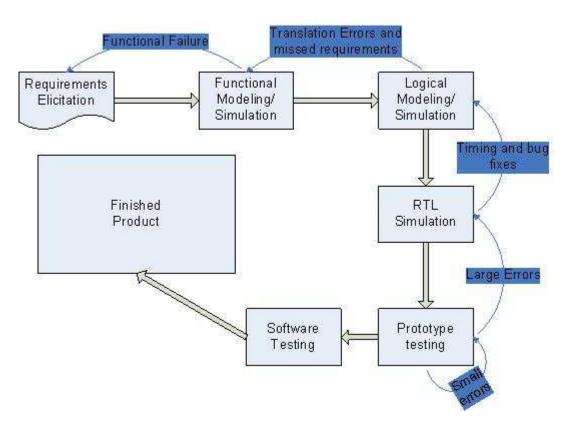

The traditional design path for new HW-SW systems had several steps [45], all of which still exist in some form in Co-Design [35]. The traditional design path is described below and in figure 2.1:

- 1. Determine the statement of work. A description of the task to be completed, its inputs and its outputs.

- 2. Requirements specification produces a document that lists all of the features and performance requirements for the system.

- 3. Functional models are built and tested to prove that the algorithms chosen will in fact meet the functional requirements.

- 4. Logical models are created that implement the algorithms in terms of physically implementable units.

- 5. The results of testing of this model are compared to both the requirements and the results from the functional model. This is done to ensure that no side effects or artifacts have slipped into the design in the translation to the logical level. If problems or mistakes exist, the process goes back to step 3.

- 6. The system is simulated at the register transfer level. This simulation includes timings of the signals as they pass through the components and their connections. If the simulation indicates that the module/device will not perform as designed, return to step 4.

- 7. A prototype system is produced and tested against the test bench that was used in the simulations.

- 8. If at this point, the prototype is deemed to not perform satisfactorily, two options exist. If there are only a few changes (i.e. small errors) that can be fixed by changing some of the connections on the physical board, this is often done. Otherwise, the system needs to be re-synthesized with the problems fixed. (i.e. go to step 3 or 4.)

- 9. Once the prototype has been produced, a copy is turned over to the software team for testing of the software components.

In this older design path, there were some significant problems [54]. Software development is delayed until near the end of the cycle, and the division of hardware and software is determined before design is completed and thus before detailed simulations can be run. Changes in the interface between the hardware and software modules may cause redesign and re-implementation of software modules. This separation of the hardware and software teams requires clear and unambiguous documentation, including recording the changes as they happen so that the changes can be identified and tracked.

The major limitation of the approach was that the division of what components are implemented in software and hardware respectively is determined only once, during the requirements elicitation. This decision is not looked at again in the traditional design path unless significant problems<sup>3</sup> are found. When significant problems are found, the system is redesigned and the partitioning is reexamined.

<sup>&</sup>lt;sup>3</sup>A device that performs too slowly to be useful in the market or a device that consumes too much power are examples of significant problems.

Figure 2.1: The traditional design path

This singular look at the partitioning can create a system that does not have a good cost/performance ratio.

As these design path limitations were recognized, the design path for new systems underwent changes. These systems have become more complex and the design problems more common [54]. Systems now need more simulations, contain more complex designs and have tight timing requirements. With this complexity has come the necessity to simulate hardware, software and the inter-communication at the same time. This requirement has produced changes in the design path, design environments and simulation tools. Simulators that could only deal with hardware needed to be extended to allow for simulation of software modules [48]. Software designers can no longer wait for the system prototype to be completed before testing as the division into hardware and software modules is no longer predetermined.

These problems, and the tighter coupling of hardware and software have spawned new design paths and languages [7, 15]. Some of the new design paths combine new languages and methodologies into a unified design environment, while others try to leverage the existing knowledge base of developers by modifying tools and languages that are in use. Both of these solutions have common elements to the new design path.

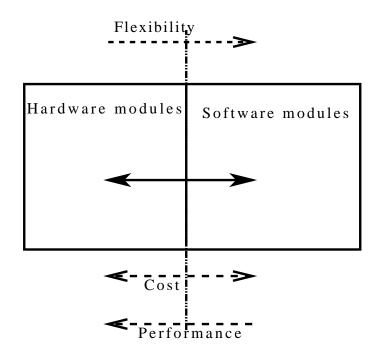

In Co-Design, the design path has not changed in essence, except that now there are additional steps earlier on to integrate the software development, and possibly move some of the modules across the hardware/software boundary. This ability to move components across the boundary has necessitated further simulations at the lower levels to ensure that the requirements are still met. Moving modules across the hardware/software boundary changes the cost, flexibility and performance of the system. This relationship can be seen in Figure 2.2. As the figure shows, as more modules are placed in hardware, performance increases while flexibility decreases. Cost may or may not change as modules move across the partition. A low cost generalized processor could be swapped out for a high cost Application Specific Integrated Circuit (ASIC), or the change may mean that some of the hardware is not needed at all.

Figure 2.2: The boundary between hardware and software

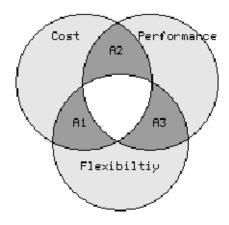

An optimal configuration of the system could mean lowest cost configuration, fastest, best cost for performance or the system that will be the most flexible. The solution space for this can be seen in Figure 2.3. This figure represents the solutions that have the acceptable cost, performance and flexibility. The zones marked A1, A2, and A3, denote sub-optimal solutions. In particular, A3 represents the solutions that meet the performance and flexibility requirements, but will be too costly to manufacture.

#### 2.1.1 Co-Design environments and Co-Design languages

Hardware description languages, or HDLs, are used to design and test new systems. Two examples of these are VHDL and Verilog. HDLs alone are, however, not capable of expressing the design requirements or describing software systems. Thus, new languages and extensions to the HDLs have been developed to fulfill this need. This section provides a survey of these tools.

The earliest projects in the area were to replace the HDLs with a modeler board

Figure 2.3: Systems configuration solution space

to allow output from software simulators to be used as input data for the hardware simulation. These systems had very long simulation run times [27]. This was due to the fact that the software simulation clock ran slower than the hardware modeler board clock which ran in real time. These early attempts required the hardware simulation to be reset and rerun every few time units of software simulation. This reset was necessary because the hardware simulations ran too fast and produced more data than the software simulation could process. Simulation speed decreased as the simulation progressed. This resulted in a delay for large simulations. The main disadvantage of this entire design approach, however, is that it requires the hardware partition to be set and a prototype created [35].

There are substantial differences between the industrial and academic solutions to the Co-Design problems. These include scalability, ability to leverage previous knowledge, and conceptual cohesiveness. The industrial solutions tend to be pragmatic, scalable solutions are built on/into existing tools and languages. This eases acceptance by industry system designers without extensive re-training. The academic solutions are often fresh starts to the problems which allows for a conceptually complete solution. These solutions are rarely scalable, however, and require learning of new design concepts and languages.

The two main HDLs that have the majority of the industrial market share are Verilog and VHDL [42]. Both of these HDLs have been extended to aid in Co-Design.

Both Verilog and VHDL have been extended to provide a Programming Language Interface (or PLI). The PLIs offer the most basic level of interaction, and may not be supported by the entire tool set. Verilog has been extended a number of times to aid in Co-Design. Under Verilog, there is the PLI [37], a scripting solution called VeriSchemeLog [29], and SystemVerilog<sup>4</sup>.

VeriSchemeLog is an automation tool. It uses Scheme (a derivative of Lisp) to provide scripting support for common tasks. It is used to create interfaces between modules and external simulators [29]. These areas are prone to design mistakes and typographical errors. Automating the creation of these interfaces provides internal consistency and eliminates errors caused by spelling mistakes.

SystemVerilog is a standard which was developed by the IEEE and Accellera<sup>5</sup>. SystemVerilog is an additional specification to the Verilog specification that adds system verification elements and co-design constructs to Verilog. With this addition, Verilog will become a full spectrum co-design tool. SystemVerilog is physically implementable, which means that once designs are verified, a prototype can be manufactured without translation to another HDL.

There have been several industrial projects devoted to extending VHDL to enable it to describe a Co-designed system. Examples include the VHDL PLI [27], and Co-ware [50]. VHDL PLI allows designers to add links to software modules in VHDL design. Co-ware is a solution that emphasizes the connections between VHDL and C/C++ modules. These solutions take different paths to solving the problem as they have different views of what is the major problem.

VHDL PLI is an interface first devised to allow VHDL designs to indicate that information is required from an external software module. A PLI now exists in most HDLs, but for simplicity, this thesis will use PLI to subsequently refer to the VHDL PLI. PLI allows VHDL simulators to perform function calls on external simulators to retrieve information. This allows for the inclusion of the Application Programming Interface(API) to be built into the VHDL design. This helps solidify the API and

<sup>&</sup>lt;sup>4</sup>www.systemverilog.org

<sup>&</sup>lt;sup>5</sup>www.systemverilog.org

make the software interface less prone to change. The PLI made it possible to simulate software at the same time as hardware, but this did not integrate the software development in the hardware design process.

Co-ware [50] can use different languages for each type of module. It does this by separating the functional units from the communication channels. This allows reuse and refinement of modules without affecting the entire system. Co-ware can leverage both the C/C++ and VHDL knowledge bases with its mixed language approach. Co-ware was designed and created when co-designed systems did not yet have the access to Co-Simulation, but individual tools for simulation and verification were available. This approach allows for better communication between the hardware and software design teams, but the designs are still not integrated and changing a module from hardware to software requires the module to be recoded for the other simulator.

The early systems were then followed by the academic attempts to enable a single simulation/design tool to represent the entire system for its entire design path. A new system needed to integrate the design of the hardware and software components, and the ability to simulate both at the same time. These academic solutions involved completely new design languages and ways of thinking about systems design. Examples of these are Ptolemy [31], QUEST II [53], and Chinook [26]. Ptolemy attempts to find what they termed better solutions by looking at the system and its communications as a whole. QUEST II is an extension of the Time Warp simulator to allow for VHDL simulations. Lastly, Chinook looks at behavioral designs, and interactively helps the user determine the design for the system.

The goal of Ptolemy is not to reduce design time, but to improve the quality of design by examining the models of computation that are used [31]. Ptolemy uses the terminology of stars and galaxies to talk about the components and their groupings. This use of different terminology and the use of its own XML derivative language to describe how the "galaxies" are connected differs from the industry standard. Additionally, the language is not physically implementable or easily translated to an HDL that can be synthesized.

QUEST II is part of the SAVANT project at the University of Cincinnati. The

aim of the SAVANT project is to build freely available VHDL analysis tools [52]. The QUEST II project focused on the complexity of the system design as the main problem that was causing slower simulations [53]. Thus Wilsey et al. wrote modules for the Time Warp simulator [18] to enable VHDL simulations within the context of QUEST II [47]. Time Warp is a distributed simulator framework for using many interconnected computers to speed up simulation. They found that they could speed up VHDL simulations through distributed simulation.

Chinook is a high level modeling tool that aids developers in the choices for which modules to place in hardware or software [26]. Combined with its companion co-simulation tool Pia, Chinook offers rapid evolution of designs by offering quick high level simulations. Chinook is not designed to be a final development tool, only a preliminary exploration tool to assist with the hardware/software partitioning decision.

There have been two programming language-based systems for the co-design specification problem. These systems are System $C^6$  and SpecC [55]. Both of these new HDLs are based on the C/C++ programming language. They differ on how the hardware portions are specified, and simulated. The simulation portion of this discussion can be found in the next sub-section.

SpecC was proposed by Jianwen Zhu et al. [55]. This HDL was designed from the ground up to be a co-design modeling super-set extension to the C programming language. It has the ability to model a system in differing levels of abstraction at the same time. This allows the mixing of high level algorithms with low level RTL simulations in a single simulation. Any valid design, even if made of mixed levels, can be fed into a simulator for execution and testing. This allows modules to be developed and implemented independently. SpecC is a more academic solution and is not physically implementable.

In contrast to SpecC, SystemC has been proposed by a consortia of companies that are involved in systems design [38]. SystemC is also designed to enable designs to have multiple levels of abstraction combined into a single design. SystemC allows

<sup>&</sup>lt;sup>6</sup>more information at www.systemc.org

the mixing of high level algorithms with low level RTL simulations in the same way as SpecC. SystemC also has a simulation core built into it. Thus, it can compile to a single application with a standard C compiler. This application is a simulation of the design along with its test bench. This inclusion of a test bench in the simulation allows for test bench reuse as the modules are refined. Additionally, the consortia responsible for the development of SystemC have stated that, in future versions of SystemC, hardware modules will be able to go from simulation to physical device with re-implementation of the design in a different HDL.

#### 2.2 Simulation

Simulations can be broken into several groups: un-timed functional simulations, discrete event simulations, and continuous event simulations. Un-timed simulations do not use a clocking mechanism. The difference between discrete and continuous simulations is how event states are handled. While all three types are important tools, this section describes their differences and applicability to Co-Simulation of systems considered in this thesis.

Un-timed simulations do not need a clock of any type. These include Markov models and agent-based simulations, as well as algorithmic simulations. In the design cycle, these simulations are used to prove that an algorithm or process can achieve a design within specifications. Examples of these simulations are programs written to verify correctness of the algorithm. Often it is just the general algorithm that is tested. These simulations typically run at very high speeds and are only done at a preliminary level.

Discrete event simulations treat events and state as blocks and units. The clock cycle used in most system designs makes an excellent division for the blocks of events, and separate the simulation into blocks of time (i.e. a time quantum). Such simulations assume that state changes do not occur between the units, even though we know that, in reality, the value of a system variable may change several times during a clock cycle.

An example of the assumption that state changes are only important at the clock pulses is the modeling of the difference in time it takes a signal to travel over two connections of different lengths. While this time difference is minor, there is a difference. When the time quantum of a simulation is large enough, this difference is ignored. This can cause problems in some circuit simulations, but there are techniques to deal with this problem. Circuit designs which do not use a clock to control state changes, or for which the clock runs extremely fast, are susceptible to this problem. Signals arriving at different times can cause incorrect answers when they fail to arrive in the correct time quantum. In these cases, a discrete simulation with variable length time quantum resolution is used [43].

In continuous event simulations, state change is a continuum. Events can occur instantly, but the change does not have instantaneous effect in continuous event simulations. State changes are not on/off type decisions, but more like the result from an equation. Think of water flowing from a valve. We can look at the water and see that it is flowing, but when we first turned on the valve, was the valve completely on as soon as it was turned? Did the water flow at fully as soon as the valve was on? Continuous simulation has this same view of events and their effects. Events can start at times other than on a time quantum, and their effects are not instant.

How time is treated and used is a major difference between continuous and discrete simulations. In discrete simulations, all events happen at a point in time and all state changes only happen during events. In continuous simulations, events may have a start time, but the properties and state can change at points other than at that events point in time. Discrete simulations can be used to approximate continuous event simulation. Discrete event simulations make up the majority of simulations in design and Co-Design.

As mentioned earlier, the clock tick makes a useful barrier to determine events and state changes. Computers are often thought of as having on/off logic, and the clock as having precise square edges to the pulse. In reality, this clock pulse has a rising time, and a falling time that is non-zero. There are some simulations that use a modified sine wave for the clock pulse in the design and Co-Design process,

but often they are replaced with discrete event simulations that can approximate the results. Thus, they do not provide completely accurate results. Square waves and discrete simulations are used because in most systems, a clock pulse is used to coordinate execution. Continuous simulations are needed to describe circuits that do not use a clock, but that is out of scope of this thesis.

Discrete simulations include any simulation that uses time in non-overlapping blocks. In many discrete simulations, some events are generated from earlier events. Examples of this can be found in most levels of system simulation. A call to use a piece of data may require that the data is loaded from storage before it can be used. Additionally, if a task has been split into subtasks with modules each doing their part and handing the data on to the next module<sup>7</sup>, then each module's completion causes the next to start with new data. Since the time to process an event or a module's actions is known, its results will trigger other modules after that period has expired in simulation time. Thus we can insert events in the queue to happen at the correct point in time.

Simulation time does not equate to real time. High level algorithm simulations often run faster than the target system will run, while low level system simulations will run slower than the target system. The differences in speed are due to the amount of detail required, and the complexity of the simulation. The closer the simulation is to simulating actual wires and transistors, the more details that will need to be tracked by the simulator and the slower the simulation.

Detailed Co-Simulation runs very slowly due to its complexity and the number of components that must be modeled. Co-simulations often combine hardware and software simulators. Early attempts at this involved re-running the software simulator until it reached the same time index as the hardware simulator, then processing the next step before restarting the software simulation [27]. This disparity was caused by the software simulator running faster than the hardware simulator could process the input data. This caused the final steps to be slow as they had to wait for the software simulator to continually catch up from the beginning each step. This was

<sup>&</sup>lt;sup>7</sup>this is called pipelining

later fixed by synchronizing the clock pulses of the two simulators.

Advances have continued to the point where there are now unified simulators that can simulate both the software portions and the hardware portions of a system without the need to run separate simulators, such as: SystemC and SpecC as mentioned in the previous section. This advance has reduced the run time of the simulations [22], but the simulators are now CPU bound [19]. This implies that further run time reduction may be found by reducing or distributing the CPU load.

It is important to note that it is not possible to get the same behavior in a simulation as with the real device. If the design being simulated has some events which happen in a nondeterministic order, then it is impossible to create a simulator that will always give the correct answer, as the answer changes. If two modules write to the same location at the same time, a race condition exists and only one of the writes will appear to have occurred, namely the last write operation to be performed. The simulator does not know which module will execute last in the real device. The order that modules write their data in the simulation may be different in the real execution of the device.

The scope of this thesis is restricted to discrete event simulations of Co-Design systems. The majority of the simulations done during the design cycle are done as discrete event simulations. Continuous simulations are often replaced with discrete event simulations. Additionally, un-timed simulations run at very high speeds and do not need to be sped up further.

#### 2.3 Partitioning

In this thesis, partitioning is used in two separate contexts. The primary aspect of partitioning is the partitioning of modules into hardware or software in the target system. The second aspect of partitioning is the partitioning of simulation modules to run on different computational nodes. Both of these aspects of partitioning have the same background material, but different implications for the work in this thesis. While the background material and problem scopes are related, there are some

differences in these partitionings that must first be discussed before an in-depth exploration of the partitioning problem can occur.

#### 2.3.1 Partitioning for Simulation

Deciding where to run each of the modules, or even how to break a simulation into modules is classified as part of the partitioning problem. There are constraints on what makes a good partitioning. Modules need to communicate with each other in order to pass data and control messages. Distributing the simulation will enable/require some of these modules to run on separate machines. There is a cost in time incurred to communicate between modules across machines instead of within a machine or application. Thus, this partitioning to make simulation modules needs to be done such that it limits the communications cost between simulation modules as much as possible for that system configuration.

There are a great number of possible combinations for this type of partitioning. Given N components, and M computational units to spread them across, this equals  $N^M/M!$  combinations to evaluate to determine the best solution. Since each of the N modules can be assigned to each of the M computational resources, but the resources can be equivalent, each partition can be assigned to any computational unit and still have the same result, thus, the M! is divided out to reduce the assignments of the same partitions to different resources. The problem of finding the optimal partitioning is considered to be NP-complete [33].

A common method for determining where to partition a system is called *min-cut* [2]. Min-cut partitioning attempts to break as few communication lines between modules as possible, while creating the required partitions. Not all min-cut solutions reduce communications. If two modules are highly coupled, the communications cost for running them on separate machines could outweigh the benefits. It can be better to cut many rarely-used connections than one often-used connection. Thus min-cut is not always optimal, but it can have good utility when communications costs are low.

Simulation constraints can help with the decision of how to group portions of the

examined three methods of automatically dividing circuits for simulations [11, 12]. They tested manual partitioning and two methods of automated partitioning (K-FM and K-AFM). K-FM is a 2-way partitioning algorithm by Fidducias-Mattheyeses [20]. K-AFM extends the K-FM model to have acyclic behavior. Both algorithms try to minimize the cut cost. They try to cut as few communication lines as possible while creating M roughly equal sized partitions. The output only indicates where the partitioning is to be made. Neither algorithm creates simulations with the partitions.

Chen et al. found that neither K-FM or K-AFM methods were as effective as a hand-partitioning of the circuit for simulation. The test circuits used in the experiments ranged from 6,000 gates to 64,000 gates. These are relatively small designs compared to what is used today. Simulations of modern systems require the simulation of 1,000,000+ gates and software modules.

Even with the small designs used by Chen *et al.*, they found that their least effective partitioning tool could result in a speed up. The amount of speed up found was dependent on the structure of the circuit, and the partitioning method. Simulations of some circuits could only exploit the physical parallelism through manual partitioning or optimistic simulation<sup>8</sup>. No circuit found less than 3 times speed up across 16 computers. Many found their peak speed up, however, across 4 or 8 computers. This is likely due to the small size and complexity of circuits used in the experiments.

Some a priori knowledge can help with the partitioning. There are often areas of a design that require data to be processed at the same time in different modules. Obviously, these represent excellent modules to run on different computational nodes. It has also been shown that some areas of a design are particularly excellent candidates for separation onto distinct compute nodes, specifically hardware modules that demonstrate symmetry [33].

While these automated partitioning techniques can provide an improvement over manual partitioning, or no partitioning, they also create either a delay before the

<sup>&</sup>lt;sup>8</sup>Optimistic simulations allow portions of the simulation to get ahead of the rest of the simulation, they may need to resimulate if thier inputs change for results that have already been produced.

simulation can be run, or a delay during simulation startup while the partitioning is determined. A delay before the simulation can be run is created by having to run a tool to determine the partitioning and making the partition changes manually. This can be avoided by implementing these techniques in a distributed simulator. However, the cost of the technique is now paid at the start of every simulation.

#### 2.3.2 Partitioning for System Configuration

Partitioning for hardware/software division is done many times over the course of the design cycle as trade-offs between speed, cost and timing are worked out. In this case, the more simulations that the designers have time to complete, the hope is that the closer the final design will be to the optimal partitioning. As more modules are moved into hardware, the cost of the system goes up, but sometimes a hardware module is the only solution which meets the hard real-time requirements. A balance between cost and meeting the timing requirements is worked out over the course of many simulations.

Over the course of the design, several decisions must be made:

- Which algorithm to use for each of the modules?

- How to implement the chosen algorithms?

- How will the implementation be translated to its final form?

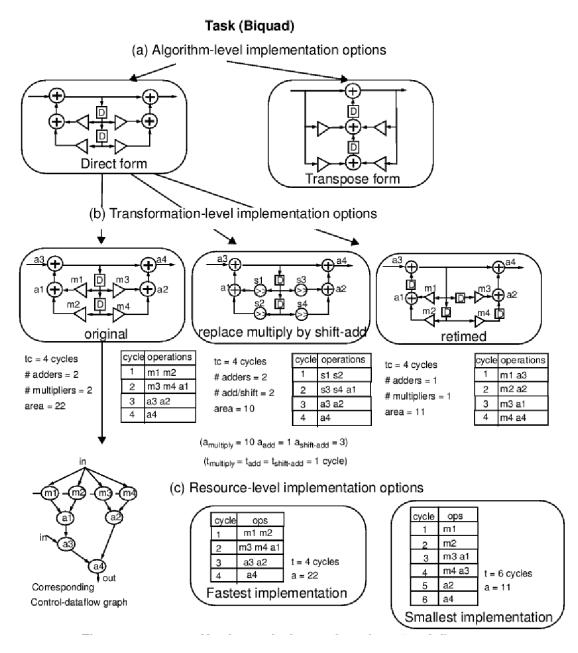

An example of these decisions that happen in a hardware module is deciding if the use of adders and multipliers would be more efficient, in both cost and time, or whether the design should be implemented with adders and shift registers. Figure 2.3.2 shows an example of this decision process. This example shows how a single component decision could need seven simulations to determine its final configuration. It is important to note that the simulations would need to be done in combination with other components and their multiple configuration options.

As systems increase in complexity, so does the number of simulations that are needed to find a optimal partitioning. The design process of partitioning modules

**Figure 2.4:** Partitioning steps of a single element of a Co-design, from Kalavade and Lee's partitioning paper [30]

into hardware and software says that if there are N modules to determine the final configuration, and each module has only to decide between hardware and software, then the number of simulations required to exhaustively search for the optimal configuration is greater than  $2^N$ . This would imply that that there is only one implementation option for each of the hardware and software configurations. In general this is  $M^N$  where M is the fewest number of options for implementing a module. Thus the general form is closer to the number of simulations required for an optimal partitioning. Modern systems have large numbers of modules, which makes finding an optimal partitioning require an impractical number of simulations. It is important to note that two hardware implementations of the same algorithm can have different simulation results, and thus the base of 2 is a lower bound. A priori knowledge and trend analysis will reduce this number significantly but the problem of finding an optimal partitioning is still NP-Hard [30].

Partitioning into hardware and software modules is part of the design process. This thesis does not change the design process, but demonstrates a tool to reduce the time spent in simulations. This allows for two things: more simulations to be run, and/or less design cycle time spent on simulation.

#### 2.4 Parallel Processing

Parallel processing can often complete a a task quicker by attacking it with multiple processors. Both CPU (working time) and I/O (waiting for resources) bound tasks can benefit from parallel processing if it is done right. Breaking up a problem into tasks or sections for parallel processing can be done two basic ways. The task can be broken into sub-tasks and each task handled by a different unit. Alternately, the data can be broken into groups and have each compute node do all of the work for that chunk of data. These techniques are called code and data partitioning [34].

Complex tasks often require many things to be done before the next step can be accomplished. As an example, think of the steps to painting a room:

#### 1. Wash the walls

- 2. Tape/cover areas that need protection

- 3. Paint the trim/edges

- 4. Paint the main areas

- 5. Clean up

This is an example of a set of concurrent tasks that can be completed faster if done in parallel. Two people working on this job will finish it faster. The two people could each work on half of the room, or they could each work on the next step as the other person finishes the previous step in another portion of the room. These are data partitioning (where all work is split between the workers), while the latter would be code partitioning (where the workers specialize in tasks).

There are limits to the advantage of parallel processing [24]. Amdahl's law clearly states the speed up is limited by three factors: 1) the amount of sequential processing, 2) the amount of parallel processing, and 3) the amount of resources. Ahmdal's law can be written as  $SpeedUp = (T_{sequential} + T_{parallel})/(T_{sequential} + (T_{parallel}/M))$ . This tells us that adding resources will only speed up the sections of the simulation that have inherent parallelism. Kiovisto did an excellent analysis of the implications of Amdahl's law with respect to how much speedup can be found through exploiting parallelism for given ratios of sequential to parallel sections of an application [32]. He showed that the speed up factor in a set of parallel tasks would be reduced if there was sequential processing that took more than 1% of total execution time and that the reduction would be proportional to the amount of sequential processing over 1%

There are several major techniques that aid in programming parallel processing applications. Each corresponds to a different method of connecting the compute nodes<sup>9</sup>. The techniques are message passing interface (or MPI), inter-process communications (or IPC) and specialized communications routing software [44]. MPI is used in low latency inter-computer applications like cluster computing, while IPC is typically used in multiprocessor environments, such as SMP, where communication does not leave the computer. The specialized communications software referred to

<sup>&</sup>lt;sup>9</sup>A compute node is a single location for processing the data. A computer may have more than one compute node.

in this thesis is used in grid computing systems that allow an application to share computing resources over large areas and may even support compute nodes being added or dropped.

Inter-process communication (IPC) is a general term that covers any type of communication from one distinct process to another. The term IPC in this thesis refers to communication between processes within a machine. It can be used to synchronize or exchange data across separate processes. It can be used on SMP machines for communication, but specialized communications protocols have also been developed to aid with developing applications for parallel computing [9].

A common communication and synchronization protocol that is used in parallel programming is called MPI, or Message Passing Interface [8]. MPI is a standard that sets out methods of communicating and commands to use to facilitate it. Various vendors supply MPI libraries for developers to use when doing parallel programming. The developer is still required to decide how to design the application, but the communication between the parts is simplified.

Sometimes, custom communications software is needed to address special issues for a parallel computing task. Typically, this happens when the machines involved do not have constant available resources, in that compute nodes may removed from or added to the pool of nodes. Custom software handles routing information to its destination and restarting elements of the task that have failed due to nodes leaving the system [28].

There are three major classes of parallel processing machines: multiprocessors, clusters, and grids. Each of these have increasing communication overhead, but higher flexibility. Multiprocessors offer the lowest communications delay as the compute nodes are tightly coupled. Cluster computers require low communications latency and high bandwidth between several closely related machines. Grid computers often use the Internet for the interconnection between machines. These machines vary in computing power, memory and processor type.

Multiprocessors are computers with more than one CPU or core. There are three types of multiprocessors in use today. SMP machines are common and have shared memory banks. DMPs have distributed memory banks (or separate memory for each processor), and are mostly used in specialized high performance computing. There are also machines called vector processors which use multiple data paths and memory banks, but the processors all do the same task [25]. Vector processors and DMPs will not be covered in the scope of this thesis.

SMP machines can have a large number of processors, but the cost and complexity of the machines rises quickly as more processors are added. Alternatives to SMP machines are found in clustering, grid computing and cloud computing.

Cluster computing uses many machines connected together on a dedicated high-speed network. The machines do not need to be identical. MPI or another communications protocol is required for the processes to communicate across the machines. The advantage of clusters is a higher work/cost ratio at the expense of a higher communications cost.

Grid computing is related to cluster computing, but there are two major differences. The primary difference is that the machines on a grid are not on a dedicated network. Secondly, the machines may or may not be dedicated to the parallel processing tasks. In grid computing, machines can be added or dropped from the network of machines solving the problem at hand. In grid computing, specialized communications and control systems are used to migrate the tasks to available resources. This is done while keeping the actual location of a running process invisible to the program and programs that interact with it [21]. There are some grids that have been deployed that span the globe [41] [17].

MOSIX is an interesting type of grid computing [6]. MOSIX takes the view that the grid should be transparent to the user and designer. From the designer's point of view, a MOSIX cluster can be treated as an SMP machine<sup>10</sup>. IPC can, therefore, be used to communicate between processes. This allows testing of SMP parallel processing programs on inexpensive hardware. MOSIX takes care of all of the load balancing, data transmission and communication between nodes.

<sup>&</sup>lt;sup>10</sup>See http://www-106.ibm.com/developerworks/edu/l-dw-linuxmosix-i.html

## 2.5 Distributed Simulations

As stated previously, distributing simulations over many compute nodes may reduce the simulation run time. In a discrete event simulation, there are often many tasks that need to be done before the clock can be advanced. If any of these can be done at the same time on separate nodes, the simulation time should be lower as long as the communications delay does not negate the speedup. If the time to pass the data between nodes is higher than the time to complete all tasks on a single processor, then the centralized simulation would be faster.

There are three major categories of distributed simulation: code division, and synchronous and asynchronous simulators with work division. Code division can be used for distributed simulations by examining the simulation and breaking the task of simulation into modules and pipelining the execution. Asynchronous and synchronous distributed simulations look for tasks that are being simulated that can be done in parallel. Synchronous simulations require that the simulation time in all modules be the same. Asynchronous simulations do not have this requirement. Time skew in an asynchronous simulation can cause problems, this is discussed later in this section. In general, a synchronous distributed simulation will be slower than the same simulation done as an asynchronous simulation. However, as the synchronous simulation does not have to deal with time skew, it is easier to create and validate [21].

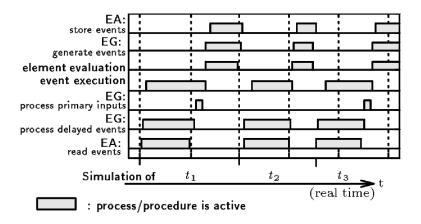

Code division can be used for distributed simulation, but it does not provide the scalability that data division offers. Code division separates areas of the simulation that can be done at the same time. Examples of this are simulations where the data is processed multiple times. Each of the processes can be scheduled onto a separate processor. As shown in Figure 2.5, Luksch [34] shows that when the simulation in his experiment is spread across three or more processors, a theoretical three times speed up could be found. Due to poor communications design and implementation in his experiment, no speed up was found. The time spent synchronizing data overwhelmed the speed up from the parallel processing.

Figure 2.5: Code partitioning example [34]

Synchronous simulations do not process data until the unified clock reaches the time where it would be processed. This means that if one module takes longer to process its data than the others, it becomes a bottleneck. A good partitioning can reduce this, but not entirely. Synchronous simulations are not as fast as asynchronous simulations, but they are easier to write and to modify without introducing errors into the simulation as there is no need for roll-back or anti-messages.

The main difference between synchronous and asynchronous distributed simulations is the unified clock. If one module of an asynchronous simulator can go faster, it will continue to simulate until input is not available. When it needs input, it has to wait. This leads to portions of the simulation being ahead, and possibly working with data that will change before the answer is needed.

Asynchronous simulations can have modules that provide erroneous data. The possibility of a module being ahead so far that it is working with the wrong data has been addressed in two different ways. The solutions are termed optimistic and conservative. Optimistic simulators assume that the data that a module currently has, will not change before the output is required [18, 52]. Conservative simulators only produce output when a module's data cannot change before its output is needed [31].

In an optimistic simulator, when the input for a module changes after the output is produced, the simulator must send out *anti-messages*, or rollback to a previous

state. This ensures that any modules that used possibly wrong data can use the new data and reissue any messages. While the anti-messages and rollbacks take time, if there are only a few rollbacks, then the optimistic simulations are faster than the conservative simulation.

Conservative simulators do not have to deal with roll backs or anti-messages [3]. Conservative simulators only prepare output if it can be guaranteed that the input will not change before the output is needed. This causes conservative simulators to run slower than optimistic simulators, but faster than synchronous simulators.

There is a hierarchy of possible speed up in distributed simulations. As mentioned earlier, this ordering is as follows, from slowest to fastest:

- Monolithic simulation, or non-distributed simulation.

- Synchronous distributed simulation,

- Asynchronous conservative distributed simulation, and

- Asynchronous optimistic distributed simulation.

The possible speed up is also inversely proportional to the complexity of creating a simulator with that technique. The monolithic simulators are the easiest to create, but they are also the slowest.

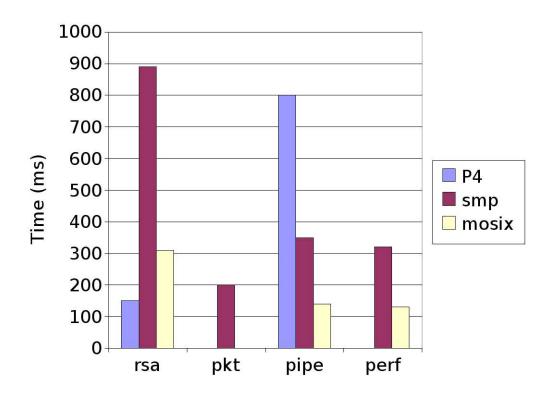

Some projects that have used synchronous and asynchronous optimistic simulation in system design<sup>11</sup> are found in table 2.5. These projects show that the simulations can be distributed in each of these ways. Both of the asynchronous simulator projects predate research into Co-Design. While SystemC MPI and Distributed SystemC are proof of concept projects. Parallel SystemC is from a 2009 paper [19] and is a parallel work to this thesis.

Time Warp is an optimistic distributed simulation framework. The framework uses plug-ins to enable different simulations. It has been extended in the SAVANT project to simulated VHDL designs. The sub-project TyVis produced the plug-ins and translation engine for VHDL into a form that could be simulated by the TyVis

<sup>&</sup>lt;sup>11</sup>TyVis predates Co-design, thus the generic term of system design has been used

Table 2.1: Reviewed Distributed Simulators

| Simulator           | Type                      |

|---------------------|---------------------------|

| TyVis               | Asynchronous/Optimistic   |

| Cpoker              | Asynchronous/Conservative |

| SystemC MPI         | Synchronous               |

| Distributed SystemC | Synchronous               |

| Parallel SystemC    | Synchronous               |

kernel. The translation engine created extended C++ code that could be simulated in Time Warp or any other optimistic simulation framework [52].

Cpoker [3] was a simulator designed to explore the overhead and communications cost as well as the run time advantages of an asynchronous conservative hardware simulator. They found that the run time could be reduced, but not linearly as CPU resource were added. However, their research focused on the costs of maintaining the state of the simulator and the communications cost.

The SystemC MPI project demonstrated that MPI calls could be included in SystemC Modules<sup>12</sup>. The MPI calls can than be used to communicate between SystemC simulators or other systems. These calls can be added to any module, but they have to be explicitly added and they do not follow the SystemC model.

Distributed SystemC offers explicit connections between simulators [49]. It allows developers to explicitly create multiple separate simulators, and control what is in each of them. This forces the simulation partitioning problem onto the developer. The developer needs to choose which modules belong to each simulator. The interaction between modules is modeled as SystemC communications channels. Signals are sent over TCP/IP. This makes the connection semantics integrate naturally into the design, but it also means that the systems that the simulators will be run on is decided at compile time due to the configuration of the communications channels.

In contrast, during the same period as this thesis, Ezudheen *et al.* from the National Institute of Technology Calicut developed a parallel SystemC simulator

<sup>&</sup>lt;sup>12</sup>see http://www5a.biglobe.ne.jp/ hamabe/index.html

[19]. This simulator creates groups of modules and associates them with a CPU at run time based on which partitioning algorithm was in use for each experiment. They examined manual partitioning, two work sharing algorithms, and a work stealing algorithm. The work sharing algorithms collected the activated modules into chunks to be allocated explicitly to processors. This was done either as a division of the number of modules by the resources, or by measuring the load of each CPU and allocating more modules to the less loaded resources. In contrast the work stealing algorithm allows an underutilized CPU to steal modules that are waiting on another CPU.

These four partitioning algorithms were studied under three conditions: 1) as the number of CPUs changed, 2) as the number of modules changed, and 3) as the run time for a module changed. All of these were measured against the run time of the simulation and compared with the unmodified SystemC simulator. A comparison of their simulator to the simulator proposed in this thesis can be found in section 4.3.

Some simulations cannot be helped by distribution. Those that can have their simulation time reduced, exhibit either parallelism in the processing, or data, and/or require multiple independent processing passes of the data. Hardware simulations exhibit all of the requirements. The method of distributing the simulation can also affect the speed up. A synchronous simulator is the next step to speeding up Co-Simulation. The complexity of creating the synchronous simulator is well within reach, while still offering some speed up.

## 2.6 Summary

This chapter has covered background information that is necessary to understand the motivations and experimental system design of this thesis. The design path and its changes due to the development of Co-Design as an industrial design technique were reviewed. Additionally the general types of simulations were reviewed, as was the differences between simulation and Co-Simulation. The general theory of the partitioning problem was presented and related to this work. Parallel processing systems,

their advantages and disadvantages were presented and briefly discussed. Finally a review of the distributed simulator techniques and projects that relate to this thesis was reviewed. Now that the problems in the design path have been explored, a solution to the run time issue caused by the need to test hardware/software partitions can be explored. This proposed solution used the simulator built into SystemC as a base for a synchronized distributed simulator.

## CHAPTER 3

# PROTOTYPE AND EXPERIMENT DESIGN

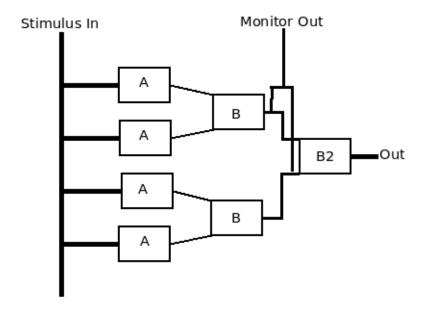

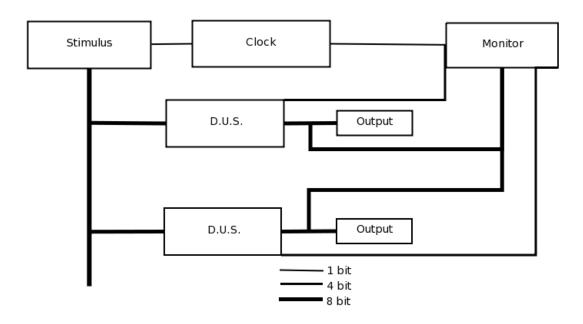

This chapter describes the design of PDQScS (Parallel Distributed Quick SystemC Simulator), the evaluation techniques and the performance experiment design. PDQScS is a prototype synchronous distributed simulator derived from the simulator included with SystemC. PDQScS is compared to the SystemC simulator to verify correctness of the computational capabilities of the new system as well as run time performance characteristics.

PDQScS is a modification of the existing multi-threaded co-simulation tool/language SystemC. As a language, SystemC is an HDL based on C++, but it also has a reference simulator for the language. PDQScS retains the simulator portion of SystemC, but modifies it so that it runs as a multi-process application. These processes are then distributed to separate CPU resources as available.

The design goals of the prototype for this thesis are the following:

- 1. a system that does not increase work for the designer of a Co-Design system,

- 2. scalable in both Co-Design system design size and number of CPU resources, and

- 3. allow existing system designs to be simulated without modification.