# AN ALGORITHM FOR PROTECTING POWER TRANSFORMERS

#### A Thesis

Submitted to the College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in the

Department of Electrical Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

by

# HARJEET SINGH GILL

July 1997

© Copyright Harjeet Singh Gill, 1997. All rights reserved.

### **PERMISSION TO USE**

In presenting this thesis in partial fulfillment of the requirements for a Master's degree from the University of Saskatchewan, the author has agreed that the Libraries of this University may make it freely available for inspection. The author further agrees that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professors who supervised the thesis work or, in their absence, by the Head of the Department or the Dean of the College in which the thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without the author's written permission. It is also understood that due recognition shall be given to the author and to the University of Saskatchewan in any scholarly use which may be made of any material in this thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical Engineering, University of Saskatchewan, Saskatoon, Saskatchewan, Canada S7N 5A9

#### UNIVERSITY OF SASKATCHEWAN

#### **Electrical Engineering Abstract 97A459**

#### AN ALGORITHM FOR PROTECTING POWER TRANSFORMERS

Student: Harjeet Singh Gill Supervisors: Dr. T.S. Sidhu

Dr. M.S. Sachdev

M.Sc. Thesis Submitted to the College of Graduate Studies and Research July 1997

#### ABSTRACT

Electric power utilities have traditionally used electromechanical and solid-state relays for protecting power transformers. Differential protection is the conventionally used scheme for the purpose. With the advent of digital technology, researchers and designers have made remarkable progress in the development of microprocessor-based relays. These relays use algorithms similar in principle to their electromechanical counterparts. Several algorithms, based on differential principle and suitable for implementation on microprocessors, have been proposed in the past. However, these algorithms are adversely affected by current transformer saturation and ratio-mismatch conditions.

This thesis describes a technique that provides a new approach for protecting power transformers. The technique uses positive- and negative-sequence models of the power system in a fault-detection algorithm. While phase voltages and currents at the transformer terminals are used to detect fault, no information concerning parameters of the transformer and power system is required.

The performance of the proposed technique was studied for a variety of operating conditions using data generated by simulations on the electromagnetic transient program, EMTDC. Performance of the developed technique was also evaluated for saturation and ratio-mismatch conditions of the current transformers. A theoretical basis explaining the stable performance during such conditions is also established.

The proposed algorithm can be adapted to protect the transformer which is connected to a source but is not supplying any load. Occasionally, switch-on faults may occur when a transformer is energized. A criterion to detect such faults is proposed and test results verifying the same are also included in the thesis.

#### **ACKNOWLEDGMENTS**

The author would like to express his gratitude and appreciation to Dr. T.S. Sidhu and Dr. M.S. Sachdev for their guidance and assistance throughout the course of this work. The advice and encouragement provided by them is thankfully acknowledged.

The author is thankful to Mr. Ratan Das and Mr. Pramod Dhakal for providing advice and help in many ways during the work. Thanks are due to Mr. D. Karaloff, Mr. I.J. MacPhedran, Mr. K.D. Jeffrey and Mr. J.E. Moore for their assistance. The support of Mr. Trinh Minh Thu is also thankfully acknowledged.

Special thanks are extended to author's parents, Squadron Leader Ranjit Singh Gill (Retd.) and Smt. Joginder Kaur, and to the brother, Mr. Paramjeet Singh Gill and all other family members for their constant encouragement and support in making this work a reality. But for their assistance, this work would not have been possible.

Financial support provided by the National Sciences and Engineering Research Council (NSERC) of Canada, and leave provided by the Government of India are gratefully acknowledged.

# **Dedicated To Grandparents**

Smt. Harnam Kaur

Smt. Surjit Kaur

S. Gajjan Singh Gill

S. Kartar Singh Cheema

# TABLE OF CONTENTS

|    | PERM           | MISSION  | N TO USE                                          | i          |

|----|----------------|----------|---------------------------------------------------|------------|

|    | ABS'           | TRACT    |                                                   | ii         |

|    | ACK            | NOWLE    | EDGMENTS                                          | i <b>v</b> |

|    | DED            | ICATIO   | N                                                 | v          |

|    | TAB            | LE OF C  | CONTENTS                                          | vi         |

|    | LIST OF TABLES |          |                                                   |            |

|    | LIST           | OF FIG   | URES                                              | <b>x</b> i |

|    | LIST           | OF SYN   | MBOLS                                             | xx         |

| 1. | INT            | RODUC    | TION                                              | 1          |

|    | 1.1.           | Backgr   | ound                                              | 1          |

|    | 1.2.           | Protecti | ion of power systems                              | 1          |

|    | 1.3.           | A digita | al relay                                          | 5          |

|    | 1.4.           | Objecti  | ve of the research                                | 8          |

|    | 1.5.           | Outline  | of the thesis                                     | 8          |

|    | 1.6.           | Summa    | nry                                               | 10         |

| 2. | DIF            | TERENT   | TIAL PROTECTION                                   | 11         |

|    | 2.1.           | The dif  | ferential principle                               | 11         |

|    | 2.2.           | Probler  | ns with differential protection                   | 13         |

|    |                | 2.2.1.   | Ratio-mismatch                                    | 13         |

|    |                | 2.2.2.   | Difference in current transformer characteristics | 13         |

|    |                |          | and burdens                                       |            |

|    |                | 2.2.3.   | Current transformer saturation                    | 14         |

|    |                | 2.2.4.   | Magnetizing inrush                                | 16         |

|    | 2.3.           | Percent  | tage-bias and harmonic-restraint                  | 18         |

|    | 24             | Digital  | algorithms for transformer protection             | 20         |

|    |       | 2.4.1.   | Waveshap     | e identification technique      | 20   |

|----|-------|----------|--------------|---------------------------------|------|

|    |       | 2.4.2.   | Harmonic     | -restraint algorithms           | 21   |

|    |       |          | 2.4.2.1.     | Least error squares technique   | 21   |

|    |       |          | 2.4.2.2.     | Discrete fourier algorithm      | 25   |

|    |       |          | 2.4.2.3.     | Kalman filter                   | 26   |

|    |       | 2.4.3.   | Model-bas    | sed algorithms                  | 27   |

|    | 2.5.  | Discussi | on of the al | lgorithms                       | 29   |

|    | 2.6.  | Algorith | ms dealing   | with CT saturation              | 30   |

|    | 2.7.  | Summar   | y            |                                 | 32   |

| 3. | THE   | PROPO    | SED TEC      | HNIQUE                          | 33   |

|    | 3.1.  | Introduc | tion         | •                               | 33   |

|    | 3.2.  | Develop  | ment of th   | e technique                     | 34   |

|    |       | 3.2.1.   | External     | fault                           | 34   |

|    |       | 3.2.2.   | Internal f   | ault                            | 41   |

|    | 3.3.  | Fault-de | tection for  | unloaded transformers           | 43   |

|    |       | 3.3.1.   | External     | fault                           | 45   |

|    |       | 3.3.2.   | Internal f   | ault                            | 47   |

|    | 3.4.  | Comput   | ation of in  | cremental voltages and currents | 50   |

|    | 3.5.  | The Alg  | orithm       |                                 | 53   |

|    |       | 3.5.1.   | Design of    | f the LES filter                | 58   |

|    | 3.6.  | Switch   | on transfo   | rmers                           | 60   |

|    |       | 3.6.1.   | External     | fault                           | 61   |

|    |       | 3.6.2.   | Internal f   | ault                            | 63   |

|    | 3.7.  | Fault-de | etection     |                                 | 63   |

|    | 3.8.  | Linking  | the propos   | sed algorithms                  | . 60 |

|    | 3.9.  | Current  | transforme   | er saturation                   | 68   |

|    | 3.10. | CT ratio | o-mismatcl   | 1                               | 73   |

|    | 3.11. | Feature  | s of the pro | posed technique                 | 73   |

|    | 3 12  | Summa    | rv.          |                                 | 74   |

| , | SIM  | ULATIO                                | N STUDIES                                          | 75  |  |

|---|------|---------------------------------------|----------------------------------------------------|-----|--|

|   | 4.1. | Introduct                             | Introduction                                       |     |  |

|   | 4.2. | System modeling and signal processing |                                                    |     |  |

|   | 4.3. | Test stud                             | lies                                               | 77  |  |

|   |      | 4.3.1.                                | Internal faults                                    | 78  |  |

|   |      |                                       | 4.3.1.1. Single phase-to-ground fault: Phase A     | 78  |  |

|   |      |                                       | 4.3.1.2. Two-phase fault: Phase B-Phase C          | 78  |  |

|   |      |                                       | 4.3.1.3. Three-phase fault                         | 86  |  |

|   |      | 4.3.2.                                | External faults                                    | 88  |  |

|   |      |                                       | 4.3.2.1. Single phase-to-ground fault: Phase C     | 88  |  |

|   |      |                                       | 4.3.2.2. Two-phase fault: Phase A-Phase B          | 93  |  |

|   |      |                                       | 4.3.2.3. Three-phase fault                         | 95  |  |

|   | 4.4. | Effect of                             | fratio-mismatch                                    | 97  |  |

|   |      | 4.4.1.                                | Single phase-to-ground fault: Phase A              | 99  |  |

|   |      | 4.4.2.                                | Two-phase fault: Phase A-Phase B                   | 102 |  |

|   | 4.5. | Effect of                             | f CT saturation                                    | 102 |  |

|   |      | 4.5.1.                                | Three-phase fault                                  | 102 |  |

|   |      | 4.5.2.                                | Single phase-to-ground fault : Phase B             | 105 |  |

|   |      | 4.5.3.                                | Two-phase fault: Phase A-Phase B                   | 109 |  |

|   |      | 4.5.4.                                | Two-phase-to-ground fault : Phase A-Phase B-ground | 110 |  |

|   | 4.6. | Faults in                             | unloaded transformers                              | 113 |  |

|   |      | 4.6.1.                                | Three-phase (internal) fault                       | 113 |  |

|   |      | 4.6.2.                                | Two-phase fault: Phase B-Phase C                   | 115 |  |

|   | 4.7. | High-im                               | pedance faults                                     | 119 |  |

|   |      | 4.7.1.                                | Single phase-to-ground (external) fault : Phase A  | 119 |  |

|   |      | 4.7.2.                                | Single phase-to-ground (internal) fault : Phase B  | 125 |  |

|   | 4.8. | Switch-c                              | on faults                                          | 130 |  |

|   |      | 4.8.1.                                | External faults                                    | 130 |  |

|   |      |                                       | 4.8.1.1. Two-phase fault: Phase A-Phase B          | 130 |  |

|   |      |                                       | 4812 Single phase-to-ground fault : Phase A        | 132 |  |

|    | 4.8.2.       | Internal fau  | ults                                  | 135 |

|----|--------------|---------------|---------------------------------------|-----|

|    |              | 4.8.2.1. S    | Single phase-to-ground fault: Phase B | 135 |

|    |              | 4.8.2.2.      | Three-phase-to-ground fault           | 135 |

|    |              | 4.8.2.3.      | Γwo-phase fault: Phase B-Phase C      | 138 |

|    | 4.9. Magneti | zing inrush   |                                       | 138 |

|    | 4.10. Summa  | у             | •                                     | 138 |

| 5. | SUMMARY.     | AND CONC      | CLUSIONS                              | 142 |

|    | 5.1. Suggest | ions for futu | re work                               | 145 |

|    | REFERENC     | ES            |                                       | 146 |

|    | Appendix A.  | SYMMET        | RICAL COMPONENTS AND SEQUENCE-        | 150 |

|    |              | NETWOR        | RKS                                   |     |

|    | Appendix B.  | EMTDC A       | AND CT MODEL                          | 153 |

|    | Appendix C.  | DATA          |                                       | 155 |

|    | Appendix D.  | ANTI-AL       | IASING FILTER DESIGN                  | 157 |

|    | Appendix E.  | ADDITIO       | NAL TEST RESULTS                      | 159 |

# List of Tables

| Table 3.1. | The filter coefficients for a 25 point LES filter based on a sampling rate of 1440 Hz. | 59       |

|------------|----------------------------------------------------------------------------------------|----------|

| Table E.1  | Summary of additional test results                                                     | 184, 185 |

# List of Figures

| Figure 1.1. | Typical relay protection zones in a power system.                                                                                                                   | 2    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2. | (a) Single-line diagram of a protective relay arrangement (b) DC trip circuit.                                                                                      | 4    |

| Figure 1.3. | Functional block diagram of a digital relay.                                                                                                                        | 7    |

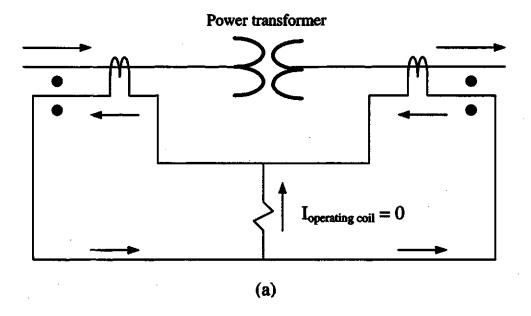

| Figure 2.1. | Basic differential scheme for (a) no-fault and (b) internal fault conditions of a power transformer.                                                                | 12   |

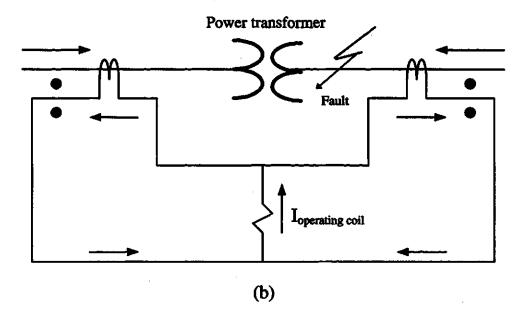

| Figure 2.2. | Current waveforms of ct's (a) primary current, and secondary currents for (b) mild and (c) severe ct saturation states.                                             | 15   |

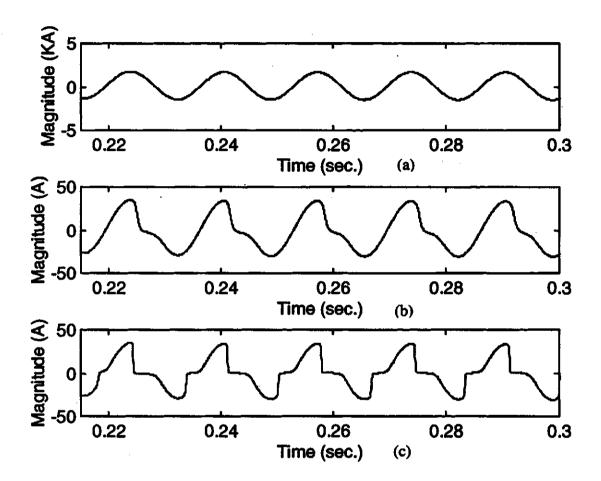

| Figure 2.3. | Magnetizing curve for a transformer core.                                                                                                                           | 17   |

| Figure 2.4. | Magnetizing inrush phenomenon in a power transformer.                                                                                                               | 17   |

| Figure 2.5. | Percentage-bias differential relay (a) circuit and (b) characteristics.                                                                                             | 19   |

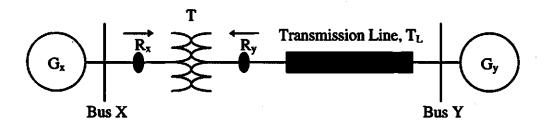

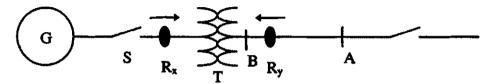

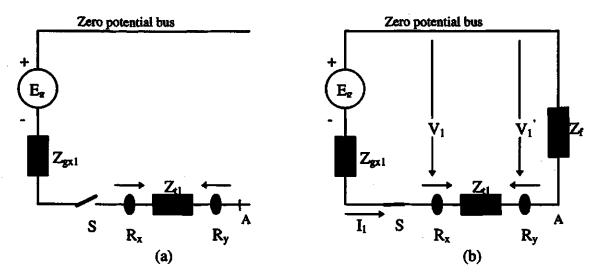

| Figure 3.1. | Circuit used for developing the proposed technique for protecting power transformers.                                                                               | 34   |

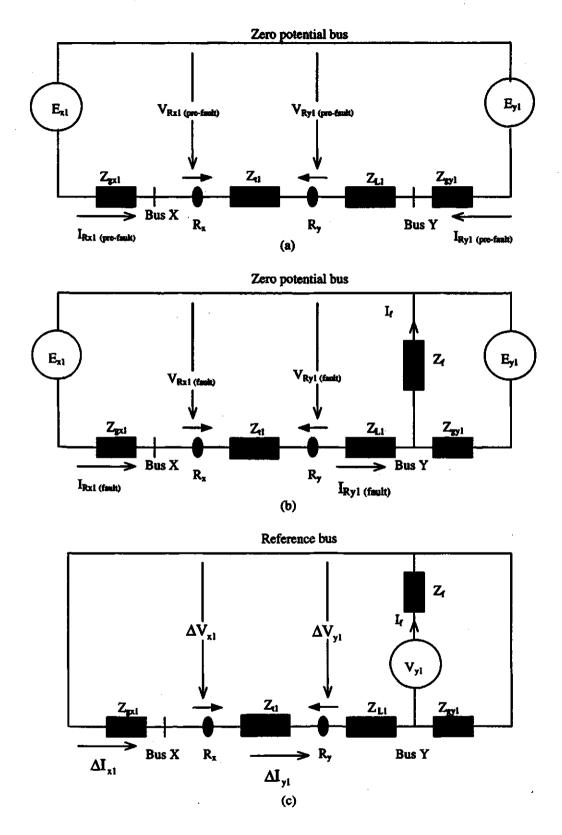

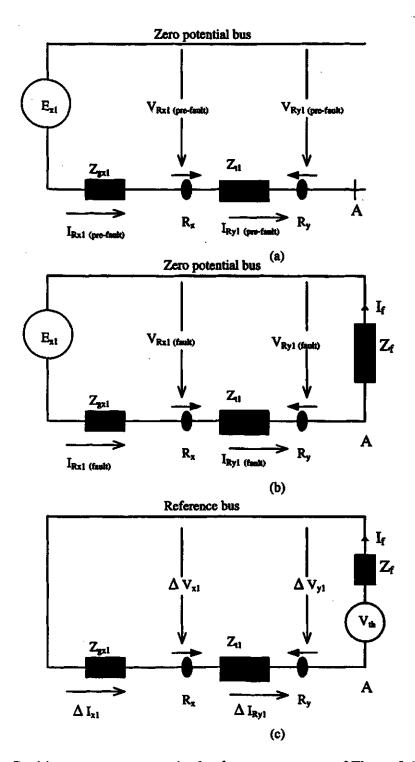

| Figure 3.2. | Positive-sequence networks for the power system of Figure 3.1 for an external fault (a) Pre-fault circuit, (b) fault circuit and (c) Thevenin's equivalent circuit. | 35   |

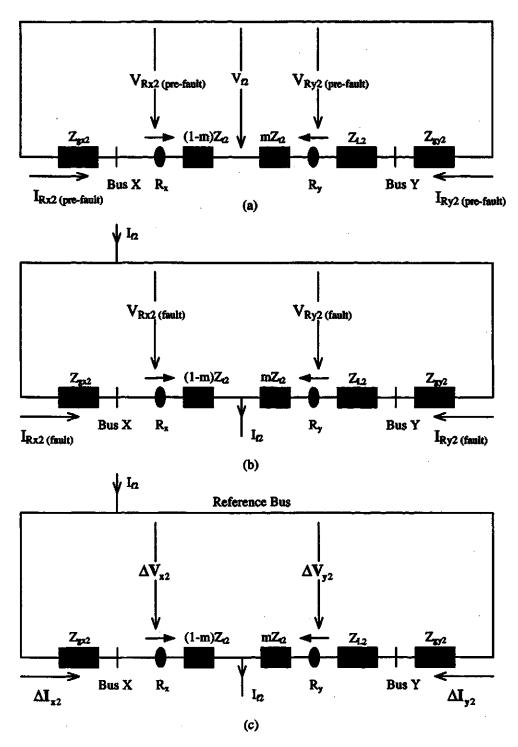

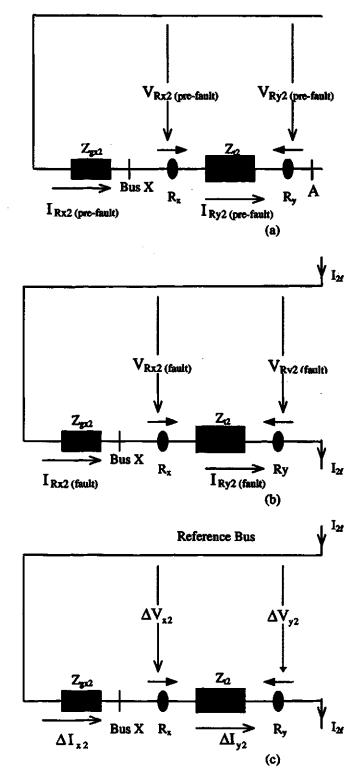

| Figure 3.3. | Negative-sequence networks for the power system of Figure 3.1 for an external fault (a) Pre-fault circuit, (b) fault circuit and (c) Thevenin's equivalent circuit. | 39   |

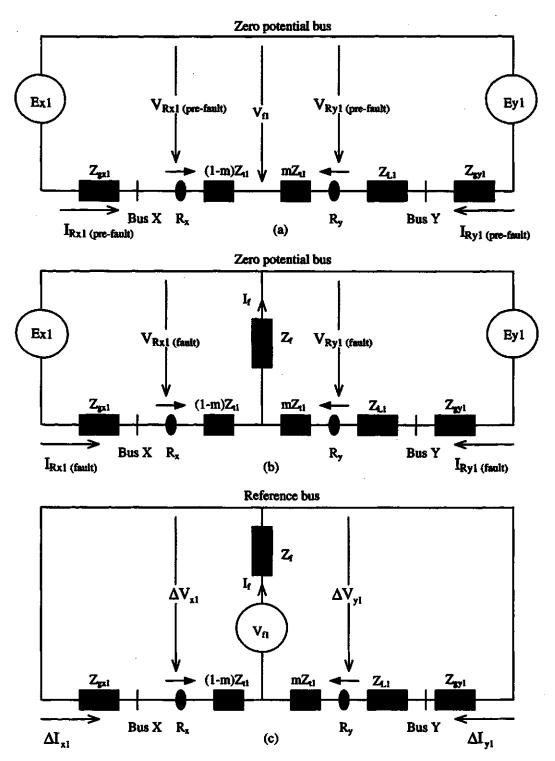

| Figure 3.4. | Positive-sequence networks for the power system of Figure 3.1 (internal fault). (a) Pre-fault, (b) fault and (c) Thevenin's equivalent circuit.                     | 42   |

| Figure 3.5. | Negative-sequence networks for the power system of Figure 3.1 (internal fault). (a) Pre-fault, (b) fault and (c) Thevenin's equivalent circuit.                     | . 44 |

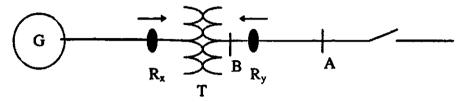

| Figure 3.6. | Unloaded power transformer.                                                                                                                                         | 45   |

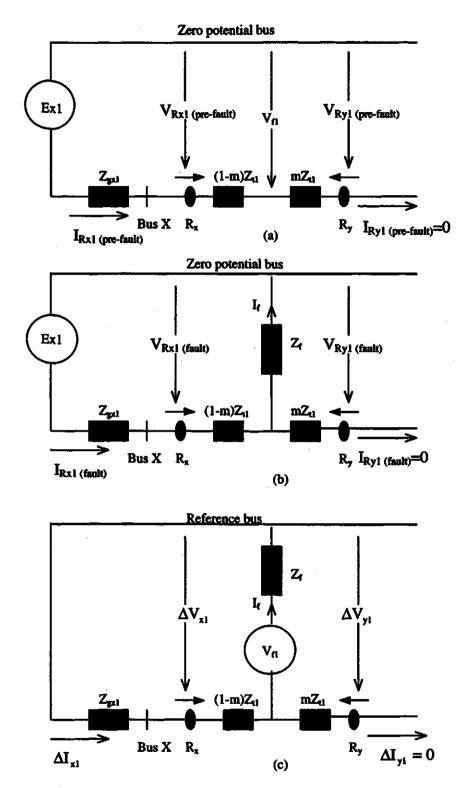

| Figure 3.7. | Positive-sequence networks for the power system of Figure 3.11 for an external fault at A). (a) Pre-fault, (b) fault and (c) Thevenin's equivalent circuit.         | 46   |

| Figure 3.8.            | Negative-sequence networks for the power system of Figure 3.1 for an external fault. at A (a) Pre-fault, (b) fault and (c) Thevenin's equivalent circuit. | 48 |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

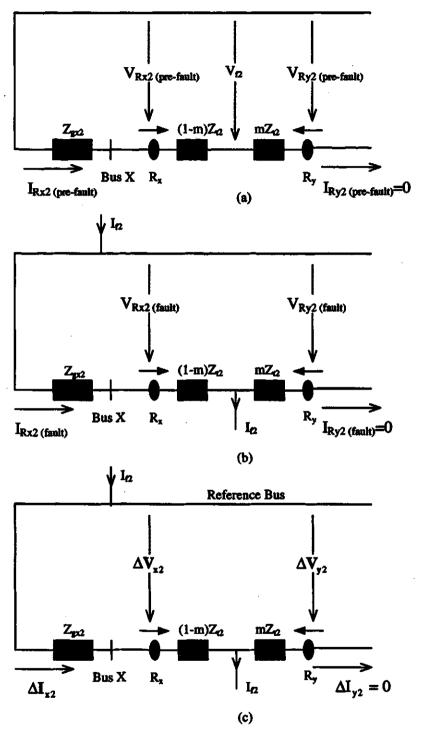

| Figure 3.9.            | Positive-sequence networks for the power system of Figure 3.1 (internal fault). (a) Pre-fault, (b) fault and (c) Thevenin's equivalent circuit.           | 49 |

| Figure 3.10.           | Negative-sequence networks for the power system of Figure 3.1 (internal fault). (a) Pre-fault, (b) fault and (c) Thevenin's equivalent circuit.           | 51 |

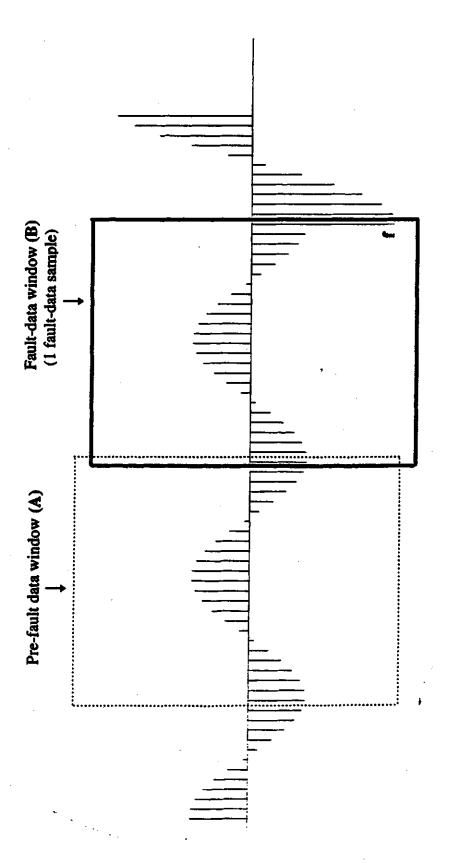

| Figure 3.11.           | Location of data window at different sampling instants.                                                                                                   | 52 |

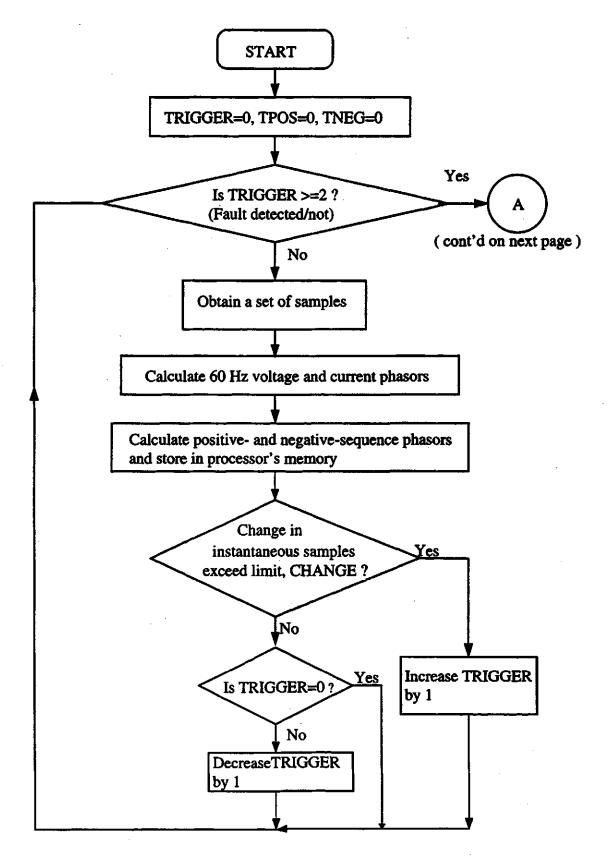

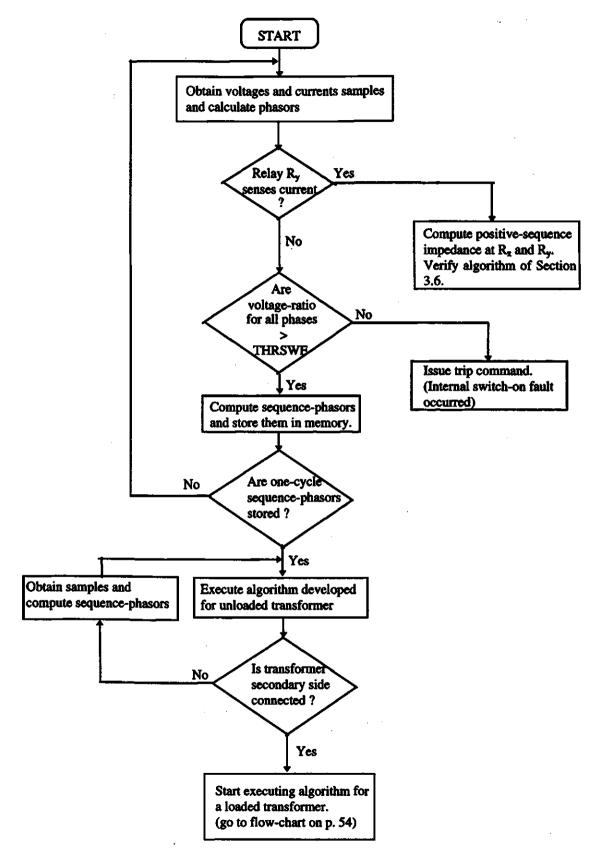

| Figure 3.12.           | Flow chart of proposed algorithm (pre-fault section).                                                                                                     | 54 |

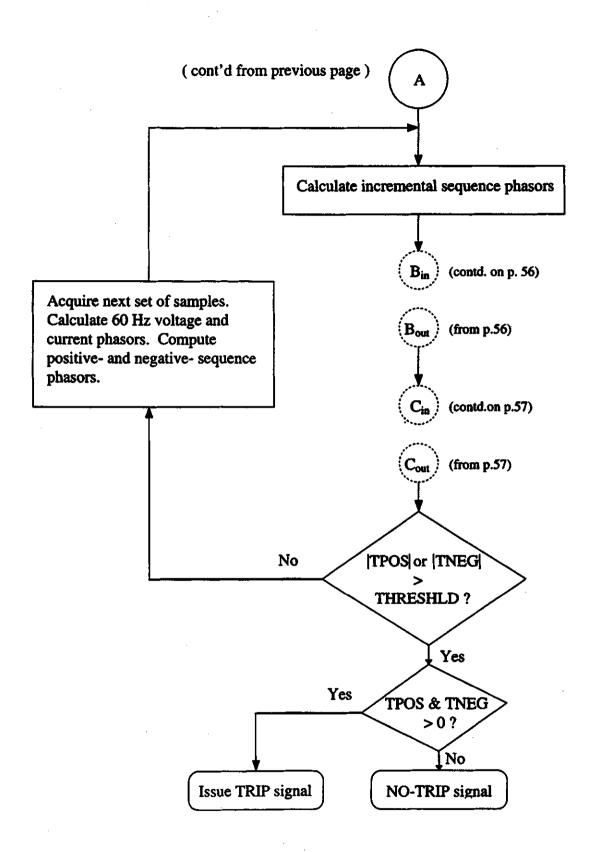

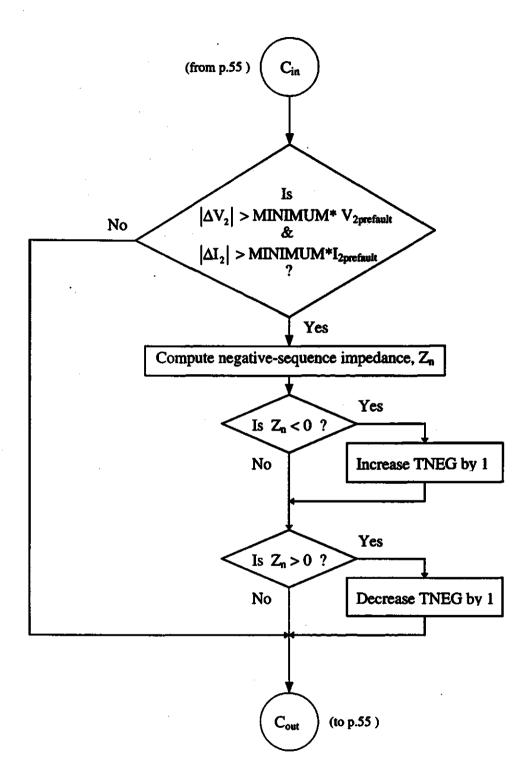

| Figure 3.12. (contd.). | Flow chart of proposed algorithm (fault section).                                                                                                         | 55 |

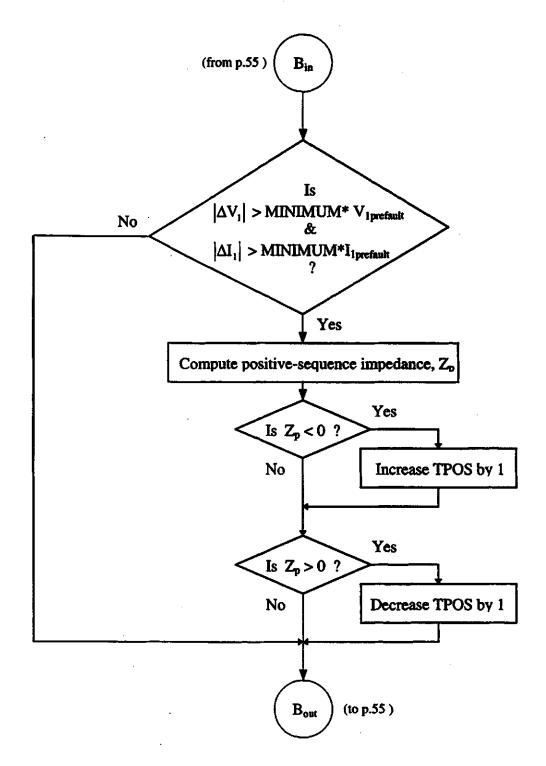

| Figure 3.12. (contd.). | Segment to check threshold for positive-sequence voltage and current.                                                                                     | 56 |

| Figure 3.12. (contd.). | Segment to check threshold for negative-sequence voltage and current.                                                                                     | 57 |

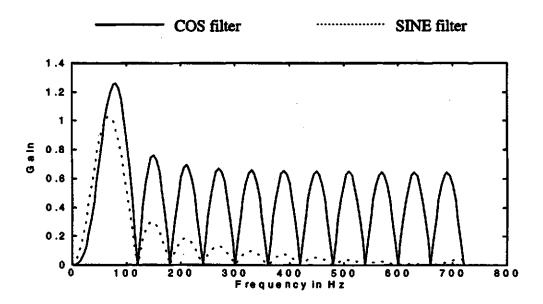

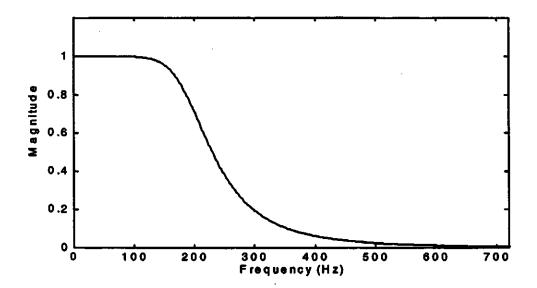

| Figure 3.13.           | Frequency response of least error squares filter having a data window of 25 samples.                                                                      | 60 |

| Figure 3.14.           | Switching-on of a power transformer.                                                                                                                      | 61 |

| Figure 3.15.           | (a) Pre-fault and (b) fault positive-sequence networks for an external fault at A                                                                         | 62 |

| Figure 3.16.           | (a) Pre-fault and (b) fault negative-sequence networks for an external fault at A                                                                         | 63 |

| Figure 3.17.           | Fault-detection characteristics for a loaded transformer (a) Internal fault (b) External fault.                                                           | 64 |

| Figure 3.18.           | Fault-detection characteristics for an unloaded transformer (a) Internal fault (b) External fault.                                                        | 65 |

| Figure 3.19.           | Switch-on fault-detection characteristics (a) Internal fault (b) External fault.                                                                          | 66 |

| Figure 3.20.           | Flow-chart for combining the developed algorithms.                                                                                                        | 67 |

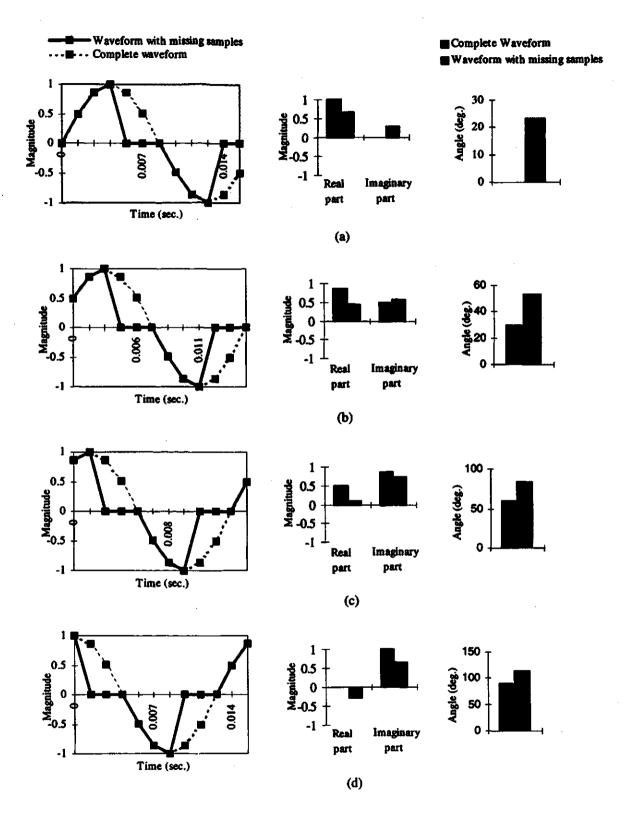

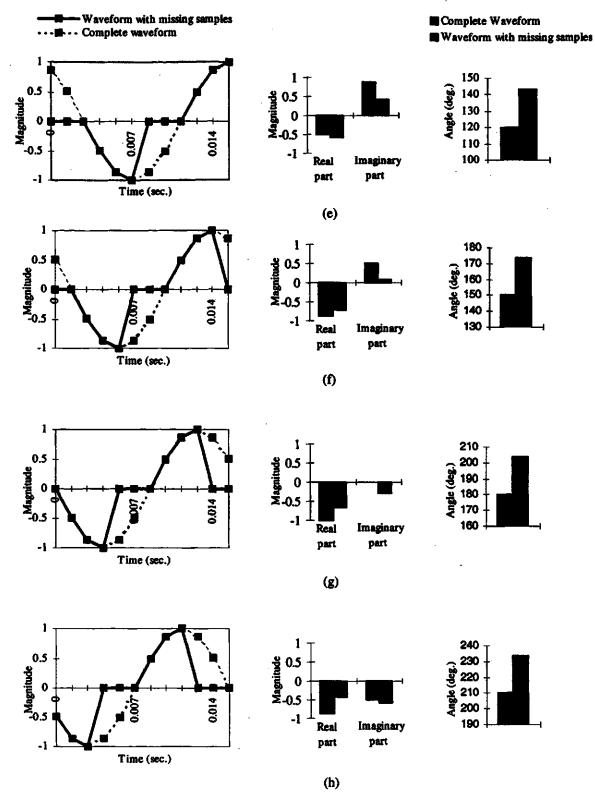

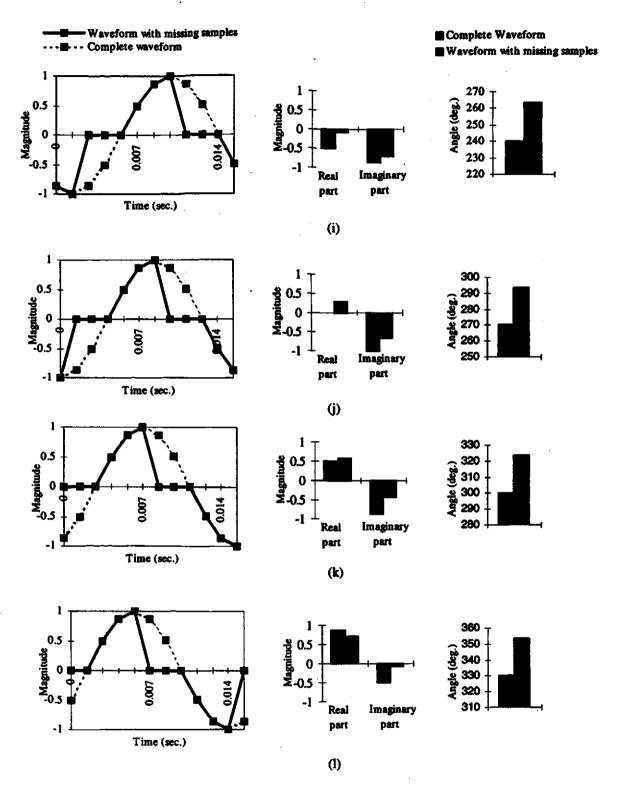

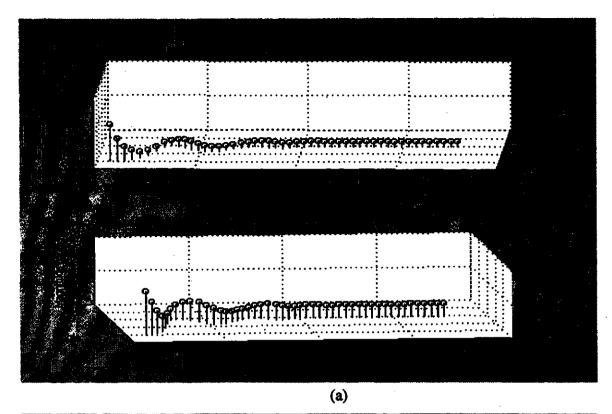

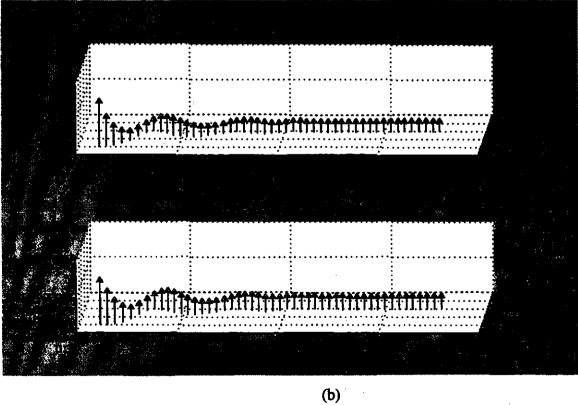

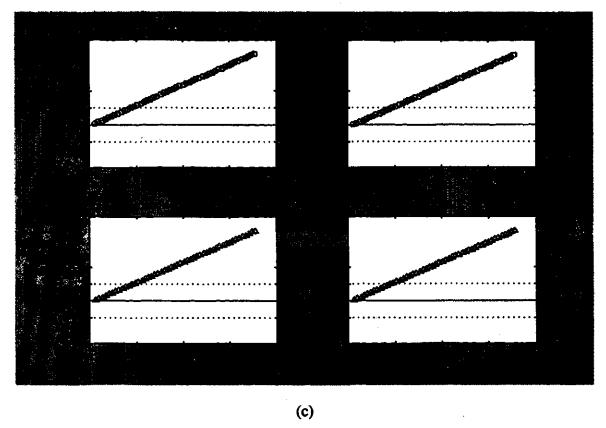

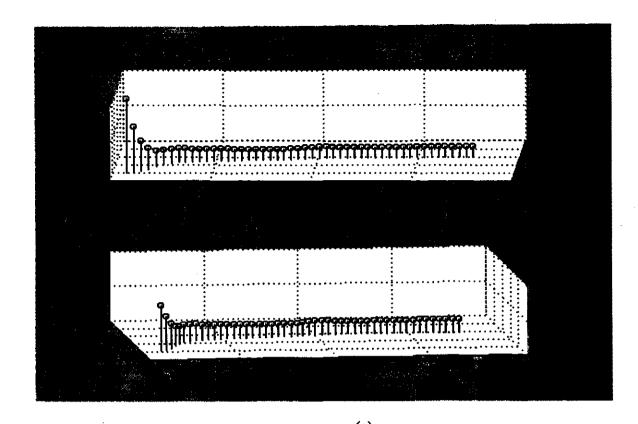

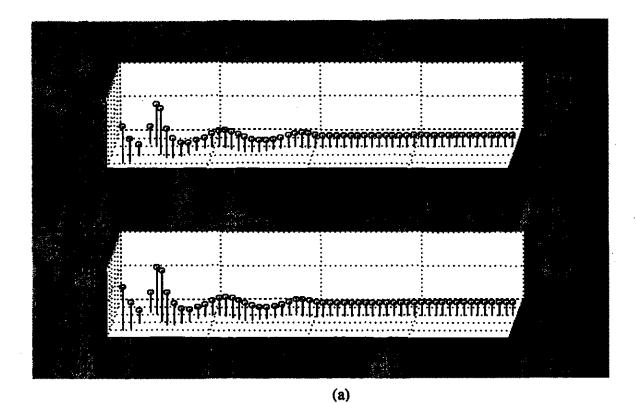

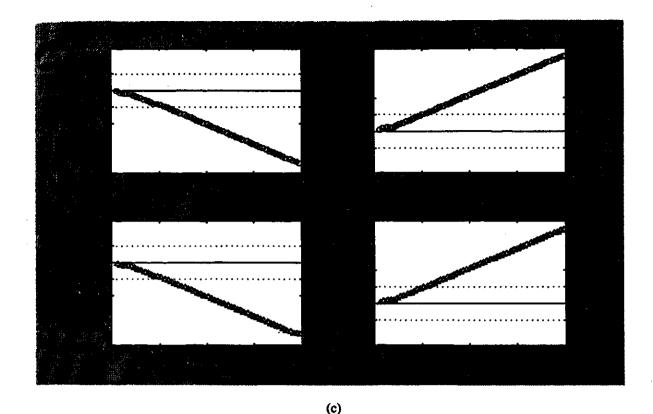

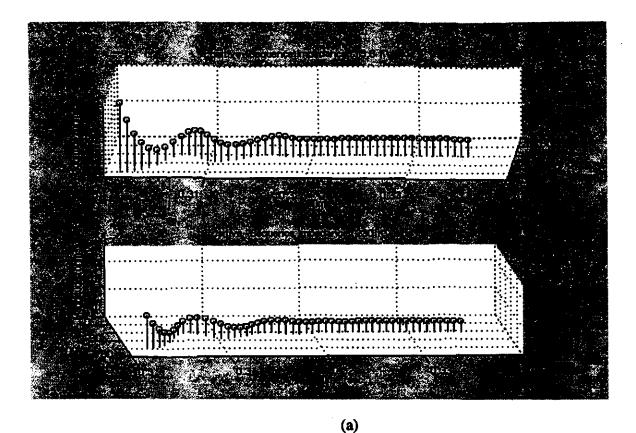

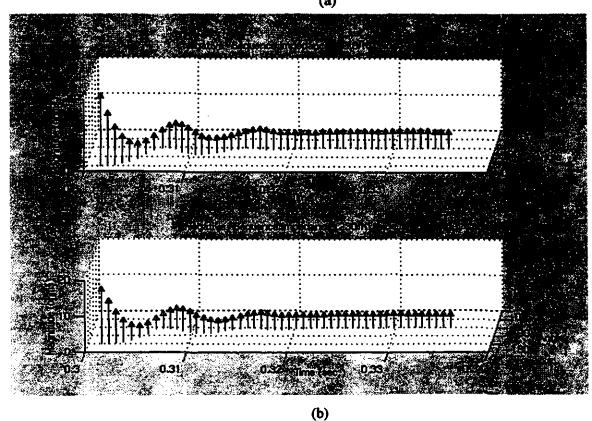

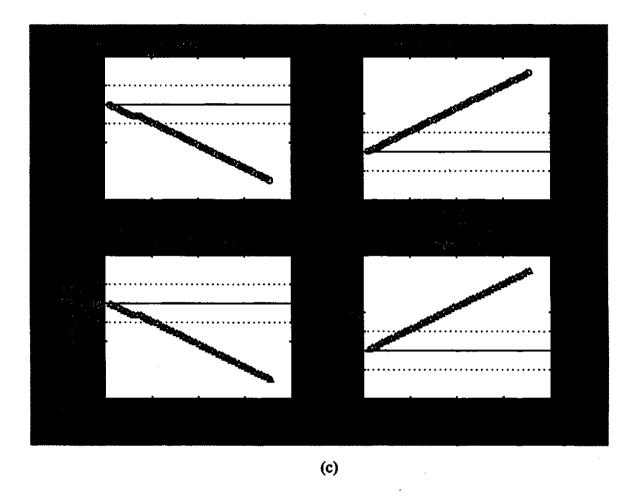

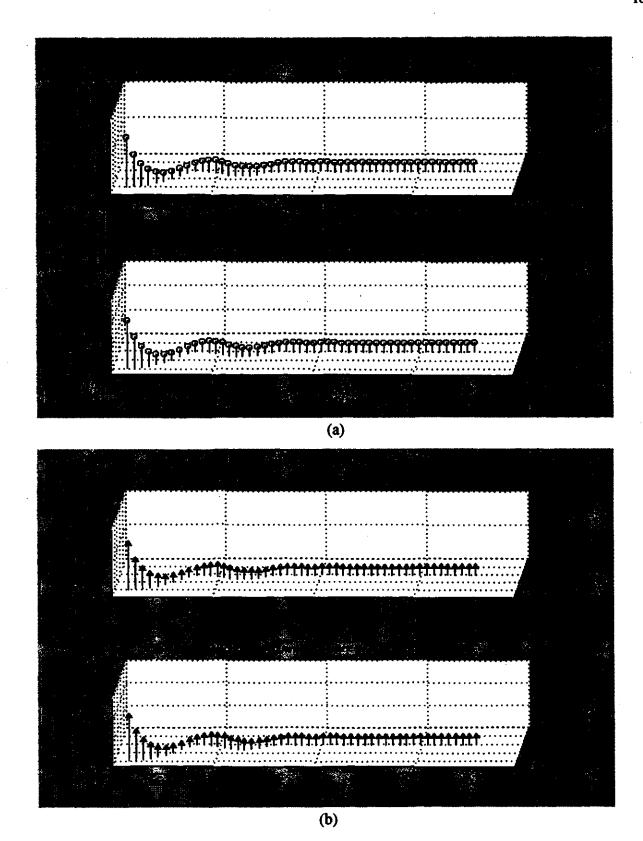

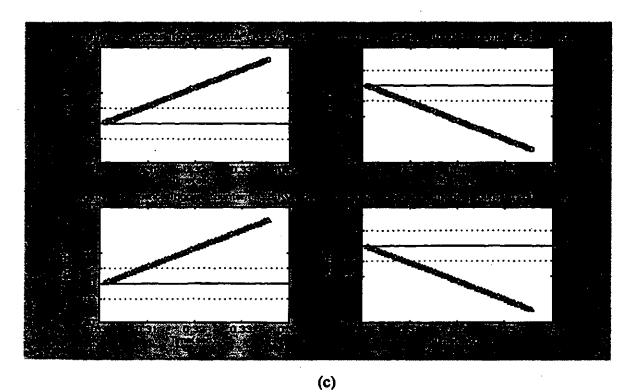

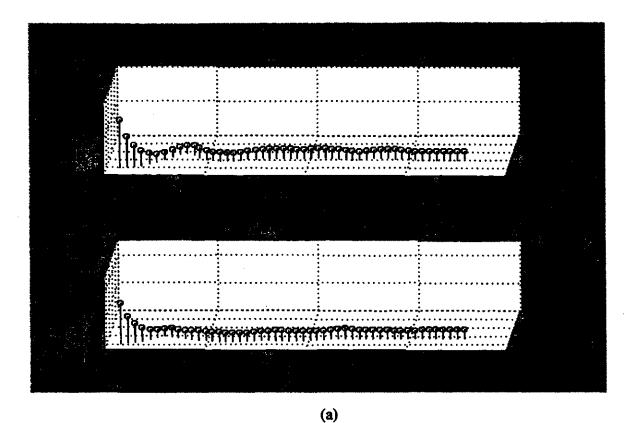

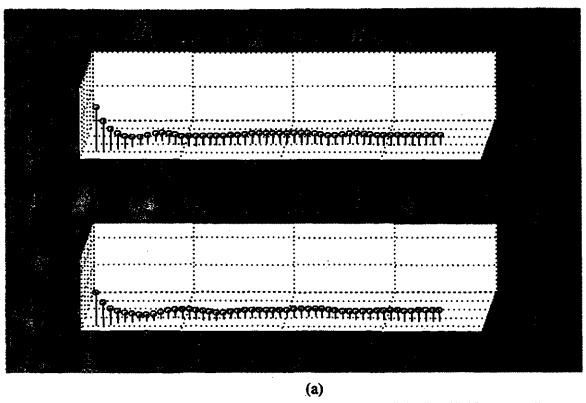

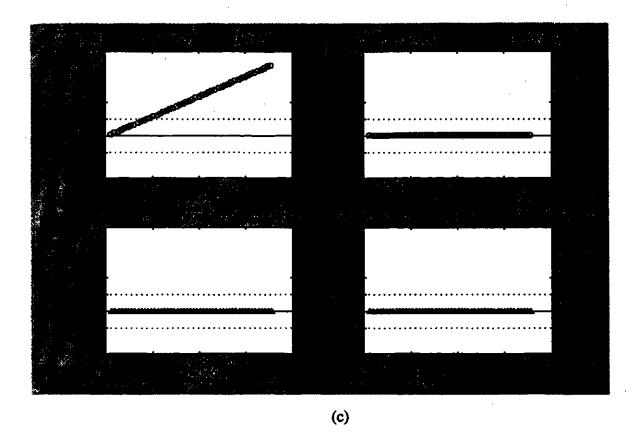

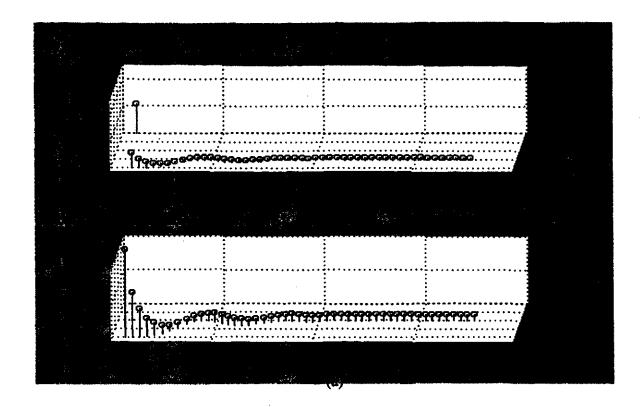

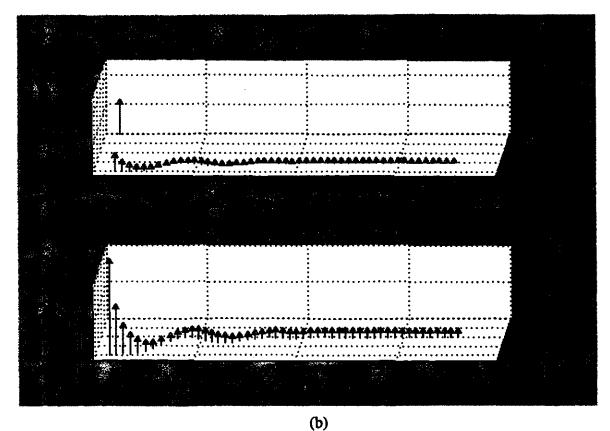

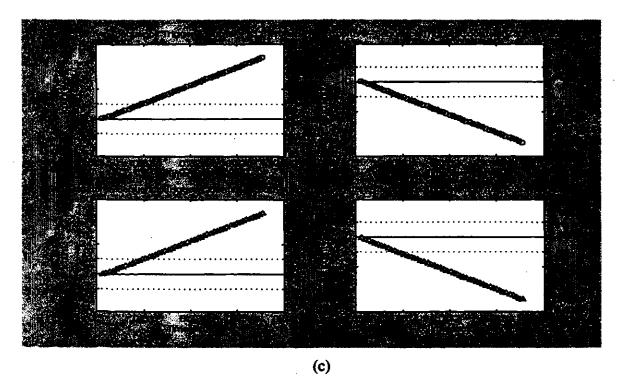

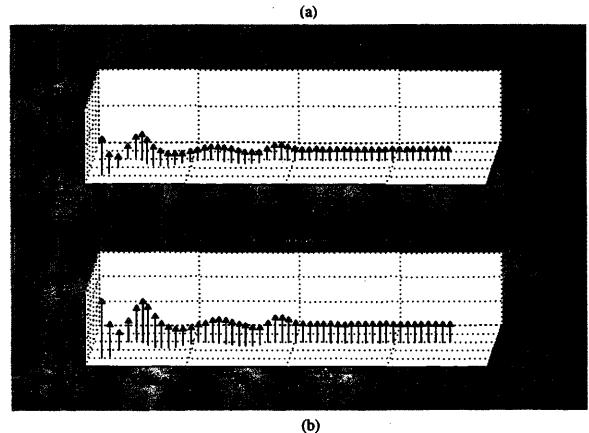

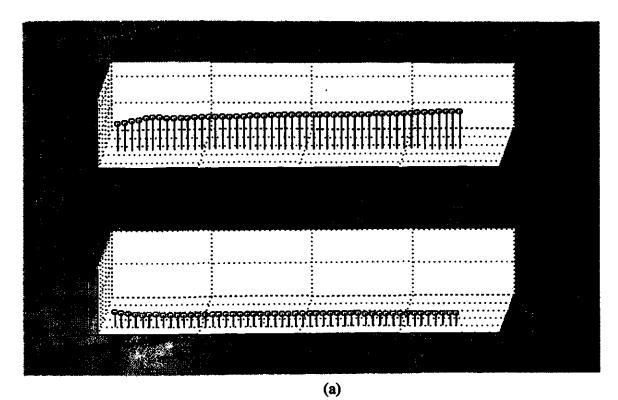

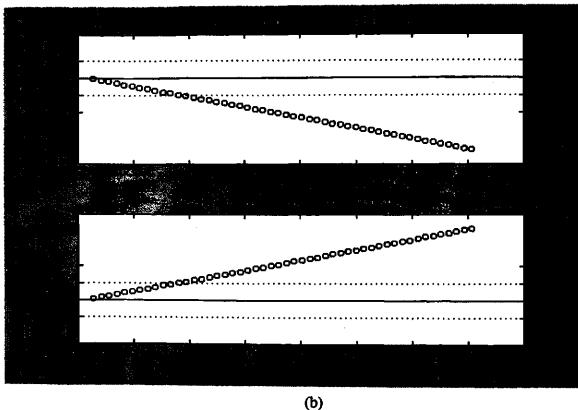

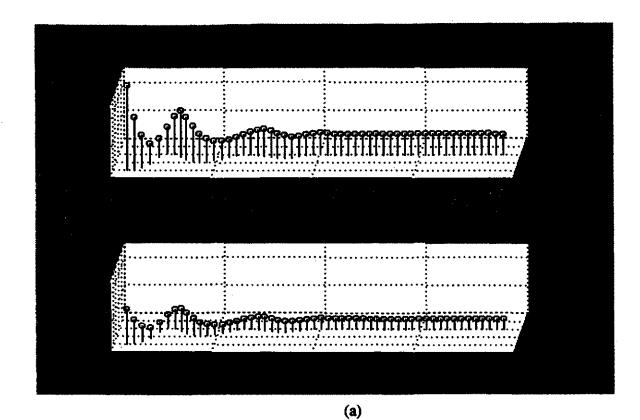

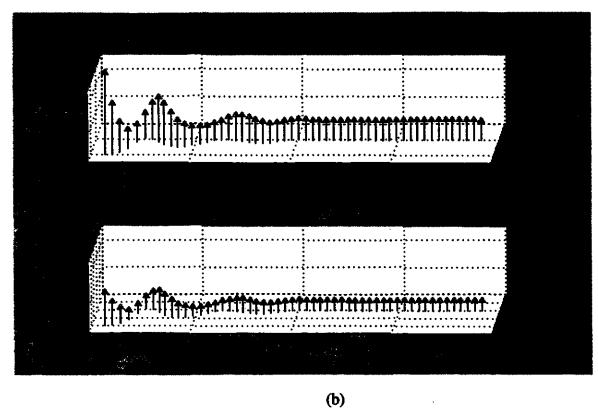

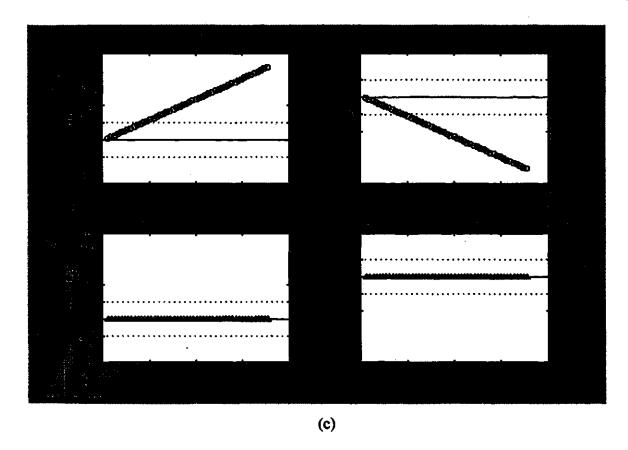

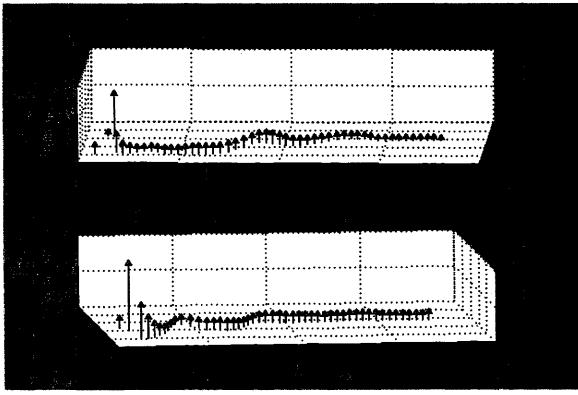

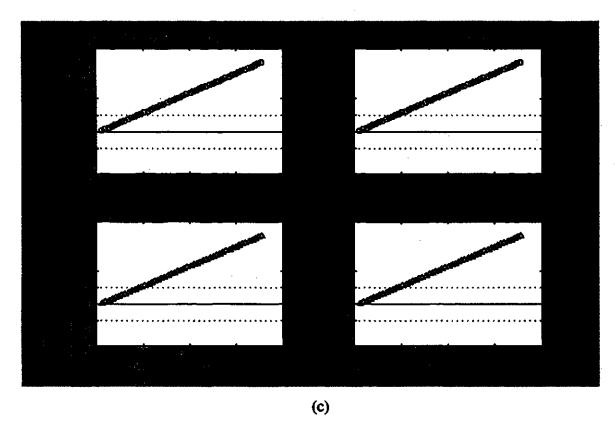

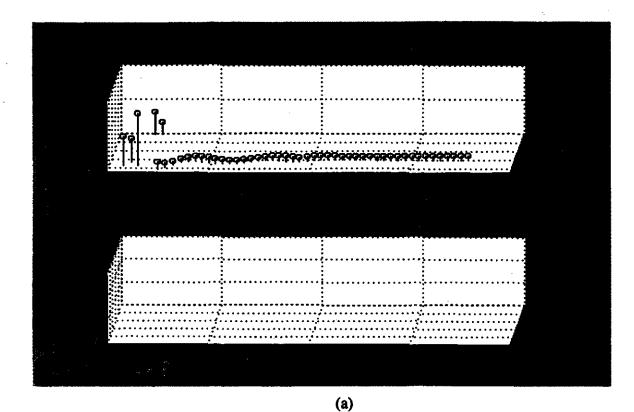

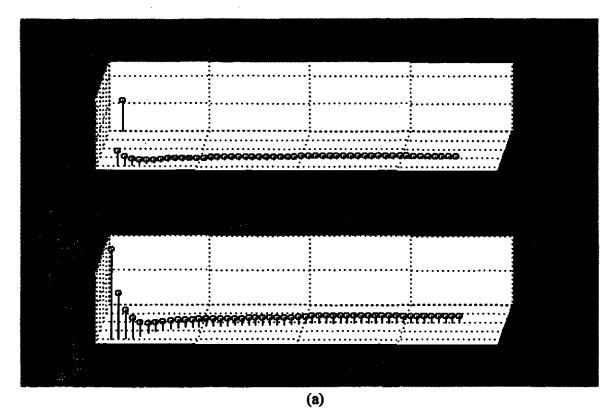

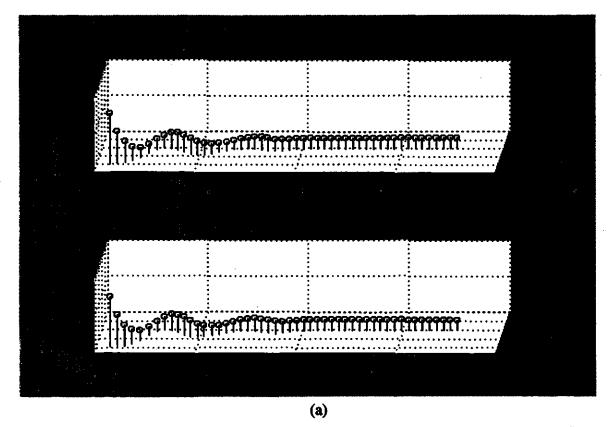

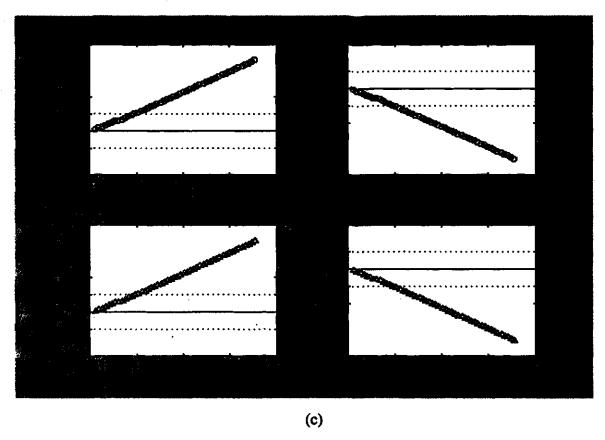

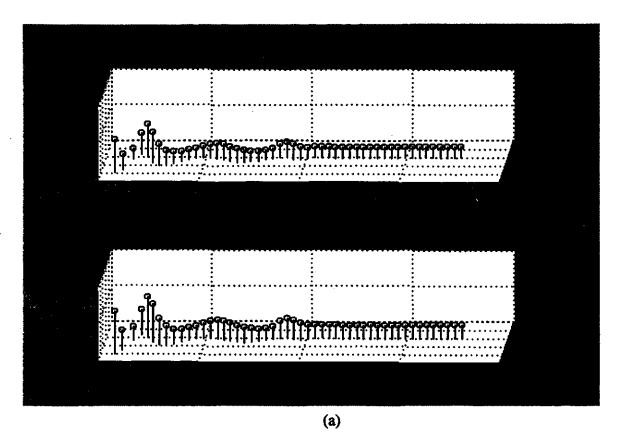

| Figure 3.21. | Correlation of complete current waveform(unsaturated ct) and waveform with samples of low value (saturated ct) with full-cycle Sine and Cosine waveforms - Waveform configurations, Magnitudes of Phasors' Real and Imaginary components & Phasor angle - at different instants of data window (a) $0^0$ (b) $30^0$ (c) $60^0$ (d) $90^0$ w.r.t. Sine and Cosine waveforms. | 69     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 3.21. | Correlation of complete current waveform(unsaturated ct) and waveform with samples of low value (saturated ct) with full-cycle Sine and Cosine waveforms - Waveform configurations, Magnitudes of Phasors' Real and Imaginary components & Phasor angle - at different instants of data window (e)12 0° (f) 150° (g) 180° (h) 210° w.r.t. Sine and Cosine waveforms.        | 70     |

| Figure 3.21. | Correlation of complete current waveform(unsaturated ct) and waveform with samples of low value (saturated ct) with full-cycle Sine and Cosine waveforms -Waveform configurations, Magnitudes of Phasors' Real and Imaginary components & Phasor angle -at different instants of data window (i)240° (j)270° (k) 300° (l) 330° w.r.t. Sine and Cosine waveforms.            | 71     |

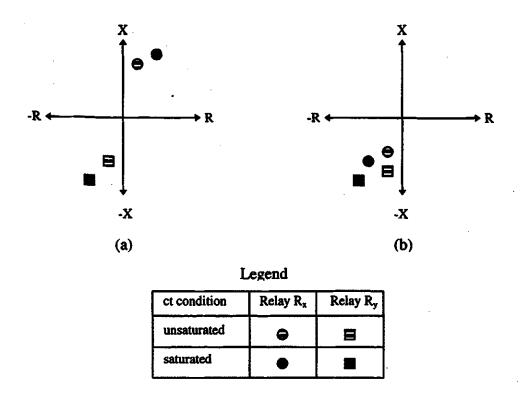

| Figure 3.22. | Effect of ct saturation on impedance seen by relays.                                                                                                                                                                                                                                                                                                                        | 72     |

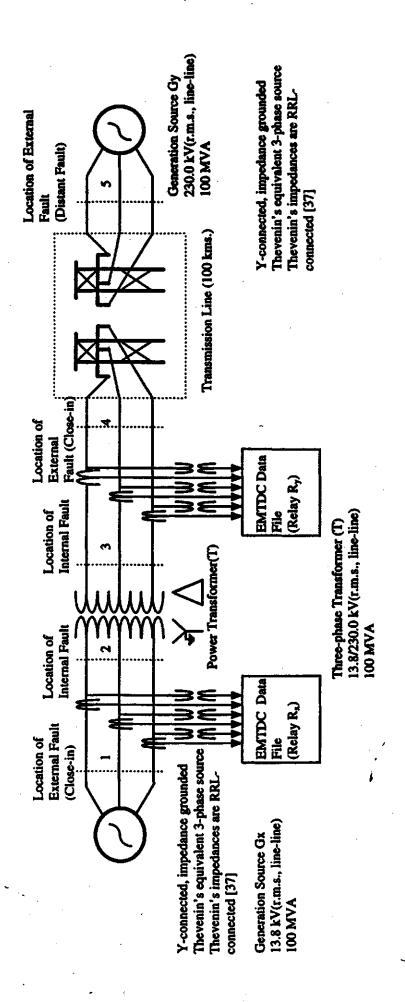

| Figure 4.1.  | System model used for generating simulated data using EMTDC.                                                                                                                                                                                                                                                                                                                | 76     |

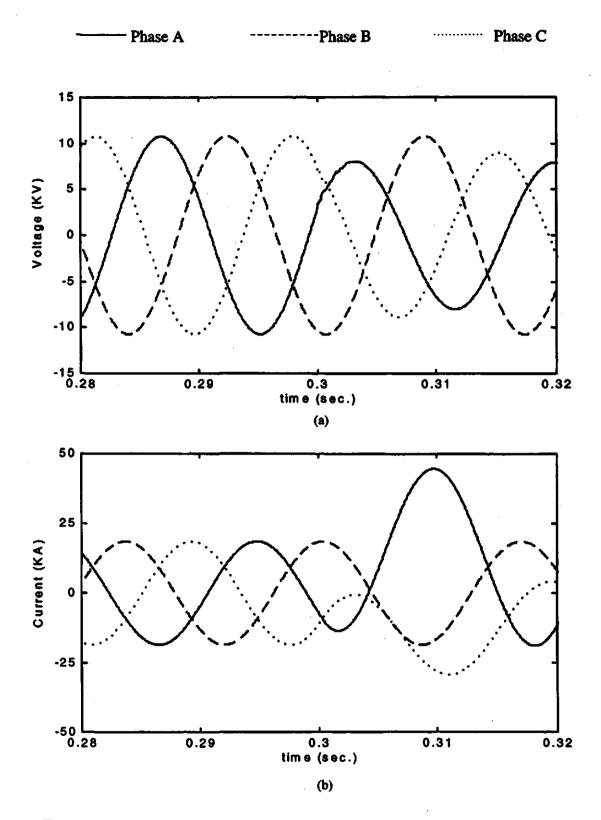

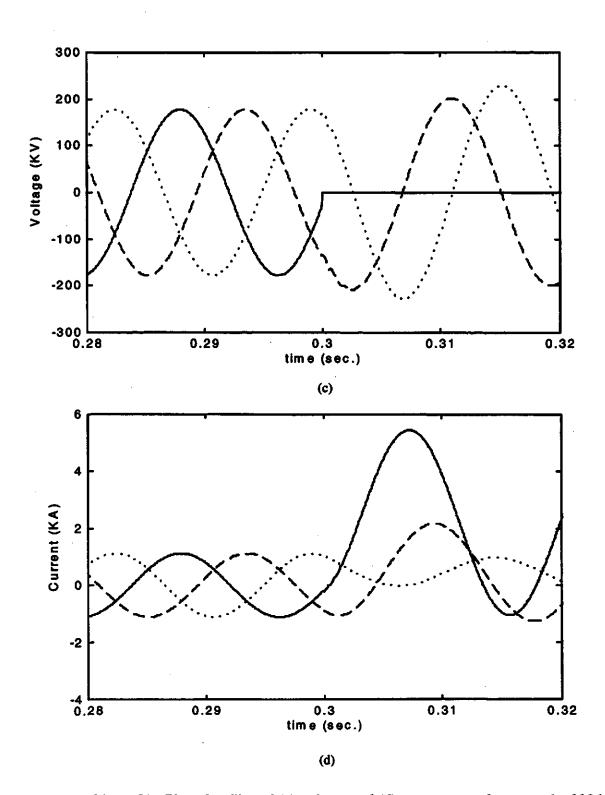

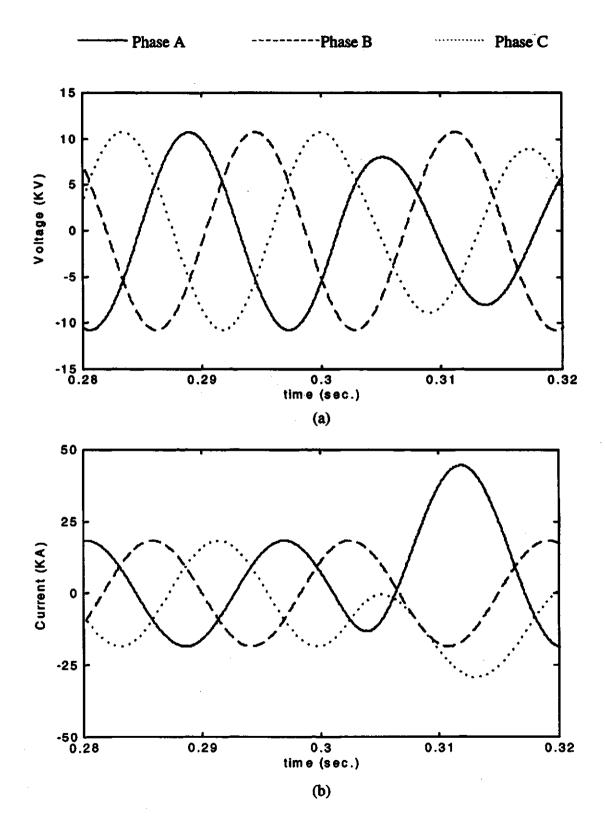

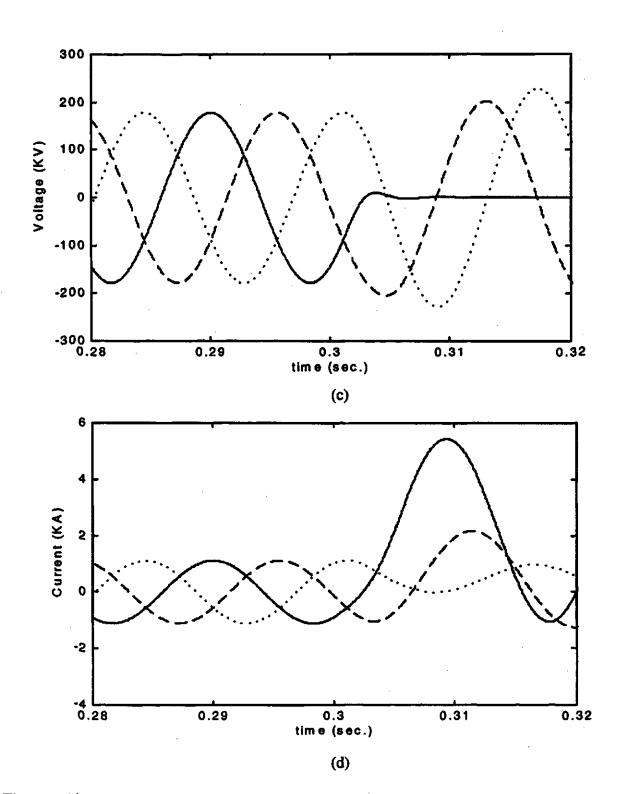

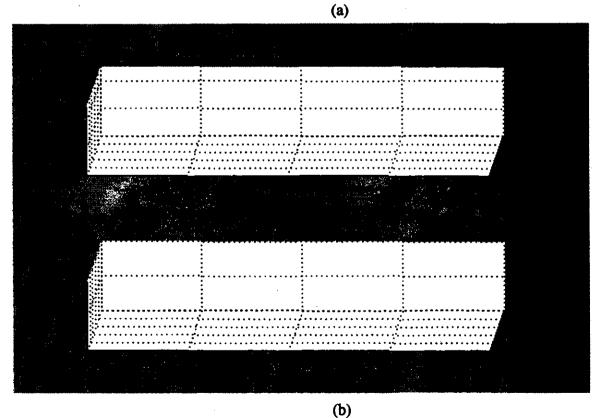

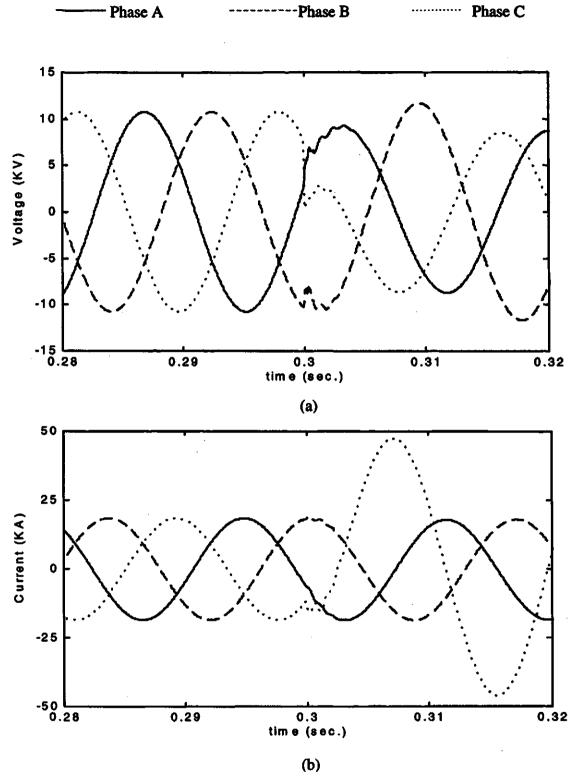

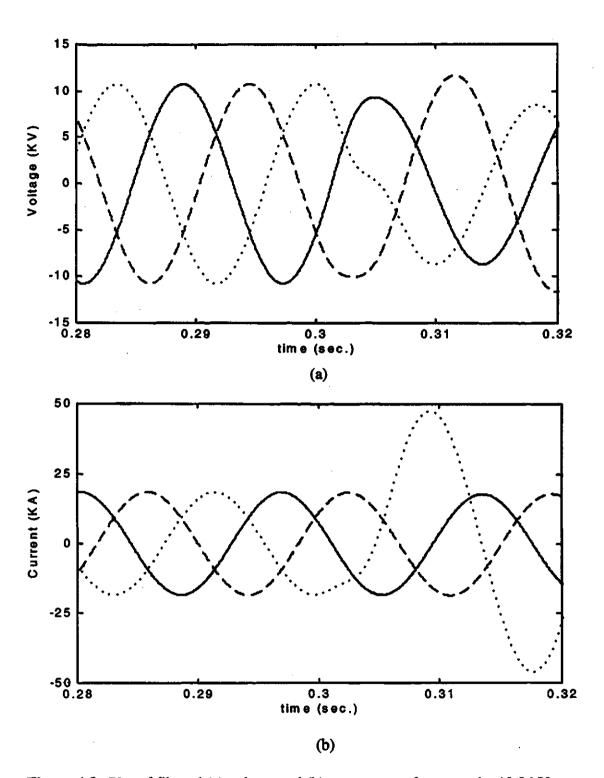

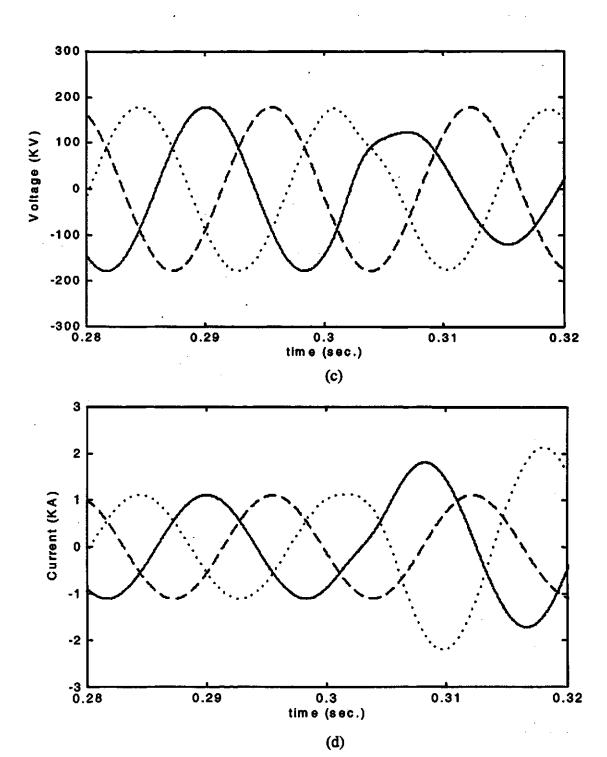

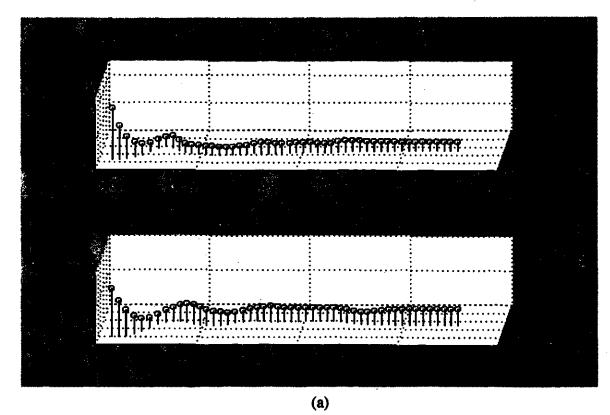

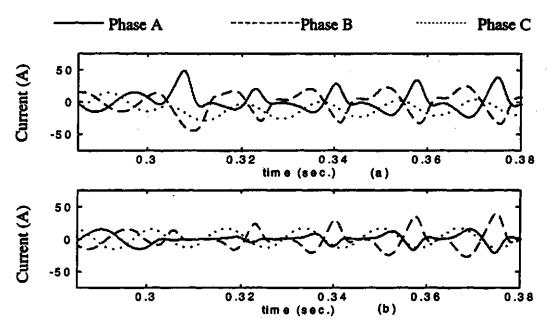

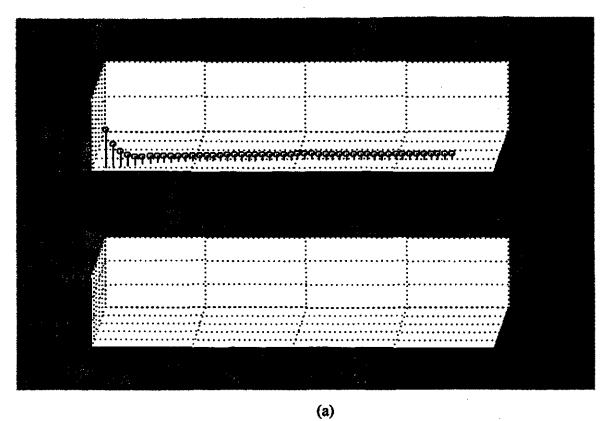

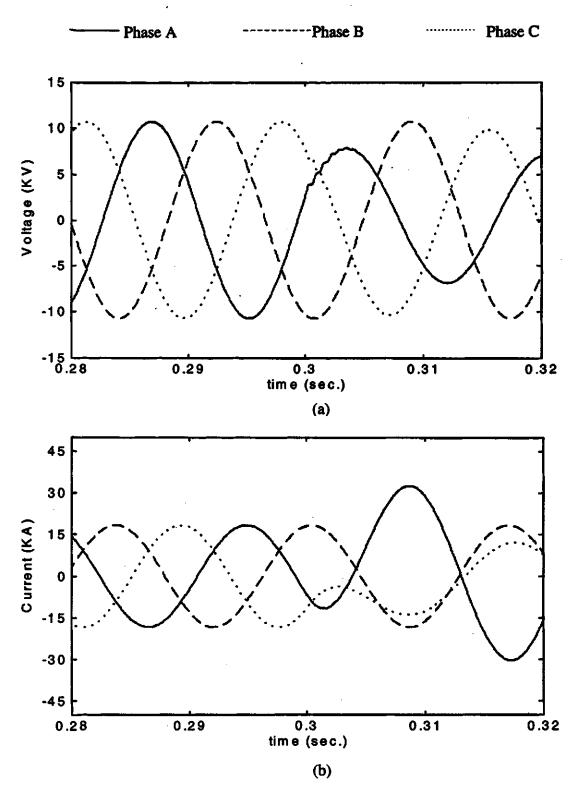

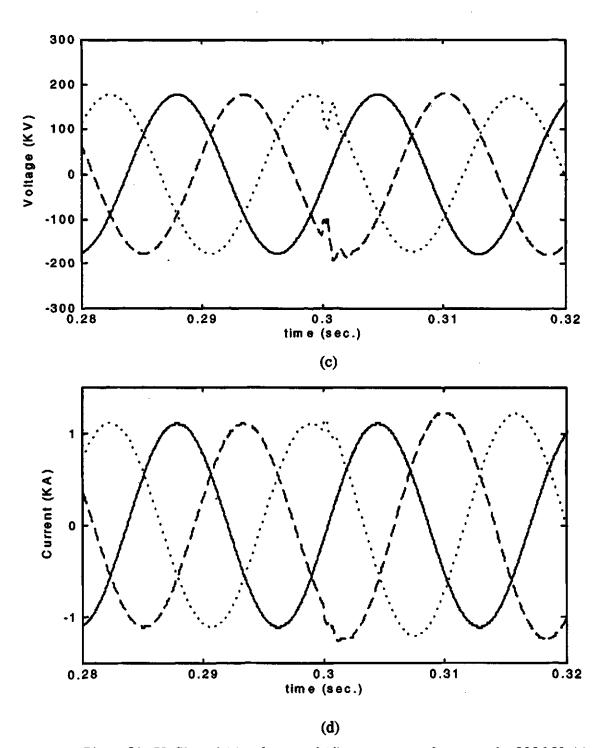

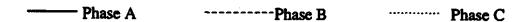

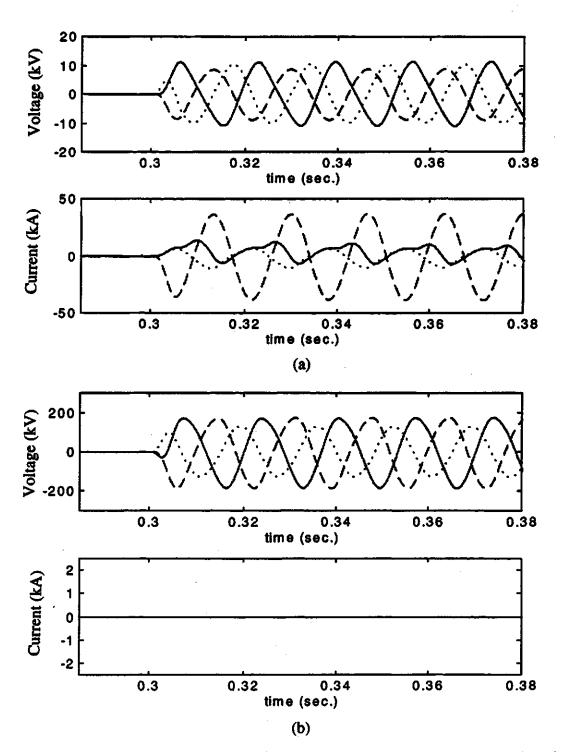

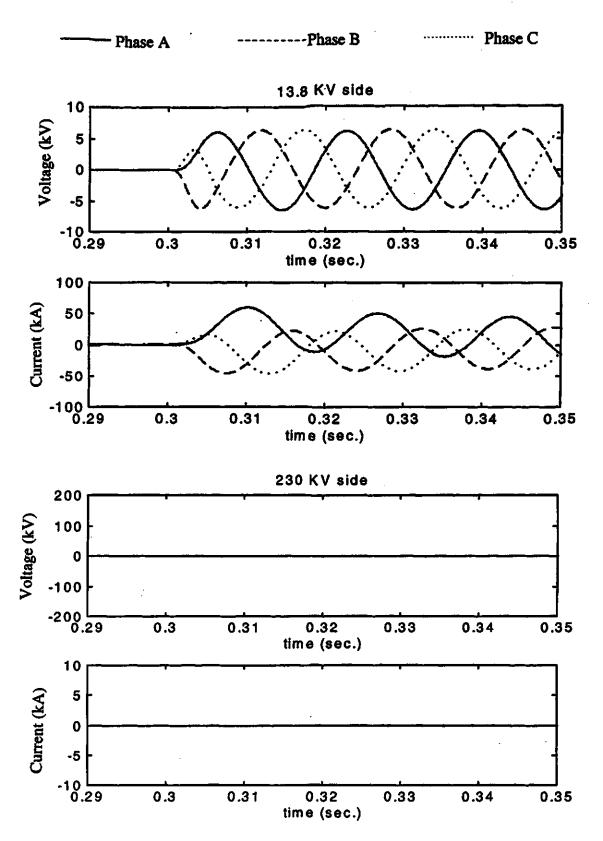

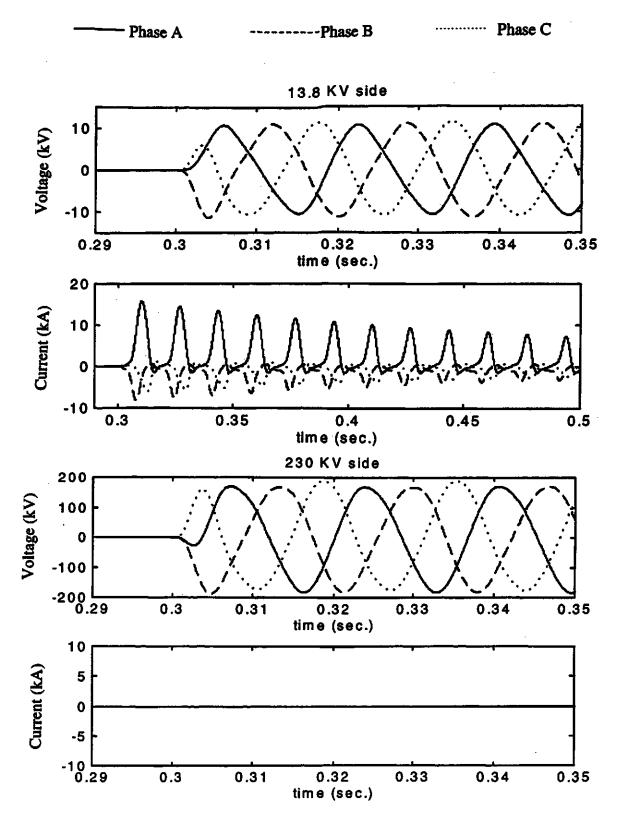

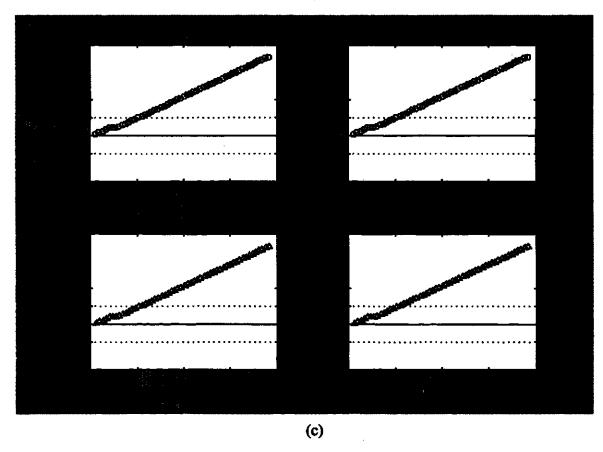

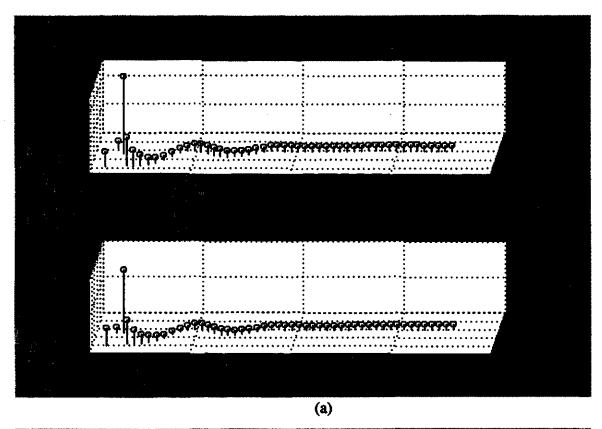

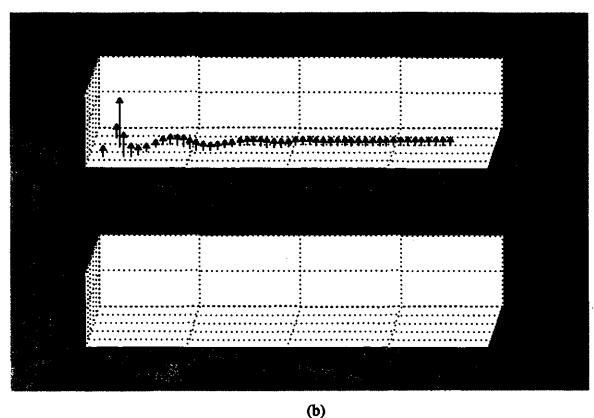

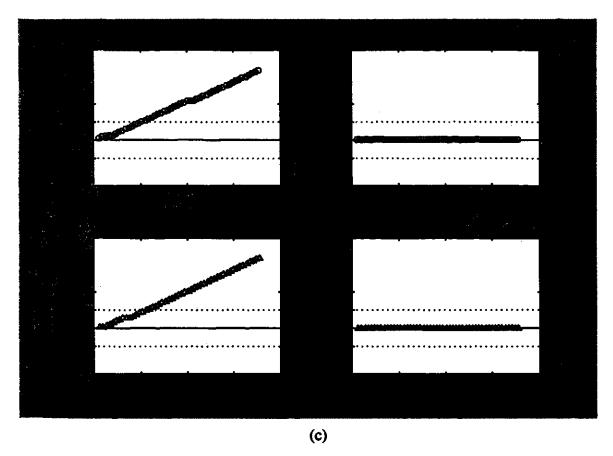

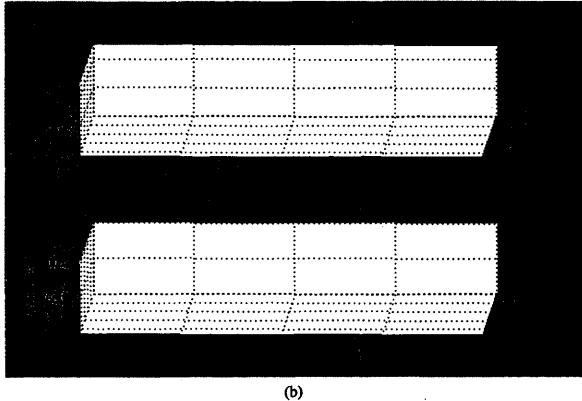

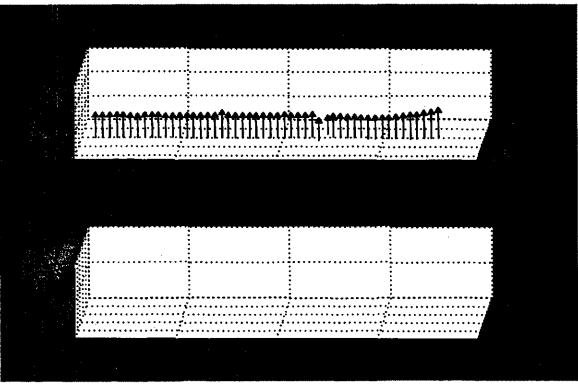

| Figure 4.2.  | Plot of unfiltered (a) voltage and (b) current waveforms on the 13.8 kV side and (c) voltage and (d) current waveforms on the 230 kV side of power transformer for A-g internal fault in the 230 kV winding.                                                                                                                                                                | 79, 80 |

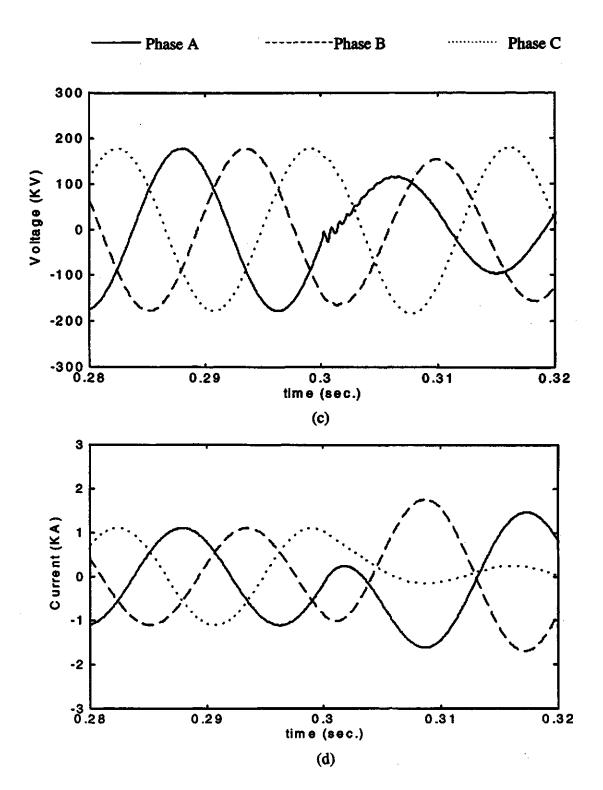

| Figure 4.3.  | Plot of filtered (a) voltage and (b) current waveforms on the 13.8 kV side and filtered (c) voltage and (d) current waveforms on the 230 kV side of power transformer for A-g internal fault in the 230 kV winding.                                                                                                                                                         | 81, 82 |

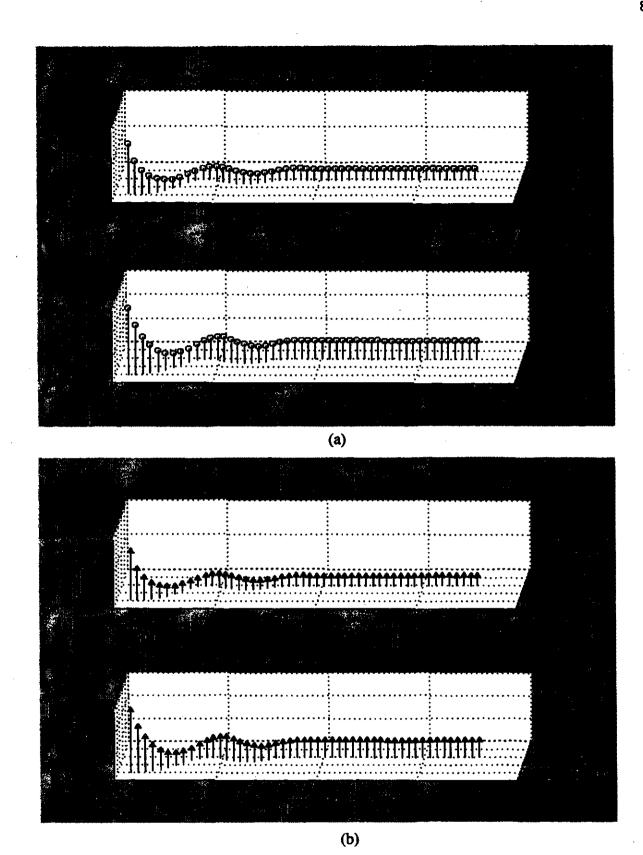

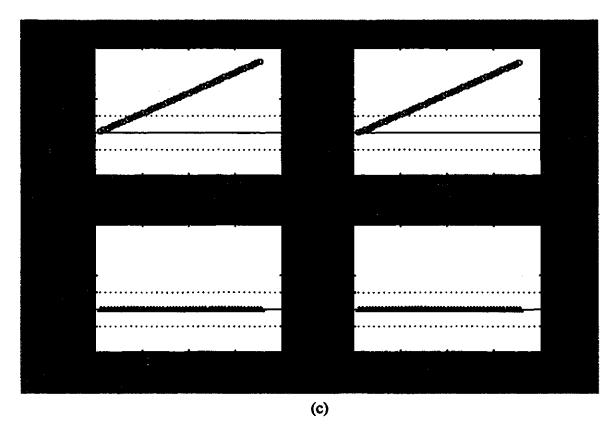

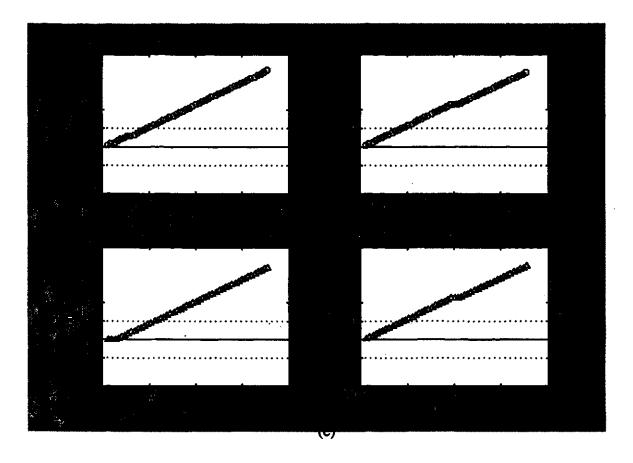

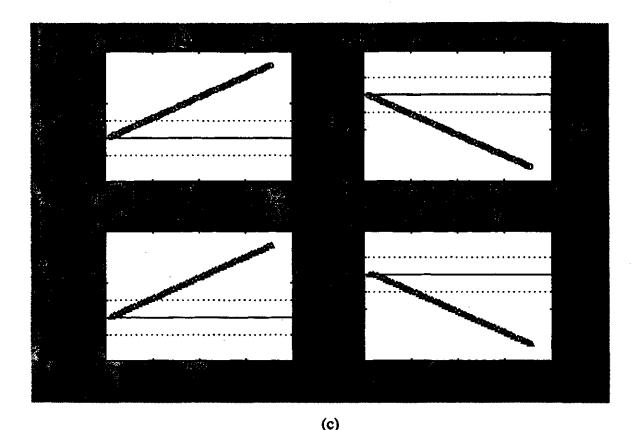

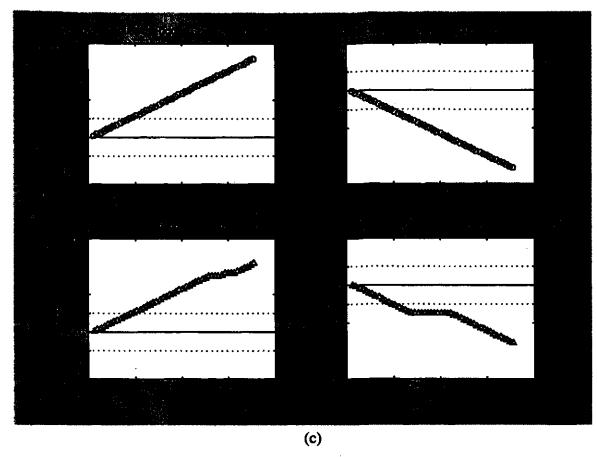

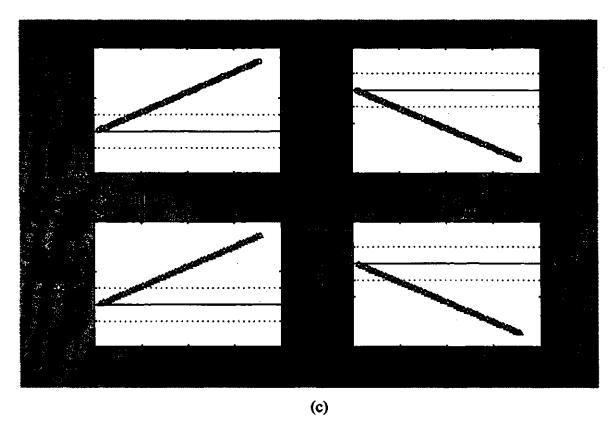

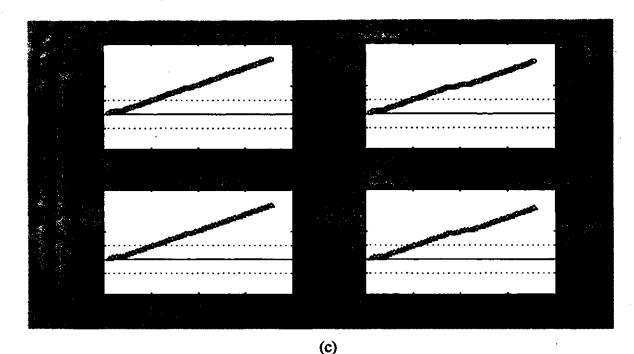

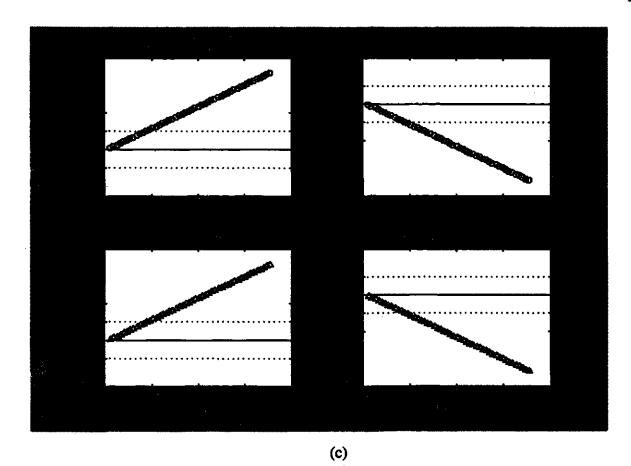

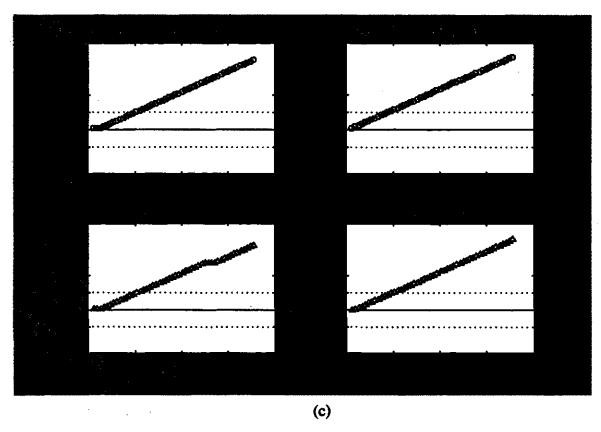

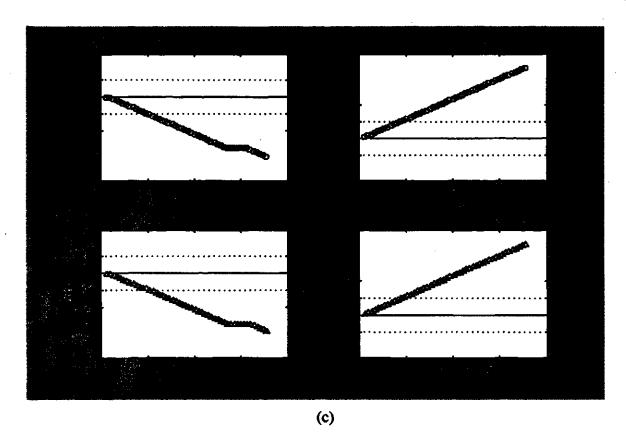

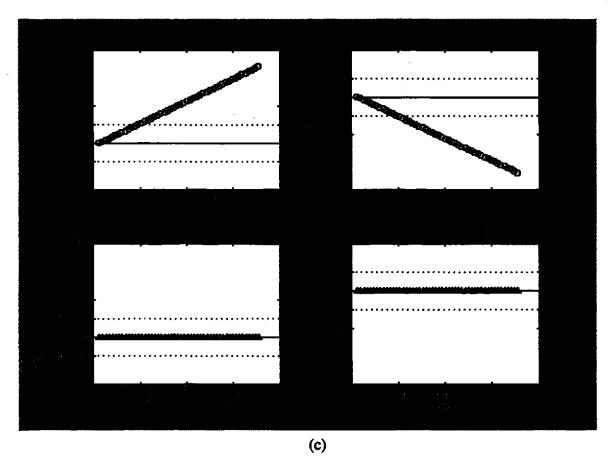

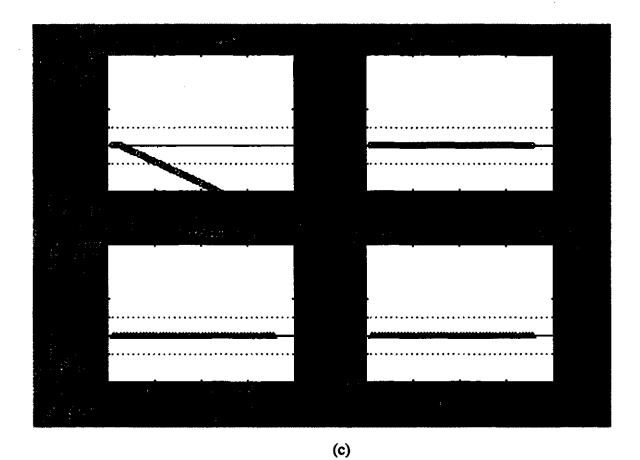

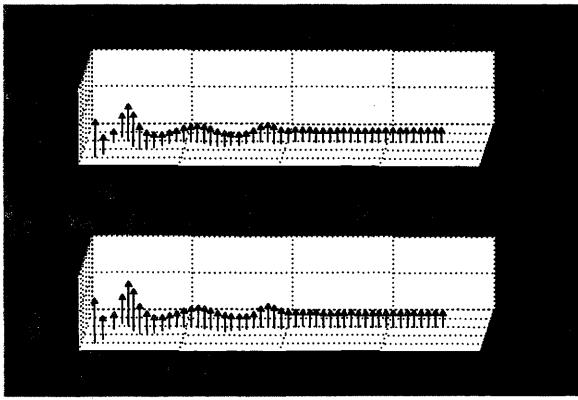

| Figure 4.4.  | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-ground internal fault in the 230 kV winding of the power transformer (location 3, Figure 4.1).                                                                                                                                                                        | 83     |

| Figure 4.4.  | Plot of (c) trip counters for relays on two sides of power transformer for A-g internal fault in 230 kV winding.                                                                                                                                                                                                                                                            | 84     |

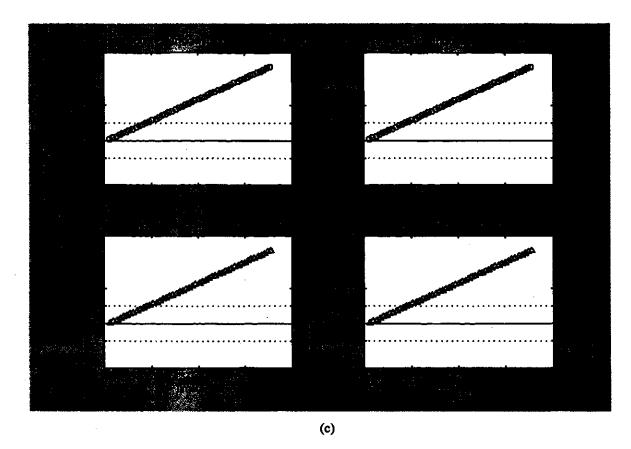

| Figure 4.5.  | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase B-Phase C internal fault in the 230 kV winding of the power transformer (location 3. Figure 4.1)                                                                                                                                                                        | 85     |

| Figure 4.5.  | Plot of (c) trip counters for relays on two sides of power transformer for Phase B-Phase C internal fault in 230 kV winding.                                                                                                                       | 86     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figure 4.6.  | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for a three-phase internal fault in the 13.8 kV winding of the power transformer (location 2, Figure 4.1).                                               | 87     |

| Figure 4.6.  | Plot of (c) trip counters for relays on two sides of the power transformer for a three-phase internal fault in 13.8 kV winding.                                                                                                                    | 88     |

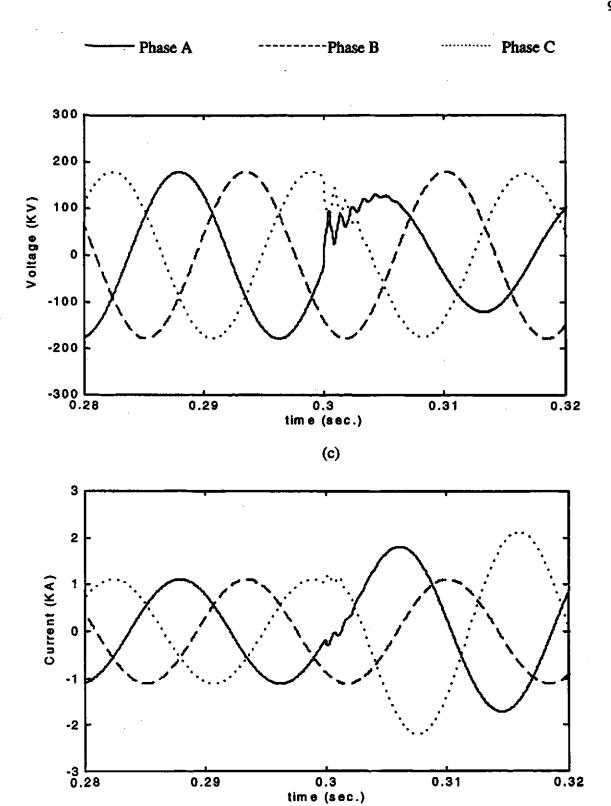

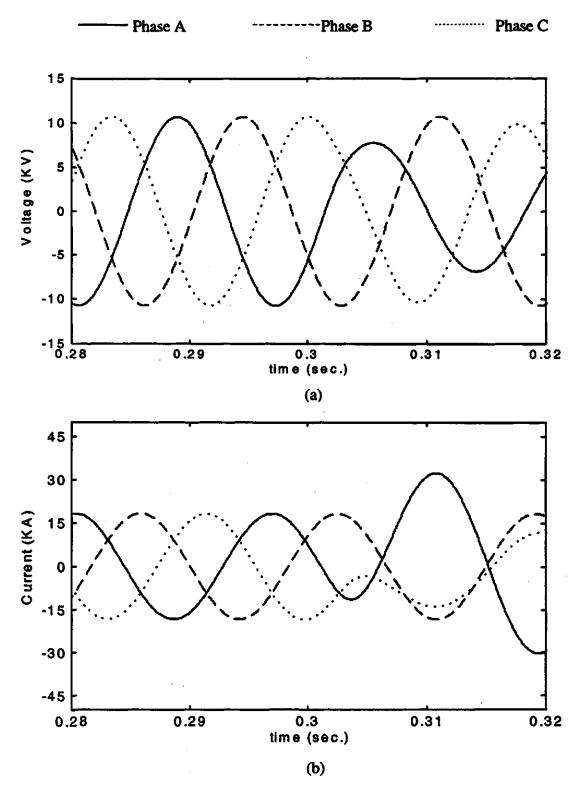

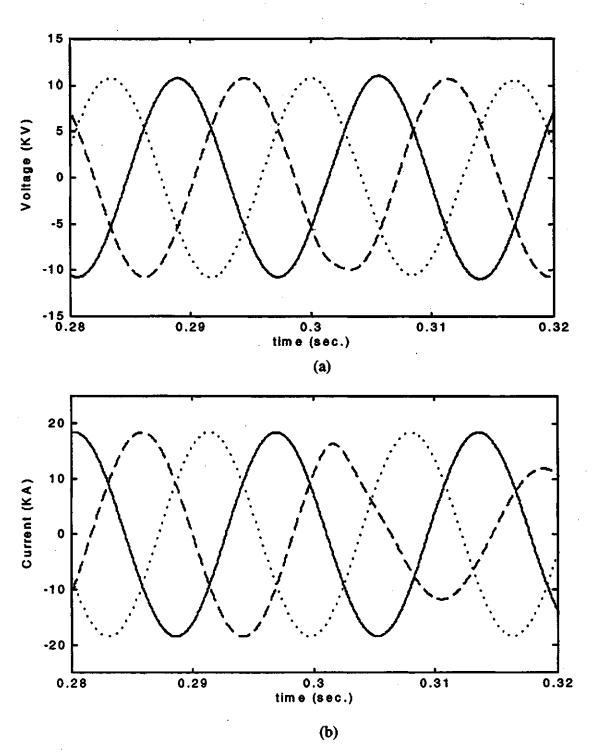

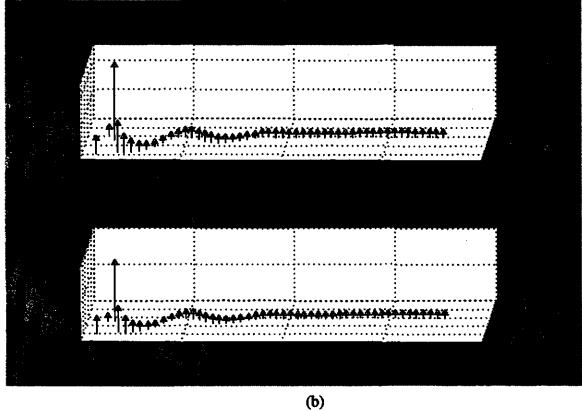

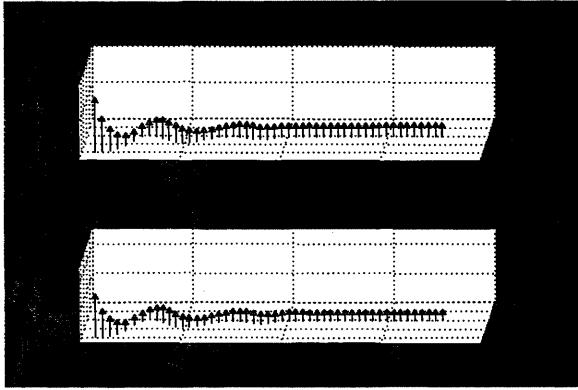

| Figure 4.7.  | Plot of unfiltered (a) voltage and (b) current waveforms on the 13.8 kV side and unfiltered (c) voltage and (d) current waveforms on the 230 kV side of the power transformer for C-g external fault on the 13.8 kV side (location 1, Figure 4.1). | 89, 90 |

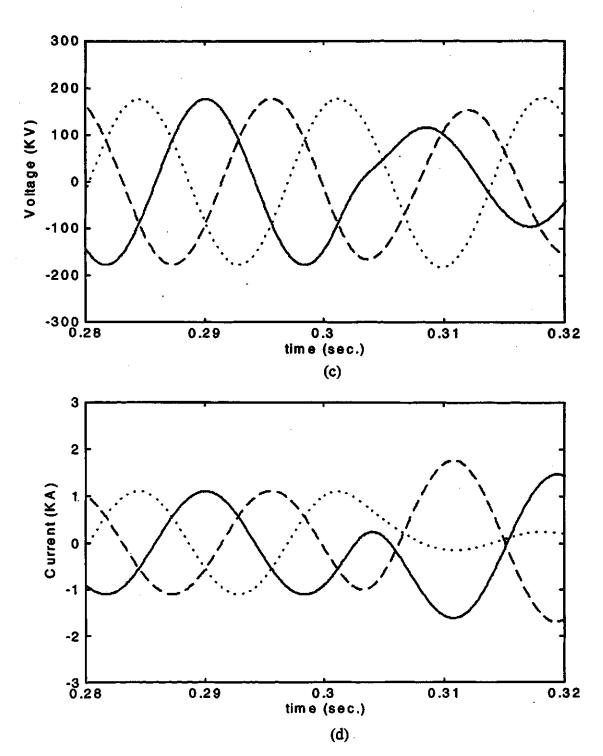

| Figure 4.8.  | Plot of filtered (a) voltage and (b) current waveforms on the 13.8 kV side and filtered (c) voltage and (d) current waveforms on the 230 kV side of the power transformer for C-g external fault on the 13.8 kV side (location 1, Figure 4.1).     | 91, 92 |

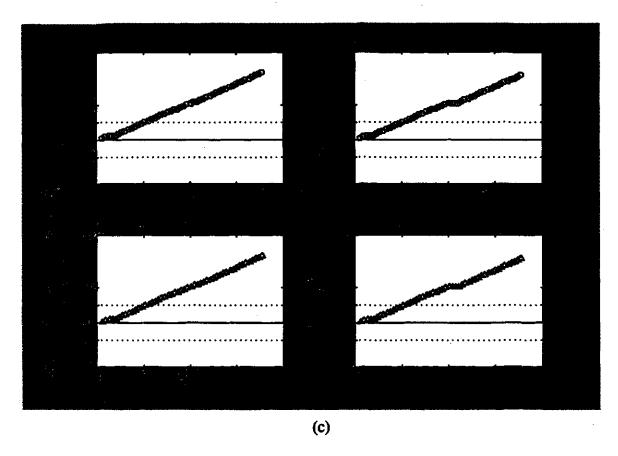

| Figure 4.9.  | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase C-ground external fault on the 13.8 kV side of the power transformer (location 1, Figure 4.1).                                                 | 94     |

| Figure 4.9.  | Plot of (c) trip counters for relays on two sides of power transformer for C-g external fault on 13.8 kV side (location 1, Figure 4.1).                                                                                                            | 95     |

| Figure 4.10. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-Phase B external fault on the 230 kV side of the power transformer (location 5, Figure 4.1).                                                 | 96     |

| Figure 4.10. | Plot of (c) trip counters for Phase A-Phase B external fault on 230 kV side of the power transformer (location 5, Figure 4.1).                                                                                                                     | 97     |

| Figure 4.11. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for a three-phase external fault on the 230 kV side of the power transformer (location 5, Figure 4.1).                                                   | 98     |

| Figure 4.11. | Plot of (c) trip counters for three-phase external fault on 230 kV side of the power transformer (location 5, Figure 4.1).                                                                                                                         | 99     |

| Figure 4.12. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-ground external fault on the 13.8 kV side of the power transformer (location 1, Figure 4.1).                                                 | 100    |

| Figure 4.12. | Plot of (c) trip counters for Phase A-g external fault on 13.8 kV side                                                                                                                                                                             | 101    |

| of the power transformer (location 1, Fi | rigure | 4. i). |

|------------------------------------------|--------|--------|

|------------------------------------------|--------|--------|

| Figure 4.13. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-Phase B external fault on the 230 kV side of the power transformer (location 5, Figure 4.1).   | 103 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.13. | Plot of (c) trip counters for Phase A-Phase B external fault on 230 kV side of the power transformer (at location 5, Figure 4.1).                                                                    | 104 |

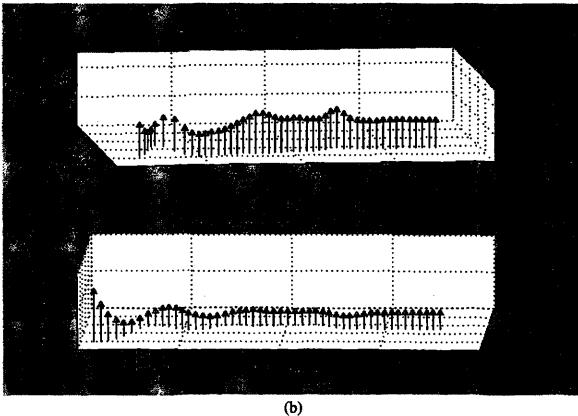

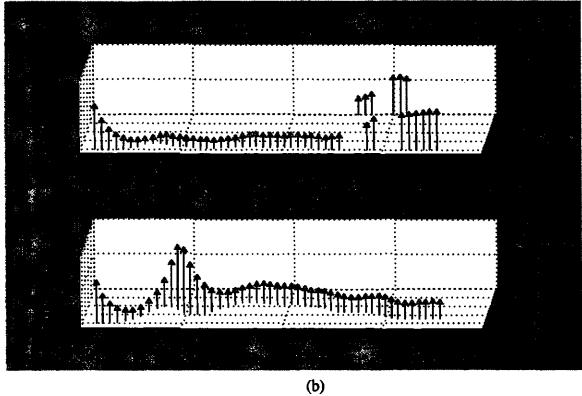

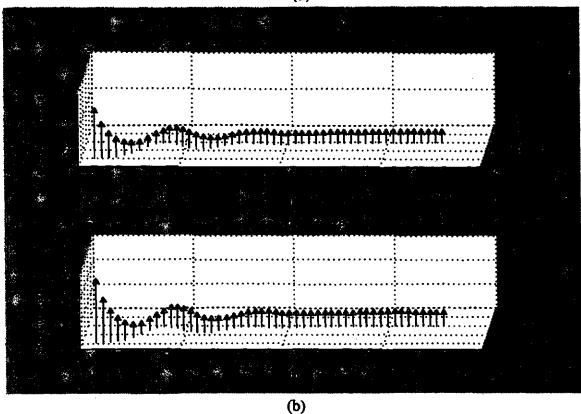

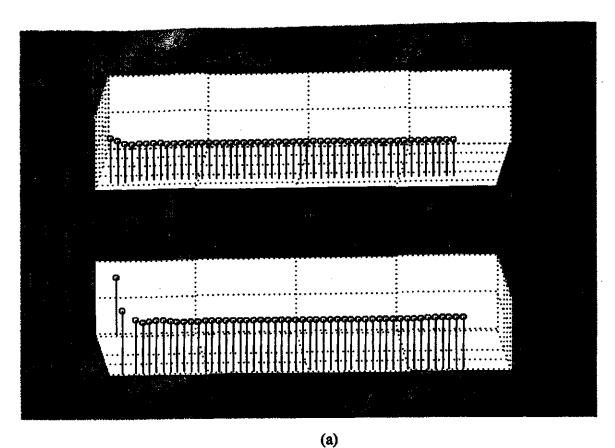

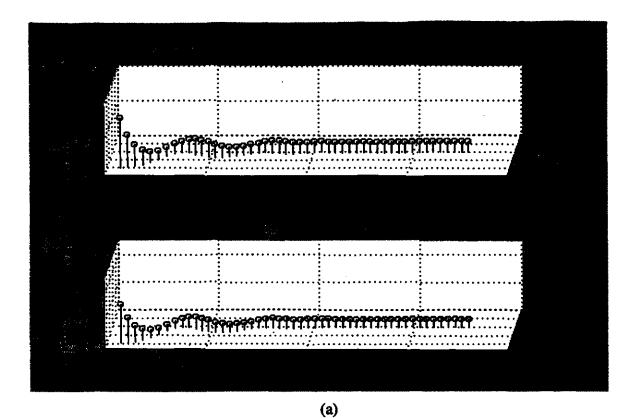

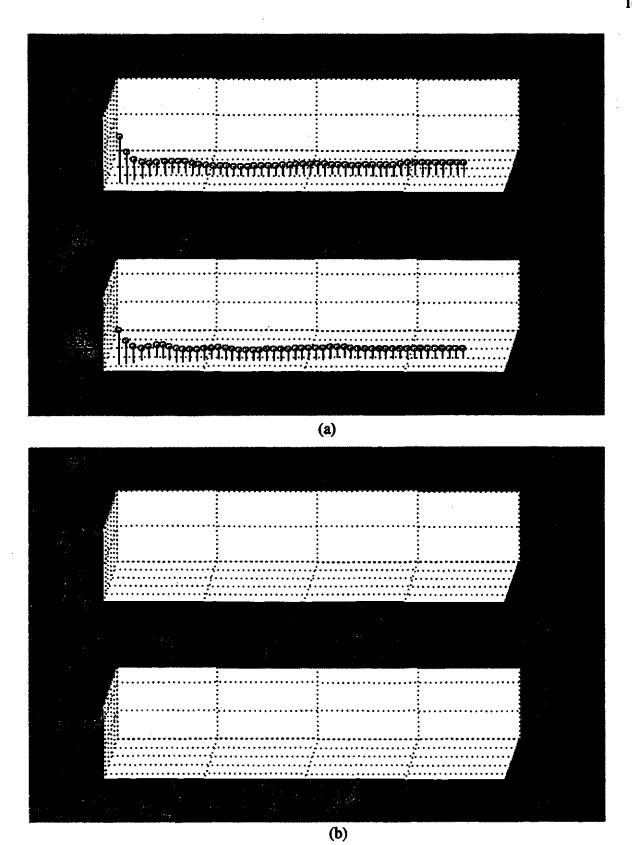

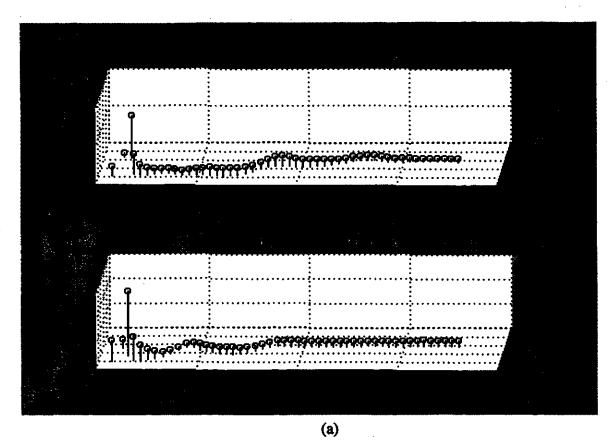

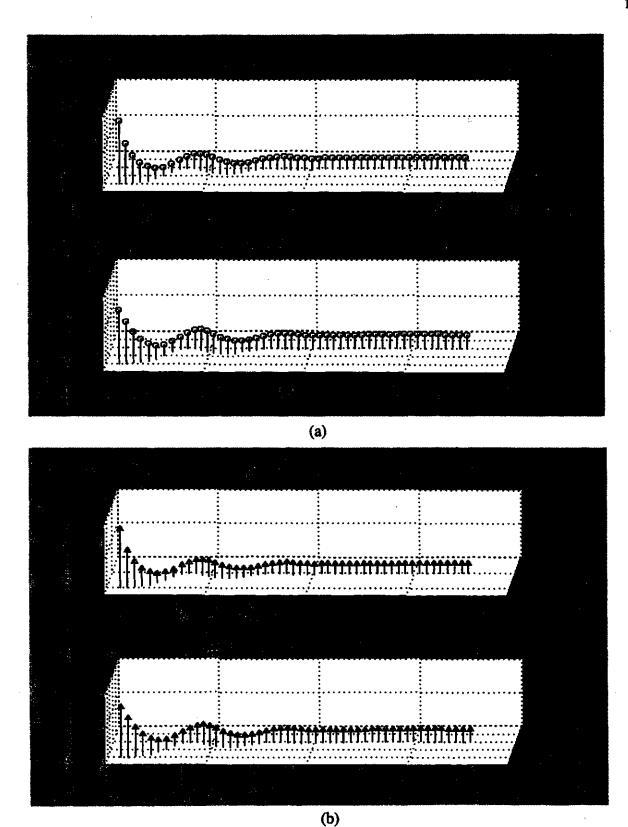

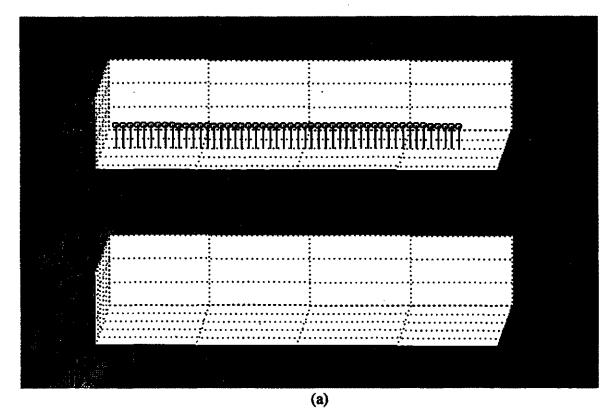

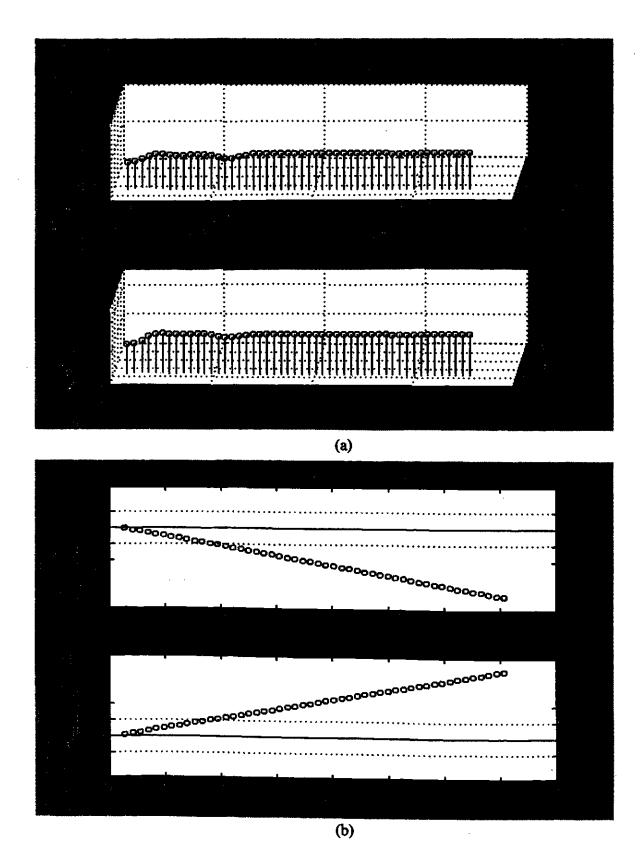

| Figure 4.14. | Plot of ct output waveforms on (a) 13.8 kV and (b) 230 kV sides of power transformer for a three-phase internal fault in 13.8 kV winding.                                                            | 104 |

| Figure 4.15. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for a three-phase internal fault in the 13.8 kV winding of the power transformer (location 2, Figure 4.1). | 106 |

| Figure 4.15. | Plot of (c) trip counters for a three-phase internal fault in the 13.8 kV winding (location 2, Figure 4.1).                                                                                          | 107 |

| Figure 4.16. | Plot of ct output waveforms on (a) 13.8 kV and (b) 230 kV sides of power transformer for B-ground internal fault in 230 kV winding.                                                                  | 107 |

| Figure 4.17. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase B-ground internal fault in the 230 kV winding of the power transformer (location 3, Figure 4.1). | 108 |

| Figure 4.17. | Plot of (c) trip counters for Phase B-ground internal fault in the 230 kV winding of the power transformer (location 3, Figure 4.1).                                                                 | 109 |

| Figure 4.18. | Plot of ct output waveforms on (a) 13.8 kV and (b) 230 kV sides of power transformer for Phase A - Phase B external fault on 230 kV side (location 5, Figure 4.1).                                   | 110 |

| Figure 4.19. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-Phase B external fault on the 230 kV side of the power transformer (location 5, Figure 4.1).   | 111 |

| Figure 4.19. | Plot of (c) trip counters for Phase A-Phase B external fault on 230 kV side of the power transformer (Location 5, Figure 4.1).                                                                       | 112 |

| Figure 4.20. | Plot of ct output waveforms on (a) 13.8 kV and (b) 230 kV sides of power transformer for Phase A - Phase B-ground external fault on 230 kV side (location 4, Figure 4.1).                            | 113 |

| Figure 4.21. | Plot of (a) positive-sequence and (b) negative-sequence impedances                                                                                                                                   | 114 |

|              | 4.1).                                                                                                                                                                                                                                 |          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 4.21. | Plot of (c) trip counters for Phase A-Phase B-ground external fault on 230 kV side of the power transformer (location 4, Figure 4.1).                                                                                                 | 115      |

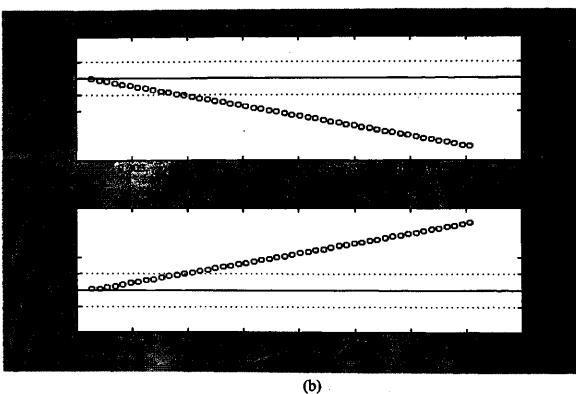

| Figure 4.22. | Plot of (a) positive-sequence and (b) negative-sequence impedances on 13.8 kV and 230 kV sides of the unloaded transformer for a three-phase fault in the 230 kV side.                                                                | 116      |

| Figure 4.22. | Plot of trip counters on the 13.8 kV and 230 kV sides of the unloaded transformer for a three-phase fault in the 230 kV side.                                                                                                         | 117      |

| Figure 4.23. | Plot of (a) positive-sequence and (b) negative-sequence impedances on 13.8 kVand 230 kV sides of the unloaded transformer for a Phase B - Phase C fault on the 230 kV side.                                                           | 118      |

| Figure 4.23. | Plot of trip counters on the 13.8 kV and 230 kV sides of the unloaded transformer for a Phase B - Phase C fault on the 230 kV side.                                                                                                   | 119      |

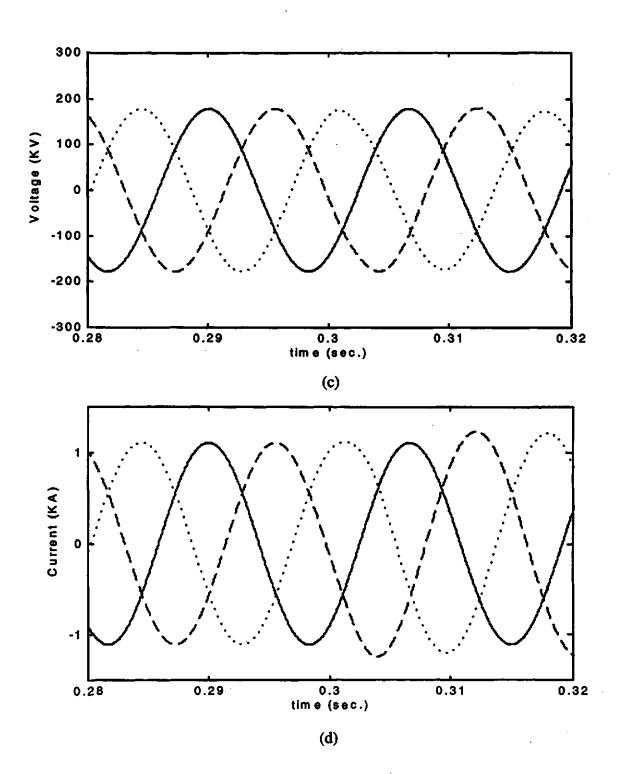

| Figure 4.24. | Unfiltered (a) voltage and (b) current waveforms on the 13.8 kV side and (a) voltage and (b) current waveforms on the 230 kV side of power transformer for Phase A-ground external fault on 230 kV side (location 5, Figure 4.1).     | 120, 121 |

| Figure 4.25. | Filtered (a) voltage and (b) current waveforms on the 13.8 kV side and (c) voltage and (d) current waveforms on the 230 kV side of power transformer for Phase A-ground external fault on 230 kV side (location 5, Figure 4.1).       | 122, 123 |

| Figure 4.26. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-ground external fault on the 230 kV side of the power transformer.                                                              | 124      |

| Figure 4.26. | Plot of (c) trip counters for a high-impedance Phase A-ground external fault on 230 kV side of the power transformer (location 5, Figure 4.1).                                                                                        | 125      |

| Figure 4.27. | Unfiltered (a) voltage and (b) current waveforms on the 13.8 kV side and (c) voltage and (d) current waveforms on the 230 kV side of power transformer for Phase B-ground internal fault in 13.8 kV winding (location 2, Figure 4.1). | 126, 127 |

| Figure 4.28. | Filtered (a) voltage and (b) current waveforms on the 13.8 kV side and (c) voltage and (d) current waveforms on the 230 kV side of                                                                                                    | 128, 129 |

on the 230 kV side of the power transformer (location 4, Figure

|              | winding (location 2, Figure 4.1).                                                                                                                                                                     | -   |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.29. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase B-ground internal fault in the 13.8 kV winding of the power transformer (location 2, Figure 4.1). | 131 |

| Figure 4.29. | Plot of (c) trip counters for a high-impedance Phase B-ground internal fault in 13.8 kV winding of the power transformer (location 2, Figure 4.1).                                                    | 132 |

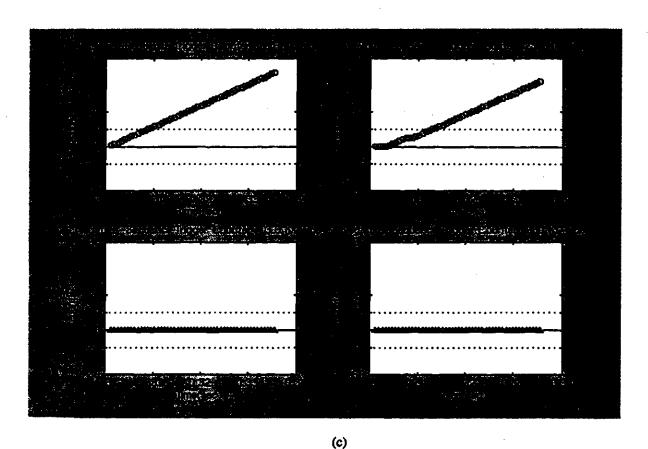

| Figure 4.30. | Plot of (a) positive-sequence impedance computed by the relays and (b) trip counters for Phase A-Phase B switch-on external fault for the power transformer (location A, Figure 3.14).                | 133 |

| Figure 4.31. | Plot of (a) positive-sequence impedance computed by the relays and (b) trip counters for Phase A-ground switch-on external fault for the power transformer (location A, Figure 3.14).                 | 134 |

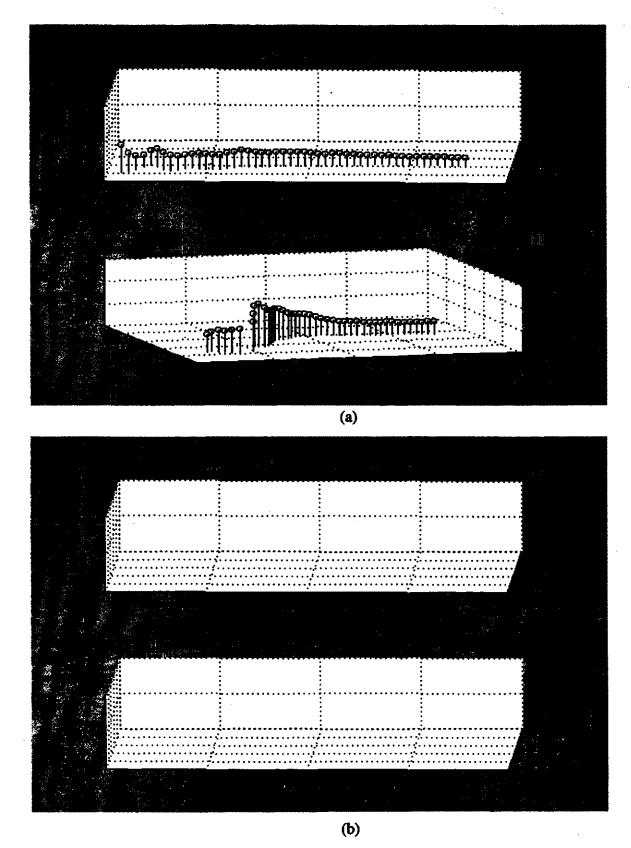

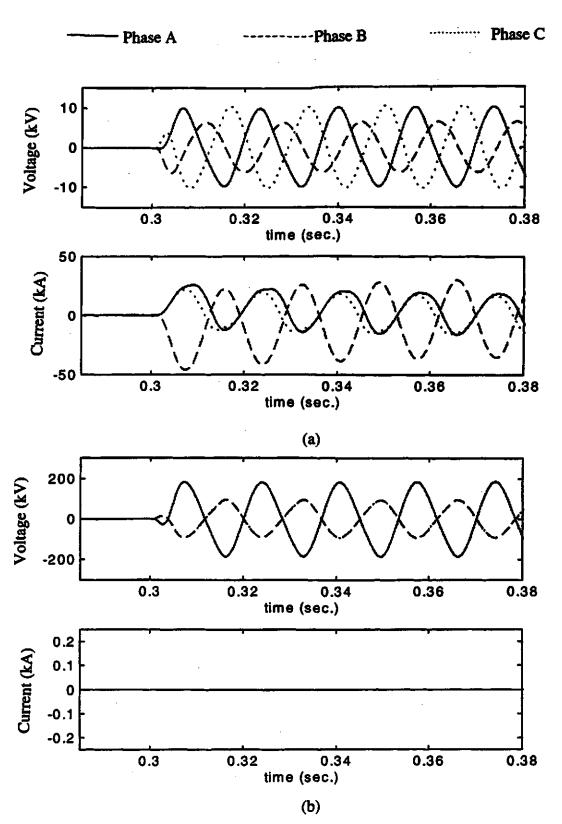

| Figure 4.32. | Voltage and current waveforms on (a) 13.8 kV and (b) 230 kV sides of power transformer for Phase B-ground switch-on internal fault in 13.8 kV winding.                                                | 136 |

| Figure 4.33. | Voltage and current waveforms on 13.8 kV and 230 kV sides of power transformer for a three-phase-ground switch-on internal fault in the 230 kV winding.                                               | 137 |

| Figure 4.34. | Voltage and current waveforms on (a) 13.8 kV and (b) 230 kV sides of power transformer for Phase B - Phase C switch-on internal fault in the 230 kV winding.                                          | 139 |

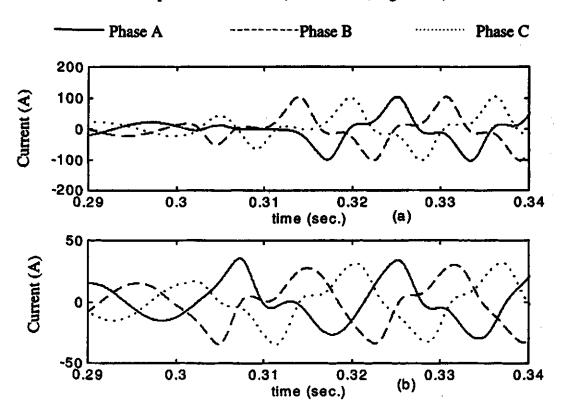

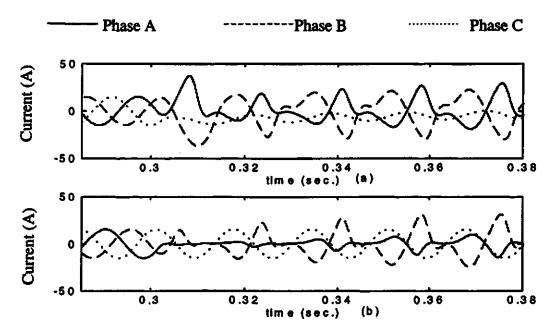

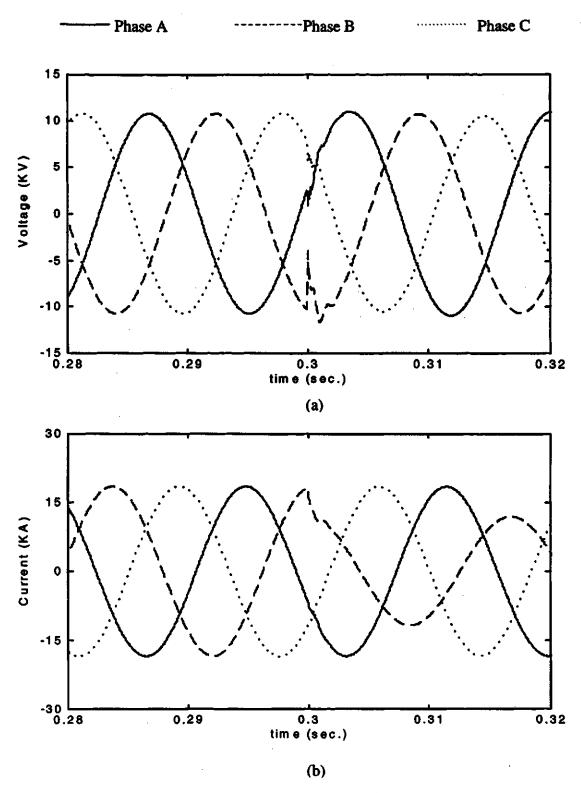

| Figure 4.35. | Voltage and current waveforms on 13.8 kV and 230 kV sides of the power transformer for magnetizing inrush condition (transformer switched-on at 0.3 seconds).                                         | 140 |

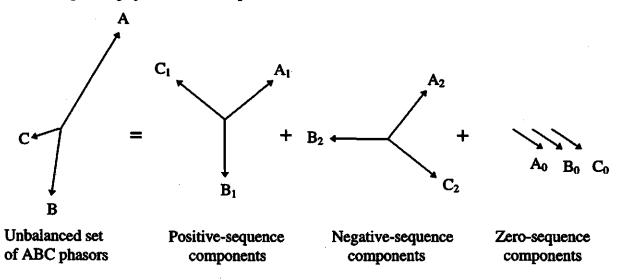

| Figure A.1.  | Decomposition of an unbalanced set of ABC phasors into symmetrical components.                                                                                                                        | 150 |

| Figure B.1.  | CT model.                                                                                                                                                                                             | 153 |

| Figure D.1.  | Magnitude response of anti-aliasing filter.                                                                                                                                                           | 158 |

| Figure E.1.  | Plot of (a) positive-sequence and (b) negative-sequence impedances for relays on two sides of power transformer for C-g internal fault in the 230 KV winding (location 3, Figure 4.1).                | 160 |

| Figure E.1.  | Plot of (c) trip counters for relays on two sides of power                                                                                                                                            | 161 |

power transformer for Phase B-ground internal fault in 13.8 kV

|             | transformer for C-g internal fault in the 230 KV winding (location 3, Figure 4.1).                                                                                                                     |             |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure E.2. | Plot of (a) positive-sequence and (b) negative-sequence impedances for relays on two sides of power transformer for B-g external fault in the 230 KV winding (location 5, Figure 4.1).                 | 162         |

| Figure E.2. | Plot of (c) trip counters for relays on two sides of power transformer for B-g external fault on 230 KV side (location 5, Figure 4.1).                                                                 | 163         |

| Figure E.3. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for a three-phase external fault on the 230 kV side of the power transformer (location 5, Figure 4.1).       | 164         |

| Figure E.3. | Plot of (c) trip counters for three-phase external fault on 230 KV side of the power transformer (location 5, Figure 4.1).                                                                             | 165         |

| Figure E.4. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-Phase C internal fault in the 13.8 kV winding of the power transformer (location 2, Figure 4.1). | 160         |

| Figure E.4. | Plot of (c) trip counters for Phase A-Phase C internal fault on 13.8 KV winding of the power transformer (location 2, Figure 4.1).                                                                     | 167         |

| Figure E.5. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-Phase C external fault on the 13.8 kV side of the power transformer (location 1, Figure 4.1).    | 168         |

| Figure E.5. | Plot of (c) trip counters for Phase A-Phase C external fault on 13.8 KV side of the power transformer (location 1, Figure 4.1).                                                                        | 169         |

| Figure E.6. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-ground internal fault on the 230 kV winding of the power transformer (location 3, Figure 4.1).   | 170         |

| Figure E.6. | Plot of (c) trip counters for Phase A-g internal fault in 13.8 KV winding of the power transformer (location 3, Figure 4.1).                                                                           | <b>17</b> 1 |

| Figure E.7. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-ground internal fault on the 230 kV side of the unloaded transformer (location B, Figure 3.6).   | 172         |

| Figure E.7. | Plot of (c) trip counters for a Phase A-ground internal fault on 230 kV side of the unloaded transformer (location B, Figure 3.6).                                                                     | 173         |

| Figure E.8. | Plot of (a) positive-sequence and (b) negative-sequence impedances                                                                                                                                     | 174         |

|              | computed by the relays for a three-phase external fault on the 230 kV side of the unloaded transformer (location A, Figure 3.6).                                                                       |     |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure E.8.  | Plot of (c) trip counters for a three-phase external fault on 230 kV side of the unloaded transformer (location A, Figure 3.6).                                                                        | 175 |

| Figure E.9.  | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for a three-phase external fault on the 13.8 kV side of the unloaded transformer.                            | 176 |

| Figure E.9.  | Plot of (c) trip counters for a three-phase external fault on 13.8 kV side of the unloaded transformer.                                                                                                | 177 |

| Figure E.10. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase A-Phase B external fault on the 230 kV side of the power transformer (location 5, Figure 4.1).     | 178 |

| Figure E.10. | Plot of (c) trip counters for a high-impedance Phase A-Phase B external fault on 230 KV side of the power transformer (location 5, Figure 4.1).                                                        | 179 |

| Figure E.11. | Plot of (a) positive-sequence and (b) negative-sequence impedances computed by the relays for Phase B-Phase C internal fault in the 13.8 kV winding of the power transformer (location 2, Figure 4.1). | 180 |

| Figure E.11. | Plot of (c) trip counters for a high-impedance Phase B-Phase C external fault on the 13.8 KV side of the power transformer (location 2, Figure 4.1).                                                   | 181 |

| Figure E.12. | Plot of (a) positive-sequence impedance computed by the relays and (b) trip counters for Phase B-Phase C switch-on external fault for the power transformer (location A, Figure 3.14).                 | 182 |

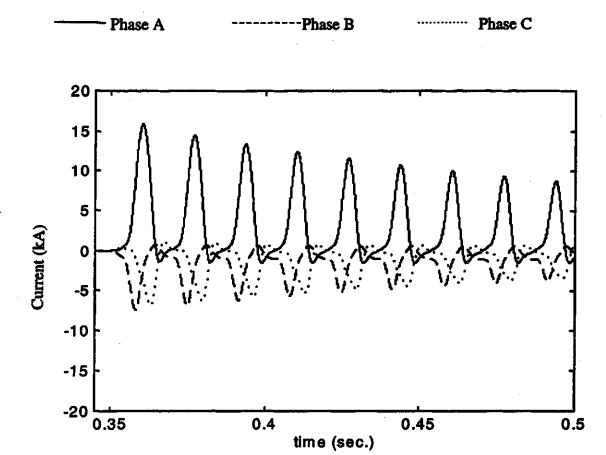

| Figure E.13. | Current waveforms on 13.8 KV side of the power transformer for magnetizing inrush condition (transformer switched-on at 0.35 seconds)                                                                  | 183 |

# **List of Symbols**

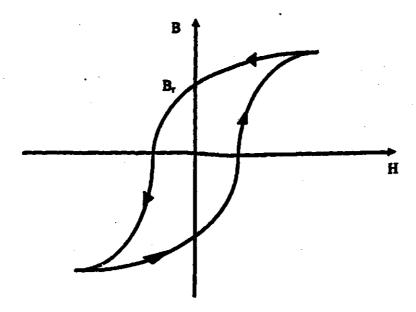

| В                         | Magnetic flux density                                                               |

|---------------------------|-------------------------------------------------------------------------------------|

| $\mathbf{B_r}$            | Remanent flux density                                                               |

| H                         | Magnetic flux intensity                                                             |

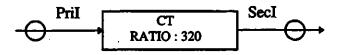

| CT                        | Current transformer                                                                 |

| $Z_{t1}$                  | Positive-sequence impedance of the power transformer                                |

| $Z_{t2}$                  | Negative-sequence impedance of the power transformer                                |

| $Z_{gx1}$                 | Positive-sequence impedance of the generator G <sub>x</sub>                         |

| $Z_{gx2}$                 | Negative-sequence impedance of the generator G <sub>x</sub>                         |

| $Z_{gy1}$                 | Positive-sequence impedance of the generator Gy                                     |

| $Z_{gy2}$                 | Negative-sequence impedance of the generator Gy                                     |

| $Z_{L1}$                  | Positive-sequence impedance of the transmission line                                |

| $Z_{L2}$                  | Negative-sequence impedance of the transmission line                                |

| m                         | constant which defines the fault location in the transformer, 0 <m<1< td=""></m<1<> |

| $\mathbf{K}_{\mathbf{a}}$ | Voltage-ratio of secondary to primary voltage of phase A in the power               |

|                           | transformer                                                                         |

| $K_b$                     | Voltage-ratio of secondary to primary voltage of phase B in the power               |

|                           | transformer                                                                         |

| $K_c$                     | Voltage-ratio of secondary to primary voltage of phase C in the power               |

|                           | transformer                                                                         |

| R, X                      | Resistive and reactive components of the impedance respectively                     |

| a                         | Phasor operator                                                                     |

### 1. INTRODUCTION

#### 1.1. Background

An electric power system consists of four major divisions: generation, transmission, distribution, and utilization. An electric utility generates, transmits and distributes energy to a variety of consumers.

Since power systems are spread over vast territories and comprise of large number of components, the probabilities of component failure, abnormalities and faults are significant. Occurrence of faults can cause damage to the equipment and injury to personnel resulting in substantial monetary losses to utilities and consumers.

Each system element should, therefore, be protected from damage due to faults and adverse operating conditions. Protective relays, which activate trip circuits of circuit breakers for isolating the faulted components from the rest of the power systems, are used for this purpose.

# 1.2. Protection of power systems

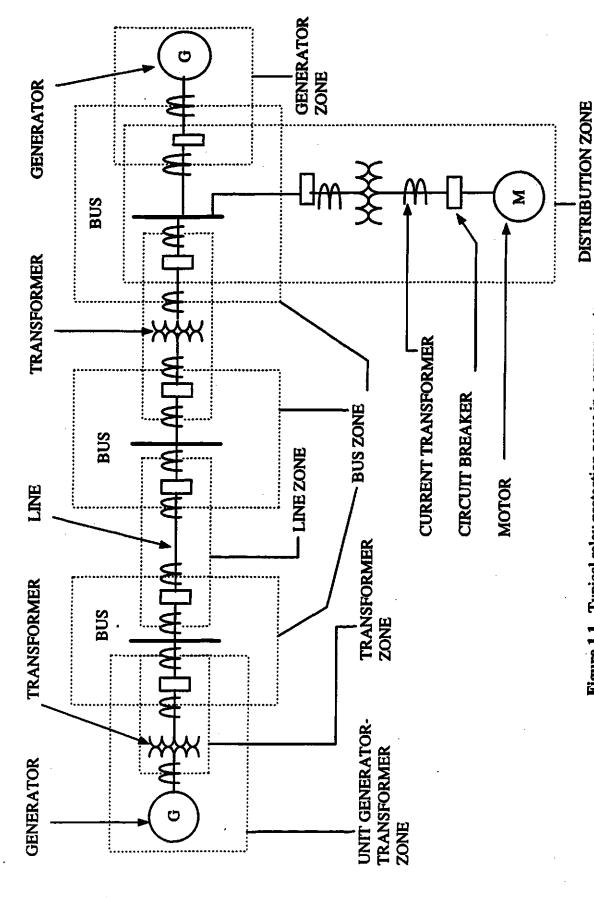

The major function of protective devices is to detect the occurrence of faults and to isolate the faulted sections from the rest of the power system. A power system is divided into protection zones, as shown in Figure 1.1, to achieve the intended objective. Each zone usually includes one major element and is protected by using a set of protective relays [1]. The protective relays, responsible for protecting a zone, operate and disconnect the zone from the remaining system when a fault occurs. The relays also alert operators and start equipment for recording the waveforms of system currents and voltages.

Figure 1.1. Typical relay protection zones in a power system.

Adjacent zones overlap to ensure that no part of the power system is left unprotected. Back-up relays are also provided to ensure isolation of the faulted equipment in case the primary relays fail to operate. The back-up relays usually operate after a time-delay and isolate not only the faulted zone but also the adjoining zone(s).

Fuses were used as protective devices in the early developments of power systems. They were, and are still, in use for protection purposes. Fuses are effective and inexpensive but have inherent disadvantages, such as their inability to discriminate between supply and load side faults and to restore the circuit after the fault is cleared. Moreover, they need replacement after each operation.

Development of electromechanical relays provided a significant improvement in the protection of power systems. The relays provided means for controlling the operating times and ability to reclose the circuits. This improved the sensitivity and selectivity of the protection schemes.

Solid state relays were introduced in early 1950s. These relays were not initially accepted by the users because of the their inadequate designs and high failure rates of electronic components. Later developments utilized newer semiconductor technology and introduced improved designs. Several kinds of solid state and electromechanical relays are being used in power systems today [2]. Recent advances in the very large scale integrated circuits have led to the development of microprocessors and data acquisition chips. These have resulted in the development of digital relays.

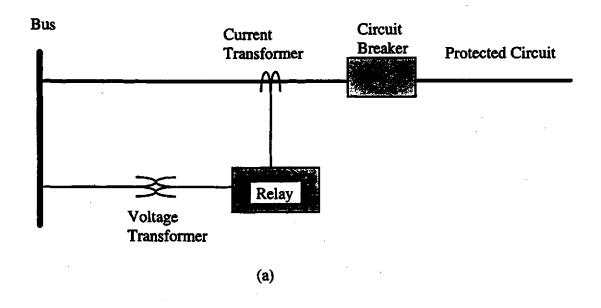

Relays energize trip circuits which result in the opening of circuit breakers. The single-line diagram of a typical relay set up is shown in Figure 1.2(a). The functional block diagram of the dc trip circuit, used for opening the circuit breaker, is shown in Figure 1.2(b). The relay senses the system voltages and currents through voltage and current transformers respectively. The protective relay senses the occurrence of a fault and activates the trip relay which, in turn, closes the breaker contact (CS). This energizes

Legend CS -- Contactor switch

52T-- breaker trip coil

Figure 1.2. (a) Single-line diagram of a protective relay arrangement (b) DC trip circuit.

the breaker coil (52T) and opens the circuit breaker to disconnect the faulted section from the rest of the power system.

## 1.3. A digital relay

A digital relay is a microprocessor-based device that uses software to process quantized signals for implementing the relay logic. Most of the research in the area of digital protection relates to the development of algorithms for specific applications.

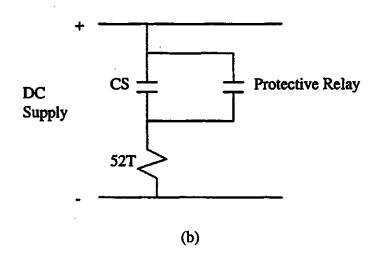

The block diagram of a typical digital relay is shown in Figure 1.3. The relay can be divided into analog input, digital input and digital output subsystems, and a microcomputer.

The input to a digital relay consists of analog and digital signals derived from the power system. The analog signals, system voltages and currents, stepped down to appropriate levels are applied to the analog input subsystem. The outputs from the subsystem are fed to the analog interface of the microcomputer.

The digital input subsystem receives the status of circuit breakers and isolators. Isolation circuitry and transient protection is used in analog and digital input subsystems for preventing the relay from system transients. The outputs are provided through digital output subsystem.

The microcomputer, in a digital relay, consists of a central processing unit, non-volatile memory (ROM), random access memory (RAM), analog interface, and communications hardware and appropriate software. The voltages and currents are sampled and quantized, and are fed into the microcomputer. In most digital relaying applications, the data samples complete with time stamps are stored in a RAM. These are transferred to permanent memory storage (local or remote) as soon as possible. A nonvolatile memory, ROM, is used for storing relay programs and settings. The relay logic is executed in the central processing unit.

Figure 1.3. Functional block diagram of a digital relay.

Communication links are provided to share information with other devices. A self-diagnosis software resides in the relay and checks the relay state repeatedly. This feature allows the relay to remove itself from service when a malfunction (component failure) occurs and to alert the control center. Digital relays are usually powered from the station battery which is provided with a battery charger. This ensures relay operation during outages of the station ac supply.

A digital relay can perform as well as or better than its electromechanical and solid-state counterparts. A digital relay is continuously active and self-diagnosis routines are repeatedly carried out to detect failures to allow timely corrective actions. This makes digital relays more reliable than their electromechanical and solid-state counterparts. Additional diagnostic features to monitor peripherals are also implemented to further improve the reliability. Functions of a digital relay can be changed simply by changing the relay software, therefore, allowing the use of a common hardware platform. Also, the relay settings can be changed using communication interface. Moreover, flow of input data in the relay hardware can be changed through different routes under program control when trouble arises in normal input paths. This makes a digital relay more flexible and reliable in operation.

A digital relay can store fault data which can be used for diagnosis purposes and system improvements. Fault locations can be calculated from the stored data making it easier for the maintenance staff to carry out repairs.

# 1.4. Objective of the research

Transformer differential protection is adversely affected by phenomena, such as magnetizing inrush, current transformer (ct) ratio-mismatch and ct saturation. A literature survey revealed that most of the work on transformer protection using digital relays had concentrated on the development of algorithms to discriminate between magnetizing inrush, external faults and internal faults. No concerted effort seems to have been made to address the problem of ct ratio-mismatch and ct saturation.

The objective of this research was to develop a microprocessor based technique which can detect faults and determine if they are inside or outside the protection zone of a transformer. Moreover, the performance of the technique should not be affected by magnetizing inrush, ct saturation and ct ratio-mismatch.

#### 1.5. Outline of the thesis

The thesis is organized in five chapters and five appendices. The first chapter introduces the subject of the thesis and describes its organization. It also presents a brief historical background of protective relays, their role in power systems, and an introduction to digital relays.

Chapter 2 gives an overview of the conventionally used differential protection scheme and outlines its limitations. An introduction to the percentage-bias and harmonic restraint principles is provided. A brief review of the previously proposed digital algorithms for power transformer protection is included and their pertinent characteristics are discussed.

The proposed fault-detection technique is developed in Chapter 3. An algorithm based on the technique is presented and the procedural steps involved in the algorithm are illustrated using a flow chart. The chapter also includes the study of the effects of ct ratio-mismatch and ct saturation on the proposed technique. A theoretical basis, describing the impact of ct saturation on the proposed technique, is developed. The chapter also proposes criteria for detecting faults when a transformer is switched on and when a transformer secondary is not connected to a load or system.

Chapter 4 describes system modeling and data processing steps that are used for evaluating the performance of the proposed technique. The electromagnetic transient simulation package, EMTDC, was used to generate simulation data. Results obtained using the simulated data for different type of faults are presented and discussed. The

impacts of ct ratio-mismatch and ct saturation are also studied and selected cases are presented.

Appendix A outlines the concept of symmetrical components, used for analyzing an unbalanced three-phase system by transforming it into a set of balanced networks. These networks, called sequence-networks, are briefly defined in this appendix. An introduction to the EMTDC and current transformer model used in the simulations is given in Appendix B. Appendix C lists the parameters of the power transformer and other components of the power system model used for generating simulation data. The design and frequency response of the anti-aliasing filters, used for off-line processing of the data, are presented in Appendix D. Appendix E includes additional test results which demonstrates the usefulness of the proposed technique.

The specific contributions made by this thesis are as follows.

- 1. An improved technique for protecting transformers has been developed. The technique is described in Chapter 3.

- 2. A digital algorithm based on the proposed technique is also reported in Chapter 3.

- 3. A theoretical analysis showing the effect of ct saturation on the proposed technique has been carried out. This is presented in Chapter 3 and verified by the test results given in Chapter 4. The effect of ct ratio-mismatch on the proposed technique is studied. The stable performance provided by the technique under such condition is shown by test results given in Chapter 4.

- 4. A criteria to detect faults occurring during switch-on and unloaded operation of the transformer are also developed. They are described in Chapter 3 and the performance results are included in Chapter 4.

## 1.6. Summary

This chapter has presented a brief introduction to the concepts of power system protection. The development of protective devices from fuses to the present day digital relays has been described. Block diagram of a typical digital relay and advantages of digital relays have also been outlined.

Most of the previously proposed algorithms for protecting transformers are based on the principle of differential protection. Some of these algorithms are reviewed in Chapter 2.

### 2. DIFFERENTIAL PROTECTION

Differential protection is conventionally used for protecting most power transformers and generators. During the last five years, differential protection of transmission lines has also become a viable technique. As the protection of each component of the power system is considered, differential protection is invariably a prime candidate, and is often selected to provide primary protection [1].

The differential protection technique applied to power transformers is discussed in this chapter. Its fundamental principle and limitations are examined. Special features, incorporated in differential relays, to prevent misoperations are briefly discussed. Digital algorithms, proposed in the past, for protection of power transformers are reviewed. This is followed by a discussion of the previously proposed algorithms.

# 2.1. The differential principle

The differential principle, as applied for protecting power transformers, can be described with the help of Figure 2.1. The levels of currents on the primary and secondary sides of the power transformer are reduced by the cts. The outputs of these cts are compared. The ratios of primary and secondary cts are selected such that each ct produces the same secondary current for nominal line currents. The operating coil of the relay is connected to secondary windings of two cts in such a way that the net current flowing through it equals the difference between the secondary currents of cts provided on the two sides of the power transformer. Net current through the operating coil of differential relay is zero for normal operation and external faults. An internal fault in the power transformer upsets this balance and causes a current to flow in the relay's operating coil. This is shown in Figure 2.1(b).

Figure 2.1. Basic differential scheme for (a) no-fault and (b) internal fault conditions of a power transformer.

An internal fault is not the only cause for the presence of differential currents. A small amount of current normally flows in the operating element because of current needed to magnetize the core, mismatch of cts ratios and differences in characteristics of the cts. Large amounts of currents in the operating elements are experienced due to ct saturation and magnetizing inrush. These phenomena are described briefly in the following section.

### 2.2. Problems with differential protection

As pointed out in the preceding section, the net current through the operating element of a differential relay is never zero. Non-linear phenomena such as magnetizing inrush and ct saturation are experienced which results in operating current in the differential relay even when there is no fault in the protection zone. These phenomena are described in the following sections.

#### 2.2.1. Ratio-mismatch

Most power transformers are equipped with on-load tap changers which operate to change the turns ratio between the primary and secondary sides of the transformer as the system operating conditions change. Since the ct ratios are selected to match the transformer operation at its nominal tap setting, the operation of the tap-changer disturbs the balance between the outputs of the primary and secondary side cts and, consequently, causes currents to flow in the operating element of the differential relay.

To avoid tripping due to ratio mismatch, differential relays are provided with a percentage-bias feature which is described in Section 2.3.

#### 2.2.2. Difference in current transformer characteristics and burdens

The primary and secondary current transformers (ct's) used for differential protection of power transformers are designed for operation at different voltage levels. Their characteristics are, therefore, difficult to match over their entire range of operation. Also, the length of the leads connecting the primary and secondary cts to the relay

cannot be exactly equal. The VA burdens on the cts are, therefore, unequal. This causes cts to produce different outputs for the same levels of input currents. The consequences is that some current flows in the operating element of the differential relay during through faults.

#### 2.2.3. Current transformer saturation

The current transformer (ct) is a basic component in any relaying scheme. The primary winding of a ct is in series with the line and, therefore must carry the current that may happen to flow in the line. When a short-circuit occurs on the line, the line current becomes large which also flows in the ct primary. The secondary current also increases. Ideally, the secondary current should be proportional to the primary current and the ct must develop sufficient voltage to make this current flow in the secondary circuit. To generate this voltage, part of the primary current becomes the magnetizing current that produces flux in the core of the ct. Normally, the magnetizing current is small and the secondary current remains proportional to the primary current for all practical purposes. If the ct has to develop large voltage to overcome the voltage drop in the secondary circuit, the core flux levels must be high. If the flux approaches the saturation level, the exciting current becomes large and the secondary current does not increase proportionally. As the primary current increases beyond the saturation level, the core saturates during a part of the cycle [3]. The magnetizing current is large when the core is saturated. Consequently the secondary current out of ct is less than its level had the ct not saturated. The result is that the secondary current becomes distorted.

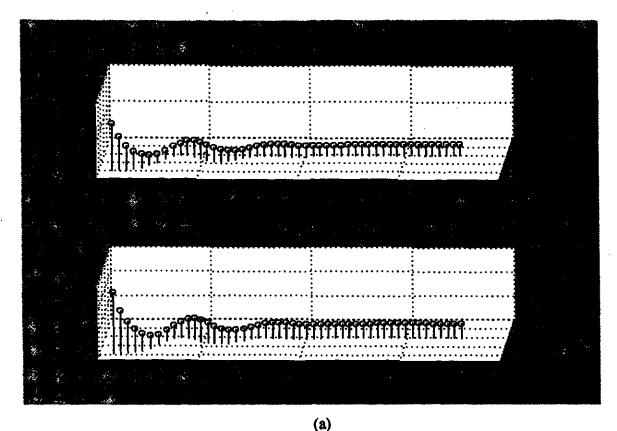

Figures 2.2 (a), (b) and (c) show the waveforms of ct primary current and the corresponding secondary currents for mild and severe ct saturation conditions respectively. Inductance in the burden (load connected to the ct) results in a more gradual drop-off, while a lower burden reduces the distortion of the secondary current. Since the cts used in differential protection schemes are in series with the line, they carry large amounts of currents during internal and external faults. A high level of current can cause

one or more ct(s) to saturate resulting in different secondary currents out of the cts which would have been otherwise equal.

Figure 2.2. Current waveforms of ct's (a) primary current, and secondary currents for (b) mild and (c) severe ct saturation states.

This results in the flow of a differential current in the operating element of the relay even when the fault is outside the protection zone. Saturation of cts can cause the differential relays to operate during external faults and, therefore, steps must be taken to detect ct saturation and prevent the relay operation when it is necessary.

# 2.2.4. Magnetizing inrush

When a transformer is switched-on at a time when the normal steady-state flux should be different than that existing in the transformer core, magnetizing inrush currents occur [1]. The magnitude of the inrush currents can be several times the rated full-load current of the transformer. The factors controlling the magnitude and duration of the magnetizing inrush currents include the rating of the transformer, size of the power system it is connected to, resistance of the circuit from the source to the transformer, type of iron used to form the core and the level of the residual flux. The phenomenon of magnetizing inrush is random. It depends on the residual flux in the transformer core and the instant at which the voltage is applied to energize the transformer.

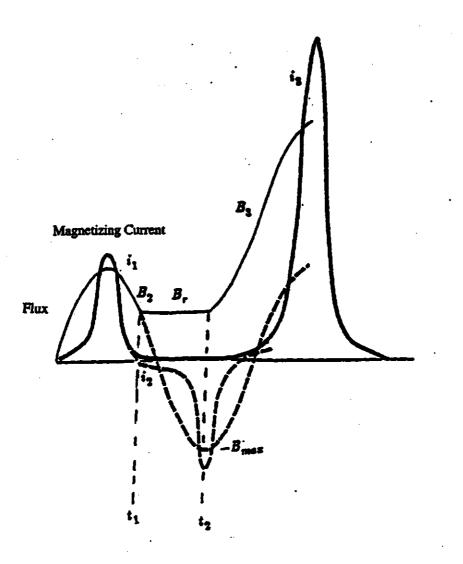

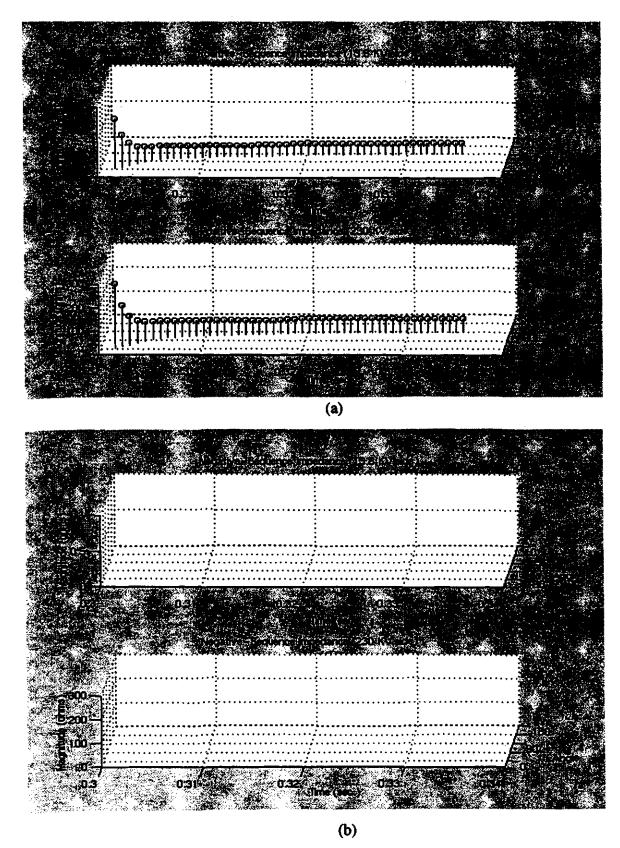

Consider the magnetizing curve of a transformer core shown in Figure 2.3. When power to the transformer is switched off at time  $t=t_1$ , the magnetizing current traces the hystersis loop to zero. The flux at that time is  $+B_r$ , which is now the remanent flux. If the transformer were not switched off, the magnetizing current  $(i_1)$  and the flux density  $(B_2)$  would have followed the dashed curves as shown in Figure 2.4 [4]. Assuming that the transformer is re-energized at time instant  $t=t_2$ , when the normal value of flux density would have been  $-B_{max}$ . Since the magnetic flux inside the transformer core cannot change instantaneously, the flux density starts at  $B_r$  and traces the curve  $B_3$  instead of starting at the normal value of  $-B_{max}$ . This curve is a sinusoid riding a dc offset. The transformer core saturates. To provide the high value of flux density  $(B_3)$ , a large magnetizing current is required which is drawn from the source. The current corresponding to the flux density  $B_3$ , is shown as  $i_3$  in Figure 2.4. This current is substantially greater than the normal magnetizing current  $i_1$ , also shown in Figure 2.4.

Maximum inrush does not occur every time the transformer is energized because

Figure 2.3. Magnetizing curve for a transformer core.

Figure 2.4. Magnetizing inrush phenomenon in a power transformer.

the probability is low for energizing at zero crossing point of the voltage waveform. Energizing at maximum voltage does not produce an inrush if there is no residual flux. If a transformer is energized at an instant of the voltage waveform which corresponds to the residual flux density in the core, the process of switching-in becomes a smooth continuation of the previous operation and does not cause any magnetizing inrush. In a three-phase transformer, the inrush will vary appreciably in the three phases and its magnitude will be different in different phases.

The waveform of the magnetizing inrush current is not sinusoidal. It is distorted due to core saturation and interphase coupling. Since the inrush currents flow in the primary windings of a transformer, they are interpreted as internal faults by differential relays.

To prevent differential relay from operating during magnetizing inrush, harmonic restraint is incorporated in the relays.

# 2.3. Percentage-bias and harmonic-restraint

The phenomena that affect the operation of a differential relay are reviewed in the previous section. The percentage-bias and harmonic restraint features are used to prevent differential relays from operating during magnetizing inrush and external faults.

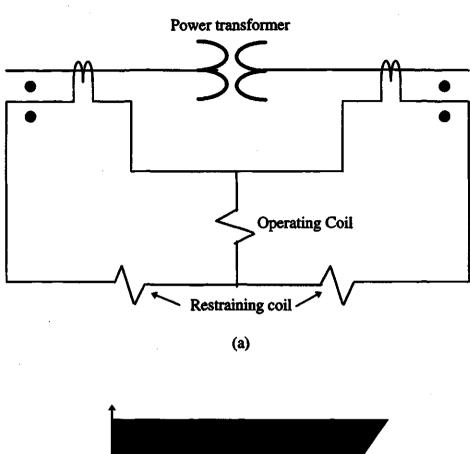

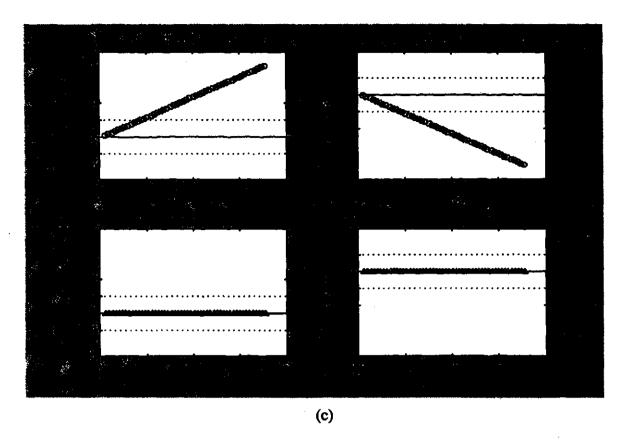

A percentage-bias differential relay has two restraining windings as shown in Figure 2.5(a). Currents in the operating windings of a differential relay are equal to the differences between the currents in primary and secondary side cts. The restraint is proportional to the sum of ct currents. The differential current required to operate the relay must exceed a set percentage of the total restraint. The ratio of the operating current and restraining current expressed as a percentage is usually called the slope of the relay characteristic. A typical percentage-bias characteristic is shown in Figure 2.5(b). The slope is adjustable and can be made large enough to prevent the relay from operating due

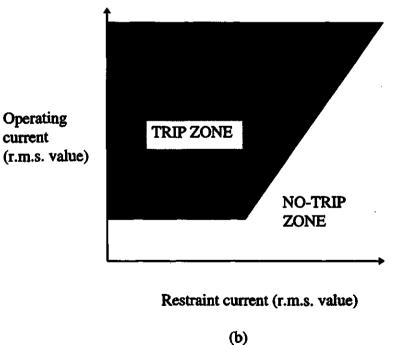

Figure 2.5. Percentage-bias differential relay (a) circuit and (b) characteristics.

to inaccuracies of the cts and off-nominal taps of transformers. The differential current due to ct ratio mismatch is countered by the restraining current and the relay is restrained from operating improperly [5]. This feature increases the security of the relay while it keeps its sensitivity at a reasonable level.

Analysis of typical inrush currents indicate that the second harmonic current is predominant in these currents [6]. This component is extracted from the differential currents using frequency selective circuits and is used to restrain the operation of transformer differential relays. The basic purpose of using the harmonic restraint feature is to restrain the relay for all levels of magnetizing inrush but permit operation for internal faults.

## 2.4. Digital algorithms for transformer protection

The digital algorithms proposed for transformer protection can be broadly divided into the following categories:

- 1. Waveshape identification technique

- 2. Harmonic restraint algorithms

- 3. Model-based algorithms

These algorithms are briefly described in this section.

# 2.4.1. Waveshape identification technique

Substantial differential currents flow in the operating coil of a differential relay on the occurrence of an internal fault. However, as described before, magnetizing inrush, ct ratio mismatch and differences in ct characteristics also result in differential currents which do not represent actual faults in the protected zone. Rockefeller [7] suggested that the magnetizing inrush currents can be identified by monitoring the time duration between successive peaks of the currents. The two successive peaks of a magnetizing inrush current are either 4 or 16 ms apart whereas the successive peaks of a

fundamental frequency fault current occur at an interval of 7.5 to 10 ms. Also, the peak value of a fault current is within 75 to 125 percent of its previous peak and is of the opposite sign. Rockefeller, therefore, suggested the use of current waveshapes for identifying the inrush phenomenon.

# 2.4.2. Harmonic-restraint algorithms

These algorithms use harmonic components of the differential currents to restrain the relay during magnetizing inrush. As described earlier, unlike fault currents, magnetizing inrush currents contain large proportions of second harmonic frequency components. This fact is used in developing harmonic restraint algorithms. Digital differential relays sample the currents at regular intervals of time and calculate the peak values of their fundamental frequency and harmonic components. If the second harmonic component in a differential current exceeds a pre-specified percentage of its fundamental frequency component, it is concluded that magnetizing inrush is being experienced. The algorithms using the harmonic restraint principle utilize different techniques to estimate the magnitudes of the fundamental and harmonic frequency components of the currents. Some of the filtering techniques are briefly described in the following sections.

# 2.4.2.1. Least error squares technique

Sachdev and Baribeau [8] described the Least Error Squares (LES) approach for developing a digital filter which explicitly takes account of the decaying d.c. components in the system voltages and currents. This curve-fitting technique is based on minimizing the mean-square error between the actual and assumed waveforms. The technique uses the coefficients of the designed filter to compute the real and imaginary components of the voltage and current phasors.

In designing the LES filter, it is assumed that the power system currents and voltages are composed of an exponentially decaying dc component, a fundamental frequency component and components of a few harmonics.

Consider that the waveform of a voltage can be modeled as

$$v(t) = A_0 e^{-t/\tau} + \sum_{n=1}^{N} A_n \sin(n\omega_0 t + \theta_n).$$

(2.1)

where:

v(t) is the instantaneous value of the voltage at any time t,

τ is the time constant of the decaying dc component,

N is the highest order harmonic component present in the voltage,

$\omega_0$  is the fundamental frequency of system in radians/seconds,

$A_0$  is the initial value of the dc offset at time t=0,

$A_n$  is the peak value of the  $n^{th}$  harmonic component, and

$\theta_n$  is the phase angle of the  $n^{th}$  harmonic component.

The Taylor series expansion for the decaying dc component gives

$$e^{(-t/\tau)} = 1 - \left(\frac{t}{\tau}\right) + \left(\frac{1}{2}\right)\left(\frac{t}{\tau}\right)^2 - \left(\frac{1}{6}\right)\left(\frac{t}{\tau}\right)^3 + \dots$$

Applying the trigonometric identity  $\sin(A+B)=\sin A\cos B+\cos A\sin B$  and using the first two terms of the Taylor series expansion of the decaying dc component, Equation (2.1) becomes

$$\mathbf{v}(t) = \mathbf{A}_0 - \left(\frac{\mathbf{A}_0}{\tau}\right) t + \sum_{n=1}^{N} \mathbf{A}_n \left[\sin(n\omega_0 t)\cos\theta_n + \cos(n\omega_0 t)\sin\theta_n\right]. \tag{2.2}$$

If the fourth and higher order harmonics are assumed to be removed by the anti-aliasing filter, and  $t = t_1$ , Equation (2.2) becomes

$$v(t_1) = A_0 - \left(\frac{A_0}{\tau}\right) t_1 + (A_1 \cos \theta_1) \sin(\omega_0 t_1) + (A_1 \sin \theta_1) \cos(\omega_0 t_1) +$$

$$(A_2 \cos \theta_2) \sin(2\omega_0 t_1) + (A_2 \sin \theta_2) \cos(2\omega_0 t_1) + (A_3 \cos \theta_3) \sin(3\omega_0 t_1) + (A_3 \sin \theta_3) \cos(3\omega_0 t_1).$$

(2.3)

This equation can be expressed as

$$v(t_1) = a_{11}x_1 + a_{12}x_2 + a_{13}x_3 + a_{14}x_4 + a_{15}x_5 + a_{16}x_6 + a_{17}x_7 + a_{18}x_8.$$

(2.4)

where:

$$x_1 = A_0$$

,  $x_2 = -\left(\frac{A_0}{\tau}\right)$ ,  $x_3 = A_1 \cos \theta_1$ ,  $x_4 = A_1 \sin \theta_1$ ,  $x_5 = A_2 \cos \theta_2$ ,  $x_6 = A_2 \sin \theta_2$ ,

$$x_7 = A_3 \cos \theta_3$$

,  $x_8 = A_3 \sin \theta_3$ , and

$$\begin{aligned} a_{11} &= 1, \ a_{12} = t_1, \ a_{13} = \sin(\omega_0 t_1), \ a_{14} = \cos(\omega_0 t_1), \ a_{15} = \sin(2\omega_0 t_1), \ a_{16} = \cos(2\omega_0 t_1), \\ a_{17} &= \sin(3\omega_0 t_1), \ a_{18} = \cos(3\omega_0 t_1). \end{aligned}$$

The voltage signal is sampled at intervals of  $\Delta t$  s. Equation (2.4) can be rewritten in the following form by substituting  $t_1 = \Delta t$ ,  $2\Delta t$ , ....,  $m\Delta t$  as follows.

$$V(\Delta t) = a_{11}x_1 + a_{12}x_2 + a_{13}x_3 + a_{14}x_4 + a_{15}x_5 + a_{16}x_6 + a_{17}x_7 + a_{18}x_8$$

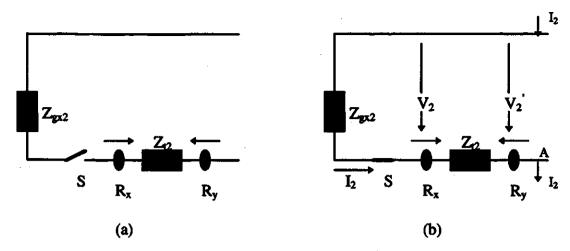

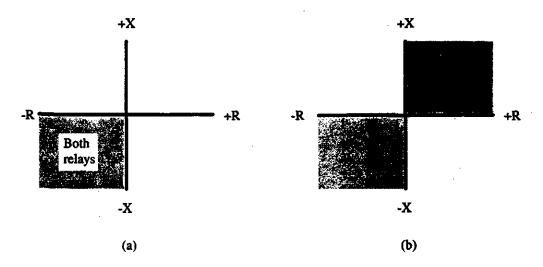

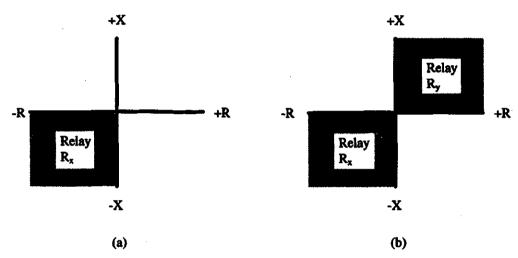

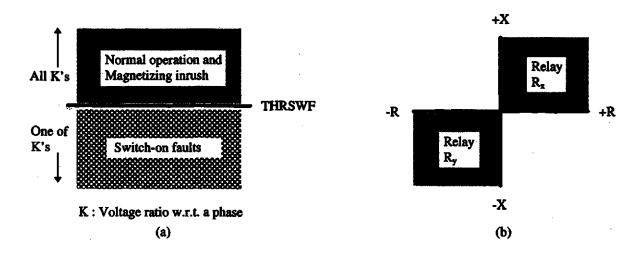

$$v(2\Delta t)=a_{21}x_1+a_{22}x_2+a_{23}x_3+a_{24}x_4+a_{25}x_5+a_{26}x_6+a_{27}x_7+a_{28}x_8$$