# AN EFFICIENT DOCSIS UPSTREAM EQUALIZER

A Thesis Submitted to the College of Graduate Studies and Research in Partial Fulfillment of the Requirements for the Degree of Master of Science in the Department of Electrical and Computer Engineering University of Saskatchewan

> by Md. Mushtafizur Rahman Choudhury

> > Saskatoon, Saskatchewan, Canada

© Copyright Md. Mushtafizur Rahman Choudhury, March, 2014. All rights reserved.

## Permission to Use

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, it is agreed that the Libraries of this University may make it freely available for inspection. Permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professors who supervised this thesis work or, in their absence, by the Head of the Department of Electrical and Computer Engineering or the Dean of the College of Graduate Studies and Research at the University of Saskatchewan. Any copying, publication, or use of this thesis, or parts thereof, for financial gain without the written permission of the author is strictly prohibited. Proper recognition shall be given to the author and to the University of Saskatchewan in any scholarly use which may be made of any material in this thesis.

Request for permission to copy or to make any other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan, Canada S7N 5A9

## Acknowledgments

I would like to express my heartiest gratitude to my supervisor, Professor J. Eric Salt for his guidance and teaching throughout my pursuit of this Industrial Oriented Masters degree. His guidance and encouragement from the very beginning of this IOM program, always kept me on the right track and increased my confidence in doing research independently. My co-supervisor, Professor Ha H. Nguyen has also played an important role throughout the IOM program. I am very happy to have had the opportunity to work with such a wonderful supervisors.

I would also like to thank NSERC and TRLabs for financially supporting in the pursuit of completing the IOM program successfully. Special thanks to Mr. Andrew Kostiuk, head of interactive application services in TRTech, Saskatoon for his guidance, questions and comments in the continuation of research studies for two successive summer terms at TRLabs.

I would like to thank all my colleagues in the IOM program. This includes Rory Gowen, Suresh Kalle and Andy Fontaine, with whom I have enjoyed many constructive discussions and collaborations. I am also grateful to the Department of Electrical and Computer Engineering at University of Saskatchewan for providing high quality education and research environment.

A special thanks to Professor Aryan Saadat Mehr and Dr. Brian Berscheid for being in my M.Sc. thesis advisory committee and Professor Alexandre V. Koustov for being an external examiner. Their constructive criticism, comments and suggestions will be an asset to achieve my future goal.

Finally, I would like to express my gratitude to my parents, Md. Shazidur Rahman Choudhury and Kamrunnesa Choudhury, and my wife Iffath Fathima Chowdhury who have provided tremendous support, encouragement and inspiration over the years.

## Abstract

The advancement in the CATV industry has been remarkable. In the beginning, CATV provided a few television channels. Now it provides a variety of advanced services such as video on demand (VOD), Internet access, Pay-Per-View on demand and interactive TV. These advances have increased the popularity of CATV manyfold. Current improvements focus on interactive services with high quality. These interactive services require more upstream (transmission from customer premises to cable operator premises) channel bandwidth.

The flow of data through the CATV network in both the upstream and downstream directions is governed by a standard referred to as the Data Over Cable Service Interface Specification (DOCSIS) standard. The latest version is DOCSIS 3.1, which was released in January 2014. The previous version, DOCSIS 3.0, was released in 2006.

One component of the upstream communication link is the QAM demodulator. An important component in the QAM demodulator is the equalizer, whose purpose is to remove distortion caused by the imperfect upstream channel as well as the residual timing offset and frequency offset. Most of the timing and frequency offset are corrected by timing and frequency recovery circuits; what remains is referred to as offset.

A DOCSIS receiver, and hence the equalizer within, can be implemented with ASIC or FPGA technology. Implementing an equalizer in an ASIC has a large non-recurring engineering cost, but relatively small per chip production cost. Implementing equalizer in an FPGA has very low non-recurring cost, but a relatively high per chip cost. If the choice technology was based on cost, one would think it would depends only on the volume, but in practice that is not the case. The dominant factor when it comes to profit, is the time-tomarket, which makes FPGA technology the only choice.

The goal of this thesis is to design a cost optimized equalizer for DOCSIS upstream demodulator and implement in an FPGA. With this in mind, an important objective is to establish a relationship between the equalizer's critical parameters and its performance. The parameter-performance relationship that has been established in this study revealed that equalizer step size and length parameters should be 1/64 and approximately 20 to yield a near optimum equalizer when considering the MER-convergence time trade-off.

In the pursuit of the objective another relationship was established that is useful in determining the accuracy of the timing recovery circuit. That relationship establishes the sensitivity both of the MER and convergence time to timing offset.

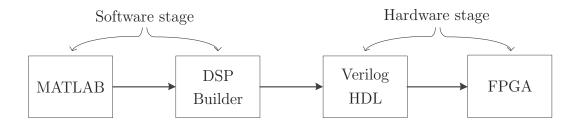

The equalizer algorithm was implemented in a cost effective manner using DSP Builder. The effort to minimize cost was focused on minimizing the number of multipliers. It is shown that the equalizer can be constructed with 8 multipliers when the proposed time sharing algorithm is implemented.

# Table of Contents

| Pe            | ermis  | sion to Use                                       | i    |

|---------------|--------|---------------------------------------------------|------|

| A             | cknov  | wledgments                                        | ii   |

| $\mathbf{A}$  | bstra  | $\operatorname{ct}$                               | iii  |

| Ta            | able o | of Contents                                       | V    |

| $\mathbf{Li}$ | st of  | Tables                                            | viii |

| $\mathbf{Li}$ | st of  | Figures                                           | ix   |

| $\mathbf{Li}$ | st of  | Abbreviations                                     | xiii |

| 1             | Intr   | oduction                                          | 1    |

|               | 1.1    | Evolution of Cable Television                     | 1    |

|               | 1.2    | The Architecture of Cable Networks                | 7    |

|               | 1.3    | DOCSIS Upstream Demodulator                       | 9    |

|               | 1.4    | DOCSIS Upstream Channel                           | 11   |

|               | 1.5    | Statement of Research Problems                    | 13   |

|               | 1.6    | Organization of the Thesis                        | 14   |

| <b>2</b>      | CA     | TV Upstream Channel                               | 15   |

|               | 2.1    | Overview                                          | 15   |

|               | 2.2    | Physical Layer of DOCSIS Upstream Channel         | 15   |

|               |        | 2.2.1 Basic Modulation and Demodulation Technique | 16   |

|               |        | 2.2.2 Channel Impairments                         | 18   |

|          | 2.3 | MAC layer of DOCSIS Upstream Channel                      | 21 |

|----------|-----|-----------------------------------------------------------|----|

| 3        | The | eory of Equalization                                      | 24 |

|          | 3.1 | Least Mean Square Error Equalizer                         | 24 |

|          |     | 3.1.1 System Model                                        | 24 |

|          |     | 3.1.2 Mean Squared Error (MSE) Criterion                  | 29 |

| 4        | DO  | CSIS Equalizer                                            | 47 |

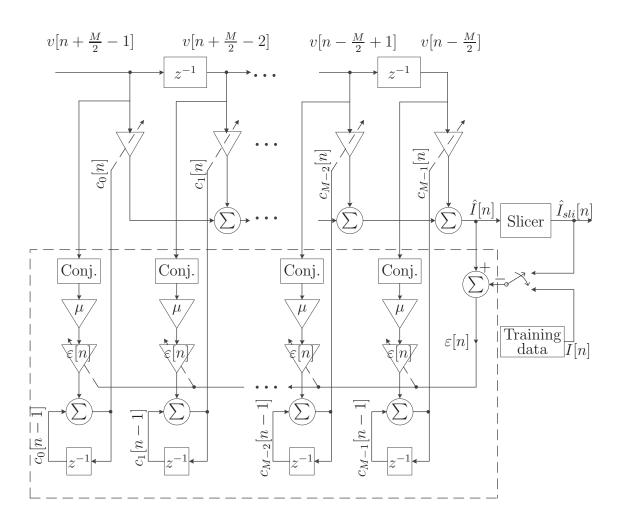

|          | 4.1 | Coefficient Update Algorithm                              | 48 |

|          | 4.2 | LMS Algorithm                                             | 48 |

|          | 4.3 | Structure of the DOCSIS Equalizer in Upstream Demodulator | 55 |

|          |     | 4.3.1 The operating Mode of the Equalizer                 | 57 |

|          | 4.4 | Performance Criterion                                     | 58 |

| <b>5</b> | Imp | elementation of the DOCSIS Equalizer                      | 61 |

|          | 5.1 | Implementation Roadmap                                    | 62 |

|          | 5.2 | Implementation Issues to Find a Cost Effective Equalizer  | 63 |

|          | 5.3 | Effect of Timing Error on Equalizer Performance           | 72 |

|          |     | 5.3.1 Establishing the Timing Reference                   | 73 |

|          | 5.4 | Implementation Structure of the Equalizer                 | 75 |

| 6        | Sim | ulation Results                                           | 80 |

|          | 6.1 | MATLAB Simulation Results                                 | 80 |

|          | 6.2 | DSP Builder Simulation Results                            | 89 |

| 7        | FPO | GA Based Results                                          | 93 |

|    | 7.1   | Equipment Description                                                                 | 93  |

|----|-------|---------------------------------------------------------------------------------------|-----|

|    | 7.2   | Performance of FPGA Implementation                                                    | 97  |

| 8  | Sun   | nmary and Conclusions                                                                 | 101 |

|    | 8.1   | Contribution towards establishing parameters-performance relationship for             |     |

|    |       | the equalizer                                                                         | 101 |

|    | 8.2   | Contributions towards critical issues that affects equalizer performance $\ldots$     | 102 |

|    | 8.3   | Contributions towards cost optimization and implementation $\ldots$ $\ldots$ $\ldots$ | 104 |

| Re | efere | nces                                                                                  | 105 |

# List of Tables

| 1.1 | Versions of DOCSIS standard with the released year and features                                                                     | 9  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | DOCSIS specified echoes with their parameters                                                                                       | 20 |

| 5.1 | Performance measures of a 20 tap equalizer with different step sizes for a threshold of 125% of mean squared error in steady state. | 70 |

# List of Figures

| 1.1 | Bidirectional frequency band in a DOCSIS network                                                                           | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------|----|

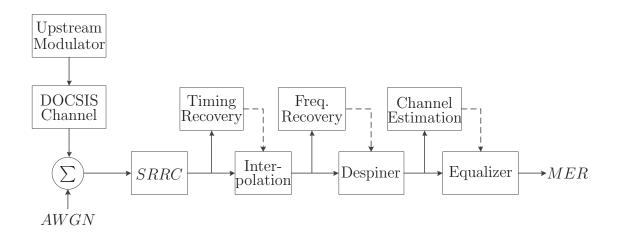

| 1.2 | High-level block diagram of DOCSIS network                                                                                 | 10 |

| 1.3 | High-level block diagram for a DOCSIS 3.0 Upstream Demodulator $\ . \ . \ .$                                               | 10 |

| 1.4 | Process of micro-reflection generation in a cable plant                                                                    | 12 |

| 2.1 | High-level block diagram of DOCSIS upstream communication system $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A}$ | 15 |

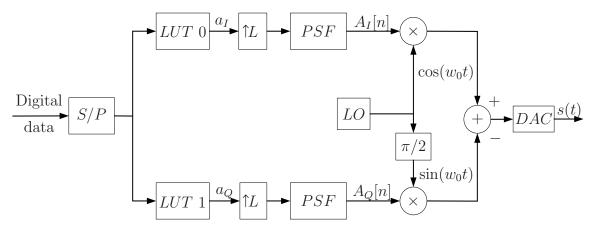

| 2.2 | Basic block diagram of QAM modulator                                                                                       | 16 |

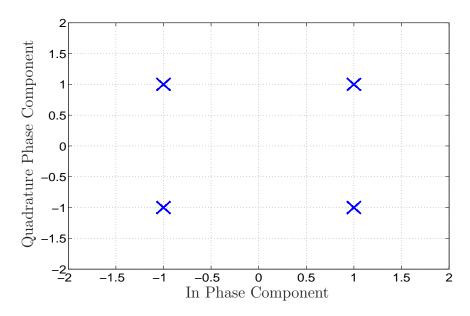

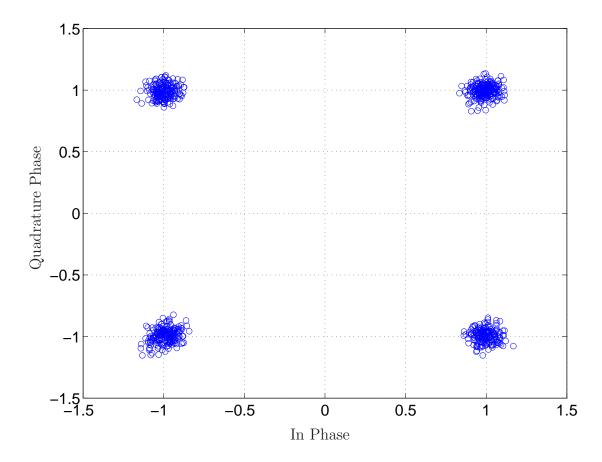

| 2.3 | Constellation diagram for 4-QAM data                                                                                       | 17 |

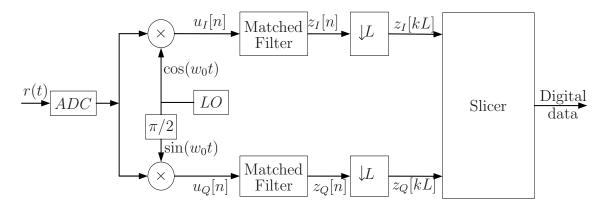

| 2.4 | Basic block diagram of QAM demodulator                                                                                     | 18 |

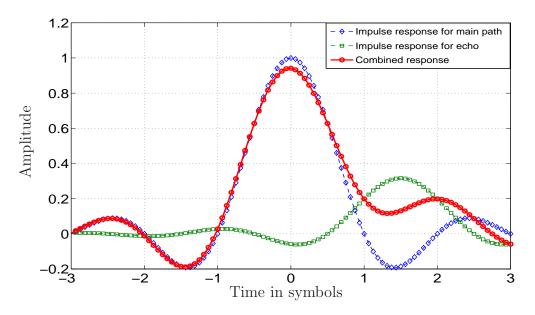

| 2.5 | Impulse response of channel model to illustrate the effect of echo                                                         | 20 |

| 2.6 | Constellation diagram showing the effect of echo                                                                           | 21 |

| 2.7 | Process of ranging mode operation                                                                                          | 22 |

| 3.1 | The Digital Communication System                                                                                           | 25 |

| 3.2 | The Modified Digital Communication System                                                                                  | 27 |

| 3.3 | Generating $h[l]$                                                                                                          | 28 |

| 3.4 | Somewhat Refined System Model                                                                                              | 28 |

| 3.5 | Symbol rate System Model                                                                                                   | 29 |

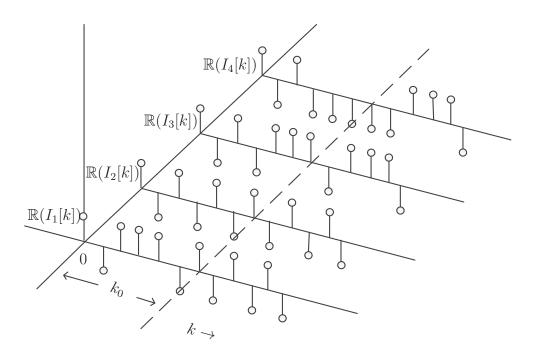

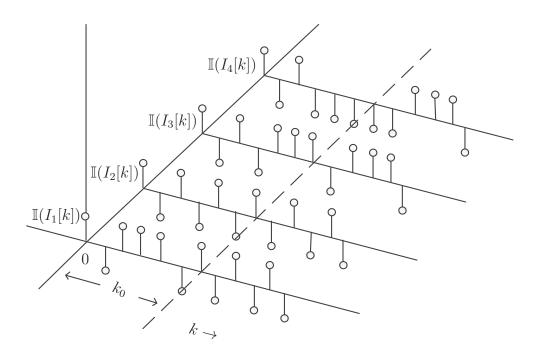

| 3.6 | Real part of four sample functions in stochastic process $I[k]$                                                            | 40 |

| 3.7 | Imaginary part of four sample functions in stochastic process $\boldsymbol{I}[k]$                                          | 41 |

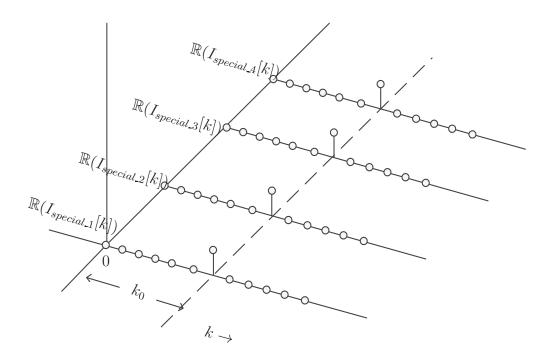

| 3.8 | Real part of four sample functions in stochastic process $I_{special}[k]$                                                  | 42 |

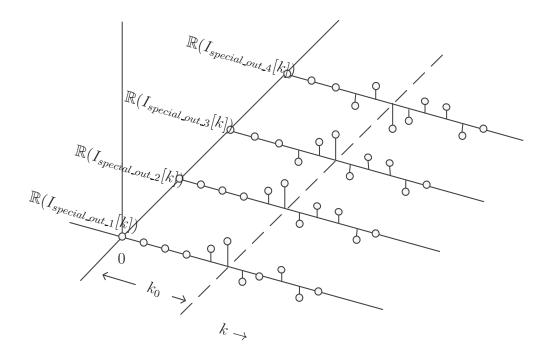

| 3.9 Real part of equalizer output for input $I_{special}[k]$                                                                                                              | 3 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

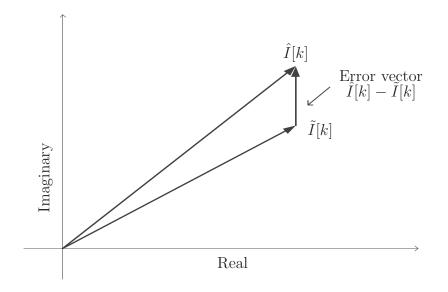

| 3.10 Vectors used in MER $\dots \dots \dots$                              | 1 |

| 4.1 Block diagram of 24 tap symbol-spaced complex adaptive equalizer 56                                                                                                   | 3 |

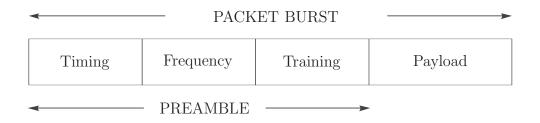

| 4.2 A typical DOCSIS packet burst                                                                                                                                         | 7 |

| 4.3 Block diagram for MER measurement                                                                                                                                     | ) |

| 5.1 A high-level structure of implementation roadmap. $\dots \dots \dots$ | } |

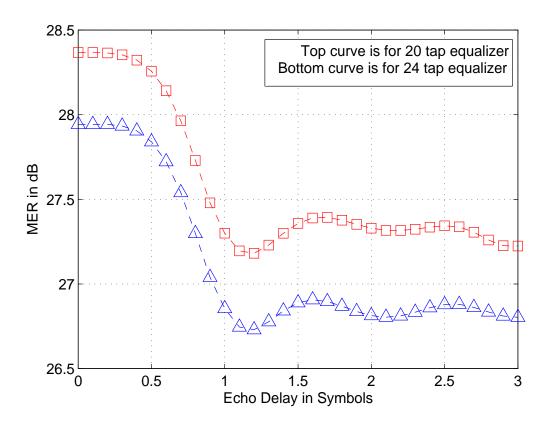

| 5.2 MER comparison in a DOCSIS single echo channel with echo strength 0.3162                                                                                              |   |

| of main path and a step size of $\mu = \frac{1}{64}$ in a 20 and 24 tap equalizers                                                                                        | ) |

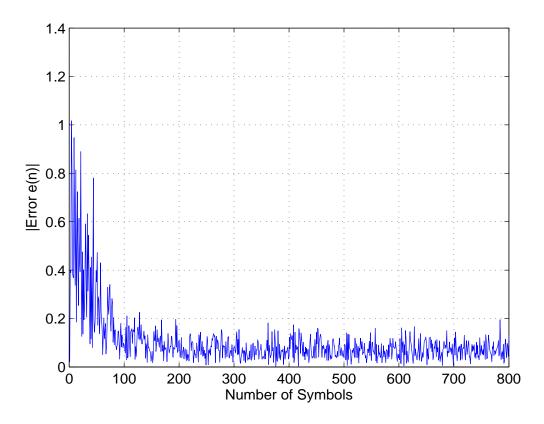

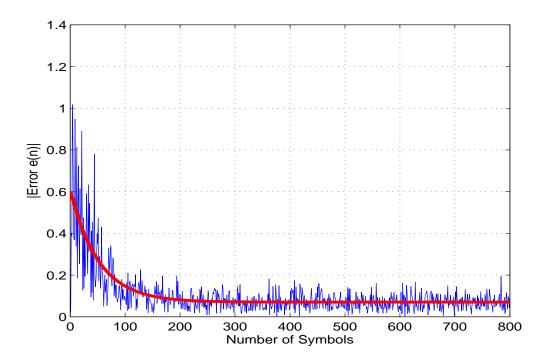

| 5.3 Equalizer error in a 20 tap equalizer with step size, $\mu = \frac{1}{64}$                                                                                            | 3 |

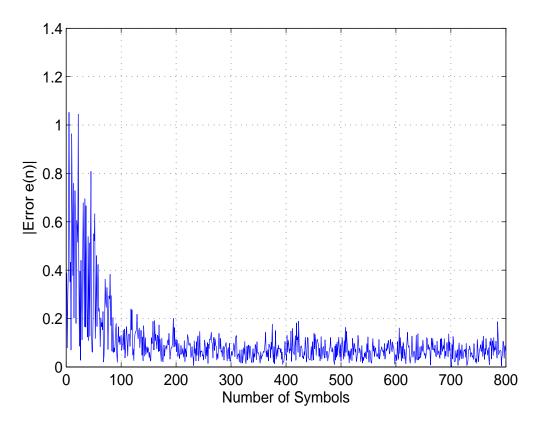

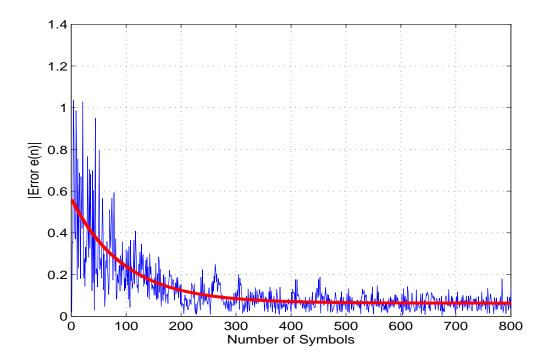

| 5.4 Equalizer error in a 24 tap equalizer with step size, $\mu = \frac{1}{64}$                                                                                            | 7 |

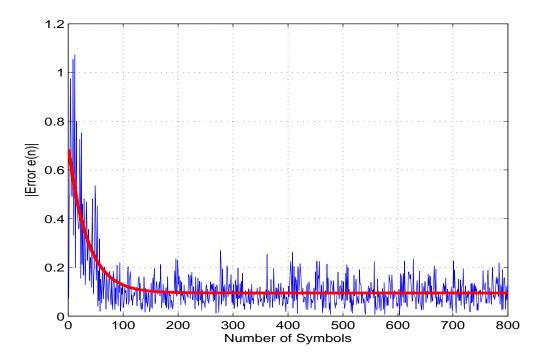

| 5.5 Equalizer error with step size, $\mu = \frac{1}{32}$                                                                                                                  | 3 |

| 5.6 Equalizer error with step size, $\mu = \frac{1}{64}$                                                                                                                  | ) |

| 5.7 Equalizer error with step size, $\mu = \frac{1}{128}$                                                                                                                 | ) |

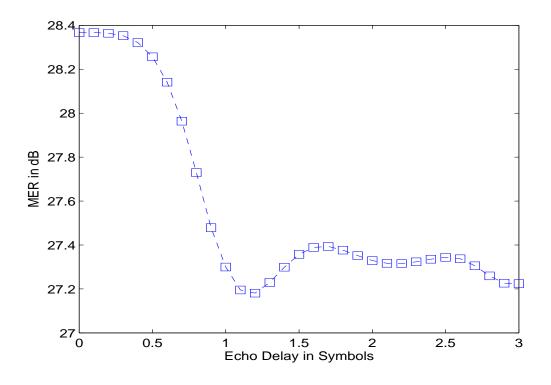

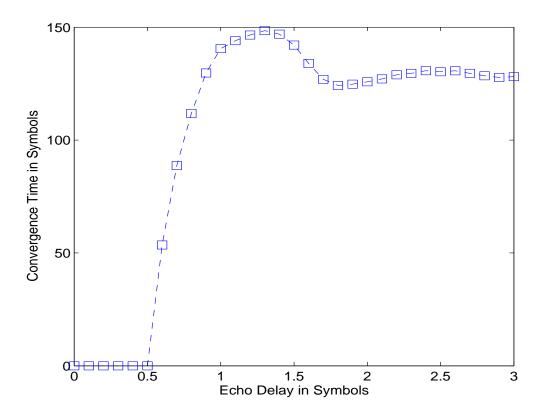

| 5.8 MER in a DOCSIS single echo channel with echo strength 0.3162 of main<br>path and a step size of $\mu = \frac{1}{64}$ in a 20 tap equalizer                           | L |

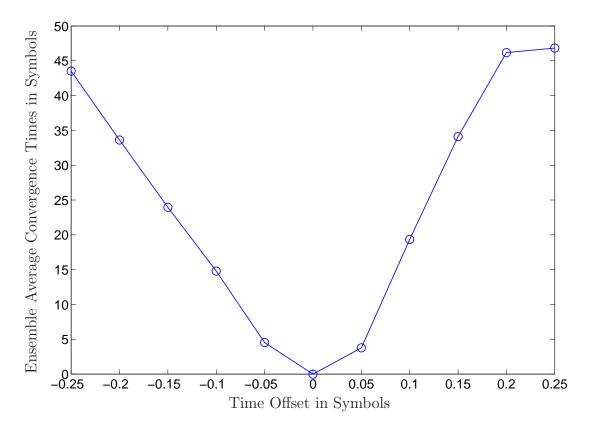

| 5.9 Convergence time in a DOCSIS single echo channel with echo strength 0.3162                                                                                            |   |

| of main path and a step size of $\mu = \frac{1}{64}$ in a 20 tap equalizer                                                                                                | 2 |

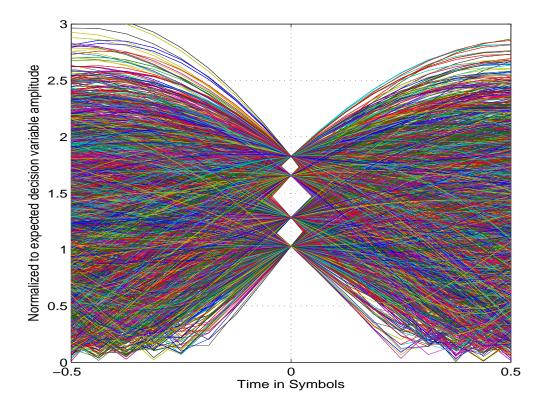

| 5.10 Magnitude of Matched Filter Output in Eye Diagram Format                                                                                                             | } |

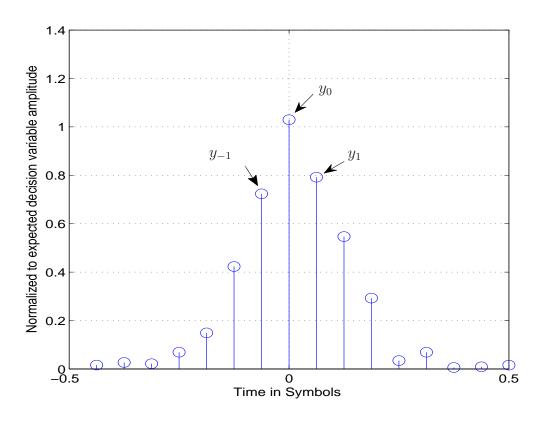

| 5.11 Minimum of Magnitudes of Matched Filter Output                                                                                                                       | 1 |

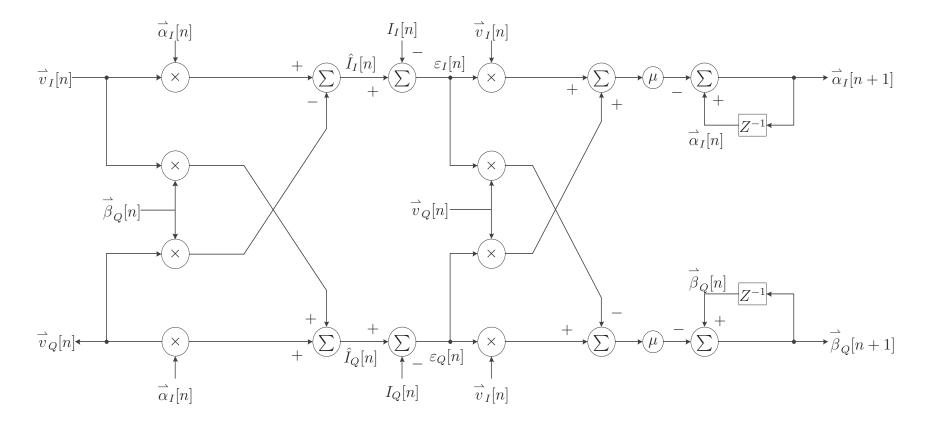

| 5.12 Canonical structure of equalizer                                                                                                                                     | 3 |

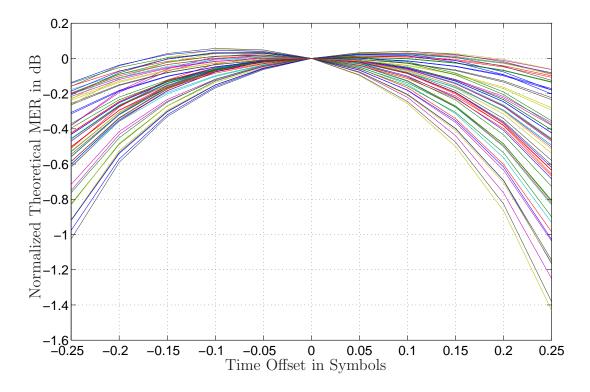

| 6.1 Normalized theoretical MER for a SNR of 30 dB and an infinite length equalizer 81                                                                                     | L |

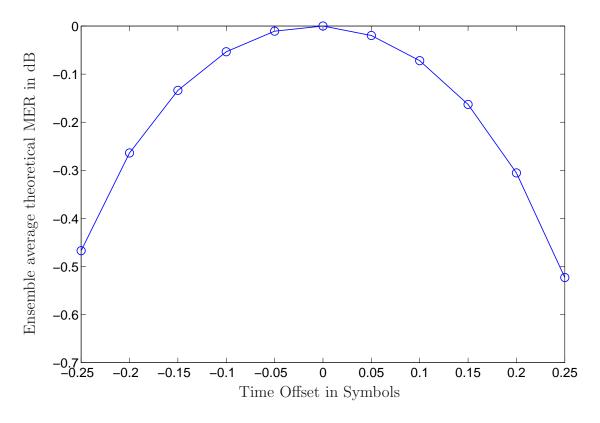

| 6.2  | Ensemble average of normalized theoretical MERs (infinite length equalizer,<br>SNR = 30  dB)                               | 82 |

|------|----------------------------------------------------------------------------------------------------------------------------|----|

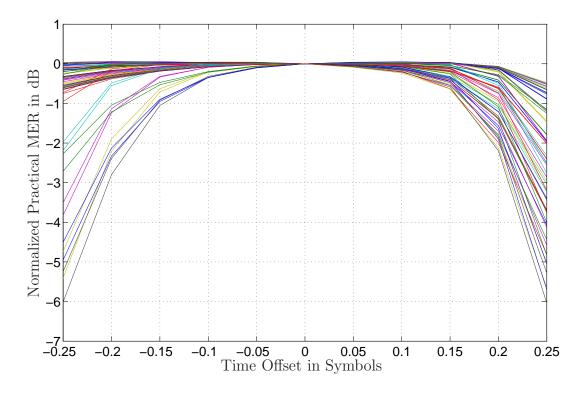

| 6.3  | Normalized practical MER (20 tap equalizer, $SNR = 30 \text{ dB}$ )                                                        | 83 |

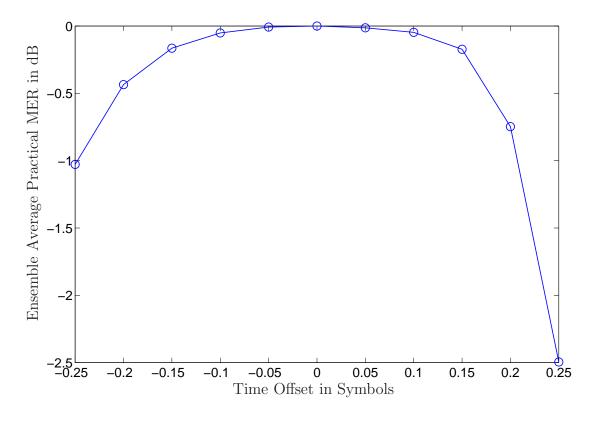

| 6.4  | Ensemble average of normalized practical MERs (20 tap equalizer, $SNR = 30$ dB)                                            | 84 |

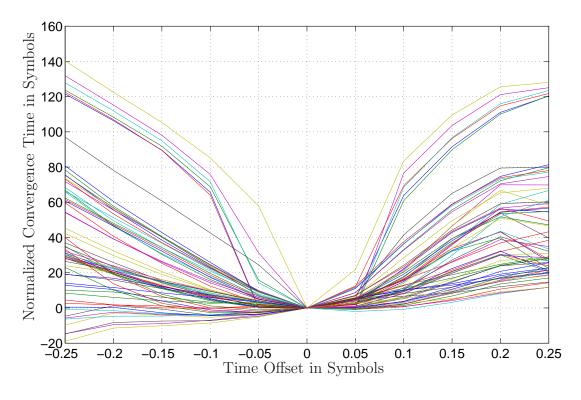

| 6.5  | Relative convergence time $(\mu\sigma_I = \sqrt{2}/64)$ (20 tap equalizer)                                                 | 85 |

| 6.6  | Ensemble average of normalized convergence times $(\mu \sigma_I = \sqrt{2}/64)$ (20 tap equalizer)                         | 86 |

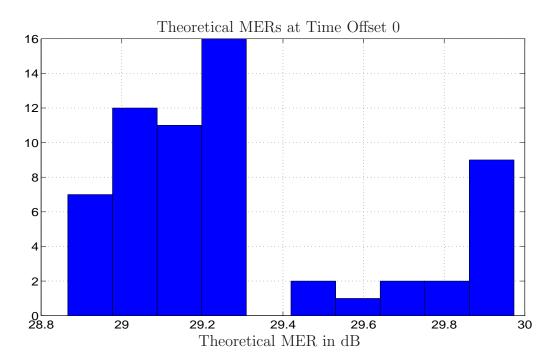

| 6.7  | Histogram of theoretical MER (infinite length equalizer)                                                                   | 87 |

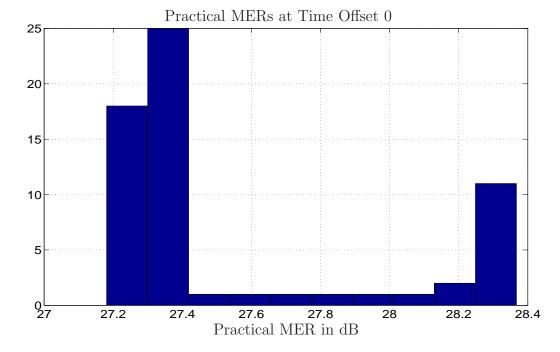

| 6.8  | Histogram of practical MER (20 tap equalizer)                                                                              | 87 |

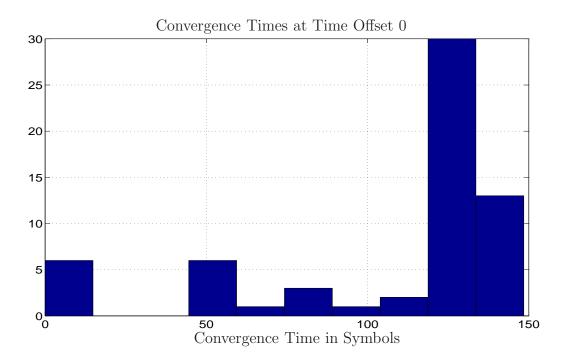

| 6.9  | Histogram of convergence time $(\mu \sigma_I = \sqrt{2}/64)$ (20 tap equalizer)                                            | 88 |

| 6.10 | Constellation plot of the noise corrupted QPSK data at the input of the equalizer                                          | 88 |

| 6.11 | Constellation plot of the noise corrupted QPSK data at the output of the equalizer                                         | 89 |

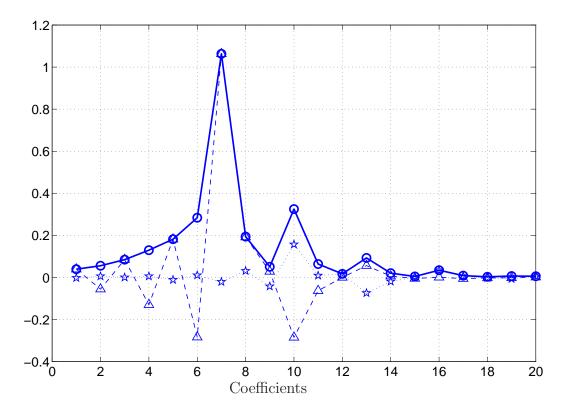

| 6.12 | Equalizer coefficients at steady state                                                                                     | 90 |

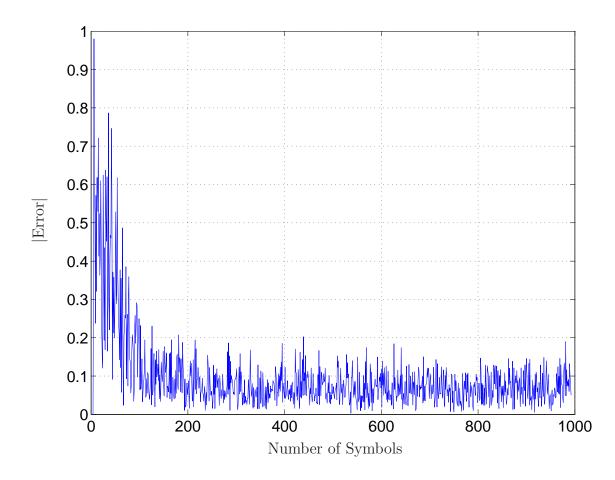

| 6.13 | Equalizer error in DSP Builder                                                                                             | 91 |

| 6.14 | Constellation plot of the output of the equalizer                                                                          | 92 |

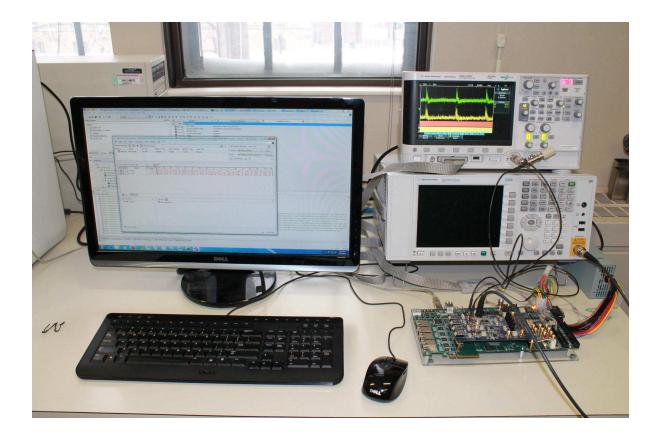

| 7.1  | Hardware and measurement equipment                                                                                         | 94 |

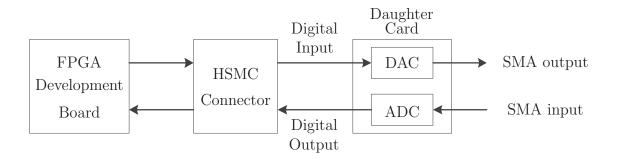

| 7.2  | High level block diagram illustrating connections between the DE4 Board and the daughter card                              | 96 |

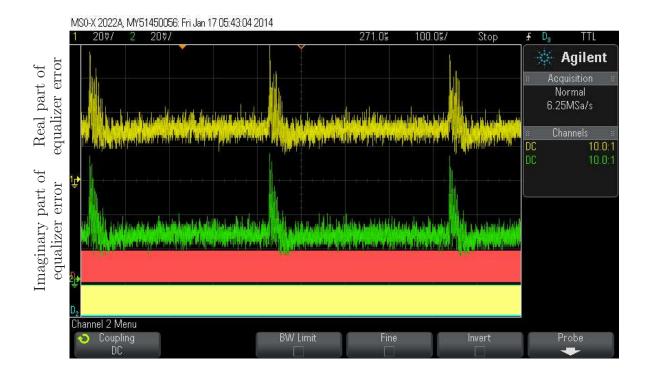

| 7.3  | Comparison between the real part of equalizer output and the respective real part of the training data in the oscilloscope | 98 |

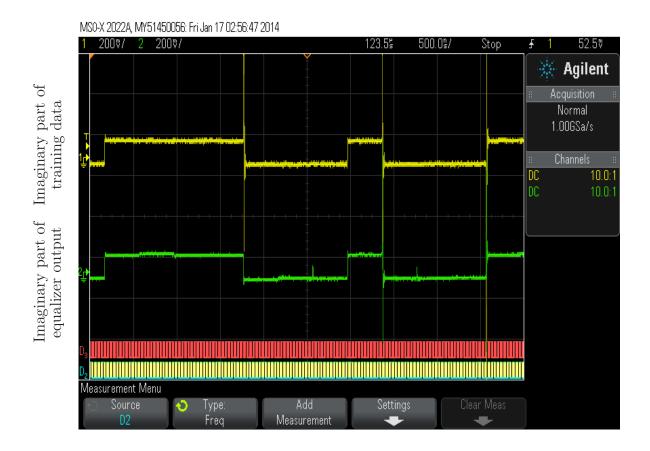

| 7.4 | 4 Comparison between the imaginary part of the equalizer output and the re- |     |  |

|-----|-----------------------------------------------------------------------------|-----|--|

|     | spective imaginary part of the training data in the oscilloscope            | 99  |  |

| 7.5 | Comparison between the real part of equalizer output and the corresponding  |     |  |

|     | training data in Signal Tap                                                 | 100 |  |

| 7.6 | Equalizer error displayed in the oscilloscope                               | 100 |  |

# List of Abbreviations

| AGC    | Automatic Gain Control                          |

|--------|-------------------------------------------------|

| AWGN   | Additive White Gaussian Noise                   |

| ASIC   | Application Specific Integrated Circuit         |

| ADC    | Analog to Digital Converter                     |

| CATV   | Community Antenna Television                    |

| CMTS   | Cable Modem Termination System                  |

| CM     | Cable Modem                                     |

| DOCSIS | Data Over Cable Service Interface Specification |

| DSP    | Digital Signal Processing                       |

| DAC    | Digital to Analog Converter                     |

| FCC    | Federal Communication Commissions               |

| FPGA   | Field Programmable Gated Array                  |

| НВО    | Home Box Office                                 |

| HFC    | Hybrid Fibre Coax                               |

| ISI    | Inter Symbol Interference                       |

| LUT    | Look Up Table                                   |

| LO     | Local Oscillator                                |

| MATV   | Master Antenna Television                       |

| MAC    | Media Access Control                            |

| MSE    | Mean Square Error                               |

| MER    | Modulation Error Ratio                          |

| QAM    | Quadrature Amplitude Modulation                 |

| SRRC   | Square Root Raised Cosine Filter                |

| TDMA   | Time Division Multiple Axis                     |

|        |                                                 |

## 1. Introduction

### 1.1 Evolution of Cable Television

In a communication system, the link between the transmitter and receiver can be wireless, optical fibre, a twisted pair of wires or a co-axial cable. Among these, co-axial cable networks are prominently used in communication to homes. A variety of services such as high speed internet, analog television, high definition digital television, digital audio and IP telephony are provided through co-axial cable networks. Modern cable networks are able to provide two way communication between customer and a central point, which is called the headend. Each home is linked to the headend by a single cable that is divided into many channels using frequency division. On top of that each channel is broken into time slots. In the end for all intents and purposes many homes can communicate with the headend simultaneously.

Although in the early year cable television complemented the regulated television broadcasting, later it emerged as a major force in an increasingly demanding telecommunication and entertainment sector. Cable television services then rapidly started to reach the subscribers, making the cable industry an attractive investment. The local cable operator took the lead to develop this promising sector a link to the information superhighway. The development of cable industry was not easy at all. The evolution of cable industry has been hindered by restrictions imposed by regulation authorities.

In the 1940s and 1950s cable television was developed in USA [1]. The modern day cable plant started as a Community Access Television or Community Antenna Television network [1], [2]. The community antenna television network was called CATV. In the beginning cable plant was used to connect a common antenna to TV receivers that were not within line of sight of the broadcast antenna. In its infancy, which was in the 1940's, CATV systems were deployed in rural areas where over-the-air reception was limited by mountainous terrain or by the distance from the broadcast transmitters. The reception of radio wave signal also was weak in the cities where high rise buildings blocked radio waves. Cable television system operators located antennas on mountains tops and other high points where reception of broadcasting signals was good. They then distributed the signals by a co-axial cable to the subscribers. The networks consists of a community receive antennas and co-axial cable with uni-direction power flow. Later the cable operators piped in TV channels from other cities and used the CATV network to provide their customers with more television channels. Having many channels made CATV systems popular in urban areas and the number of CATV subscribers increased rapidly.

In the early 1950's cable television was still fairly new and expensive. The restrictions imposed by Federal Communication Commissions (FCC) on new TV stations made it difficult for the cable operators to move forward. After a short time the FCC released a nationwide television broadcasting plan which prompted many new stations. With the rapid increase in TV stations cause an increase in the sale of TV sets and antennas. Manufacturers made many models of TVs available, but supply was ahead of demand. Those who had own TV sets also owned an antenna. It was common to see arrays of TV antennas on the roofs of a high rise apartment. Later, Milton Jerrold Shapp developed a system where one master antenna (MATV) [2] could be used for all televisions in a building. His idea was to connect an active signal booster to broadband antenna and use it to drive the co-axial cable with the multiple channel broadband signals. At about the same time Robert (Bob) Tarlton thought that this technique would also work for an entire city. A structure like today's cable television was born when he wired an entire city using co-axial cable and commercially manufactured signal boosters.

By 1952, cable systems were operated in 70 communities and served 14,000 subscribers nationwide in USA [2]. In the late 1950s, cable operators were able to take advantage of microwave and other technologies to pick up broadcast signals from distant broadcasting stations. The ability to access signals from broadcasting stations started a new era for the cable television industry. Cable system moved from transmitting local broadcast signals to providing many programming choices. Once cable operators increased to the number of channels, CATV became much more attractive and the cable system became increasingly popular. The popularity provided an economic opportunity for the cable operator who quickly moved into the large cities. By 1962, almost 800 cable systems were operating and served approximately 850,000 subscribers in USA.

Many local broadcasters felt cable system was in an unfair competition. They asked the government to stop cable operator from distributing TV channels originating from distant broadcasters. The FCC responded by placing restrictions on cable systems disallowing them to import signals from distant broadcasting stations. As a result the growth of the cable industry slowed for next few years.

In the early 1970s, the FCC continued its restrictive policies by enacting regulations that limited the ability of cable operators to offer movies, sporting events, and syndicated programming. The freeze on cable's development lasted until 1972, then FCC started relaxing restrictions on importing distant signals. The continuous concerted effort by the cable industry at federal and local levels resulted in gradual lessening of restrictions on cable industry throughout the decade. These changes along with the development of satellite communications technology and pay TV programming were believed by many to be the main driving force behind the success of the cable industry during the last two decades. The offer of more services led to a substantial increase in subscribers. In 1972 the first pay TV network was launched with Home Box Office (HBO) service. This represented the first successful pay cable service in history. Though very few subscribed to HBO in the beginning, its subscriber base steadily grew and it became one of the most viewed TV service throughout the world. The success of HBO inspired the cable operators to offer many other programming services. With the help of satellite technology HBO was the first programming service conveyed to the subscribers. The second service that used satellite technology was a local TV station that broadcast sports and classic movies. The distribution of station signals by satellite made it available to cable operators to provide services throughout North America. Today almost all cable broadcasting is distributed by satellite. By the end of the 1970's cables growth had resumed and nearly 16 million households were cable subscribers.

The rules and regulations were becoming favourable for the cable industry to explore other opportunities. The 1980 cable act established a friendly regulatory framework for the cable industry. This cable act inspired many to invest in cable plant and television programming. This friendly environment had a strong impact on the rapid growth of cable services. One of the largest private construction projects started after World War II in the cable industry from 1984 through 1992. In this period industry spent more than \$15 billion on the wiring throughout USA, and billions more on program development. The relaxation of FCC rules with the combination of satellite technology paved the way for the cable industry to become a major force in providing high quality video entertainment and information services to subscribers. By the end of the decade, nearly 53 million households subscribed to cable, and cable program networks had increased from 28 in 1980 to 79 by 1989. At the same time cable operators started increasing the price for the services they provide to subscribers.

In the late 80's and early 90's the prices charged for cable services grew to a point where it concerned the policy makers. In 1992, Congress responded by opening the door for other wireless cable and direct to home services. This lead to competition from direct satellite broadcast (DBS) service providers and telephone companies. These new service providers captured much of the growth market stalling the expansion of CATV networks.

Despite of the tight rules of Congress, many satellite networks formed an alliance with cable networks with the view of fulfilling an alternate plan to provide services to a specific sector of the market. Aided by these alliances, by the end of 1995, the number of cable networks had grown to 139 nationwide. This number steadily increased and by the end of 1998, the number of cable networks had elevated to 171. As a result, subscribers had the opportunity to choose from a wide selection of quality services. About 57% of all subscribers were receiving at least 54 channels, which was only 47 channels two years earlier. At the end of the decade, there were more than 55 million cable subscribers.

Starting in the mid 90's the cable operating companies started a major upgrade of their distribution networks. They invested \$65 billion from 1996 through 2002 to build higher capacity hybrid networks consisting of fiber optic and co-axial cable. These broadband

hybrid networks opened the gateway for the cable company to provide high speed internet access, multichannel video, two way voice and high definition and advanced digital video services to the subscribers. Later in the 2000's decade other competitive services such as telephone and digital cable services were added.

In 1996 the relaxation of telecommunication act changed the regulation and policies in favour of the cable operator services. The 1996 act was not only a blessing for the cable operators but also it attracted many investors and many new projects were launched throughout North America. This friendly regulatory environment helped the cable industries accelerate deployment of broadband services in urban, suburban and rural areas. As a result subscribers from those areas had more choices in information, communications and entertainment services.

Historically, the cable television industry was established mainly to provide television programming services. Initially, only one way communication was possible, but the demand for two way services and improved quality forced the cable operators to incorporate two way communication. Two way communication was introduced early in the 1970s with the intention to provide medical alerts, meter readings, etc. However, with progress two way communication services increased. The important aspects of two way communication is to provide data transmission and internet services to the subscribers. Cable quickly became the technology of choice for such services, dominating rival technologies, such as digital subscriber line (DSL) service, offered by telephone companies by about 2:1. Upgraded cable plant that allowed two way communication opened tremendous business opportunity and took the cable industry to an unprecedented level.

The new millennium started with a rigorous plan to convey advanced services to the subscribers over the cable broadband networks in a minimum possible time. Cable companies started testing video services that could change the way people watch television. These services include video on demand (VOD), Internet access, Pay-Per-View on demand and interactive TV. The addition of these advanced services challenged the equipment on customer premises and forced the cable operators to upgrade it. The cost was substantial, so the cable companies moved very carefully. The solution was a sophisticated digital set top box which

was initially very expensive. In the mid 1990's the cost of the digital set top boxes dropped and it started to become widely used. By 2000, digital set-top boxes could be remotely activated, programmed and monitored which allowed the cable operators to incorporate sophisticated encryption technology. Furthermore, this upgraded digital set top boxes paved the way for Pay-per-view and Video-on-Demand services to name a few. In addition to that, the inclusion of digital video compression technology (MPEG 2) greatly increased the capacity of system by packing 10 digitally encoded TV channels into one standard analog channel. The cable industry then had the capacity to provide many speciality channels like HBO, Discovery, ESPN, the shopping channels etc. These advancements in cable industry steadily increased the number of cable subscribers. By the end of 2000, about 40 percent of North Americans had access to high speed internet services. At the same time, growth in telephone services over cable was also notable in the limited market areas. By 2002, more than 2 million subscribers were using cable for their phone service provided by about 280 cable networks. The number of cable networks has steadily increased ever since.

The main competitor of CATV network is the telephone plant, which is primarily a wire line network. Both networks provide service via wire, but they are very different in their technology. Telephone system started two way communication long before the CATV system. The telephone service providers are connected to each other where as cable operators are isolated. One of the important differences is that in a telephone network each subscriber is connected to the central point via a dedicated line. On the other hand in a CATV networks subscribers are connected to headend by a shared co-axial plant network. This is possible in CATV system by using frequency division of its larger bandwidth to provide many channels.

Telephone services over the cable network evolved through two technologies. At first the service required a dedicated bandwidth for an entire conversation. It also required dedicated signal processing equipment that was designed to provide high reliability. This technology was used until about 2003. At time the technology changed to voice-over-IP (VOIP). This is packet based time sharing system that piggybacks the terminal equipment used for data services. While the quality of service for the VOIP technology is not as quite as good, it could be provided with much less cost.

The number of cable operators declined slightly in 2001 and 2002 due to unforeseen upgrading costs and tough competition. However, the cable industry overcame the challenges and in 2005 according to a FCC report, the use of cable modems had climbed 30%.

The CATV is still a very young industry and still in the growth phase. According to the cable television advertising bureau's report, about 92 million households are currently subscribe to cable. Cable systems are operating in every state of the United States and in many other countries, such as Canada and Australia, and throughout Europe and much of East Asia.

### **1.2** The Architecture of Cable Networks

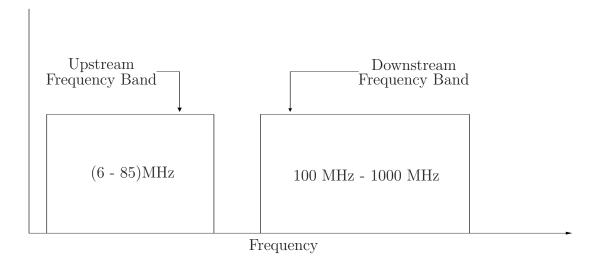

Modern day cable networks must support two-way communication. In simpler words, there must be two communication links between the headend and end users. The link that supports communication from the headend to the end users is called the downstream communication link [3]. The link that supports communication in the other direction, which is from the end users to the headend, is called the upstream communication link [3]. For two-way communication, the frequency spectrum on the cable is divided. Upstream communication links are assigned the lower frequency region (typically 5-85 MHz) [3], while downstream communication links are assigned the upper frequency region (typically 100 MHz-1000 MHz) [3], as depicted in Figure. 1.1

The bidirectional frequency spectrum are standardized by Data Over Cable Service Interface Specification (DOCSIS) [3]. DOCSIS is an international telecommunication standard that came into existence as a result of lack of interoperability among various cable networks. DOCSIS was developed by a non-profit research and development consortium of cable operators and equipment manufacturers called CableLabs with the aim to promote interoperability. The first version of the DOCSIS standard is DOCSIS 1.0, originally developed in March 1997 [4]. In April 1999, it was revised to become DOCSIS 1.1. The primary upgrade was the addition of Quality of Service (QOS) capabilities. Since the beginning of DOCSIS, continuous demand for increased data throughput forced CableLabs to release further upgraded versions of the DOCSIS standard. All versions of the DOCSIS standard

Figure 1.1 Bidirectional frequency band in a DOCSIS network

are described chronologically in Table. 1.1. At the time of writing, the latest version of the DOCSIS standard was DOCSIS 3.0, which was released in 2006. The next version, which is DOCSIS 3.1, is expected to be released in 2014.

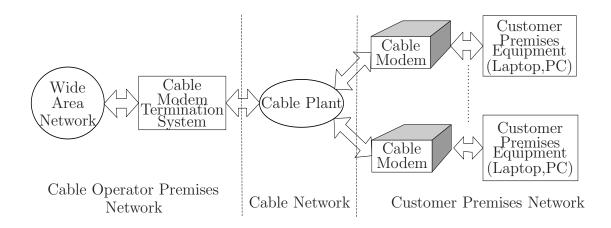

A simplified block diagram of a DOCSIS network [3] is shown in Figure. 1.2. The DOCSIS network consists of a Cable Modem Termination System (CMTS), a Cable Network and many Cable Modem (CMs). The CMTS resides in the headend whereas the CM resides in the subscriber premises. The cable networks can be all co-axial cable or a hybrid of optical fiber and co-axial cable. The heart of the DOCSIS network is the CMTS, which communicates with the cable modem through the cable network in a bidirectional way. The upstream communication system changed considerably with each new version of the DOCSIS standard. A few of these changes are increased symbol rate, the addition of an error control coding scheme, modulation scheme and the packet format. The critical components of both the CMTS and CM are a modulator and a demodulator. The link between CMTS modulator and CM modulator is called the upstream channel and the link between CMTS demodulator and CM modulator is called the upstream channel.

| DOCSIS Version | Year Released | Features                                      |  |

|----------------|---------------|-----------------------------------------------|--|

| DOCSIS 1.0     | 1997          | Basic broadband Internet connectivity         |  |

| DOCSIS 1.1     | 1999          | Quality of Service, Dynamic Services, Con-    |  |

|                |               | catenation, Fragmentation, IP Multicast,      |  |

|                |               | Fault Management, Secure Software etc. and    |  |

|                |               | includes all the features of DOCSIS 1.0       |  |

| DOCSIS 2.0     | 2001          | Significantly enhanced upstream capacity, 6.4 |  |

|                |               | MHz maximum upstream channel width, 27        |  |

|                |               | Mbps maximum upstream channel capacity,       |  |

|                |               | Increased robustness to upstream noise and    |  |

|                |               | channel impairments etc. and includes all the |  |

|                |               | features of DOCSIS 1.1.                       |  |

| DOCSIS 3.0     | 2006          | Channel bonding to increase possible upstream |  |

|                |               | and downstream data rates by a factor of 4,   |  |

|                |               | Support for IPv6, Enhanced security features, |  |

|                |               | Support for IPTV etc. and includes all the    |  |

|                |               | features of DOCSIS 2.0                        |  |

**Table 1.1**Versions of DOCSIS standard with the released year and features

### 1.3 DOCSIS Upstream Demodulator

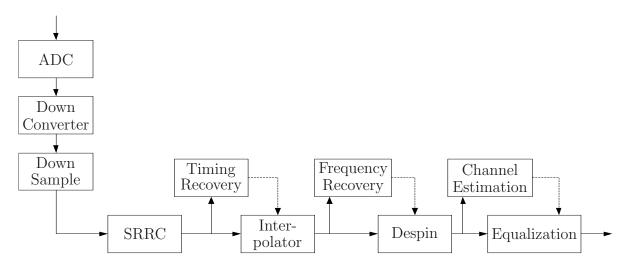

The CM modulator, Quadrature Amplitude Modulates (QAM) [5] a carrier in preparation for transmission through the cable plant. This signal is received at the CMTS where it is demodulated. The structural block diagram of DOCSIS upstream demodulator is shown in Figure 1.3. The received signal is passed through an analog to digital converter, which is denoted by ADC. The output of the ADC is down converted to a complex baseband signal and then down sampled. The output of the down sampler is passed through a Square Root Raised Cosine (SRRC) filter [6], which is matched to the pulse shaping filter [6] in the transmitter. The matched filter output is passed through a timing synchronizer [7], [8]. The purpose of the timing synchronizer is to recover timing so that the sample points in the

Figure 1.2 High-level block diagram of DOCSIS network

Figure 1.3 High-level block diagram for a DOCSIS 3.0 Upstream Demodulator

receiver coincide with the sample points in the transmitter. Timing synchronization is done in two stages [7], as a timing recovery circuit [8] and an interpolation circuit [7]. Timing recovery circuit measures the time offset in sample time between the sample time in the transmitter and the sample time in the receiver. The interpolation circuit calculates the values of the samples with the sample times delayed by the timing offset.

Frequency synchronization [9] is also necessary. It is done in two stages as well, as a frequency recovery circuit and the despiner circuit. The frequency recovery circuit measures the frequency offset due to an imprecise local oscillator in the down-converter. The despiner corrects for error in the down-conversion.

The last block of upstream demodulator is an equalizer. The purpose of the equalizer is to remove signal distortion and residual timing and frequency offset that escaped the synchronizer.

#### 1.4 DOCSIS Upstream Channel

The DOCSIS upstream channel is an one way communication link between the CM modulator in the subscriber premises and the CMTS demodulator in the cable operator's headend.

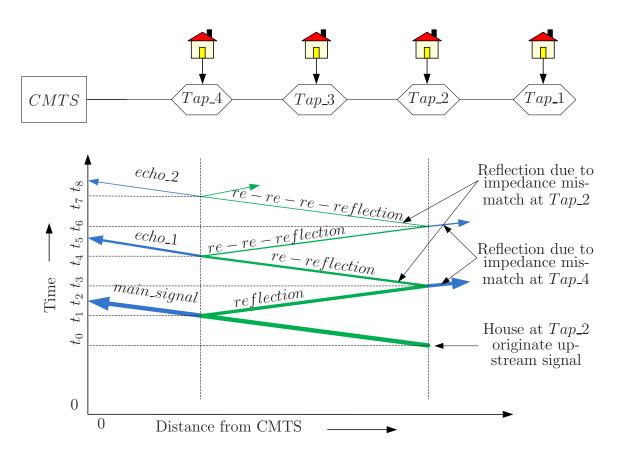

The presence of micro-reflections or echoes [3], [9] in DOCSIS upstream channels is one of the main impairments and yet somehow has not been well explained in literature. Impedance mismatches at the terminal component, poor return and isolation losses of HFC components, the corrosion of center conductor, damaged cable and using older equipments in a HFC network are a few factors that contribute to micro-reflections. One type of micro-reflection is caused when the upstream signal encounters impedance mismatches on its way to the CMTS. The mismatch causes a fraction of the signal's energy to be reflected back towards the CM. If this reflected signal encounters an impedance mismatch in downstream direction, the reflected signal is re-reflect back toward the CMTS. The re-reflection shows up at the CMTS as an echo. This phenomenon is illustrated in Figure 1.4.

The top part of Figure 1.4, shows a segment of a cable plant that connects 4 CM to a CMTS. The plant is a co-axial cable with 4 cable taps which are directional couplers divert a small portion of the downstream bound power to cable modem and add upstream bound power from the CM to the cable. The purpose of explaining echoes it is assumed the impedances of  $Tap_2$  and  $Tap_4$  do not match the impedance of the cable. The cable modem connected to  $Tap_2$  initiates an upstream transmission at time  $t_0$ . This is shown in the distance vs time plot at the bottom of Figure 1.4. The burst transmitted from the house connected to  $Tap_2$  passes through  $Tap_3$  unaffected as  $Tap_3$  is perfectly matched and reaches  $Tap_4$  at time  $t_1$ .  $Tap_4$  has an impedance mismatch that causes a reflection.

Figure 1.4 Process of micro-reflection generation in a cable plant

Subsequent to time  $t_1$ , some of the burst power is propagating in downstream direction. At time  $t_2$  the main part of the burst, which is denoted as *main\_signal* reaches the CMTS. The signal reflected from *Tap\_4* passes through *Tap\_3* in the downstream direction and reaches *Tap\_2* at time  $t_3$ . Since *Tap\_2* has an impedance mismatch it re-reflects a portion of the reflection towards the CMTS. At time  $t_5$  the re-reflected burst reaches CMTS as an echo, which is denoted as *echo\_1*. Through similar process a weaker echo, denoted as *echo\_2* reaches CMTS at time  $t_8$ .

The end effect of the mismatches is to create echoes. The echo delays, which are  $(t_5 - t_2)$ and  $(t_8 - t_2)$ , are normally much shorter than the burst length and cause interference.

#### **1.5** Statement of Research Problems

In a CATV system, upstream modulator transmits QAM data, which pass through the DOCSIS upstream channel. The upstream demodulator demodulates the received QAM data. The modulated QAM signal on its way to the demodulator encounters impairments, which include timing error, carrier frequency error, phase error, micro-reflections and thermal noise [9], [10]. These impairments need to be corrected before the signals can be successfully demodulated.

One of the major challenges in demodulating a signal received over the DOCSIS upstream channel is to mitigate the effect of the micro-reflections, which causes intersymbol interference (ISI) [11]. According to the DOCSIS standard, the micro-reflections can be as large as 10 dB below the carrier and can arrive up to seven symbol durations later. Another challenge is the correction of error in time recovery circuit. This error also causes ISI.

In order to mitigate ISI the upstream demodulator requires a timing synchronizer, a frequency synchronizer and an equalizer [9], [12], [13], [14]. Although timing and frequency synchronizer blocks correct most of timing and frequency offset, the equalizer block must suppress the error even further to minimize the ISI.

The equalizer in an upstream demodulator must adapt on a packet-by-packet basis. The received successive packet bursts could come from different CMs over different channels and require very different equalization. To facilitate the training of an equalizer, each packet is prefixed with a known preamble. The received preamble is used to estimate the impairment in the signal caused by the channel and synchronizer. By the time the end of preamble is reached, the equalizer must have converged and removed most of the ISI from the signal [15], [16], [17].

The problem is to construct an equalizer that converges quickly so the preamble length can be small and the data throughput is maximized.

The goal of this thesis is to implement the equalizer in a Stratix IV Field Programmable Gated Array (FPGA) board using the fewest possible logic elements.

#### **1.6** Organization of the Thesis

The organization of remainder of the thesis is structured chapter by chapter as follows. In chapter 2, background study about the DOCSIS upstream channel is included. This chapter also explain in details channel impairments and different channel parameters which are specified by the DOCSIS standard.

Chapter 3 and 4, include details about equalization technique and performance criteria. Chapter 3, contains the mathematics behind equalization for an infinite length equalizer. It also sets the equation for measuring different performance criteria of equalizers. Specific equalization type, which is mentioned by DOCSIS is explained in chapter 4. This chapter also talks about the structure and performance criteria of the equalizer in details.

The implementation of DOCSIS upstream equalizer is included in chapter 5. Implementation of the equalizer is solely dependent on the different parameters of the equalizer. This chapter explains how different parameters of equalizer can have an impact on the performance of the equalizer.

Chapter 6, portrays different simulation results. This chapter is partitioned in two major sections. They are MATLAB based simulation results and DSP Builder based simulation results. The MATLAB simulation results includes for both theoretical and practical equalizer. It also compares the results and explain differences. The DSP Builder simulation results includes simulation results for practical equalizer and compares with the MATLAB results. Chapter 7 is based on hardware related results.

The thesis concludes with the conclusion chapter. All the successful outcomes of the thesis are included here. This chapter also adds some indications about the future work that can be done.

## 2. CATV Upstream Channel

#### 2.1 Overview

A basic communication system consists of a transmitter, a receiver and a communication link between the transmitter and receiver. The same structure is applicable for a CATV system as well. A high-level structure of a DOCSIS upstream communication system is shown in Figure. 2.1. A modulator resides in the transmitter and a demodulator resides in the receiver. The modulator and the demodulator are connected by a cable. As this thesis is based on implementing an efficient equalizer, the purpose of which is to overcome the distortion caused by channel impairments, it is important to understand all the sources of impairments.

The next two sections of this chapter includes details about specific issues related to DOCSIS upstream channel with respect to physical layer and Media Access Control (MAC) layer.

### 2.2 Physical Layer of DOCSIS Upstream Channel

This section explains in details about the origin of major channel impairments with some background material related to the upstream cable channel.

Figure 2.1 High-level block diagram of DOCSIS upstream communication system

Figure 2.2 Basic block diagram of QAM modulator

#### 2.2.1 Basic Modulation and Demodulation Technique

According to the DOCSIS standard the modulator shown in Figure 2.1 must be Quadrature Amplitude Modulation (QAM) in the upstream direction. The structure of a QAM modulator, which is well known [5], is illustrated in Figure 2.2.

The input to the serial-to-parallel (S/P) converter is a serial binary data stream. The bit to symbol mapping is done by this serial-to-parallel converter. For an M-ary QAM technique, the input bits are partitioned into non-overlapping segments of  $\log_2 M$  bits by the serial-to-parallel converter. The rate at which the serial-to-parallel converter converts blocks of  $\log_2 M$  bits into symbols is referred to as the symbol rate. The output of the serial-toparallel converter becomes two  $\log_2 M$  bit addresses for two look-up tables (LUT 0 and LUT 1). The look-up tables map the symbol values into numbers specified by the encoding rule. The output of the two look-up tables are denoted as  $a_I$  and  $a_Q$ , where  $a_I$  and  $a_Q$  are weighted impulses to be filtered by the Pulse Shaping Filter (PSF). Prior to filtering the impulses are up-sampled by zero stuffing by a factor of L. The outputs of the pulse shaping filter are used to amplitude modulate two sinusoidal carriers in quadrature. The modulated carriers are summed and then converted to an analog signal, denoted as s(t), by a Digital-to-Analog Converter (DAC). The Local Oscillator, which is denoted as LO, generates a sinusoidal at the carrier frequency.

The symbol values that are stored in the look-up tables can be plotted in a 2-dimensional

Figure 2.3 Constellation diagram for 4-QAM data

plane, which gives birth to a diagram called a constellation plot. An example of a constellation diagram for 4-QAM is illustrated in Figure 2.3. It should be mentioned here that each symbol is represented by a complex number. The in phase and quadrature phase component  $(a_I \text{ and } a_Q)$  form the real and imaginary part of a symbol respectively.

The structure of a basic QAM demodulator is shown in Figure. 2.4. The received signal r(t) is a noise corrupted version of transmitted signal s(t). The first step in demodulation is to downconvert the received signal r(t) to a baseband signal by multiplying it with two quadrature carriers generated by the Local Oscillator (LO) in the receiver. Prior to down-conversion the received signal is passed through an analog to digital converter (ADC). It should be mentioned here that this local oscillator behaves in the same way it does in the transmitter. The downconverted in phase and quadrature phase components of the signal are denoted by  $u_I[n]$  and  $u_Q[n]$  respectively.

The downconverted baseband signal is passed through a low pass filter to remove any high frequency component that was generated during the downconvertion. This low pass filter has an impulse response identical to the pulse shaping filter and is referred to as the matched filter. The matched filter outputs are denoted as  $z_I[n]$  and  $z_Q[n]$ ; they are down-

Figure 2.4 Basic block diagram of QAM demodulator

sampled by a factor of L to produce in phase and quadrature phase components of each symbol successively. The output of the down-sampler is passed to the decision device, which is referred to as slicer. The purpose of the slicer is to determine what symbol was transmitted.

Having explained modulation and demodulation technique used in DOCSIS upstream communication system, in the following subsection the channel impairments are explained in details.

#### 2.2.2 Channel Impairments

As mentioned in section 1.5, there are numerous impairments that distort the transmitted upstream signal. The sources of most critical impairments together with their effect on distorting signals are explained in this sub-section.

#### Timing Error

One of the major channel impairments is timing error, which is the error created by sampling the received signal at the incorrect time. This type of error results from two phenomenon. One is that the oscillators that form the timing bases in transmitter and receiver are not synchronized. The other is the time to propagate through the cable plant is unlikely to be an integer number of samples.

This error, which is referred to as timing offset, causes ISI, which increase the probability

of the slicer making a wrong decision. Normally the upstream demodulator includes a circuit called the timing synchronizer that removes most of the timing error.

#### **Frequency Error**

Another important impairment that need to overcome is frequency conversion error, which is caused by the inaccuracy in the local oscillators in the transmitter and receiver. The error causes a frequency offset in the baseband signal which causes the constellation to spin and make the task of recovering the symbols very difficult.

Normally a circuitry called frequency synchronizer, whose purpose is to de-spin the constellation, is included in the upstream demodulator. The frequency synchronizer first estimates the frequency error and then passes this information to the despiner, which does not completely eliminate the spinning but slows the rate considerably.

#### **Micro-reflections**

One of the most commonly faced impairment is the presence of micro-reflection or echoes in the cable plant where many CM and the CMTS are connected to the same physical cable. Communication in the upstream direction is initiated by a CM. As the transmitted burst propagates through the large cable network to reach CMTS, it traverses taps, which directionally couple other CM's to the cable. Some of the CM's may not be perfectly impedance matched to the cable network. As a result, a portion of the transmitted burst get reflected from those impedance mismatches and eventually reaches to CMTS as echoes. The reflected copies of the main burst are called micro-reflections or echoes. The echoes are delayed and attenuated copies of the main transmitted burst.

Figure 2.5 shows three curves. One curve (solid line connecting markers ' $\circ$ ') is the output of the matched filter for the transmission of a single symbol that encounter a channel with an echo of magnitude 0.3162 with respect to the main signal and a delay of 1.5 symbols. The second curve (dashed line connecting marker ' $\diamond$ ') is that same transmission in the absence of echo. The third curve (dashed line connecting marker ' $\Box$ ') is the echo. It is clear from the combined response that it is not symmetric and does not cross zero at symbol times, which

Figure 2.5 Impulse response of channel model to illustrate the effect of echo

causes ISI.

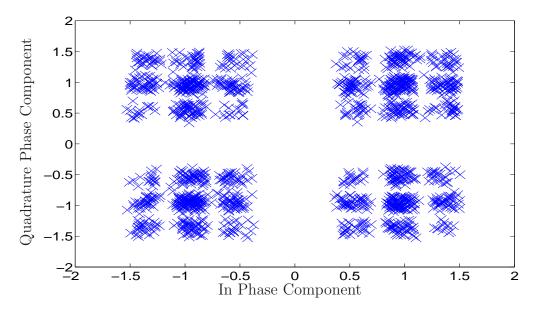

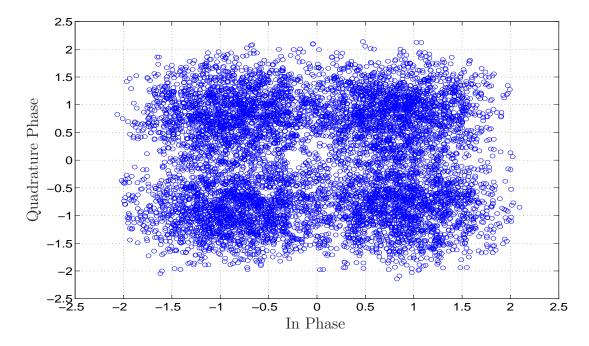

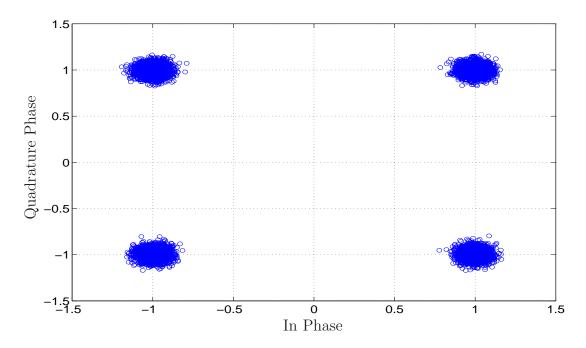

An example constellation diagram is shown in Figure 2.6 to visualize the effect of channel echoes. The decision variables is plotted for a burst of transmission of 1000 QPSK symbols that pass through the multipath channel. It is clear from Figure. 2.6 that the constellation points are scattered around the correct points described above. This scattering caused by the echo is by definition inter symbol interference.

As this thesis is based on a DOCSIS channel, it is important to know the characteristics of each echo. According to the DOCSIS standard the upstream channel consists of one main path and a maximum three echoes. The worst case parameters for each echo are specified in the DOCSIS standard as tabulated in Table 2.1.

|        | Amplitude (dBc) | Echo Delay (symbol) | Echo Phase (Rad) |

|--------|-----------------|---------------------|------------------|

| Echo_1 | -10             | 0-2.5               | 0-2π             |

| Echo_2 | -20             | 0-5                 | 0-2π             |

| Echo_3 | -30             | 0-7.5               | 0-2π             |

Table 2.1

DOCSIS specified echoes with their parameters

Figure 2.6 Constellation diagram showing the effect of echo

Having covered most critical impairments, it is understandable now how each impairment distorts the transmitted signal. It is the task of this thesis to mitigate the impairments so the decision variable can be reliably translated into the symbol that was transmitted. This task falls to an equalizer which must be included in the upstream demodulator.

### 2.3 MAC layer of DOCSIS Upstream Channel

The media access control (MAC) layer of the CMTS performs the network management tasks for the DOCSIS upstream channels. To explain all the tasks of MAC layer is beyond the scope of this thesis, but the issues relevant to this thesis are explained briefly in this section.

With the view to allow multiple users to transmit data to the CMTS in the headend via a single upstream channel, the DOCSIS standard incorporated two multiple access schemes, namely Time Division Multiple Access (TDMA) [3] and Synchronous Code Division Multiple Access (S-CDMA) [3]. Although both of these multiple access modes can be used in an upstream channel, this thesis only considers TDMA mode. In TDMA mode, each user is allowed to access a channel for a specific period of time.

Figure 2.7 Process of ranging mode operation

The CMTS MAC partitions each TDMA upstream channel into a sequence of timeslots, which are called minislots by the DOCSIS standard. The MAC allocates each minislot to a CM upon request. In the allocated minislots there are two types of packet burst transmitted over the DOCSIS channel. They are called traffic mode packets and ranging mode packets [9].

#### **Ranging Mode**

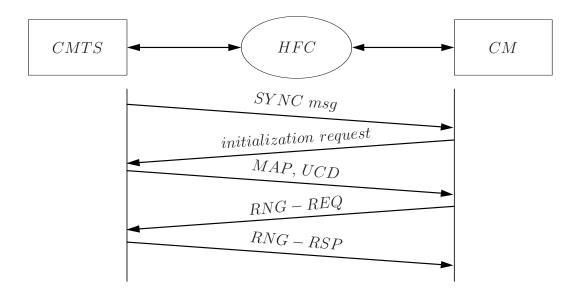

As discussed in section 2.2.2, the presence of a large number of impairments in the upstream channel makes the task symbol recovery very difficult. The primary purpose of ranging mode is to configure circuitry in the CM, whose purpose is to mitigate the effects of the channel impairments. The MAC transmits the configuration information to the CM's via the down stream channels. The MAC calculates the configuration from measurements made at the CMTS while in ranging mode. A bidirectional communication process between a CM and a CMTS is shown in Figure. 2.7.

In a CATV network, at the time a cable modem is turned on, it monitors a downstream DOCSIS channel for purpose of synchronization. To facilitate synchronization the CMTS periodically sends SYNC messages on every downstream channel. After synchronization the CM sends an initialization request on an ALOHA time slot reserved for this purpose. Upon receiving an initialization request the CMTS sends Upstream Channel Descriptor (UCD), which tells CM's the upstream channel frequency, symbol rate, modulation profile, and other parameters necessary to communicate on the network. Finally, the CMTS sends out Media Access Protocol (MAP) messages to allocate talk time to each cable modem. Since many cable modems are assigned to one upstream channel frequency, the cable modems must time-share the upstream channel using TDMA.

The cable modem is now ready to begin ranging with the CMTS. The ranging process begins with Initial Ranging, which is a process in which the cable modem begins by sending a Range-Request (RNG-REQ). If it does not receive a Range-Response (RNG-RSP) from the CMTS within 200 msec, the cable modem increases its transmit power and retransmits the RNG-REQ. This process is repeated until a RNG-RSP is received. Once the modem has received its first RNG-RSP from the CMTS it will be moved from Initial Ranging to Station Maintenance. The cable modem will also be instructed by the CMTS to make adjustments to its transmitting frequency, amplitude, timing offset and pre-equalization [3].

After successful reception of the ranging packet by the CM's, it is then registered with the CMTS. The CMTS then supervises the CM's to exit from the ranging mode and enter into the traffic mode.

### Traffic Mode

In traffic mode, real datas are transmitted by a CM. Once CM's are ranged then they are configured to mitigate most of channel impairments and the transmission are relatively free of impairments. This implies that in traffic mode, the CMTS do not need to correct transmitter specific inaccuracies.

This thesis concerns ranging the CM's. In particular it focuses on the process of configuring the pre-equalizer in the CM's. So the rest of this thesis is centred on ranging mode packet only.

# 3. Theory of Equalization

There is much literature [16], [18], [19] available for channel equalization. One of the approaches uses linear transversal filter structure, which is commonly used for equalization, is the focus of this thesis. Research has been carried out to find the optimum filter coefficients for the equalizer. Research has delivered an algorithm for coefficient that produces a decision variable with minimum mean square error [18]. It is the Mean Square Error (MSE) criterion that will be used in this thesis.

## 3.1 Least Mean Square Error Equalizer

The Least Mean Square Error (LMSE) equalizer is based on the MSE criterion [18]. This section includes the theory that supports the MSE equalization criterion. The theory of equalization is explained in the next sub-section.

## 3.1.1 System Model

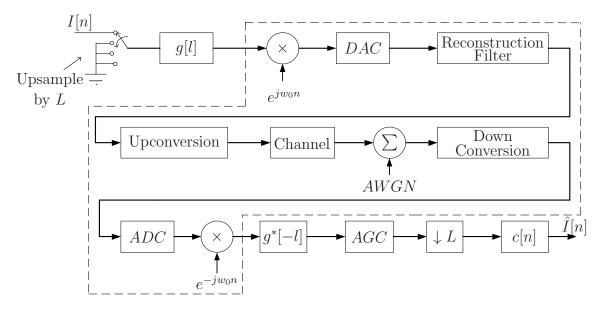

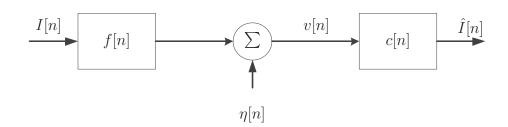

The digital system that will be used to derive a theoretical limit on the residual mean square error at the output of a mean square error equalizer is shown in Figure 3.1.

The input, I[n], is an independent, zero mean, random complex data sequence with a variance of  $\sigma_I^2$  [20]. That is

$$E[I[n]] = 0 ; -\infty < n < \infty$$

$$E[I[n]I^*[k]] = \begin{cases} \sigma_I^2 \text{ for } n = k \\ 0 \text{ for } n \neq k \end{cases}$$

(3.1)

The data are up-sampled by a factor of L with zero stuffing and shaped with a Square

Figure 3.1 The Digital Communication System

Root Raised Cosine (SRRC) filter with a roll-off-factor, r = 0.25. The filter is labelled by its impulse response g[l] and it is referred to in the literature as the pulse shaping filter. It operates at L times the symbol rate and has the following properties.

1. It has Discrete Time Fourier Transform (DTFT) denoted  $G(e^{jw})$ . The magnitude of  $G(e^{jw})$  is given by

$$G(e^{jw}) = \begin{cases} \sqrt{L} ; & |w| \le (1-\beta)\frac{\pi}{L} \\ \sqrt{L}\sqrt{\frac{1}{2} + \frac{1}{2}sin(\frac{Lw}{2\beta} - \frac{\pi}{2\beta})} ; & (1-\beta)\frac{\pi}{L} < |w| < (1+\beta)\frac{\pi}{L} \\ 0 ; & (1+\beta)\frac{\pi}{L} \le |w| \le \pi \end{cases}$$

2. The energy in g(l) is 1. That is  $\sum_{l=-\infty}^{\infty} |g(l)|^2 = 1$ . From Parseval's theorem [5] this also implies

$$\frac{1}{2\pi} \int_{-\pi}^{\pi} |G(e^{jw})|^2 dw = 1.$$

3. The peak value of the impulse response of the cascade of the pulse shaping filter and the matched filter is 1. That is to say  $max(g[l] * g^*[-l]) = 1$ . To be specific

$$\sum_{l=-\infty}^{\infty} g[m]g^*[-(l-m)]|_{l=0} = 1.$$

This is a consequence of the energy in g[l] being 1.

4. Normally g[l] is real, but it does not need to be.

The output of the pulse shaping filter is up converted in two stages: a digital stage and an analog stage. The up converted signal is transmitted over an analog medium (CATV cable) that has a real impulse response  $h_a(t)$ .

The receiver in Figure 3.1 begins with the additive noise. It first down converts the signal to an IF, then quantizes it and then digitally down-converts it to complex baseband. The down conversion to complex baseband generates a complex signal which is the complex low-pass equivalent of the real band-pass modulated signal.

The complex baseband signal is filtered with matched filter, that is actually a pair of filter that acts on the real and imaginary part separately. The matched filter is denoted by its impulse response, which is  $g^*[-l]$ . Automatic Gain Control (AGC) follows the matched filter. The gain of automatic gain control block is AGC. It is assumed the AGC is controlled to keep power of its output to the constant '1'. The output of the AGC is down-sampled by a factor of L to the symbol rate and then equalized by the block labelled as equalizer, c[n].

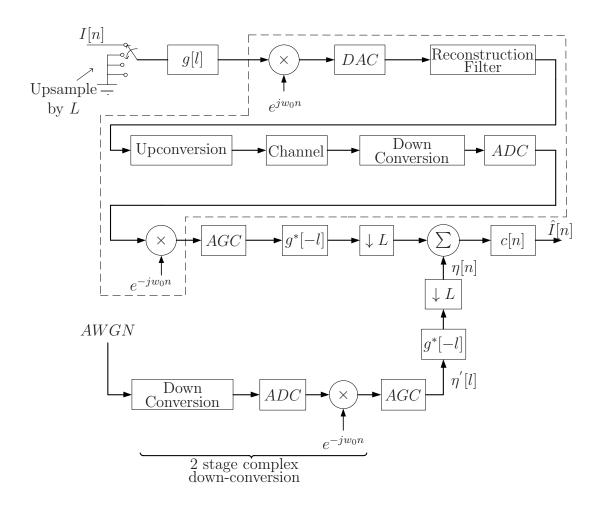

#### Simplified System Model

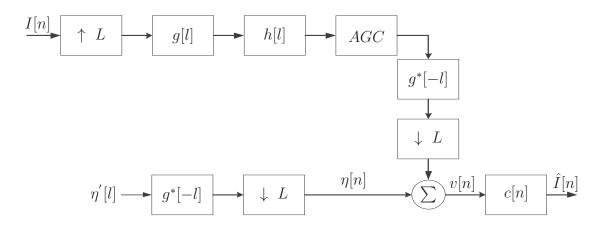

A simplified model is obtained by rearranging the natural order of the blocks in Figure 3.1 and then consolidating them. The first step is to move the AGC to the input side of filter  $g^*[-l]$ . The next step is to relocate the AWGN to the output of the down-sampler and represent it with its complex low-pass equivalent. In the relocation the noise source passes through a real down-converter, ADC, a complex down-converter, an AGC,  $g^*[-l]$  and the down-sampler. The system with AGC repositioned and noise relocated and represented by its complex low-pass equivalent, is shown in Figure 3.2. The low-pass equivalent of the noise, which is complex noise after the complex down-conversion, is denoted as  $\eta'[l]$ . The complex baseband noise is filtered with  $g^*[-l]$  and down-sampled to get  $\eta[n]$ , which is added to the signal component output of the channel.

The blocks in Figure 3.2 enclosed by the dashed line can be modelled by a filter with

Figure 3.2 The Modified Digital Communication System

impulse response  $e^{j\Delta w l}h[l]$ , where  $\Delta w$  is the difference in the up conversion and down conversion frequencies and h[l] is a time invariant complex low pass filter. Without loss of significant generality, the time expansion/contraction incurred from the small differences in frequency in the LOs that establish the time bases in the transmitter and receiver, is not included in the model.

It can be shown that a frequency offset does not affect the theoretical performance of a Least Mean Square (LMS) equalizer [18]. For that reason  $\Delta w$  is set to zero in the analysis that follows.

The critical block is the replacement filter h[l], is the channel, which has a wide band

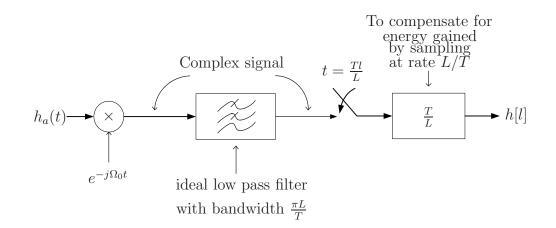

**Figure 3.3** Generating h[l]

Figure 3.4 Somewhat Refined System Model

impulse response denoted as  $h_a(t)$ . While  $h_a(t)$  is wide band, the real down-conversion contains a band-pass filter with a bandwidth equal to the nyquist zone of the analog to digital converter (ADC). That is, the band-pass filter has a bandwidth of  $\frac{L}{2T}$ Hz or  $\frac{\pi L}{T} \frac{\text{rad}}{\text{sec}}$ , where  $\frac{1}{T}$  is the symbol rate and  $\frac{L}{T}$  is the sampling rate of ADC. That being the case, h[l] is obtained from  $h_a(t)$  as shown in Figure 3.3.

After replacing the blocks inside the dashed line with a filter having impulse response h[l], the modified digital communication system becomes the one shown in Figure 3.4.

The next step is to represent the path from the system input to the adder input as the

Figure 3.5 Symbol rate System Model

low-rate filter with impulse response f[n]. This allows the system be modelled at the symbol rate as shown in Figure 3.5, where:

1.  $f[n] = AGC * g[l] \star h[l] \star g^*[-l]|_{l=Ln}$ . Note that f[n] is complex.

- 2. c[n] is the impulse response of the equalizer.

- 3. v[n] is the input to the equalizer.

- 4.  $\eta[n]$  is an independent gaussian noise sequence with  $E[\eta[n]\eta^*[n]] = \sigma_n^2$

- 5. The output of the equalizer is  $\hat{I}[n]$  which is an estimate of I[n].

# 3.1.2 Mean Squared Error (MSE) Criterion

Let I[n] is an estimated symbol at the output of the equalizer. Now, the error in estimate  $\hat{I}[n]$  is

$$\varepsilon[n] = \hat{I}[n] - I[n] \tag{3.2}$$

Both I[n] and  $\hat{I}[n]$  are random variables which means  $\varepsilon[n]$  is also a random variable.

The mean of the square of the magnitude of the error is referred to as mean squared error. It is given by [18]

$$J = E[|\varepsilon[n]|^2]$$

$$J = E[|\hat{I}[n] - I[n]|^2]$$

(3.3)

From the working system model shown in Figure. 3.5,  $\hat{I}[n]$  is given by

$$\hat{I}[n] = \sum_{k=-\infty}^{\infty} c[k]v[n-k]$$

(3.4)

Substituting equation (3.4) into equation (3.3) yields

$$J = E[|(\sum_{k=-\infty}^{\infty} c[k]v[n-k]) - I[n]|^2]$$

$$J = E[((\sum_{k=-\infty}^{\infty} c[k]v[n-k]) - I[n])((\sum_{k=-\infty}^{\infty} c[k]v[n-k]) - I[n])^*]$$

(3.5)

## Finding the Equalizer Coefficients to Minimizing MSE

There is an infinite number of complex equalizer coefficients that can be represented by

$$c[k] = c_R[k] + jc_I[k]; \ -\infty < k < \infty$$

(3.6)

where  $c_R[k]$  and  $c_I[k]$  are real coefficients.

The problem is to find the sets of  $c_R[n]$  and  $c_I[n]$  that yield the minimum J. These are the set of coefficients that satisfy

$$\frac{\delta J}{\delta c_R[n]} = 0 \text{ and } \frac{\delta J}{\delta c_I[n]} = 0 \text{ for } -\infty < n < \infty$$

(3.7)

A useful expression for  $\frac{\delta J}{\delta c_R[n]}$  is found using equation (3.5) by first exchanging the variables k and n so that the dummy variable in the summation is n and the coefficients of the equalizer are indexed by n. Second the derivative is moved inside the expectation. Doing so yields

$$\frac{\delta J}{\delta c_R[n]} = E[\{\frac{\delta}{\delta c_R[n]} (\sum_{n=-\infty}^{\infty} c[n]v[k-n] - I[k])\} \times (\sum_{n=-\infty}^{\infty} c[n]v[k-n] - I[k])^* + (\sum_{n=-\infty}^{\infty} c[n]v[k-n] - I[k]) \times \{\frac{\delta}{\delta c_R[n]} (\sum_{n=-\infty}^{\infty} c[n]v[k-n] - I[k])^*\}].$$

(3.8)

Taking the partial derivatives yields

$$\frac{\delta J}{\delta c_R[n]} = E[v[k-n](\sum_{n=-\infty}^{\infty} c[n]v[k-n] - I[k])^* + v^*[k-n](\sum_{n=-\infty}^{\infty} c[n]v[k-n] - I[k])]$$

(3.9)

Changing the dummy index variable from n to m in (3.9) allows v[k-n] and  $v^*[k-n]$  that are outside the summation to be moved inside the summation. Doing so and distributing the conjugation produces:

$$\frac{\delta J}{\delta c_R[n]} = E[\sum_{m=-\infty}^{\infty} c^*[m] v^*[k-m] v[k-n] - v[k-n] I^*[k] + \sum_{m=-\infty}^{\infty} c[m] v[k-m] v^*[k-n] - v^*[k-n] I[k]]$$

(3.10)

Taking the expectation of the four terms separately and then moving expectations inside the summations yields

$$\frac{\delta J}{\delta c_R[n]} = \sum_{m=-\infty}^{\infty} c^*[m] E[v^*[k-m]v[k-n]] - E[v[k-n]I^*[k]] + \sum_{m=-\infty}^{\infty} c[m] E[v[k-m]v^*[k-n]] - E[v^*[k-n]I[k]]$$

(3.11)

Inspection of equation (3.11) reveals that the four terms are two pairs of complex conjugates, which makes the right hand side real. Setting  $\frac{\delta J}{\delta c_R[n]} = 0$  and moving the negative terms to the left hand side yields

$$\mathbb{R}\{E[v^*[k-n]I[k]]\} = \mathbb{R}\{\sum_{m=-\infty}^{\infty} c[m]E[v[k-m]v^*[k-n]]\}.$$

(3.12)

Solving  $\frac{\delta J}{\delta c_I[n]}$  in a similar manner yields

$$\mathbb{I}\{E[v^*[k-n]I[k]]\} = \mathbb{I}\{\sum_{m=-\infty}^{\infty} c[m]E[v[k-m]v^*[k-n]]\}.$$

(3.13)

Equations (3.12)) and (3.13) can be combined into a single equation.

$$E[v^*[k-n]I[k]] = \sum_{m=-\infty}^{\infty} c[m] E\Big[v[k-m]v^*[k-n]\Big].$$

(3.14)

The solution to equation (3.14) for c[n],  $-\infty < n < \infty$ , provides an equalizer whose output is an estimate of I[k] that minimizes  $E[|\hat{I}[k] - I[k]|^2]$ .

An alternate form of equation (3.14) that will be useful later on is

$$E\Big[\sum_{m=-\infty}^{\infty} c[m]v[k-m]v^*[k-n] - v^*[k-n]I[k]\Big] = 0$$

$$E\left[v^*[k-n](\hat{I}[k] - I[k])\right] = 0.$$

(3.15)

# Solving For c[n]

The problem at hand is to find an equation that gives the optimum set of c[n]. The derivation starts by getting expressions for v[k-m] and  $v^*[k-n]$ . From the symbol rate system model shown in Figure 3.5

$$v[n] = I[n] \star f[n] + \eta[n]$$

Therefore,

$$v[k-m] = \sum_{i=-\infty}^{\infty} I[i]f[k-m-i] + \eta[k-m]$$

and

$$v^*[k-n] = \sum_{q=-\infty}^{\infty} I^*[q] f^*[k-n-q] + \eta^*[k-n].$$

(3.16)

Using equation (3.16), the product  $v[k-m]v^*[k-n]$  can be expressed as the sum of four terms:

$$v[k-m]v^{*}[k-n] = \sum_{q=-\infty}^{\infty} \sum_{i=-\infty}^{\infty} I[i]I^{*}[q]f[k-m-i]f^{*}[k-n-q] + \sum_{q=-\infty}^{\infty} \eta[k-m]I^{*}[q]f^{*}[k-n-q] + \sum_{i=-\infty}^{\infty} I[i]\eta^{*}[k-n]f[k-m-i] + \eta[k-m]\eta^{*}[k-n].$$

(3.17)

Using the statistical properties:

$$E[I[i]I[q]] = \begin{cases} \sigma_I^2 \text{ for } i = q\\ 0 \text{ for } i \neq q, \end{cases}$$

$$E[I[i]\eta[q]] = E[I^*[i]\eta[q]] = \begin{cases} 0 & \text{for all} \quad i \& q, \end{cases}$$

and

$$E[\eta[i]\eta^*[q]] = \begin{cases} \sigma_\eta^2 \text{ for } i = q\\ 0 \text{ for } i \neq q, \end{cases}$$

in taking the expectation of equation (3.17) yields

$$E[v[k-m]v^{*}[k-n]] = \sigma_{I}^{2} \sum_{i=-\infty}^{\infty} f[-m-i]f^{*}[-n-i] + \sigma_{\eta}^{2} \delta[n-m]$$

(3.18)

where  $\delta[.]$  is Kronecker delta [21] and

$$\delta[n-m] = \begin{cases} 1 \text{ for } m=n\\ 0 \text{ for } m \neq n. \end{cases}$$

Finally computing the sum over m has

$$\sum_{m=-\infty}^{\infty} c[m] E[v[k-m]v^*[k-n]] = \sigma_I^2 \sum_{i=-\infty}^{\infty} \left\{ \sum_{m=-\infty}^{\infty} c[m] f[-m-i] \right\} f^*[-n-i] + \sigma_\eta^2 \sum_{m=-\infty}^{\infty} c[m] \delta[n-m]$$

(3.19)

and making a change of index variables q = -i, then evaluating  $\sum_{m=-\infty}^{\infty} c[m]\delta[n-m] = c[n]$ , results in

$$\sum_{m=-\infty}^{\infty} c[m] E \Big[ v[k-m] v^*[k-n] \Big] = \sigma_I^2 \sum_{q=-\infty}^{\infty} \Big\{ \sum_{m=-\infty}^{\infty} c[m] f[q-m] \Big\} f^*[q-n] + \sigma_\eta^2 c[n].$$

(3.20)

The sum over m enclosed in  $\{\}$  is the convolution of c[q] and f[q]. Defining  $f_{rev}[n]$  to be the time reversal of f[n], i.e.  $f_{rev}[n] = f[-n]$  has

$$\sum_{m=-\infty}^{\infty} c[m] E \Big[ v[k-m] v^*[k-n] \Big] = \sigma_I^2 \sum_{q=-\infty}^{\infty} \Big\{ c[q] \star f[q] \Big\} f_{rev}^*[n-q] + \sigma_\eta^2 c[n].$$

(3.21)

Clearly the sum over q is a convolution, which allows equation (3.21) to be expressed as

$$\sum_{m=-\infty}^{\infty} c[m] E \Big[ v[k-m] v^*[k-n] \Big] = \sigma_I^2 c[n] \star f[n] \star f_{rev}^*[n]$$

$$+ \sigma_\eta^2 c[n].$$

(3.22)

The next step in the derivation is to find a suitable expression for the left hand side of equation (3.14):

$$v^*[k-n]I[k] = \sum_{q=-\infty}^{\infty} I[k]I^*[q]f^*[k-n-q] + \eta^*[k-n]I[k].$$

(3.23)

Taking the expected value yields

$$E\left[v^{*}[k-n]I[k]\right] = \sigma_{I}^{2}f^{*}[-n]$$

=  $\sigma_{I}^{2}f_{rev}^{*}[n].$  (3.24)

Substituting equation (3.22) and equation (3.24) into equation (3.14) has