# FPGA BASED RECONFIGURABLE BODY AREA NETWORK USING Nios II AND uClinux

A Thesis Submitted

to the College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

$\begin{array}{c} \text{by} \\ \textbf{Anthony Voykin} \end{array}$

Saskatoon, Saskatchewan, Canada

© Copyright Anthony Voykin, April 2013. All rights reserved.

# Permission to Use

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, it is agreed that the Libraries of this University may make it freely available for inspection. Permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professors who supervised this thesis work or, in their absence, by the Head of the Department of Electrical and Computer Engineering or the Dean of the College of Graduate Studies and Research at the University of Saskatchewan. Any copying, publication, or use of this thesis, or parts thereof, for financial gain without the written permission of the author is strictly prohibited. Proper recognition shall be given to the author and to the University of Saskatchewan in any scholarly use which may be made of any material in this thesis.

Request for permission to copy or to make any other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan, Canada S7N 5A9

# Acknowledgments

I would like to thank my advisors Professor Ron Bolton and Professor Francis Bui for providing me with guidance and support necessary to complete my thesis work.

I would also like to thank my colleagues at SIAST for many interesting discussions about my work.

Finally, I would like express my sincere gratitude to my wife Chrissie and children, Abby and Josh, for their understanding and support while I pursued this degree.

# Abstract

This research is focused on identifying an appropriate design for a reconfigurable Body Area Network (BAN).

In order to investigate the benefits and drawbacks of the proposed design, a BAN system prototype was built. This system consists of two distinct node types: a slave node and a master node. These nodes communicate using ZigBee radio transceivers. The microcontroller-based slave node acquires sensor data and transmits digitized samples to the master node. The master node is FPGA-based and runs uClinux on a soft-core microcontroller. The purpose of the master node is to receive, process and store digitized sensor data. In order to verify the operation of the BAN system prototype and demonstrate reconfigurability, a specific application was required.

Pattern recognition in electrocardiogram (ECG) data was the application used in this work and the MIT-BIH Arrhythmia Database was used as the known data source for verification. A custom test platform was designed and built for the purpose of injecting data from the MIT-BIH Arrhythmia Database into the BAN system.

The BAN system designed and built in this work demonstrates the ability to record raw ECG data, detect R-peaks, calculate and record R-R intervals, detect premature ventricular and atrial contractions. As this thesis will identify, many aspects of this BAN system were designed to be highly reconfigurable allowing it to be used for a wide range of BAN applications, in addition to pattern recognition of ECG data.

# Table of Contents

| P             | ermis  | ssion to Use                                   | 1   |

|---------------|--------|------------------------------------------------|-----|

| $\mathbf{A}$  | ckno   | wledgments                                     | ii  |

| $\mathbf{A}$  | bstra  | act                                            | iii |

| Ta            | able ( | of Contents                                    | iv  |

| $\mathbf{Li}$ | st of  | Tables                                         | ix  |

| Li            | st of  | Figures                                        | Х   |

| Li            | st of  | Abbreviations                                  | xiv |

| 1             | Intr   | roduction                                      | 1   |

|               | 1.1    | Motivation                                     | 1   |

|               | 1.2    | Objectives                                     | 2   |

|               | 1.3    | Thesis Organization                            | 3   |

| 2             | Elec   | ctrocardiogram Background                      | 4   |

|               | 2.1    | Electromechanical Operation of the Human Heart | 4   |

|               |        | 2.1.1 ECG Electrical Characteristics           | 6   |

|               |        | 2.1.2 Description of Fiducial Points           | 7   |

| 3             | Boo    | ly Area Networks                               | 12  |

|               | 3.1    | Introduction                                   | 12  |

|               | 3.2    | Challenges                                     | 14  |

|               |        | 3.2.1 Network Architecture                     | 14  |

|   |     | 3.2.2   | Hardware Selection                  | 16 |

|---|-----|---------|-------------------------------------|----|

|   |     | 3.2.3   | Software Architecture               | 21 |

|   |     | 3.2.4   | Wireless Protocol                   | 24 |

| 4 | Sys | tem A   | rchitecture                         | 29 |

|   | 4.1 | Electro | ocardiogram Analog Front End        | 31 |

|   |     | 4.1.1   | Block Diagram                       | 31 |

|   |     | 4.1.2   | Schematic                           | 32 |

|   |     | 4.1.3   | ECG AFE Testing                     | 38 |

|   |     | 4.1.4   | Design Considerations               | 39 |

|   | 4.2 | Digita  | l Transmitter                       | 41 |

|   |     | 4.2.1   | Block Diagram                       | 42 |

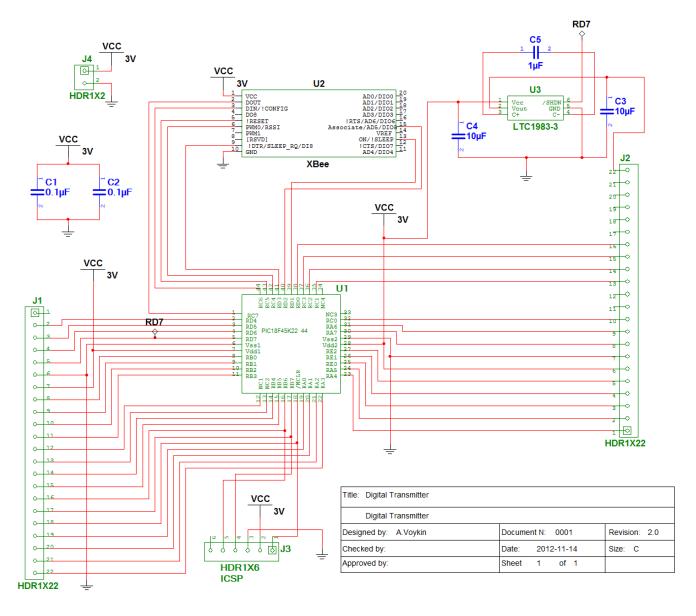

|   |     | 4.2.2   | Schematic                           | 42 |

|   |     | 4.2.3   | Software                            | 46 |

|   |     | 4.2.4   | Design Considerations               | 49 |

|   | 4.3 | Field l | Programmable Gate Array Server      | 54 |

|   |     | 4.3.1   | Block Diagram                       | 55 |

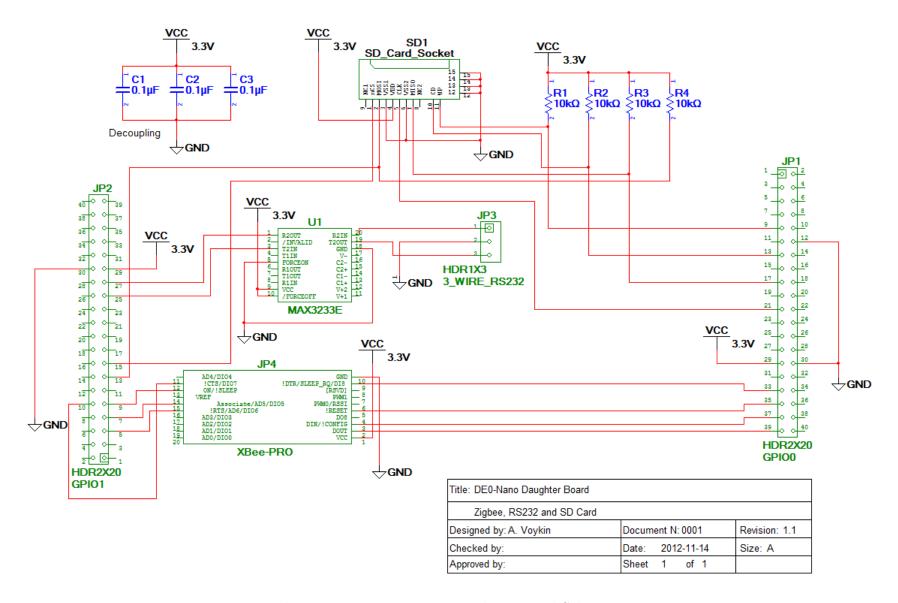

|   |     | 4.3.2   | DE0-Nano Daughter Board Schematic   | 56 |

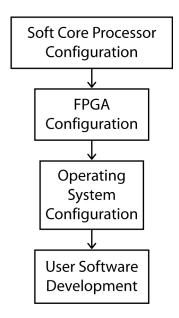

|   |     | 4.3.3   | System Configuration                | 60 |

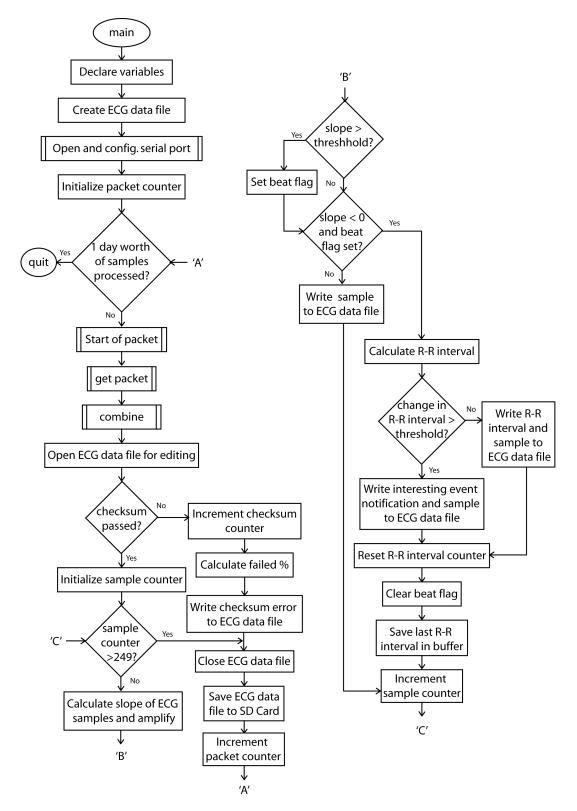

|   |     | 4.3.4   | User Software                       | 66 |

|   |     | 4.3.5   | User Software Drawbacks and Benefit | 75 |

|   | 4.4 | System  | n Reconfigurability                 | 76 |

| 7 | Fut | ure W  | ork and Conclusions                        | 100 |

|---|-----|--------|--------------------------------------------|-----|

|   | 6.2 | Contr  | ibutions                                   | 99  |

|   | 6.1 | Summ   | nary                                       | 95  |

| 6 | Sun | nmary  | and Contributions                          | 95  |

|   |     | 5.3.3  | Interesting Event Detection                | 93  |

|   |     | 5.3.2  | R-R Intervals                              | 91  |

|   |     | 5.3.1  | Acquired ECG Data                          | 90  |

|   | 5.3 | Test F | Results                                    | 90  |

|   |     | 5.2.5  | Preparation of the Sample Buffer           | 89  |

|   |     | 5.2.4  | Adjustment of the MIT-BIH Database Samples | 88  |

|   |     | 5.2.3  | Software                                   | 84  |

|   |     | 5.2.2  | Hardware                                   | 83  |

|   |     | 5.2.1  | Block Diagram                              | 83  |

|   | 5.2 | Test F | Platform                                   | 82  |

|   | 5.1 | MIT-I  | BIH Arrhythmia Database                    | 81  |

| 5 | Tes | t Resu | ılts                                       | 81  |

|   |     | 4.4.5  | FPGA Server Hardware                       | 79  |

|   |     | 4.4.4  | ECG Mote Sensor                            | 79  |

|   |     | 4.4.3  | Digital Transmitter Firmware               | 78  |

|   |     | 4.4.2  | Network Topology                           | 78  |

|   |     | 4.4.1  | FPGA Server User Software                  | 76  |

|              | 7.1   | Future Work                                                        | 100  |

|--------------|-------|--------------------------------------------------------------------|------|

|              | 7.2   | Conclusions                                                        | 100  |

| Re           | efere | nces                                                               | 103  |

| $\mathbf{A}$ | FPC   | GA Server System Development                                       | 112  |

|              | A.1   | Ubuntu Installation                                                | 112  |

|              | A.2   | uClinux Distribution                                               | 113  |

|              | A.3   | Quartus II Installation on Ubuntu                                  | 114  |

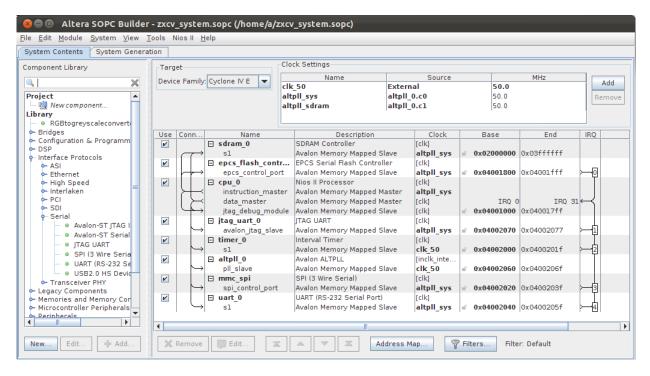

|              | A.4   | System Development with Quartus II and SOPC Builder                | 115  |

|              | A.5   | Building the uClinux Boot Image                                    | 123  |

|              | A.6   | Configuring the FPGA and Writing the Configuration to Flash Memory | 7126 |

|              | A.7   | Customizing the uClinux Boot Sequence                              | 128  |

|              | A.8   | Setting up the System to Boot from EPCS Flash Memory               | 129  |

|              | A.9   | Developing User Software                                           | 129  |

| В            | FPC   | GA Pin Assignments                                                 | 131  |

| $\mathbf{C}$ | XBe   | ee Configuration                                                   | 133  |

| D            | Scho  | ematics                                                            | 135  |

| ${f E}$      | Bill  | of Materials                                                       | 140  |

| $\mathbf{F}$ | PCI   | 3 Artwork                                                          | 144  |

| $\mathbf{G}$ | Soft  | ware                                                               | 148  |

|              | G.1   | MIT-BIH Parsing Engine                                             | 148  |

|              | G.2   | Test Platform C Code                                               | 149  |

| Ι | Truncation Noise                        | 180 |

|---|-----------------------------------------|-----|

| Н | System Specifications                   | 177 |

|   | G.5 Digital Transmitter Firmware        | 166 |

|   | G.4 FPGA Server User Software           | 159 |

|   | G.3 FPGA Server Top Level Design Entity | 157 |

# List of Tables

| 2.1 | ECG Signal Characteristics                        | 7   |

|-----|---------------------------------------------------|-----|

| 3.1 | Comparison of Low Power Wireless Technologies     | 27  |

| 4.1 | Required Bandwidth for ECG Systems                | 36  |

| 4.2 | DE0-Nano Development and Education Board Hardware | 56  |

| 4.3 | List of Software Used to Develop BAN System       | 61  |

| 4.4 | File Extensions Used in System Development        | 65  |

| 4.5 | Data Supporting R-peak Identification Example     | 73  |

| 5.1 | R-R Interval Test Data                            | 93  |

| E.1 | DE0-Nano Daughter Board BOM                       | 141 |

| E.2 | ECG AFE BOM                                       | 142 |

| E.3 | Digital Transmitter BOM                           | 143 |

# List of Figures

| 2.1 | Human Heart, from $[1]$                                    | 4  |

|-----|------------------------------------------------------------|----|

| 2.2 | Conduction System of the Heart, from [2]                   | 5  |

| 2.3 | Normal ECG Signal, from [3]                                | 8  |

| 2.4 | Illustration of an R-R Interval                            | 8  |

| 2.5 | Examples of a Sinus Rhythm and a PVC                       | 9  |

| 2.6 | PVC and Normal Sinus Rhythms                               | 10 |

| 2.7 | Frequency Spectrum of Sinus Rhythm and PVC                 | 10 |

| 2.8 | Illustration of R-R Interval in the Presence of a PAC      | 11 |

| 3.1 | Mote block diagram                                         | 13 |

| 3.2 | Typical BAN System Architecture                            | 16 |

| 4.1 | Photograph of System Nodes; a) ZigBee Mote; b) FPGA Server | 29 |

| 4.2 | ECG AFE Photo                                              | 31 |

| 4.3 | ECG AFE Block Diagram                                      | 32 |

| 4.4 | ECG AFE Schematic                                          | 33 |

| 4.5 | HPF Frequency Response                                     | 34 |

| 4.6 | LPF Frequency Response                                     | 35 |

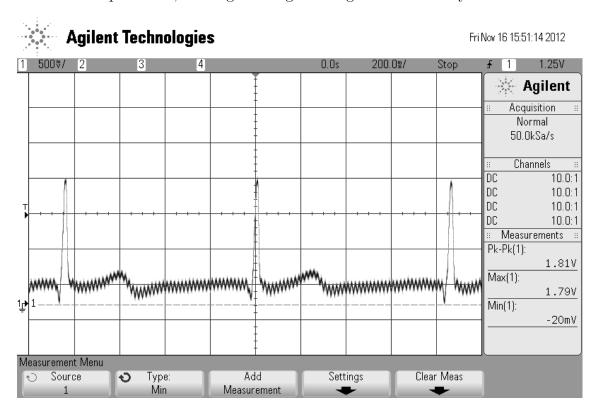

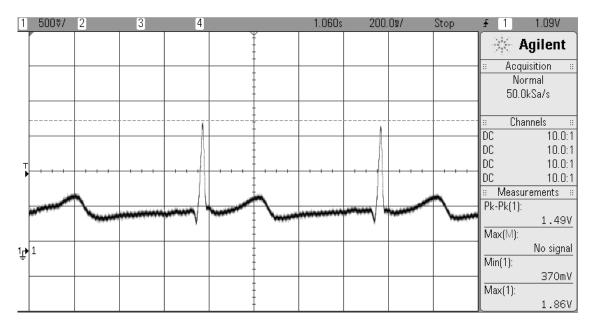

| 4.7 | ECG AFE Oscilloscope Graphic                               | 38 |

| 4.8 | Illustration of 60Hz Noise                                 | 40 |

| 4.9 | Digital Transmitter Photo                                  | 41 |

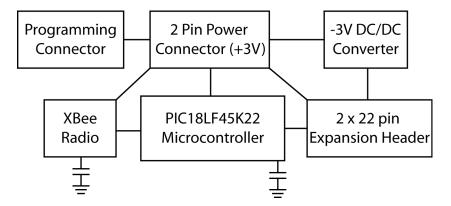

| 4.10 | Digital Transmitter Block Diagram                          | 42 |

|------|------------------------------------------------------------|----|

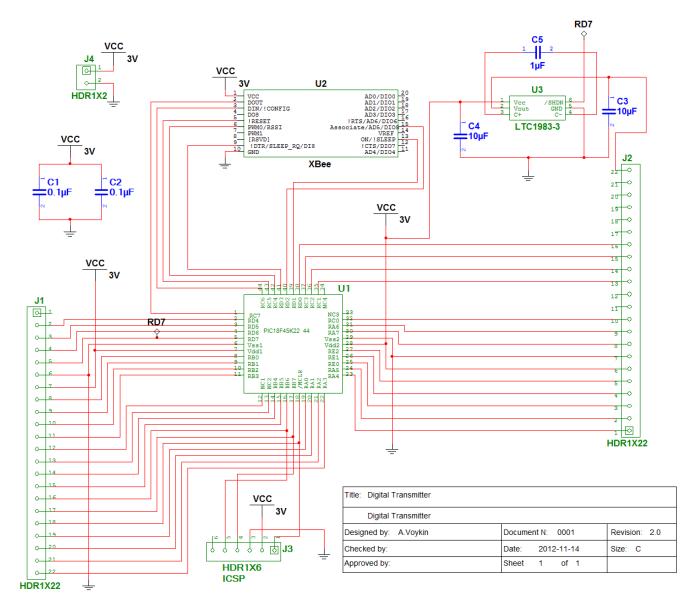

| 4.11 | Digital Transmitter Schematic                              | 43 |

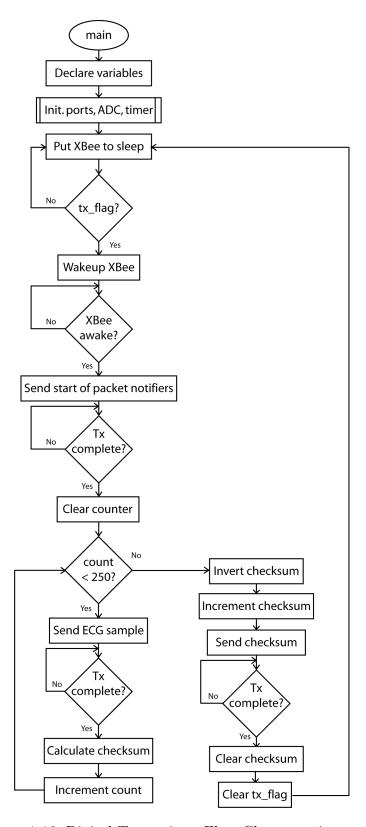

| 4.12 | Digital Transmitter Flow Chart - main program              | 47 |

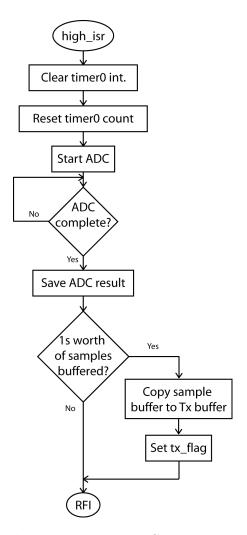

| 4.13 | Digital Transmitter Flow Chart - interrupt service routine | 49 |

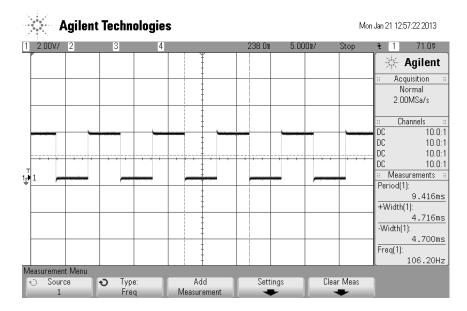

| 4.14 | PIC18LF45K22 sleep period                                  | 51 |

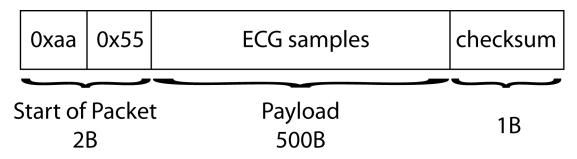

| 4.15 | ECG Mote Packet Design                                     | 52 |

| 4.16 | Modular Checksum Example                                   | 53 |

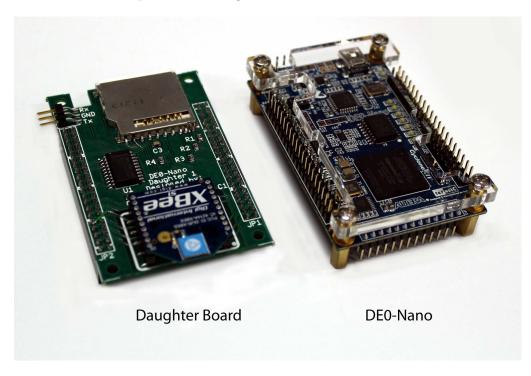

| 4.17 | FPGA Server photo                                          | 54 |

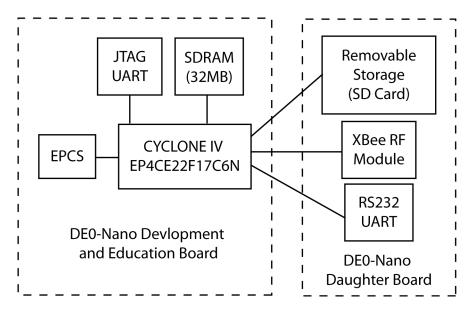

| 4.18 | FPGA Server Block Diagram                                  | 55 |

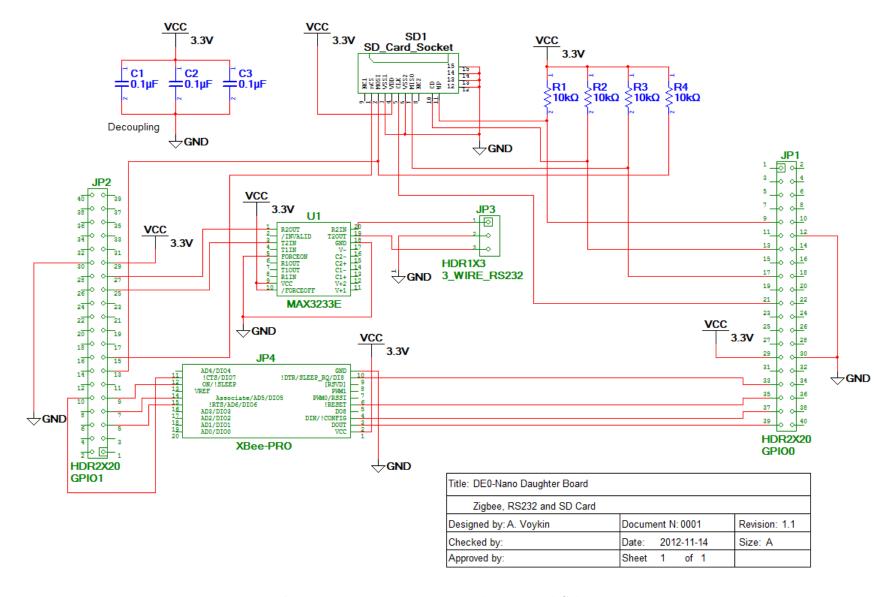

| 4.19 | DE0-Nano Daughter Board Schematic                          | 58 |

| 4.20 | FPGA Server Configuration Flow Diagram                     | 63 |

| 4.21 | FPGA Server User Software Flow Chart - main()              | 67 |

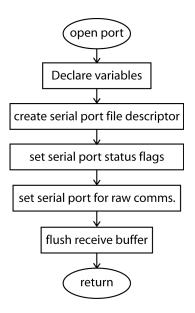

| 4.22 | open_port() Flow Chart                                     | 68 |

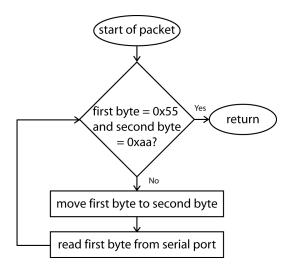

| 4.23 | start_of_packet() Flow Chart                               | 69 |

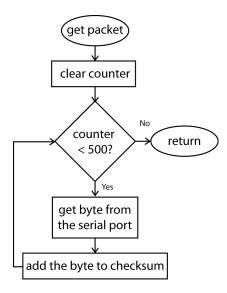

| 4.24 | get_packet() Flow Chart                                    | 70 |

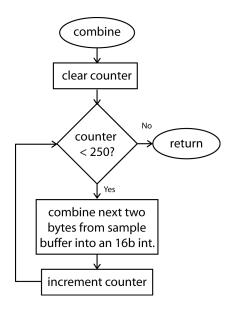

| 4.25 | combine() Flow Chart                                       | 71 |

| 4.26 | Illustration of R-peak Detection                           | 72 |

| 4.27 | PVC and Normal Sinus Rhythms                               | 74 |

| 4.28 | Removal of Baseline Drift in $y[n]$                        | 77 |

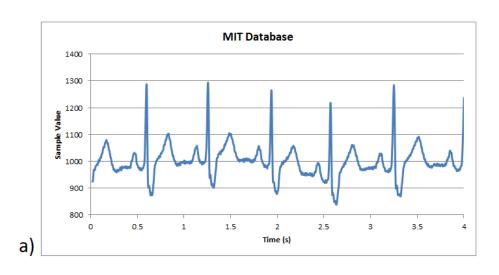

| 5.1  | Typical MIT-BIH Arrhythmia Database Data file              | 82 |

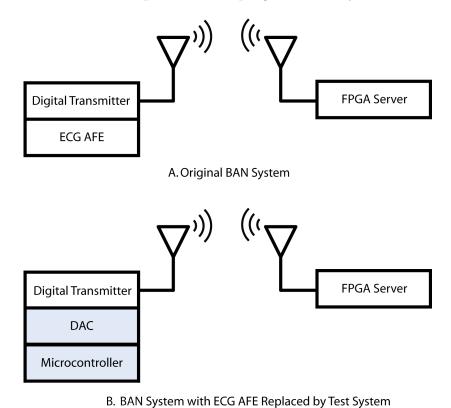

| 5.2  | Test System Block Diagram                                  | 84 |

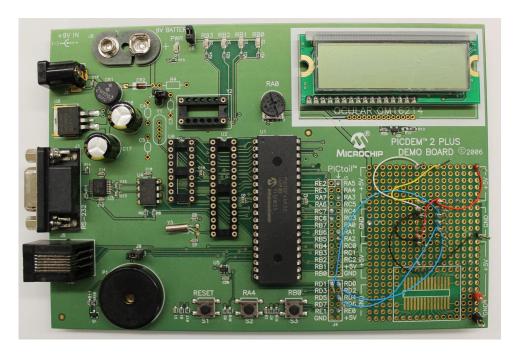

| 5.3  | PICDEM 2 PLUS DEMO BOARD                                     | 85  |

|------|--------------------------------------------------------------|-----|

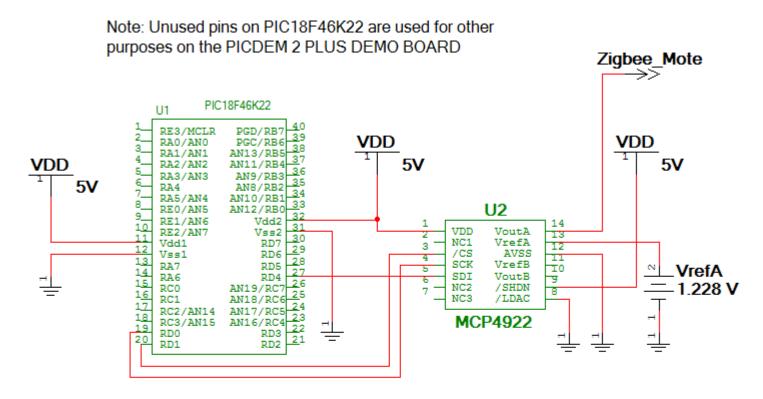

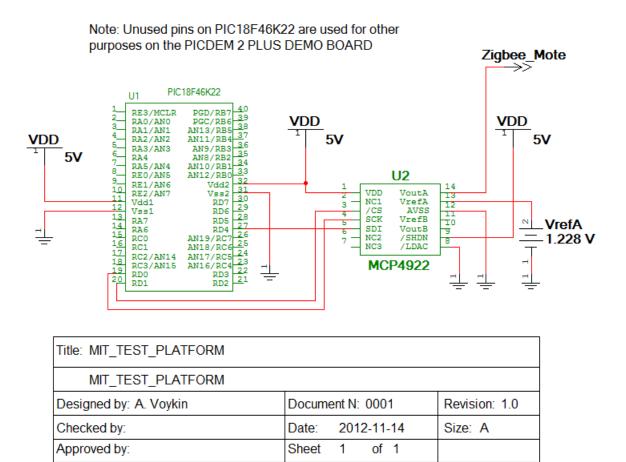

| 5.4  | Test Platform Schematic                                      | 86  |

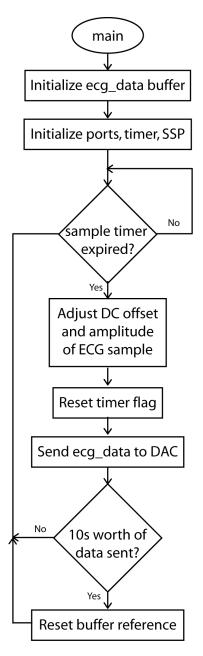

| 5.5  | Test Platform Software Flow Chart                            | 87  |

| 5.6  | Baseline Generated Using Human Subject and ECG AFE           | 89  |

| 5.7  | MIT-BIH Arrhythmia Database 213 Output From Test Platform    | 90  |

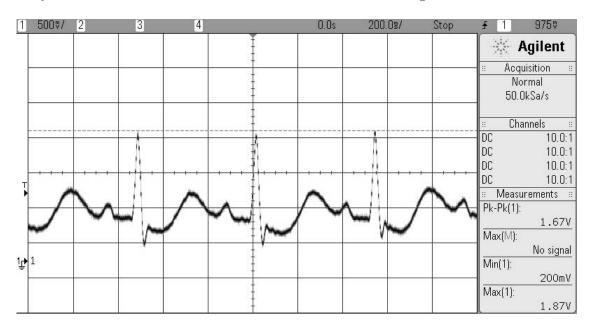

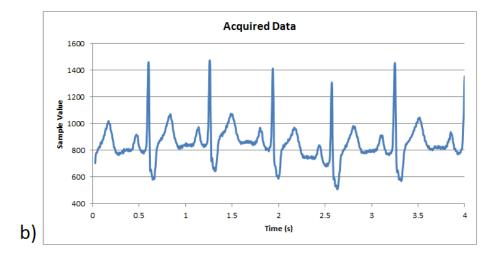

| 5.8  | MIT-BIH Arrhythmia Database vs. Data in Test System Software | 91  |

| 5.9  | MIT212 Acquired vs Raw Samples                               | 92  |

| 5.10 | MIT223 Interesting Events 1:00 to 1:20                       | 94  |

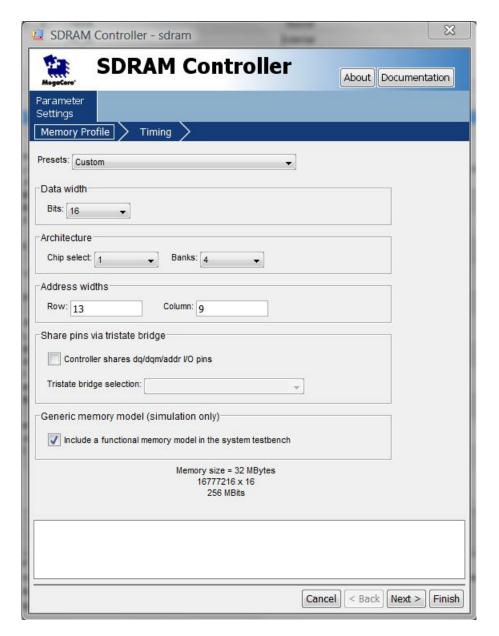

| A.1  | SDRAM Memory Profile                                         | 118 |

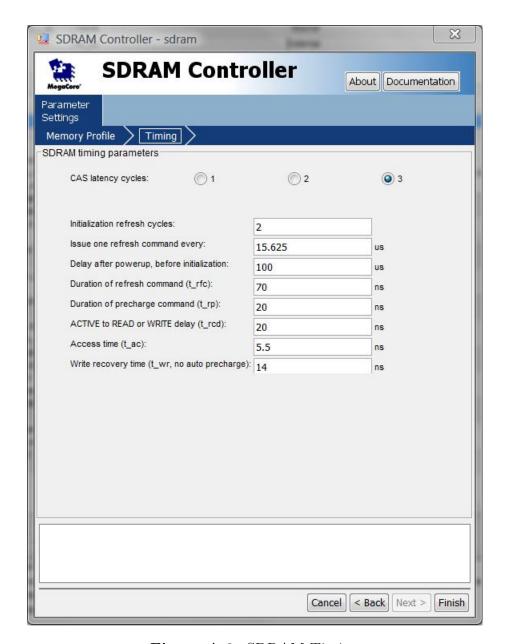

| A.2  | SDRAM Timing                                                 | 119 |

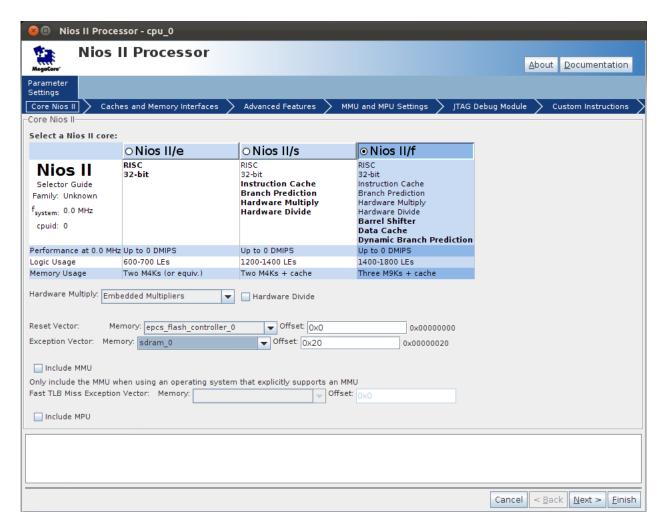

| A.3  | Nios II Configuration                                        | 120 |

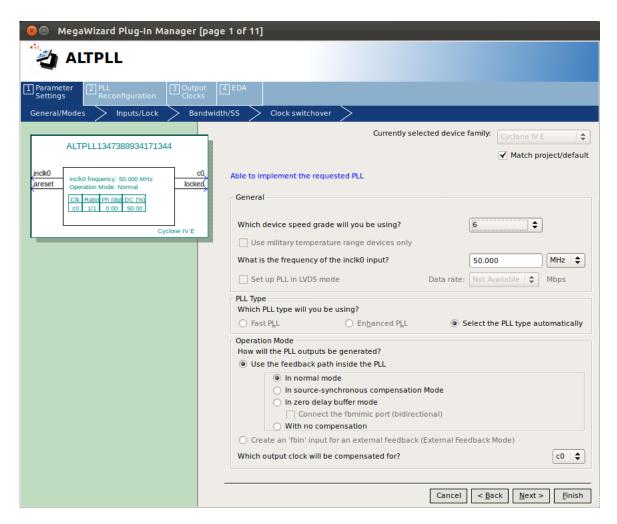

| A.4  | PLL Configuration page 1                                     | 121 |

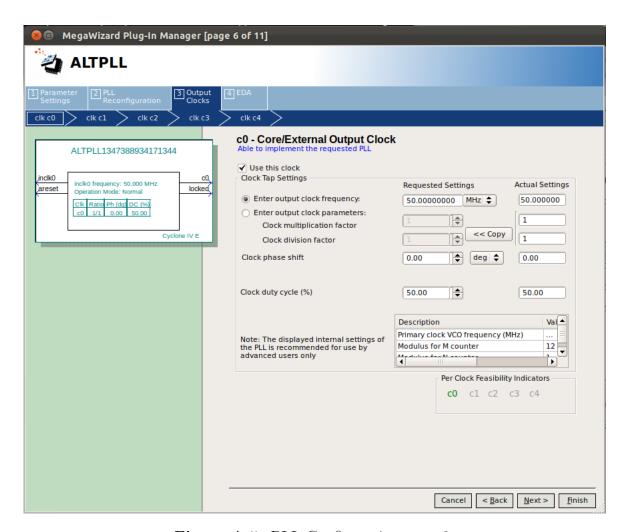

| A.5  | PLL Configuration page 6                                     | 122 |

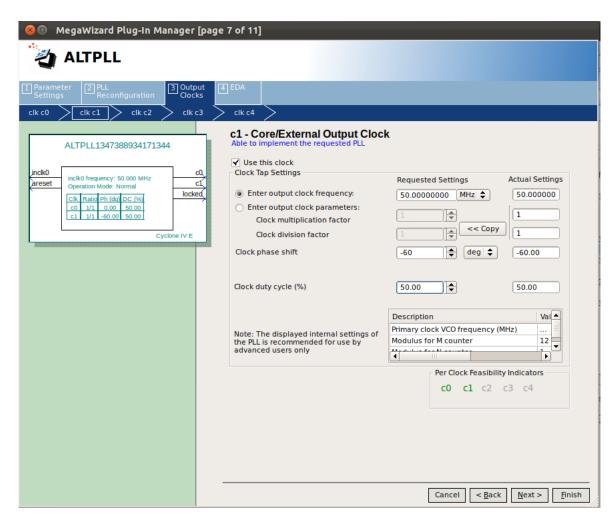

| A.6  | PLL Configuration page 7                                     | 123 |

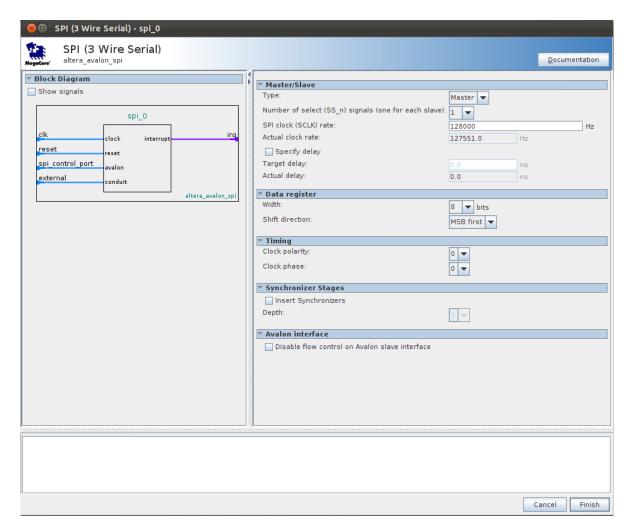

| A.7  | SPI (3 Wire Serial) Configuration                            | 124 |

| A.8  | SOPC Builder System Configuration                            | 125 |

| A.9  | nios2-configure-sof Output                                   | 127 |

| A.10 | sof2flash Output                                             | 127 |

| A.11 | nios2-flash-programmer Output                                | 128 |

| A.12 | Booting uClinux                                              | 130 |

| B.1  | FPGA Server Pin Assignments                                  | 132 |

| D.1 | DE0-Nano Daughter Board Schematic | 136 |

|-----|-----------------------------------|-----|

| D.2 | ECG AFE Schematic                 | 137 |

| D.3 | Digital Transmitter Schematic     | 138 |

| D.4 | Test Platform Schematic           | 139 |

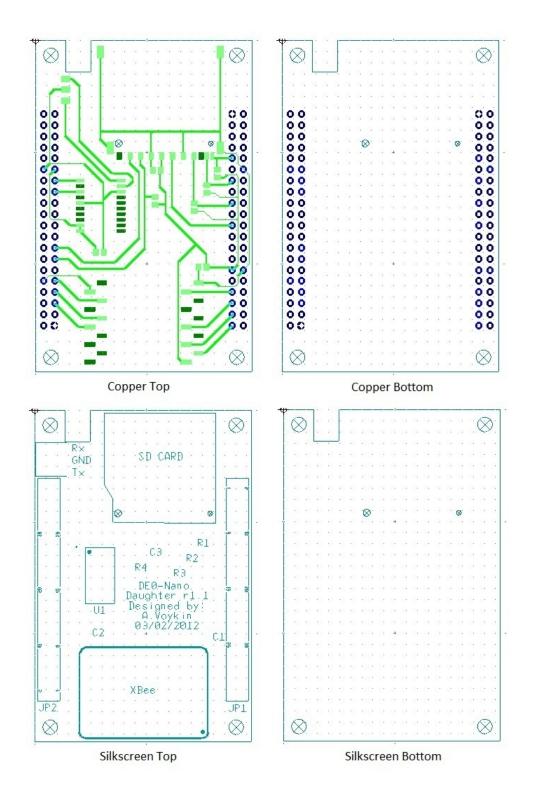

| F.1 | DE0-Nano Daughter Board           | 145 |

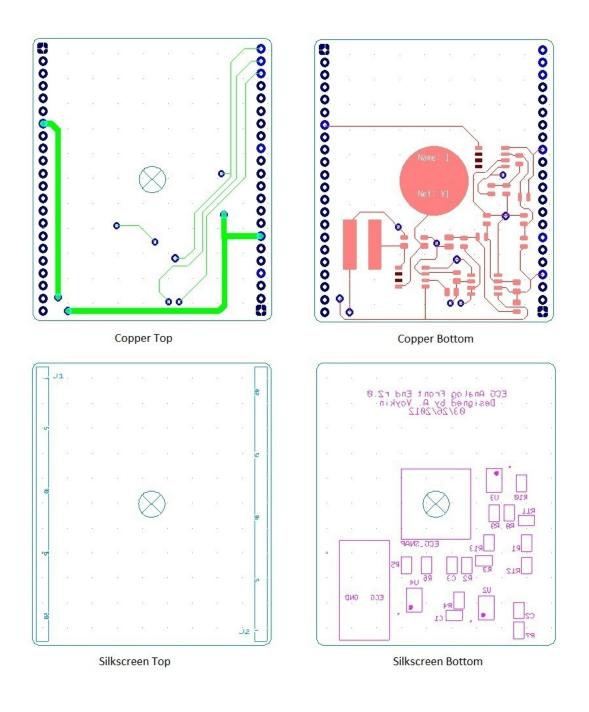

| F.2 | ECG AFE                           | 146 |

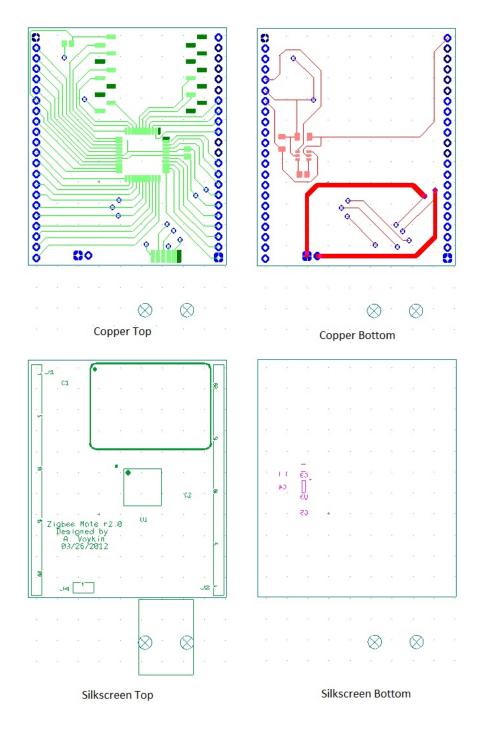

| F.3 | Digital Transmitter               | 147 |

# List of Abbreviations

ADC Analog to Digital Converter

AES Advanced Encryption Standard

AFE Analog Front End

AP Action Potential

APB Arterial Premature Beat

APS Application Support Sublayer

ASCII American Standard Code for Information Interchange

ASIC Application Specific Integrated Circuit

AT Attention

ATM Automated Teller Machine

ATV Atrioventricular

BAN Body Area Network

BLE Bluetooth Low Energy

BOM Bill of Materials

BPM Beats Per Minute

BSN Body Sensor Network

CMRR Common Mode Rejection Ratio

COTS Common Off The Shelf

CPLD Complex Programmable Logic Device

DAC Digital to Analog Converter

dB Decibels

ECG Electrocardiogram, Electrocardiography or Electrocardiograph

EDS Embedded Design Suite

EEG Electroencephalography

FHSS Frequency Hopping Spread Spectrum

FPGA Field Programmable Gate Array

FP Floating Point

GCC GNU Compiler Collection

GNU GNU's Not Unix

GPIO General Purpose Input Output

GPRS General Packet Radio Service

GUI Graphical User Interface

HDL Hardware Description Language

HPF High Pass Filter

HR Heart Rate

HRV Heart Rate Variability

IC Integrated Circuit

ICSP In Circuit Serial Programer

IDE Integrated Development Environment

INA Instrumentation Amplifier

ISM Industrial, Scientific and Medical

ISR Interrupt Service Routine

JTAG Joint Test Action Group

LA Left Atruim

LPF Low Pass Filter

LR-PAN Low Rate Personal Area Network

LV Left Ventricle

MAC Media Access Control

DMIPS Dhrystone Million Instructions Per Second

MISO Master In Slave Out

MLII Modified Limb Lead II

MMU Memory Management Unit

MOSI Master Out Slave In

MSSP Master Synchronous Serial Port

MSE Mean Squared Error

OS Operating System

PAC Premature Atrial Contraction

PCB Printed Circuit Board

PC Personal Computer

PHY Physical layer

PLL Phase Locked Loop

PVC Premature Ventricular Contraction

RA Right Atruim

RISC Reduced Instruction Set Computer

RF Radio Frequency

RTL Register Transfer Level

RTOS Real Time Operating System

RV Right Ventricle

SA Sinoatrial

SD Secure Digital

SIG Special Interest Group

SNR Signal to Noise Ratio

SRAM Static Random Access Memory

SOPC System on a Programmable Chip

SPI Serial Peripheral Interface

TC Trust Center

TQFP Thin Quad Flat Pack

TR Truncated Result

UART Universal Asynchronous Receiver Transmitter

UWB Ultra Wide Band

WBAN Wireless Body Area Network

WBSN Wireless Body Sensor Network

WiFi Wireless Fidelity

WPAN Wireless Personal Area Network

WSN Wireless Sensor Network

# 1. Introduction

Envision a world where adverse health conditions could be identified in realtime and relevant information could be communicated to physicians before health problems become deadly. The potential life saving possibilities are very exciting. This work strives to contribute to the foundation that could make this feasible.

### 1.1 Motivation

Nearly everyone experiences heart palpitations at some point in their life. A heart palpitation is an irregular heart beat, often described as a skipped beat. A patient experiencing frequent heart palpitations may plan a visit to his/her family doctor. This typically results in a routine test where the heart's electrical impulses are graphed and viewed by a doctor and sent to a specialist for further analysis. This is followed by several weeks, if not months, waiting for results. A likely scenario after receiving the test results could be additional specialized tests such as, wearing a Holter monitor for a day or more, an echocardiogram (i.e., a specialized ultrasound of the heart), or stress tests while monitoring the heart's electrical response. Specialized testing can take months to be scheduled due to lengthy wait lists and may be uncomfortable and/or inconvenient for the patient. It is plausible to suggest that over an extended period of time a heart condition that seemed relatively benign to the patient could escalate to become a serious health condition. While heart palpitations may not be considered life threatening, a patient with heart disease may be unaware of looming health problems until it's too late. The question is, with the appropriate application of technology could these scenarios and possibly many other serious health conditions be avoided or proactively addressed?

A typical Body Area Network (BAN) locates sensors in or on the human body to collect vital sign and motion data and provide feedback to the user based on the measured data. A BAN designed to measure vital signs and report abnormalities to the user potentially has lifesaving possibilities. The possibility to save lives is certainly not the only benefit provided through the use of BANs. Athletes outfitted with sensors that gather motion, orientation and vital sign data, coupled with a tool that can process the data and provide real-time feedback would be a very valuable training asset. In another example, a patient undergoing physiotherapy could use the same sensors to provide therapists with the data required to assess recovery and proactively adjust therapeutic plans.

There are many applications in many different fields that will benefit from the use of BANs. Quality of life can be improved and lives can possibly be saved. This research is motivated by the potential impact it will have on human lives.

# 1.2 Objectives

BAN systems are currently being researched in many different applications, such as health care, athletics and entertainment. With each different application comes a distinct set of requirements. In order to accommodate a diverse field of applications, a highly reconfigurable BAN system is proposed. The primary objective of this research is to identify the most appropriate design for such a system. In light of the above challenges, the research objectives are:

- 1. Review the current state of BAN research through a literature review and identify opportunities to contribute to this research.

- 2. Determine the most appropriate wireless protocol and network, hardware and software architectures to use in a reconfigurable BAN.

- 3. Identify a suitable application to demonstrate a reconfigurable BAN system.

- 4. Verify the BAN system operation using a standardized data source.

- 5. Demonstrate reconfigurability of the final BAN system.

The chapters within this thesis will fully describe how each of these objectives is accomplished.

# 1.3 Thesis Organization

Following this introduction, this thesis continues in Chapter 2 with a description of the mechanics of the heart, the heart electrical system, the method used to record the electrical impulses from the heart and some of the abnormalities within these recordings. Chapter 3 contains a review of current research work in the field of BANs. Chapter 4 provides a detailed description of the BAN system realized through this research, including the details of system reconfigurability. Chapter 5 contains a detailed review of the test results. Chapter 6 summarizes this thesis and provides a listing of the contributions of this work. Chapter 7 concludes this thesis and suggests opportunities for future work.

# 2. Electrocardiogram Background

This chapter contains a discussion of the mechanics of the heart including the heart electrical system, a description of how the electrical impulses from the heart are captured and viewed as well as an explanation of interesting cardiac events that are pertinent to this research.

# 2.1 Electromechanical Operation of the Human Heart

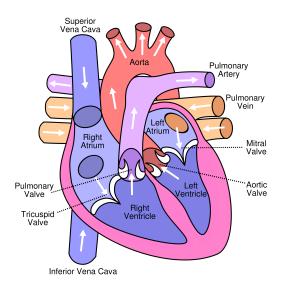

The heart is a pump that is responsible for maintaining blood flow in the body. The heart contains four chambers: right atrium (RA), right ventricle (RV), left atrium (LA), left ventricle (LV) and a series of one way valves, as shown in Figure 2.1. These chambers and valves aid in the collection and distribution of blood throughout the body. In order to move blood throughout the body the heart muscle contracts, or

Figure 2.1 Human Heart, from [1]

beats. The atria contract first, followed by the ventricles. Prior to a heartbeat, deoxygenated blood enters the RA via the superior vena cava and the inferior vena cava. At the same time, oxygenated blood returns from the lungs via the pulmonary veins and enters the LA. The atria then contract expelling blood into the ventricles. After a brief delay, the ventricles also contract. When the ventricles contract the one-way valves between the atria and the ventricles close. The contraction of the RV forces the deoxygenated blood out of the heart to the lungs and the contraction of the LV forces oxygenated blood to the rest of the body via the aorta. The atria and ventricles are muscles and in order for these muscle to contract an electrical stimulus is required.

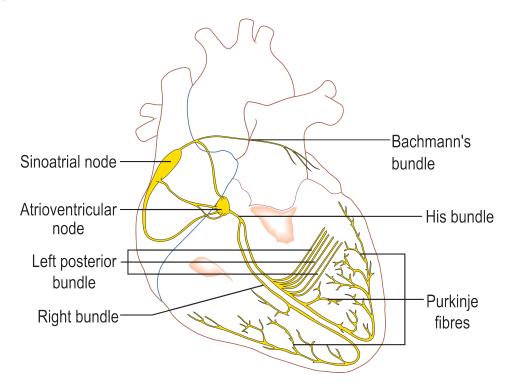

Figure 2.2 Conduction System of the Heart, from [2]

The sinoatrial (SA) node, shown in Figure 2.2 is located in the RA and is responsible for generating the electrical impulses that control the normal rhythm of the heart, as described by Boston Scientific [4]. An electrical impulse generated by the SA node cause the atria to contract. This electrical impulse then moves to the atrioventricular (AV) node through the wires in the heart, also known as the conduction

pathways. The AV node delays the electrical impulse slightly, allowing the ventricles to fill with blood. Following this delay the electrical impulse is distributed to the ventricles via the right and left bundle branches, which causes ventricular contraction. The movement of charge related to this electrical impulse can be captured with an electrocardiograph.

### 2.1.1 ECG Electrical Characteristics

An electrocardiograph (ECG) is a device that can measure the electrical characteristics of the heart. The device uses at least two electrodes attached to the human body. It measures the voltage difference between these electrodes and records the voltage over time to produce an electrocardiogram (ECG). Electrodes are used to connect the human body to an electrical circuit because the surface of the body is not highly conductive. The electrodes are typically attached to the torso near the heart and the differential voltage measured between them is referred to as a lead.

At this point, a recurring abbreviation needs to be clarified: ECG refers to electrocardiogram, electrocardiography and electrocardiograph. An electrocardiogram is both a graph of the change in differential voltage on the body surface vs. time, as a result of the electrical impulses created when the heart beats and it is also used to refer to the test that generates the graph. Electrocardiography refers to the study of electrocardiograms as well as the science of capturing the electrocardiogram. Finally, an electrocardiograph is the tool used to generate an electrocardiogram. The abbreviation ECG is used throughout this paper and the context that it is used will determine its meaning.

In order to generate an ECG, the signal parameters need to be clearly understood. According to Company-Bosch et. al. and Soundarapandian et. al. [5,6], the ECG signal characteristics are summarized in Table 2.1. On the surface of the body, the AC signal from the heart is typically in the range of 0.5 to 5mV peak to peak. The frequency components lie between 0.05 and 150Hz. Added to the low level AC signal is a DC offset of up to  $\pm 300$ mV. The offset is due to the difference in impedance between

each electrode-to-body contact. Finally, a common mode voltage of up to 1.5V may be present. The common mode signal is primarily due to power line interference when coupled to an AC power source but may also be caused by Radio Frequency (RF) or microwave interference sources.

Table 2.1

ECG Signal Characteristics

| Quantity            | Value                      |

|---------------------|----------------------------|

| AC Signal           | 0.5  to  5mV               |

| DC Offset           | $\pm 300 \mathrm{mV}$      |

| Common Mode Voltage | up to 1.5V                 |

| Frequency Range     | $0.05$ to $150\mathrm{Hz}$ |

In addition to these design constraints, the DC voltage between the electrodes can change due to changes in the electrode-skin impedance. This phenomenon is known as "baseline drift" and is generally caused by movement, changes in skin surface moisture and aging of electrodes [7]. If not addressed, baseline drift can saturate the output of an ECG Analog Front End, causing loss of valuable ECG information. When all of the design constraints have been accounted for the electrical impulses from the heart can be captured and analyzed.

# 2.1.2 Description of Fiducial Points

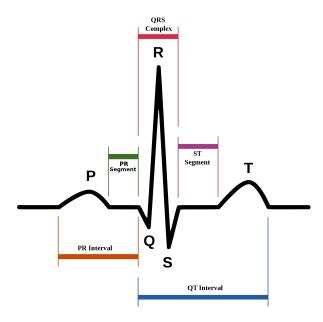

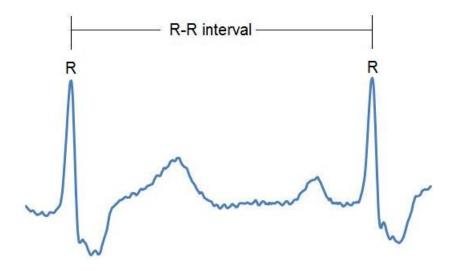

The ECG of a normal heart beat, also known as a normal sinus rhythm or sinus rhythm is shown in Figure 2.3. The QRS complex occurs due to the depolarization of the ventricles and is normally 60 to 100ms in duration according to Klabunde [8]. The highest peak in the QRS complex is referred to as the R-peak. An R-R interval, shown in Figure 2.4, is defined as the time between R-peaks. For example, a resting heart rate of 60 beats per minute equates to an R-R interval of 1 second. The inverse of the R-R interval is a measure of the instantaneous Heart Rate (HR), as shown in Equation (2.1)

$$HR(Beats Per Minute) = \frac{60 \text{ sec/min}}{R-R \text{ interval(sec/beat)}}.$$

(2.1)

Figure 2.3 Normal ECG Signal, from [3]

Figure 2.4 Illustration of an R-R Interval

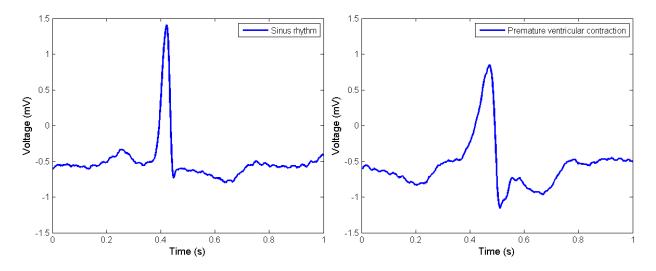

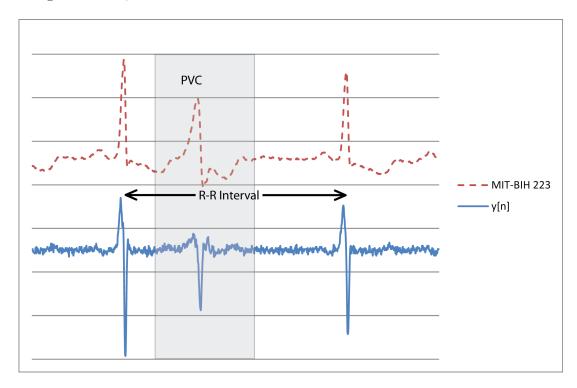

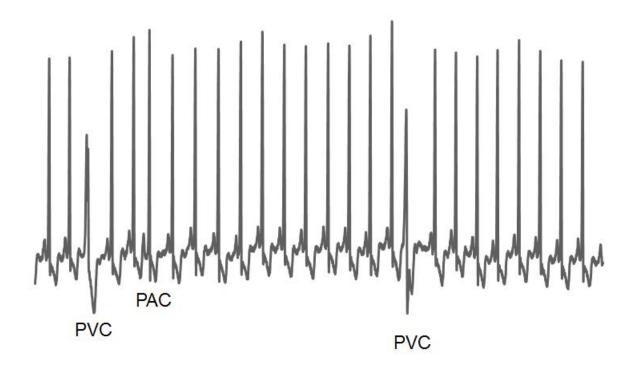

A graph of many heart beats plotted over time is used to analyze heart health. Not all beats are normal sinus rhythm beats. An abnormal event that occurs in some individuals is called a premature ventricular contraction (PVC). A PVC occurs when the ventricles contract before the atria. An example of a PVC alongside a normal sinus rhythm is shown in Figure 2.5. The PVC is characterized by having a longer than usual QRS complex (i.e. greater than 120ms) an unusual shape, according to

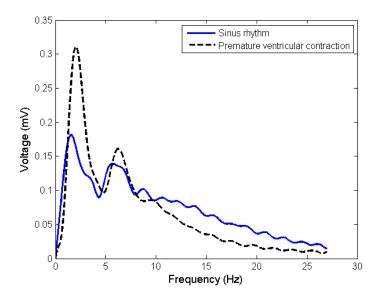

Keany et al. [9]. In most cases PVCs are no indication of extenuating health problems. However in patients with existing heart disease PVCs should be carefully monitored. A trait of the PVC that is particularly useful in identifying it is that it doesn't contain the same high frequency components as a normal QRS complex.

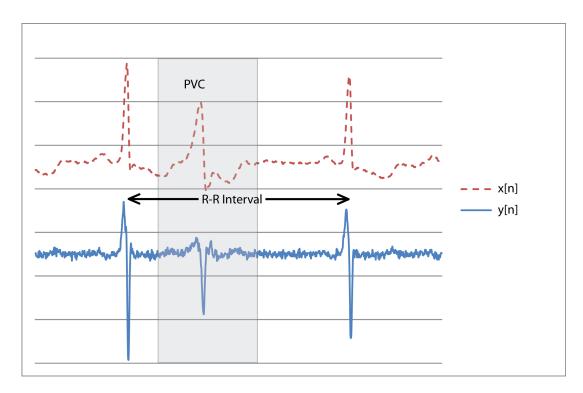

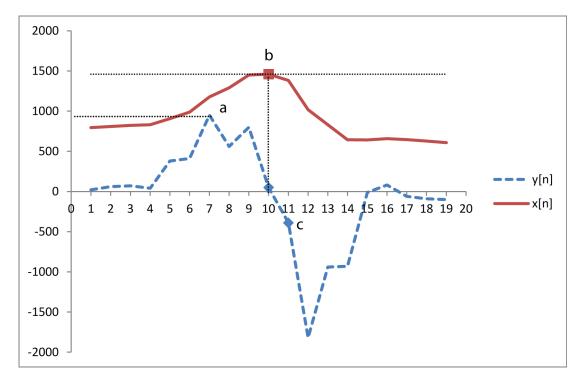

Figure 2.5 Examples of a Sinus Rhythm and a PVC

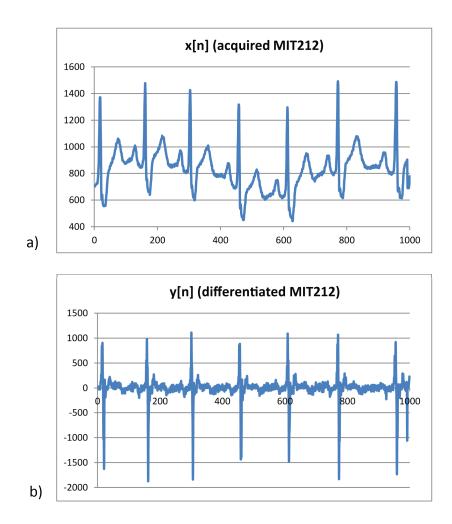

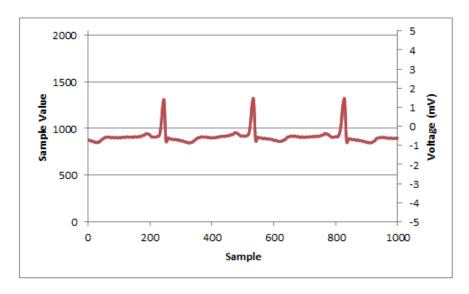

Signal power for a PVC event is concentrated below 10Hz while a normal QRS complex has more signal power in the higher frequencies, as shown in Figure 2.7. This trait can be used to distinguish normal sinus rhythms and PVCs. For example, the ratio of adjacent R-R intervals in an ECG containing normal sinus rhythms is approximately 1. If the peak of the PVC waveform is not classified as an R-peak the result is an R-R interval twice as long as the underlying sinus rhythm. The ratio of adjacent R-R intervals can then be used identify the occurrence of a PVC. This is done by filtering out the low frequency component of the ECG waveform. Figure 2.6 provides an illustration of two normal sinus rhythms surrounding a PVC, x[n], as well as the filtered waveform, y[n]. Once the waveform is filtered a threshold can be applied to the level of the filtered waveform to detect normal sinus rhythms and ignore PVCs.

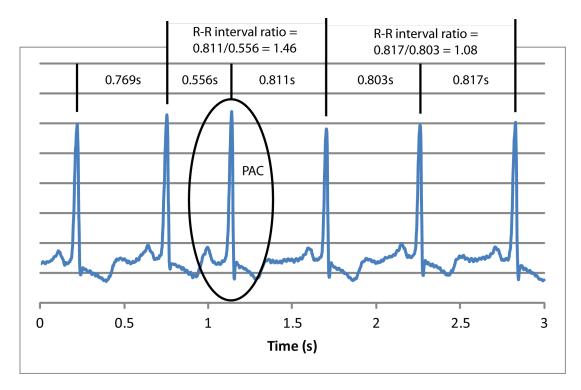

Another abnormal event that has symptoms similar to a PVC is called a premature atrial contraction (PAC). In a PAC event the heart beats prematurely with what

Figure 2.6 PVC and Normal Sinus Rhythms

Figure 2.7 Frequency Spectrum of Sinus Rhythm and PVC

appears to be a normal sinus rhythm, as shown in Figure 2.8. Similar to identifying a PVC, PACs can be detected comparing adjacent R-R intervals and flagging significant differences. The R-R interval ratio in the presence of a PAC is greater than 1 but less than 2, as shown in Figure 2.8.

Figure 2.8 Illustration of R-R Interval in the Presence of a PAC

Identifying R-peaks, PVCs, PACs or other fiducial points and abnormal events can be done using a Body Area Network (BAN). A description of BANs, including the challenges associated with designing BANs is discussed in the following chapter.

# 3. Body Area Networks

This chapter contains a detailed description of a Body Area Network (BAN) and discusses the challenges that come with designing such a network. Based on the information presented, design choices regarding the BAN system designed in this work are also identified.

## 3.1 Introduction

BAN, Wireless BAN (WBAN), Body Sensor Network (BSN) and Wireless BSN (WBSN) are all terms used to describe sensor networks that monitor signals in and around the human body and communicate the acquired data to a master unit or server, which may be a Personal Computer (PC), smart phone or other small electronic device. This thesis will use the term BAN to encompass all types of body networks.

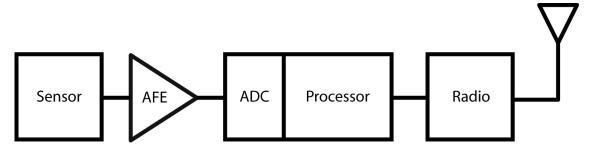

A typical BAN consists of two node types: slave nodes and master nodes. The slave nodes are also known as motes. Motes are responsible for acquiring sensor data and communicating the digitized data to the master node. The mote typically contains a sensor, an Analog Front End (AFE) for conditioning the signal, an Analog to Digital Converter (ADC), a processor and an RF radio, as shown in the block diagram in Figure 3.1. Examples of physiological signals acquired by motes includes: electrical signals produced by the brain, electroencephalogram (EEG); electrical signals produced by the heart, electrocardiogram (ECG); blood pressure; respiration rate; blood glucose; blood oxygen; electrical signals produced by the skeletal muscles, electromyogram (EMG); electrical signals produced by the eyes, electrococulogram

(EOG); and 3-axis acceleration. Depending on the BAN architecture, motes may also be responsible for processing the acquired data for the purpose of data compression, identifying interesting events, or other tasks. The master node wirelessly collects the sensor data from the motes, processes the data and may forward the data beyond the BAN. The level of processing, as well as data storage and data forwarding functions, depends on the BAN system architecture.

Figure 3.1 Mote block diagram

In recent years research interest focused on biomedical applications of BANs has gathered significant momentum. This is due in part to advancements in wireless communication technology, miniaturization and reduction in power consumption of integrated circuits, and also due to an aging and increasing world population [10]. A more mature and larger population places increasing demands on current health care systems. Appropriate application of BANs will provide many opportunities to alleviate this pressure by reducing hospital stays, technician analysis of test results, wait times for specialized tests or meeting with specialized health care professionals. The benefits gained through use of health care related BANs include reducing health care costs but more importantly these network have the potential to save lives. The ability to detect the onset of adverse health conditions relatively earlier than without BANs will revolutionize the health care industry. Some examples of related and current research include monitoring of ambulatory ECG [11–13], blood glucose [14,15] and pulse oximetry [16]. Regardless of the application, BANs are faced with many challenges.

# 3.2 Challenges

The benefits of real time physiological monitoring are poised to be significant but prior to BAN systems truly becoming mainstream many challenges must be addressed by researchers. The work accomplished by the BAN nodes must be carried out efficiently due to the small amount of energy available. Each of the nodes must be kept small in order to be comfortable and unobtrusive as possible, facilitating long term use. The BAN system must be affordable and simple to use. Privacy and security are also a significant concern when dealing with personal information, especially health records. Ideally the BAN system will be flexible enough to allow a myriad of sensor modules, applications and communication protocols. Many existing surveys have adequately covered the current state of BANs [17–19]. It is not our goal to exhaustively summarize these surveys. Instead, the remainder of this chapter will focus on four major design challenges, which are especially relevant to reconfigurable BANs: (1) selection of network architecture; (2) selection of hardware; (3) selection of software architecture; and (4) selection of wireless protocol.

### 3.2.1 Network Architecture

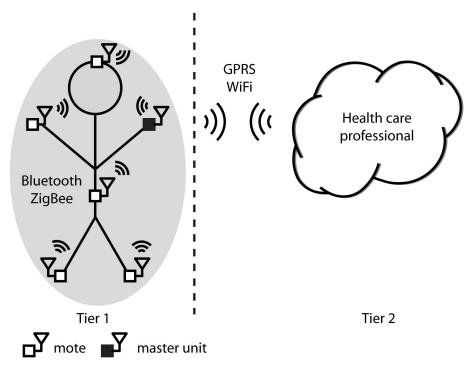

It is evident that there are significant constraints placed on BANs, making the design of such systems non-trivial. As noted by Chen et al. [18], many different systems with different network architectures, communication protocols, processor selections and applications are being researched. The typical BAN architecture uses a star topology on the body, where multiple motes communicate via ZigBee or Bluetooth with a master node. The master node forwards data via Wireless Fidelity (WiFi) or General Packet Radio Service (GPRS) to a health care professional, according to Dishongh and McGrath [20]. Many implementation variations exist in this architecture, generally driven by the application. Figure 3.2 provides a high level view of the typical architecture. As shown, intra-BAN communications occurs in tier 1 of the BAN system architecture. Any communications that exceed the boundaries of tier 1 are considered tier 2 communications (e.g., event escalation to a health care

professional). What this diagram does not illustrate is the location in the network where information processing of the sensor data occurs or where the sensor data is stored. There are many options in BAN network architectures for processing and storage of sensor data, as the following paragraphs will illustrate.

Patel et al. [21] carries out advanced processing of the data on the mote and only transmits the important features beyond the mote. This architecture provides power savings by reducing the amount of data that requires wireless transmission. However, in this application the processor on the mote must be relatively powerful and consume a relatively large number of processing cycles. In addition, historical data is not available on the master node.

Burns et al. [22] employs a slightly different approach in that the acquired data on the mote is saved to an on-board micro Secure Digital (SD) card. In this application data integrity is maintained during power or communication interruptions. However, the storage of data is distributed among the motes, making data fusion challenging.

Auteri et al. [11] keeps the motes as simple as possible while processing the data at the master node. However, the master node is a PC, which doesn't allow for mobile event escalation for the user.

In this work a network architecture was selected that is a hybrid of those previously discussed. The motes are simple devices responsible for data acquisition and forwarding, with very little processing. The master node processes the data to identify "interesting events" and store the results. This architecture was selected for the following reasons: (1) to limit the relatively high power consumption of advanced processing to a single node (i.e., the master); (2) to centralize the sensor data in order to make data fusion easier and enable real time feedback for the end user; and (3) to keep power consumption of the motes as low as possible by limiting the data processing on these nodes. However, point 3 implies that all raw data will be transmitted beyond the mote requiring relatively high power for RF devices, which is not case. Processing power of the motes is relatively low but these devices are still capable of implementing

Figure 3.2 Typical BAN System Architecture

algorithms such as compressed sensing or error correcting Reed-Solomon code. In either of these cases the encoding scheme is relatively straight forward requiring limited computing resources but decoding requires significantly more computing resources as noted by Casson and Rodriguez-Villega [23] as well as Sweeney et. al. [24].

# 3.2.2 Hardware Selection

Many authors have researched the application of FPGAs in BAN systems, specifically placed on the mote [25–29]. There are also a number of studies that place a microcontroller on the mote [11,13,22,30–32]. These documents suggest that microcontrollers and FPGAs both have a place in BANs. It is the opinion of the author that these hardware options should be applied in a complementary fashion. For example, referring back to the typical architecture in Figure 3.2, the motes are kept simple in that they are responsible for data acquisition, data forwarding and data compression and the master node is responsible for data processing, data fusion and storage. In this case the extremely low power sleep mode of modern microcontrollers can be exploited at the mote and the efficient, advanced processing capabilities and

flexibility of the FPGA can be exploited at the master node.

In this work 2 hardware options were considered for processing the data at the master node: (1) microprocessor; (2) FPGA configured as a soft-core processor. In order to accommodate the diverse demands of many different BAN applications, peripherals and communication protocols the hardware requires a high level of flexibility. In addition data processing must be completed efficiently to keep power consumption low.

As BAN applications mature the number of sensors used in each BAN will increase. In addition, different sensors have different data rate demands. For example, the data rate required to record the electrical activity of the brain is significantly more than that required to collect blood pressure data. Based on the previous points several relatively high data rate sensors are likely to be used in a single BAN. For example, a BAN used to detect sleep disorders requires EEG, ECG, EOG and EMG sensors all applied to the same patient at the same time, as shown by Nassir and Barnea [33]. Each of these sensors demands a relatively high data rate. In order to keep the power consumption of the motes in this BAN as low as possible, both data processing on the mote and data transmission from the mote to the master node should be as low as possible. To accommodate this, efficient compression algorithms should be applied on the mote. As mentioned in the previous section, decoding the data from compression algorithms will require significant computing resources. In this example an FPGA configured as a soft-core processor provides significant advantages over a microprocessor.

Depending on the selection of soft-core processor and size of FPGA selected, implementing a soft-core processor requires only a portion of the FPGA resources. As well, mechanisms are available to communicate data processed in hardware to the software (i.e., operating system) running on the soft-core microcontroller and viceversa. Therefore processing intensive tasks, such as running several decompression algorithms in parallel, can be completed in hardware and the results can be passed to the operating system. With a powerful enough microprocessor, the same decompression

sion algorithms could likely be completed in sufficient time. However, in processing intensive applications the FPGA is also more efficient, as the following paragraph illustrates.

It is well known that a hardware solution will consume less energy than a soft-ware solution when completing a processing intensive task. Frigo et al. [34] compare the power demands between a microprocessor and a Field Programmable Gate Array (FPGA) in significant data processing applications and note that the FPGA is clearly the lower energy option. In another example, Healy et al. [35] present application layer security that is reactive to attacks in a Wireless Sensor Network (WSN). This is a complex implementation of this level of security that requires significant resources making it well suited for a hardware solution. In another work, Lysecky and Vahid [36] identify reduction in processing time and power by implementing combined hardware/software solutions. They cite possible software speedups of 200 to 1000% and energy reduction by as much as 99%.

Based on the requirements for advanced and efficient data processing the master node in this work contains an FPGA configured configured with a soft-core processor. The FPGA was selected over a microcontroller for its ability to complete processing intensive tasks in parallel with software running on a soft-core processor as well as to limit the power used by the processing intensive master node. In addition the FPGA provides a migration path to an ASIC.

### **FPGA Selection**

The two largest FPGA manufacturers are Altera and Xilinx, other FPGA manufacturers include Lattice Semiconductor, Microsemi (formerly Actel), Quicklogic and Archronix. Altera and Xilinx will be reviewed in this work. The FPGA selection criteria includes FPGA cost, power consumption, features, including the soft-core processor options, as well as the availability and functionality of the system development software offered by each manufacturer.

The product line from Altera includes programmable logic devices (PLD), applicationspecific integrated circuits (ASIC), system on a chip (SoC) and FPGAs. Altera has three classes of FPGA: (1) High-End FPGAs called the Stratix Series; (2) Mid-Range FPGAs called the Arria Series; and (3) Lowest Cost and Power FPGAs called the Cyclone Series. Since BAN networks are constrained by power and cost, the Cyclone series was considered as the most appropriate series option for this work. The Cyclone Series of FPGAs is further subdivided into Cyclone and Cyclone II to V. Of these the Cyclone IV is the lowest cost and lowest power, according to Altera. The Cyclone IV devices have up to 150,000 logic elements, 6.3Mb of embedded memory, 4 general purpose phase locked loops and 360 18 x 18 bit embedded multipliers making the hardware highly reconfigurable. System development, functional and timing simulation, power analysis, timing analysis, configuration and verification of Altera devices is done using an integrated development environment (IDE) called Quartus II. Quartus II downloads are available for Windows and Linux operating systems. Included in the Quartus II IDE is a software add-on called SOPC Builder. SOPC Builder is a system development tool that allows specifying the components of an FPGA based hardware system via a graphical user interface (GUI). Examples of available components include memories, processors, serial interfaces, general purpose input outputs (GPIO), phase locked loops, timers and more. Altera offers intellectual property (IP) that can be added to FPGA designs to reduce the design cycle time. Example categories of this IP include digital signal processing (e.g., Fast Fourier Transform, Advanced Encryption Standard), embedded processors (e.g., Nios II, ARM), peripherals (e.g., UART, SPI) and many more.

Xilinx manufactures FPGAs, SoCs and PLDs. The product offering from Xilinx includes 5 FPGA families: (1) Artix-7; (2) Kintex-7; (3) Virtex-7; (4) Spartan-6; and (5) Virtex-6. Of these the Spartan-6 family is described as a family of low-cost and low-power FPGAs, making it a suitable selection for BANs. The Spartan-6 devices contain up to 150,000 logic cells, 4.8Mb of embedded memory, 6 phase locked loops and 180 18x18 bit multipliers, which is comparable to the Cyclone IV devices from

Altera. However, the Xilinx FPGAs in the Spartan-6 family are approximately half the cost of the comparable Cyclone FPGAs from Altera. System development is done using an IDE called Vivado. Within the Vivado IDE Xilinx also offers IP comparable to the IP offerings from Altera. In addition, Xilinx also has soft-core processor IP for use with the Spartan-6 devices called MicroBlaze. The MicroBlaze processor is configured using the MicroBlaze Configuration Wizard.

In summary, both Altera and Xilinx offer low power, low cost FPGAs making them suitable for the constraints of a BAN. The additional features available from each manufacturer are also comparable and they both offer advanced development systems. Xilinx is the superior choice when cost alone is considered. However, none of the hardware or software differences identified thus far were enough to make either manufacturer stand out as the clear choice. To aid the decision making processo, the soft-core processors supported by each manufacturer also require investigation.

Altera supports a number of soft-core processor options, such as the ARM Cortex M1 and A9, MIPS32 and Freescale V1 ColdFire but the Nios II processor is the only processor that is both supported by the Cyclone IV family of FPGAs and included in SOPC Builder and was therefore selected for evaluation. The Nios II processor is supported by all of the Altera FPGAs, SoCs and ASICs, allowing for a direct migration path to more powerful programmable devices, should the application demand it. The Nios II is a 32 bit Reduced Instruction Set Computer (RISC) processor with a Harvard architecture. The Nios II processor has 32 bit instructions, 32 general purpose registers and 32 x 32 bit single instruction multiply and divide functions with 32 bit results as well as instructions for 64 and 128 bit results. Three versions of processor are offered: (1) fast (Nios II/f); (2) standard (Nios II/s); and (3) economy (Nios II/e). The fast version is optimized for performance and contains the most configuration and debugging options as well as a 6 stage pipeline. Altera published specifications identify the Nios II/f processor capable of 218 Dhrystone million instructions per second (DMIPS) operating at a max frequency of 185MHz. The Nios II/f requires 1810 logic elements plus the logic elements required by peripherals. Both hardware acceleration (i.e., moving software functions to hardware) and the ability to add 256 custom instructions are supported by the Nios II processor.

The comparable soft-core processor from Xilinx that is supported by the Spartan-6 family of FPGAs is called MicroBlaze. This processor is also a Harvard architecture processor that uses 32 instructions. Three main configuration options exist for this processor: (1) Performance Optimized MicroBlaze with branch optimizations; (2) Performance Optimized MicroBlaze; and (3) Area Optimized MicroBlaze. The first two options contain a 5 stage pipeline and the last a 3 stage pipeline. The maximum performance specification from the Performance Optimized MicroBlaze is 209 DMIPS at a clock rate of 161MHz. Many aspects of this processor are highly configurable such as the cache size, optional memory management unit (MMU), embedded peripherals and pipeline length. In addition, unused processor instructions (i.e. divide for example) can be removed from the final configuration, saving FPGA area. MicroBlaze also includes a hardware acceleration feature called Fast Simplex Link (FSL) that is a high-speed link between the MicroBlaze processor and hardware logic functions.

Overall, the features and performance of the Nios II and MicroBlaze soft-core processors are very comparable. One item that makes the Nios II processor more attractable is that it has a migration path to an ASIC. However, considering that this work is focused on creating a reconfigurable system the power and cost savings provided by an ASIC design are overshadowed by the fact that the system would no longer be reconfigurable.

In this work the final implementation includes an Altera FPGA configured with a Nios II processor. Since hardware, features and development systems from both Altera and Xilinx are very suitable for a reconfigurable BAN system the final decision was based on access to resources and support.

### 3.2.3 Software Architecture

In order for a system to be highly reconfigurable, consideration also needs to be given to the software architecture. Regardless of the processor selection, microcon-

troller or soft-core processor on an FPGA, there are two main ways to implement the system firmware: (1) through custom driver development; or (2) through the use of an operating system.

Custom driver development requires programming for every peripheral and initialization of the microcontroller, which can be a challenging undertaking. For example, writing drivers for the management of removable storage is a particularly complex task. One one hand, if the system is not intended to be highly reconfigurable and does not contain overly complex peripherals, writing custom drivers is a preferable solution. In addition, it is easier to exploit the low power sleep modes of modern microcontrollers without having to concern yourself with the complexities of an operating system. In the system designed in this work the motes are designed using custom firmware for the following reasons: (1) to allow extremely low power sleep modes to be easily applied; (2) because the additional services provided by an OS are not required on the mote; (3) processing of the sensor data on the mote is not intended to be easily reconfigurable, as it is on the master node (4) the mote hardware is not relatively complex.

On the other hand, an operating system provides an abstraction layer from the complexities of the processer and peripherals, which enables relatively straight forward reconfiguration of user software. In addition an OS contains services that may be useful to BAN systems (e.g., web server). Researchers have considered the application of operating systems in WSNs. The work done by Wei et al. includes an OpenRISC processor running uC/OS-II [37], Burns et al. [22] and Ton-That et al. [38] are both running TinyOS on their platforms and Peng et al. [39] have applied uClinux to their Safety Monitoring and Warning System.

TinyOS is an embedded OS specifically designed for low power wireless sensor networks that have very limited memory resources. The OS is developed and supported by the TinyOS Alliance. The kernel requires 8kB of program memory and 512kB of data memory. This is an open source OS licensed with a Berkeley Software Distribution license. The current release is version 2.1.2. TinyOS is written in and

user applications are developed using an extension of the C programming language called nesC. TinyOS has ports for Texas Instruments MSP430, Atmel ATMega 128 and Intel XScale PXA271. Good documentation for this OS is available but the learning curve required to be efficient with nesC is significant. This OS is popular in BAN systems however, it does not contain ports for any soft-core processor and therefore was not considered further in this work.

Microcontroller Operating System Version 2 (uC/OS-II) is supported by Micrium Inc. This OS is written in C and also requires a small memory footprint. Depending on the distribution options used the kernel requires 6 to 26kB for program memory and 1+kB for data. This OS contains support for many different processors including 8-64 bit and multi-core variants. Specifically, this OS is ported for Nios II, MicroBlaze, OpenRISC, MSP430, Blackfin and many more. This OS is covered by a commercial royalty-free license (i.e., each end product requires a paid license, \$9,995 per end product when using the latest OS release uC/OS-III). However, the OS is available for free for educational use. uC/OS-II is a real-time operating system (RTOS). A RTOS is designed with a focus on the ensuring the time used to complete a task is deterministic. These operating systems are designed for applications where the time required to complete a task is just as important as the result of the task, for example in closed loop control systems. BAN applications typically do not require the advanced scheduling mechanisms of a RTOS in order to maintain data integrity.

uClinux, pronounced "you see Linux, is an open source operating system originally design for processors that did not contain a memory management unit (MMU). uClinux started as a fork off of Linux 2.0 but later versions include ports for Linux 2.4/6 and also for processors with MMUs. The latest release is version 3.4.0-uc0. Like uC/OS-II this OS is also ported for many processors including soft-core processors, Nios II and MicroBlaze. uClinux is covered under the GNU Public License (GPL), which is a free-software license allowing users to modify the software as necessary for their needs. In this work the master node runs uClinux. In order to reconfigure the user programs a programmer requires knowledge of C and Linux system calls. This

particular OS was selected because it is ported for the selected soft core processor, has open source code, extensive documentation and resources, is covered by GPL, and is popular in the research community.

### 3.2.4 Wireless Protocol

In order for a wireless technology to be suitable for BANs it must satisfy certain criteria. It must be efficient such that it is capable of long term use (i.e., days, weeks or months) operating on battery power. It must be secure through authentication and encryption. The data rates must be able to satisfy the applications and the wireless technology must be adaptable to accommodate different network architectures and quantity of network nodes. The two most commonly used wireless technologies in BANs are Bluetooth [40–43] and ZigBee [11,32,44,45]. Others include ultra-wideband (UWB), GPRS, WiFi, IEEE 802.15.6 and in-body radio frequency communications, as described by Yang [46].

UWB over IEEE 802.12.3a was a proposed technology for low energy, high data rate (100s of Mbps) Wireless Personal Area Network (WPAN) applications but the Task Group was dissolved in 2006. Following this WiMedia, Bluetooth Special Interest Group (SIG), Wireless Universal Serial Bus (USB) Promoter Group and the USB Implementers Forum all attempted to move the UWB standard forward. Blumrosen et al. [47] are researching UWB in BANs but similar works are limited. Common Off The Shelf (COTS) UWB modules are difficult to find or unavailable. Due to the lack of current research, difficulties and uncertainty with standards and limited availability of parts, UWB has not been given further consideration in this research.

Both GPRS are WiFi are suited for Tier 2 communications but not specifically for intra-BAN communications due to the relatively high power requirements. GPRS also requires a formalized network connection with a telecommunications provider. For these reasons, GPRS and WiFi are not considered suitable wireless technologies for Tier 1 of the BAN.

IEEE 802.15.6 is the Task Group working on the standard for BAN technolo-

gies [48]. According to the Task Group this standard is still in draft and has recently been shared with sponsors to test for support. Since COTS components will not be available for some time this technology will not be further addressed in this research.

Bluetooth technology was originally adopted by the IEEE 802.15.1 Task Group in 2004. Bluetooth operates in the unlicensed 2.400 to 2.4835 GHz Industrial, Scientific and Medical (ISM) band. The physical layer can be set up to limit power consumption to 1mW, which provides a usable range to about 10m, or as much as 100mW, allowing a range of up to 100m. To avoid interference with other devices operating in the same frequency band and for an added security feature, Bluetooth applies a Frequency Hopping Spread Spectrum (FHSS) method for data transmission. While transmitting data, a Bluetooth device will hop between 79 channels, each of 1MHz bandwidth, 1600 times per second using a pseudo random hopping sequence that is known by the receiver and transmitter. The typical network configuration is an ad hoc network, called a piconet. In a piconet, a master can connect with up to seven slaves. In Bluetooth networks there are three distinct security modes according to Healy et al. [35]. Mode 1 is unsecured, Mode 2 initiates security features after a link is established and Mode 3 initiates security features prior to establishing a link. To add to the security features, network nodes can choose to be discoverable or nondiscoverable. Non-discoverable nodes are not visible to other nodes in the network. The E0 stream cipher is used to encrypt data. The most recent technology release is Bluetooth v4.0. Bluetooth v4.0 includes a low energy subset called Bluetooth Low Energy (BLE). Prior to BLE, Bluetooth technology had some drawbacks that made it less suitable for a BAN than competing technologies such as ZigBee. However, BLE has reduced power consumption by reducing the duty cycle of transmission to approximately 20% while maintaining the wireless data rate at 1Mbps. This of course impacts the throughput, but at 200kbps this technology still meets the needs of most BAN applications. Network setup time was also addressed in the v4.0 release, going from 6s to 3ms. As a result, BLE is gathering momentum with respect to BANs according to Yu et al. [49].

ZigBee is designed to be a very low power, low data rate technology and is used in many applications including industrial, building and home automation, home entertainment, WSNs, toys, smoke and intruder alarms, and consumer electronics. ZigBee is built on top of the IEEE 802.15.4 standard, which only defines the Physical (PHY) and Media Access Control (MAC) layers for Low Rate Personal Area Networks (LR-PANs). ZigBee defines the network layer and Application Support Sublayer (APS). Two PHYs are specified by the IEEE 802.15.4 standard; the 868/915MHz band used in Europe, U.S. and Australia and the 2.450GHz ISM band used ubiquitously. The wireless data rate is 250kbps per channel and the useable range is 10-100 meters. Zig-Bee has a useable range of 10-100m. Support for peer to peer and star topologies is available. Three types of devices are defined by ZigBee, Coordinator, Router and End Device. The Coordinators and Routers are defined as Full Function Devices, meaning they include all aspects of IEEE 802.15.4. End Device are defined as Reduced Function Devices, meaning they do not use all aspects of IEEE 802.15.4. Security is based on an open trust model, which means that all layers (i.e., MAC, Network and APS) on a device trust each other. If a layer is responsible for generating a packet then that layer is also responsible for securing it. Security between devices in a network is based on the exchange of 128 bit Advanced Encryption Standard (AES) encrypted keys. ZigBee has an entity called a Trust Center (TC), which is a single device that is trusted by all other devices in the network. The TC is responsible for distributing keys, authenticating devices and managing end to end security in the network [35, 50]. ZigBee supports 64 bit addressing, allowing for over 65000 devices per network. Bandwidth is subdivided into 16 channels, with 5MHz spacing and each ZigBee network uses a distinct channel. In applications that have many ZigBee networks deployed in the same locale there is a possibility that two or more networks will attempt to use the same channel. Sahandi and Lui [51] have researched ZigBee networks in remote patient monitoring in a general hospital ward. The study investigated potential interference problems when ZigBee networks in the same locale used the same channels. The study concluded that multiple ZigBee networks could be applied in the same area provided that appropriate transmission time intervals are used.

Table 3.1 summarizes several of the important aspects of both Bluetooth and ZigBee, as related to BANs. Two noteworthy points are the number of devices per network and the design complexity. In the near term, eight devices per network may be suitable for BANs but likely this number will be unacceptable as more BAN systems become commercialized. Similarly, the Bluetooth SIG will likely increase this number to respond to market demands. Design complexity is a significant challenge for Bluetooth. If these two protocols are comparable in all other ways, the extra

**Table 3.1** Comparison of Low Power Wireless Technologies

| Detail                 | Bluetooth        | ZigBee   |

|------------------------|------------------|----------|

| Data rate              | 200kbps-24Mbps   | 250kbps  |

| Devices/ntwk           | 8                | 65536    |

| Security               | E0 stream cipher | 128b AES |

| Engineering complexity | high             | low      |

| Power consumption      | low              | very low |

| Frequency              | ISM band         | ISM band |

| Related Standard       | 802.15.1         | 802.15.4 |

engineering effort required will have a significant impact on the technology selection for both researchers and commercial designers. However, Bluetooth has something very important that ZigBee doesn't: it is nearly ubiquitous on cell phones. According to Yu et. al. [49] Bluetooth v4.0 will be on all smart phones by the end of 2012. In order for BANs to become mainstream in today's society, integration with smart phones will have to be accommodated. In addition, Bluetooth offers higher data rate services, which may be useful for streaming of sensor data as applications and sensors evolve. However, these higher data rate services are not available with the low power consumption BLE technology. The selection of wireless technology is very difficult and readers are encouraged to allow the applications, and not current momentum, drive the selection.

The system designed in this work uses ZigBee because it satisfies the requirements of BANs in that it uses low power, its secure and it has the required throughput. ZigBee was selected over Bluetooth due to the reduced engineering effort required to configure a network, ZigBee allows more devices per network and because ZigBee is the lower power solution (with the exception of BLE).

Based on the selections made to address each of the four major design challenges identified in Section 3.2, the following chapter includes a detailed description of the BAN system designed in this work.

# 4. System Architecture

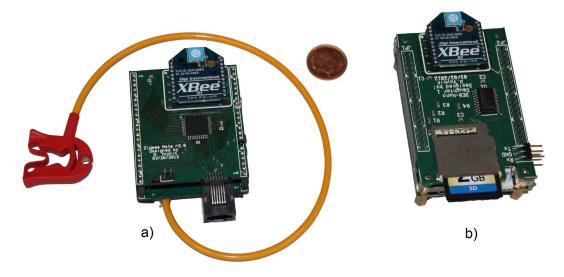

Based on the design choices identified in Chapter 3 a reconfigurable Body Area Network (BAN) system was designed and built. In this system the master node is referred to as the Field Programmable Gate Array (FPGA) Server and the slave node is referred to as the ZigBee Mote. A photograph of the system nodes is provided in Figure 4.1.

Figure 4.1 Photograph of System Nodes; a) ZigBee Mote; b) FPGA Server

The ZigBee Mote is responsible for data acquisition and wireless transmission of sensor signals. In this work, the mote was used to collect and transmit electrocardiogram (ECG) data. This modular node consists of two pieces of hardware: (1) an ECG Analog Front End (AFE); and (2) Digital Transmitter. Both of these devices were designed and built as part of this work. The ECG AFE contains circuitry for

signal conditioning a modified limb lead II ECG signal (i.e., electrodes on the chest). The major hardware components of the Digital Transmitter include: a Microchip PIC18LF45K22 microcontroller, an XBee radio from Digi International, a -3V DC-DC converter for powering dual-supply operational amplifiers and a pin header for coupling with sensor modules, such as the ECG AFE. As the following sections will show the ZigBee Mote was designed to demand very low power. In the final configuration the ZigBee Mote requires an average of 11mA. Using 2 AAA lithium batteries rated at 3000mAh the mote will work continuously for 11.4 days.

The FPGA Server is responsible for storage and processing of the sensor data received from the ZigBee Mote(s). This node is also modular and consists of: (1) a DE0-Nano Development and Education Board from Terasic Technologies; and (2) a Daughter Board. The DE0-Nano Development and Education Board was purchased from Terasic Technologies. This board contains an Altera Cyclone IV EP4CE22F17C6N FPGA. The FPGA was configured to emulate the Nios II processor and run uClinux. The complete Daughter Board was designed and built as part of this work. It includes an RS232 driver integrated circuit used for system debugging, an XBee radio and a Secure Digital (SD) card for removable storage.

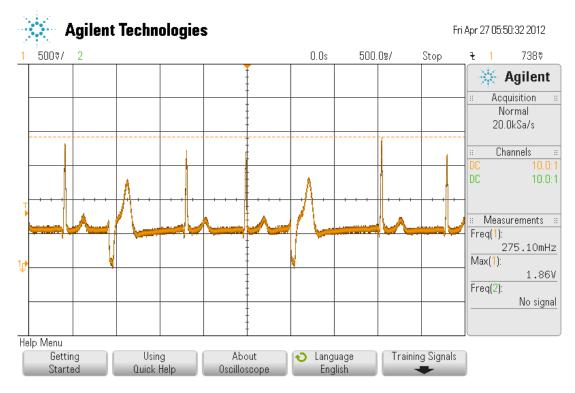

In the configuration demonstrated in this work the system has the ability to record raw ECG data and detect and record R-R intervals, premature ventricular contractions (PVC) and premature atrial contractions (PAC). Moreover, the overall system was designed to be highly reconfigurable, allowing it to be used for other BAN applications besides pattern recognition in ECG data signals.

The remainder of this chapter will describe all of the hardware and software design details for the ZigBee Mote and FPGA Server and close with a description of the reconfiguration abilities of this BAN system. The ZigBee Mote description is first and separated into 2 sections, according to the 2 distinct hardware components: (1) ECG AFE; and (2) Digital Transmitter.

### 4.1 Electrocardiogram Analog Front End

The overall purpose of the ECG AFE is to prepare the ECG signal measured on the surface of the body for analog to digital conversion. A photograph of the ECG AFE is shown in Figure 4.2.

Figure 4.2 ECG AFE Photo

# 4.1.1 Block Diagram

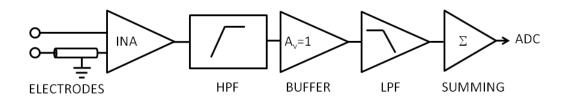

An ECG signal is difficult to measure due to the low signal voltage, low frequency and sources of interference, as discussed in Section 2.1.1. As this section will prove, a well designed circuit will address these design constraints.

As the high-level block diagram in Figure 4.3 shows, the electrodes attached to the human body connect to an instrumentation amplifier (INA). The INA is used to accommodate the differential nature of the ECG leads and reject common mode voltages in the ECG signal.

In the next stage a passive single pole High Pass Filter (HPF) is used to remove any DC offset in the signal so that subsequent amplification stages do not cause saturation. This block is rectangular to signify that it does not provide gain. This filter is susceptible to loading so it's followed by a buffer.

The output of the buffer feeds a Low Pass Filter (LPF) that has three purposes:

(1) remove high frequency noise; (2) remove alias frequencies; and (3) to provide amplification to the ECG signal.

Finally, the ECG signal is added to a positive DC value through a summing amplifier to offset the ECG signal so that it only has positive voltages. This enables the use of the single supply Analog to Digital Converter (ADC) in the microcontroller.

Figure 4.3 ECG AFE Block Diagram

Further details regarding each of these blocks is included in the following schematic description.

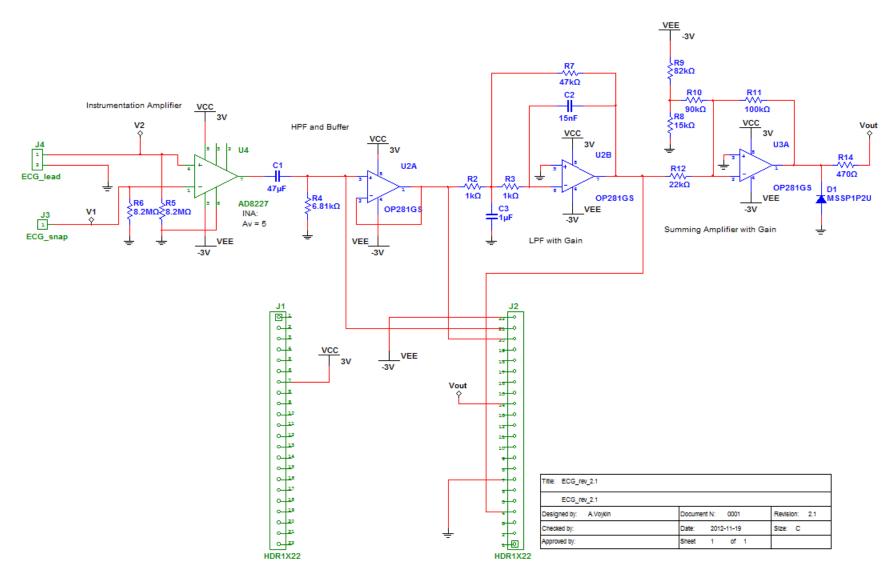

### 4.1.2 Schematic

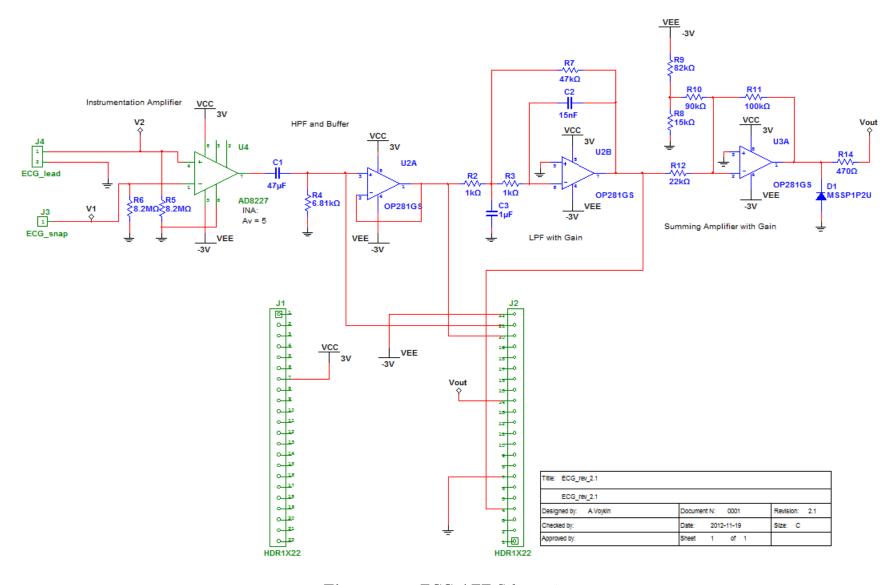

The circuit-level schematic of the ECG AFE is shown in Figure 4.4. The ECG AFE hardware is connected to the Digital Transmitter using the 1x22 pin headers J1 and J2. Power for the ECG AFE (i.e.,  $\pm 3V$ ) comes from the Digital Transmitter via these connectors.

The first amplifier stage is the INA. The INA is a wide supply range, rail to rail output amplifier from Analog Devices, part number AD8227. This INA has a high Common Mode Rejection Ratio (CMRR) of 100dB and a default gain of 5. The high CMRR reduces common mode voltages that exist on the body or are induced from external interference sources. The relatively low gain makes this INA an ideal choice for the first stage of signal conditioning. Too much gain at this stage would saturate the subsequent stages of the ECG AFE due to the unknown amplitude and polarity of the DC offset at the input of the INA, as discussed in Section 2.1.1.

Figure 4.4 ECG AFE Schematic

An  $8.2M\Omega$  resistor is connected to each input of the INA, designated R5 and R6. These resistors are used for input bias current. These resistor values should be high precision to reduce the percentage mismatch in resistance. Any difference in these resistance values will appear as a differential DC input to the INA.

The INA is followed by a passive single pole HPF with a cutoff frequency of 0.497Hz, calculated using

$$f_c = \frac{1}{2\pi RC}. (4.1)$$

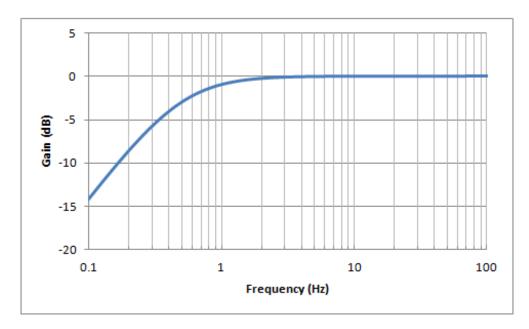

The filter response is shown in Figure 4.5.

This filter is required to remove DC voltages caused by differences in impedance between the electrodes and difference in resistance between the biasing resistors, R5 and R6. Since this passive filter is subject to loading, a voltage follower is placed next so that the filter characteristics are buffered from the remaining circuitry.

Figure 4.5 HPF Frequency Response

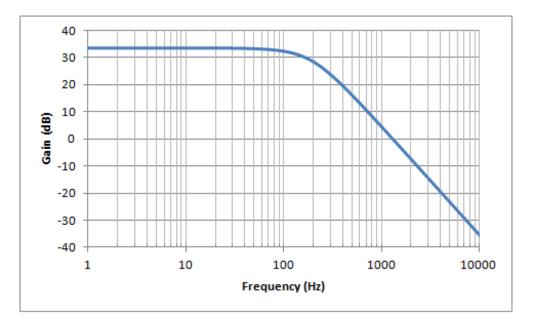

The next stage is a multiple feedback low pass Bessel filter with a cutoff frequency of 150Hz and gain of 50. The filter response is shown in Figure 4.6. The Bessel filter was selected because it does not have ripple in the pass band and it approximates a linear phase response. These characteristics will ensure that the ECG signal suffers

very little degradation as it passes through the filter. The circuit was designed using Filter $Pro^{TM}$  software version 3.1.0.23446 from Texas Instruments. The selection of the system bandwidth is discussed at the end of this section.

The final amplifier stage is a summing amplifier that adds 0.4V DC to ensure the signal entering the ADC remains positive. This stage also amplifies the signal by 4.54.

Considering the three stages of amplification: (1) INA; (2) LPF; and (3) Summing Amplifier; the end-to-end gain of the system is given by

$$Av = Av(INA) * Av(LPF) * Av(SUM) = 5 * 50 * 4.54 = 1135.$$

(4.2)

Figure 4.6 LPF Frequency Response

### Selection of System Gain

The output of the ECG AFE connects to an ADC input on the Digital Transmitter microcontroller. The ADC is configured to convert a voltage range of 0 to 2.048V. The initial design goal was to set ECG AFE gain from so that the output would span as much of the 2.048V range as possible. The problem is that the ECG AFE

output will exceed the range of the ADC input in the presence of any DC offset. The solution was to reduce the gain in the final stage of the ECG AFE to allow room for the DC offset to vary slightly. For example, when the ECG AFE was connected to the primary researcher the ECG signal at the input to the INA was close to 1.5mV peak to peak. Multiplying by the gain from Equation (4.2) results in an output from the ECG AFE of 1.7025V peak to peak. The difference between the ADC voltage range and the ECG AFE output provides 345.5mV of "wandering room" before the signal exceeds the ADC limits. In order to couple the ECG AFE with the microcontroller ADC 2 additional components are added to the circuit.

The final components in the circuit are a 0.25V Schottky diode (D1) and a 470 $\Omega$  resistor (R14). The microcontroller ADC input is limited to -0.3V, D1 is used ensure the input does not drop below this value. R14 is used to protect the microcontroller input in the event of an electrostatic discharge. R14 should be kept relatively low. Higher values (i.e., greater than  $10k\Omega$ ) will increase the ADC sample period due to the RC time constant between R14 and the ADC input pin capacitance. Microchip uses a  $470\Omega$  resistor in its development systems to protect analog inputs.

### Selection of System Bandwidth

According to Chan [52], the required bandwidth for ECG measurement is different for diagnostic and monitor quality systems is as shown in Table 4.1.

Table 4.1

Required Bandwidth for ECG Systems

| Quality    | Frequency     |  |

|------------|---------------|--|

| Diagnostic | 0.05 to 150Hz |  |

| Monitor    | 1 to 40Hz     |  |

The system designed in this research is capable of monitoring ECG signals. However, in order to build a reconfigurable system a high level of versatility is required. For that reason the initial design goal was to meet the bandwidth requirements of a diagnostic quality system. However, the following problems were encountered with the HPF when the cutoff frequency was set to 0.05Hz; (1) the bias current from the operational amplifier buffer added a significant DC offset to the output of the ECG AFE; and (2) the ECG AFE output was very slow to react to abrupt changes in the DC offset.