# Performance Analysis of Hardware/Software Co-Design of Matrix Solvers

A Thesis Presented to the

College of Graduate Studies and Research

In Fulfillment of the Requirement

For the Degree of Master of Science

In the Department of

Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

By

# Peng Huang

© Copyright Peng Huang, November 2008. All rights reserved.

#### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

S7N 5A9

#### **ACKNOWLEDGEMENTS**

First, I would like to express my sincere gratitude and appreciation to my supervisor, Dr. Daniel Teng, for his tremendous support, invaluable guidance and constant encouragement during the course of my studies. The completion of this thesis would not have been possible without Dr. Teng's exceptional supervision and ever lasting support. I am also grateful to him for providing me with various opportunities to pursue a dynamic and fascinating area of digital systems as well as explore opportunities out of the lab.

I also wish to thank all the members of VLSI lab; working with them made my time during graduate study a wonderful experience.

A countless and sincere thanks goes to my family, especially my wife, Zhang Bei, and my parents, Huang Peikuan and Qiu Sufang, for their continuous support and encouragement throughout my studies.

#### **ABSTRACT**

Solving a system of linear and nonlinear equations lies at the heart of many scientific and engineering applications such as circuit simulation, applications in electric power networks, and structural analysis. The exponentially increasing complexity of these computing applications and the high cost of supercomputing force us to explore affordable high performance computing platforms. The ultimate goal of this research is to develop hardware friendly parallel processing algorithms and build cost effective high performance parallel systems using hardware in order to enable the solution of large linear systems.

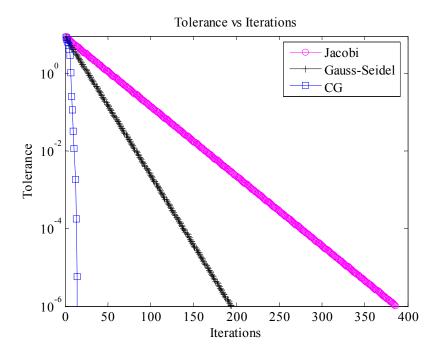

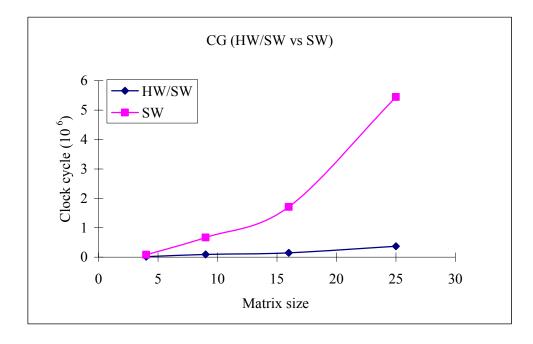

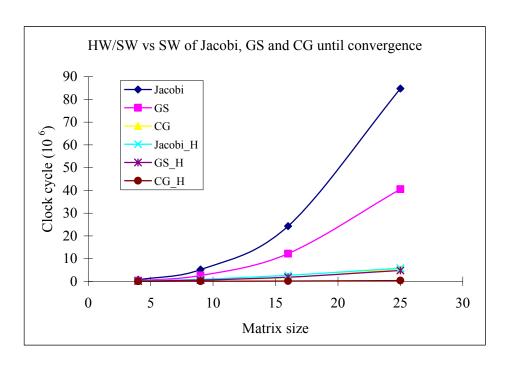

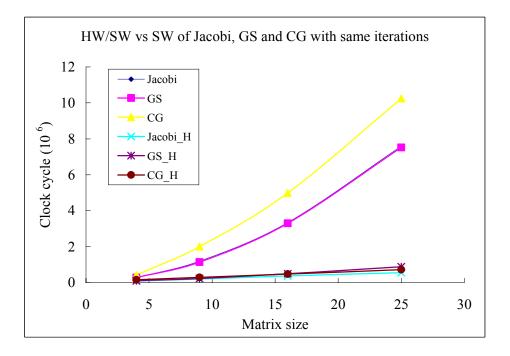

In this thesis, FPGA-based general hardware architectures of selected iterative methods and direct methods are discussed. Xilinx Embedded Development Kit (EDK) hardware/software (HW/SW) codesigns of these methods are also presented. For iterative methods, FPGA based hardware architectures of Jacobi, combined Jacobi and Gauss-Seidel, and conjugate gradient (CG) are proposed. The convergence analysis of the LNS-based Jacobi processor demonstrates to what extent the hardware resource constraints and additional conversion error affect the convergence of Jacobi iterative method. Matlab simulations were performed to compare the performance of three iterative methods in three ways, i.e., number of iterations for any given tolerance, number of iterations for different matrix sizes, and computation time for different matrix sizes. The simulation results indicate that the key to a fast implementation of the three methods is a fast implementation of matrix multiplication. The simulation results also show that CG method takes less number of iterations for any given tolerance, but more computation time as matrix size increases compared to other two methods, since matrix-vector multiplication is a more dominant factor in CG method than in the other two methods. By implementing matrix multiplications of the three methods in hardware with Xilinx EDK HW/SW codesign, the performance is significantly improved over pure software Power PC (PPC) based implementation. The EDK implementation results show that CG takes less computation time for any size of matrices compared to other two methods in HW/SW codesign, due to that fact that matrix

multiplications dominate the computation time of all three methods while CG requires less number of iterations to converge compared to other two methods.

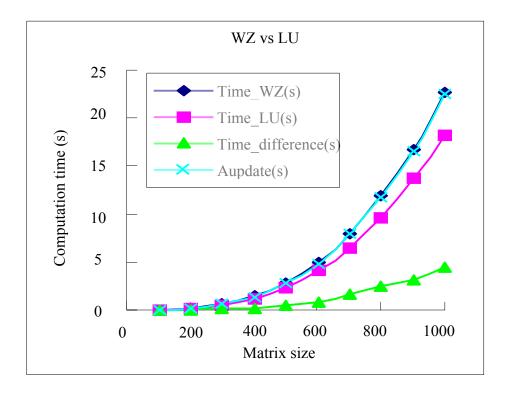

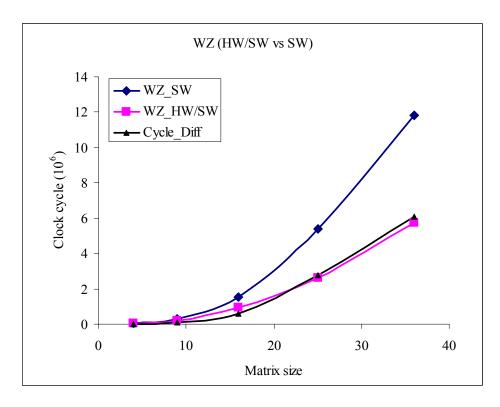

For direct methods, FPGA-based general hardware architecture and Xilinx EDK HW/SW codesign of WZ factorization are presented. Single unit and scalable hardware architectures of WZ factorization are proposed and analyzed under different constraints. The results of Matlab simulations show that WZ runs faster than the LU on parallel processors but slower on a single processor. The simulation results also indicate that the most time consuming part of WZ factorization is matrix update. By implementing the matrix update of WZ factorization in hardware with Xilinx EDK HW/SW codesign, the performance is also apparently improved over PPC based pure software implementation.

# **Table of Contents**

| PERMISSION TO USE                                   | i    |

|-----------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                    | ii   |

| ABSTRACT                                            | iii  |

| Table of Contents                                   | v    |

| List of Tables                                      | viii |

| List of Figures                                     | ix   |

| List of Abbreviations                               | xi   |

| Chapter 1 Introduction                              | 1    |

| 1.1 Motivation                                      | 1    |

| 1.2 Thesis Overview and Objectives                  | 3    |

| 1.3 Thesis Outline                                  | 4    |

| Chapter 2 Background                                | 6    |

| 2.1 SPICE Algorithm Overview                        | 6    |

| 2.2 Matrix Solving Methods Used in SPICE            | 8    |

| 2.2.1 Gaussian Elimination (GE)                     | 8    |

| 2.2.2 LU Factorization.                             | 9    |

| 2.3 Parallel Iterative Matrix Solving Methods       | 10   |

| 2.3.1 Jacobi Iterative Method                       | 10   |

| 2.3.2 Combined Jacobi and Gauss-Seidel              | 12   |

| 2.3.3 Conjugate Gradient (CG)                       | 12   |

| 2.4 Parallel Direct Matrix Solving Methods          | 14   |

| 2.4.1 Parallel Implicit Elimination (PIE)           | 14   |

| 2.4.2 WZ Factorization                              | 16   |

| 2.4.3 Comparison of Direct Methods                  | 18   |

| 2.5 Hardware Architectures for General Applications | 19   |

| 2.5.1 Toronto Molecular Dynamic (TMD) Architecture  | 19   |

| 2.5.2 Hardware/Software (HW/SW) Partitioned Computing System                        | . 20 |

|-------------------------------------------------------------------------------------|------|

| 2.5.3 Mixed-Mode Heterogeneous Reconfigurable Machine (HERA) Architecture           | . 21 |

| Chapter 3 General Hardware Architectures and HW/SW Codesigns of Iterative Methods . | . 24 |

| 3.1 FPGA-based Hardware Architectures                                               | . 24 |

| 3.1.1 Jacobi Iterative Method                                                       | . 24 |

| 3.1.2 Combined Jacobi and Gauss-Seidel Method                                       | . 27 |

| 3.1.3 Conjugate Gradient Method                                                     | . 29 |

| 3.2 LNS-based Hardware Design of Jacobi Processor                                   | . 32 |

| 3.3 Xilinx EDK HW/SW Codesign of Iterative Methods                                  | . 34 |

| Chapter 4 General Hardware Architectures and HW/SW Codesign of Direct Methods       | 42   |

| 4.1 Alternative Methods of WZ factorization and PIE                                 | 42   |

| 4.1.1 ZW Factorization                                                              | 43   |

| 4.1.2 X Factorization                                                               | 45   |

| 4.2 FPGA-based Hardware Architectures of WZ factorization                           | 47   |

| 4.2.1 Single Unit Architecture                                                      | 48   |

| 4.2.2 Scalable Architecture                                                         | 50   |

| 4.3 Xilinx EDK HW/SW Codesign of WZ Factorization                                   | . 53 |

| 4.4 Reordering Techniques for Sparse Matrix                                         | . 55 |

| Chapter 5 Performance Analysis                                                      | . 58 |

| 5.1 Performance Analysis of Iterative Methods                                       | . 58 |

| 5.1.1 Matlab Comparison of Jacobi, Gauss-Seidel and Conjugate Gradient              | . 58 |

| 5.1.2 Convergence Analysis of LNS-based Jacobi Processor                            | 61   |

| 5.1.3 Xilinx EDK Simulation of Three Iterative Methods                              | 65   |

| 5.1.4 Memory Consideration                                                          | . 69 |

| 5.2 Performance Analysis of Direct Methods                                          | . 70 |

| 5.2.1 Matlab Comparison of LU and WZ                                                | . 70 |

| 5.2.2 Xilinx EDK Simulation of WZ Factorization                                     | . 71 |

| Chapter 6 Conclusions and Future Work                                               | . 74 |

|   | 6.1 Conclusions                 | 74 |

|---|---------------------------------|----|

|   | 6.2 Suggestions for Future Work | 76 |

| A | ppendix A Numerical Examples    | 84 |

# **List of Tables**

| Table 3.1 Functions of five user control registers for CG  | . 40 |

|------------------------------------------------------------|------|

| Table 4.1 Functions of three user control registers for WZ | . 53 |

# **List of Figures**

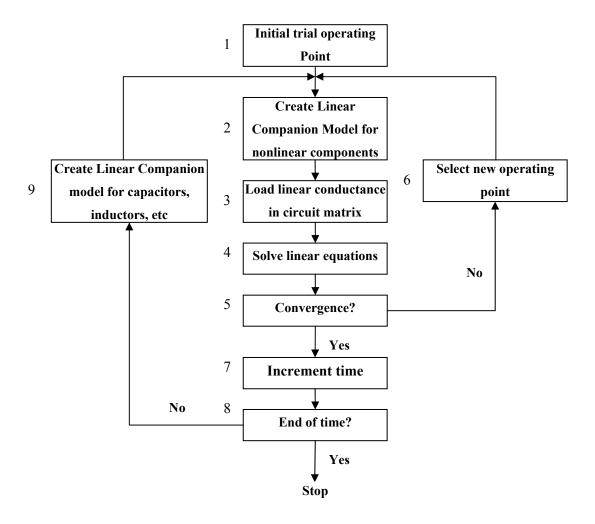

| Figure 2.1: Flow chart of SPICE algorithms                                                | 7   |

|-------------------------------------------------------------------------------------------|-----|

| Figure 2.2: Algorithm description of CG                                                   | 13  |

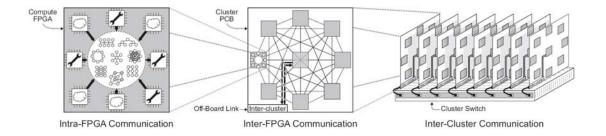

| Figure 2.3: TMD architecture hierarchy [36].                                              | 20  |

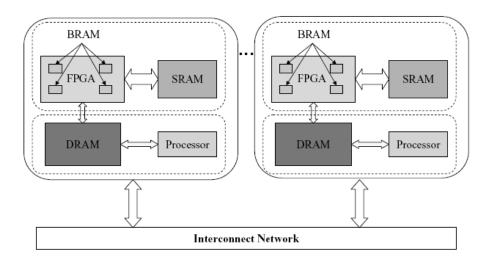

| Figure 2.4: HW/SW partitioned system architecture [40].                                   | 21  |

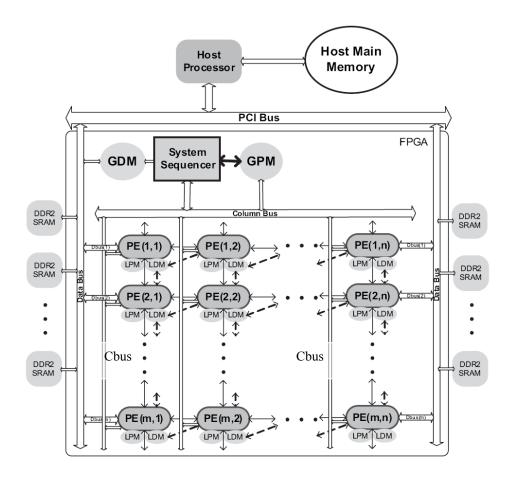

| Figure 2.5: HERA system architecture [43].                                                | 22  |

| Figure 2.6: HERA PE architecture [43]                                                     | 23  |

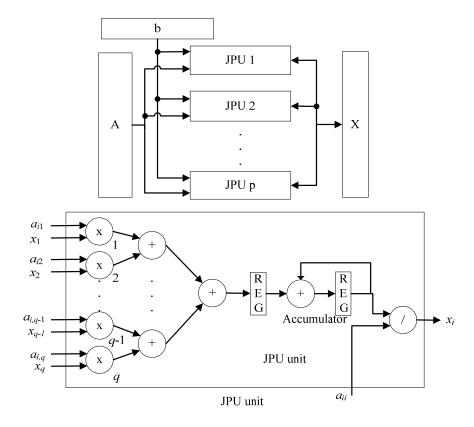

| Figure 3.1: Ideal hardware architecture for Jacobi method                                 | 25  |

| Figure 3.2: Hardware architecture for Jacobi method (case 3)                              | 26  |

| Figure 3.3: Hardware architecture for Jacobi method (case 4)                              | 26  |

| Figure 3.4: Hardware architecture for combined Jacobi and Gauss-Seidel method             | 28  |

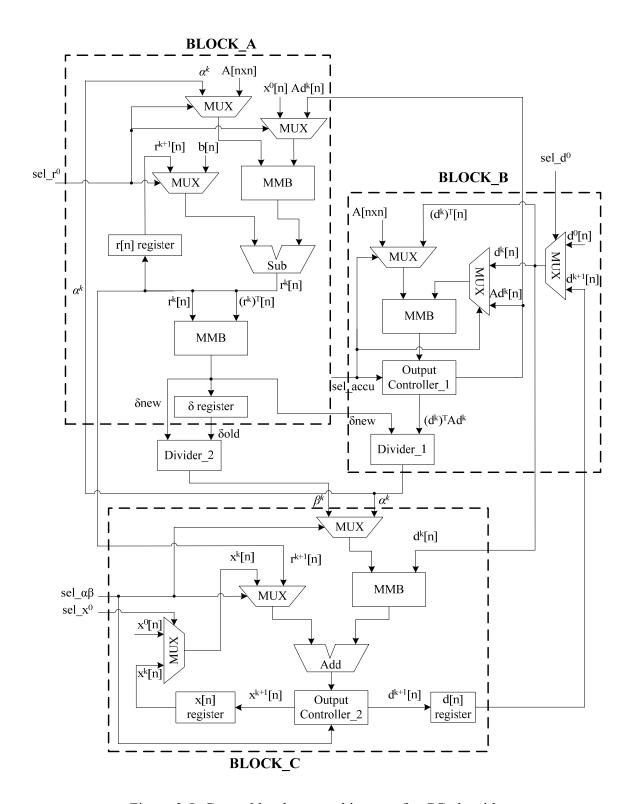

| Figure 3.5: General hardware architecture for CG algorithm                                | 31  |

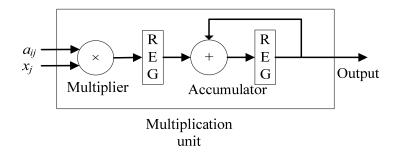

| Figure 3.6: Hardware architecture for multiplication unit                                 | 32  |

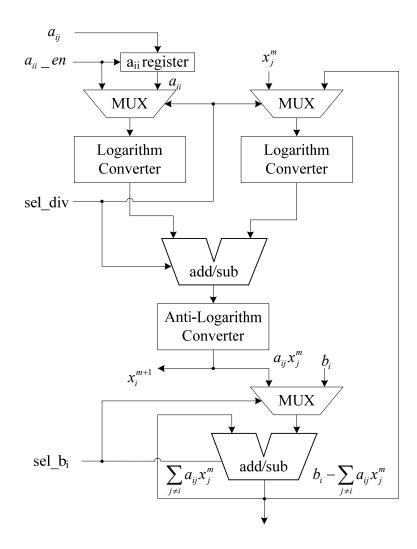

| Figure 3.7: Hardware architecture for LNS-based Jacobi processor                          | 33  |

| Figure 3.8: Hardware architecture for DED                                                 | 34  |

| Figure 3.9: Basic embedded design process flow [18].                                      | 36  |

| Figure 3.10: EDK design simulation stages [18].                                           | 36  |

| Figure 3.11: EDK design architecture of Jacobi, Gauss-Seidel, and CG                      | 38  |

| Figure 3.12: Hardware architecture of MMB                                                 | 38  |

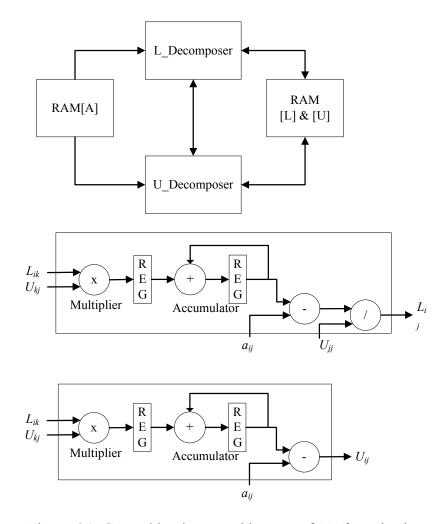

| Figure 4.1: Block diagram of a single unit for WZ factorization method                    | 49  |

| Figure 4.2: Block diagrams of Wsolver and Aupdate                                         | 49  |

| Figure 4.3: Scalable architecture of WZ factorization(case 4).                            | 52  |

| Figure 4.4: EDK design architecture of WZ factorization.                                  | 54  |

| Figure 4.5: Hardware architecture of Update block                                         | 54  |

| Figure 4.6: Sparse matrix in BDB form                                                     | 57  |

| Figure 4.7: Parallel WZ factorization of a sparse BDB matrix                              | 57  |

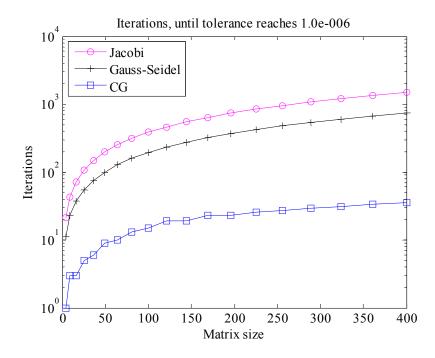

| Figure 5.1: Number of iterations required for solving specific size of linear systems for | or  |

| different tolerance values according to Jacobi, GS and CG method.                         | 59  |

| Figure 5.2: Number of iterations required for solving different size of linear systems    | for |

| specified tolerance value according to Jacobi, GS and CG method.                          | 59  |

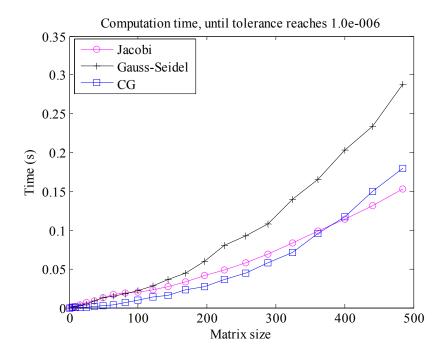

| Figure 5.3: Total computation time required for solving different size of linear systems  |

|-------------------------------------------------------------------------------------------|

| for specified tolerance values according to Jacobi, GS and CG method                      |

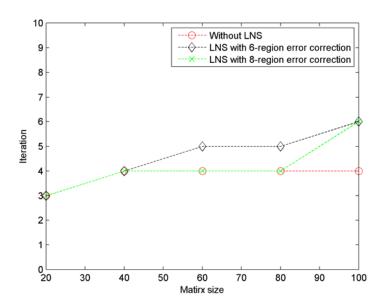

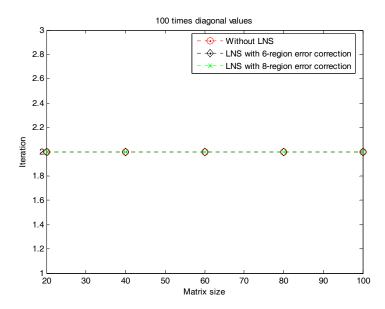

| Figure 5.4 Number of iterations required for solving different size of linear systems for |

| different diagonal values according to Jacobi method with and without using LNS. Scale    |

| factors for diagonal values are ×1.                                                       |

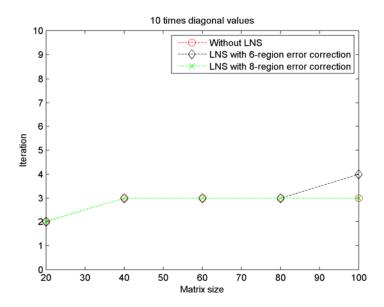

| Figure 5.5 Number of iterations required for solving different size of linear systems for |

| different diagonal values according to Jacobi method with and without using LNS. Scale    |

| factors for diagonal values are ×10.                                                      |

| Figure 5.6 Number of iterations required for solving different size of linear systems for |

| different diagonal values according to Jacobi method with and without using LNS. Scale    |

| factors for diagonal values are ×100.                                                     |

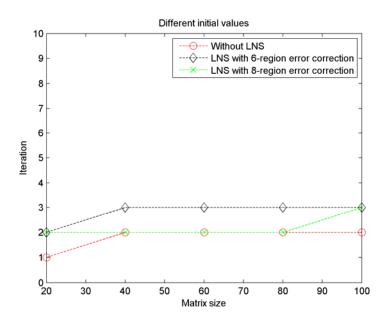

| Figure 5.7 Number of iterations required for solving different size of linear systems     |

| according to Jacobi method with and without using LNS under different initial values 63   |

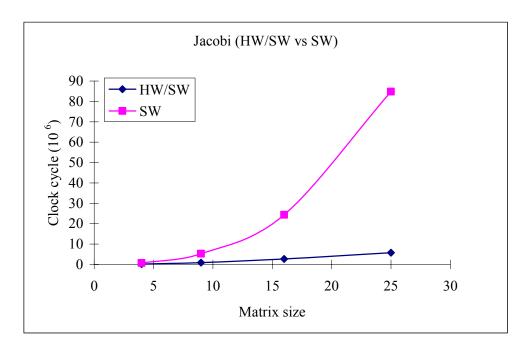

| Figure 5.8: Speed comparison of EDK SW design and HW/SW codesign of Jacobi                |

| method                                                                                    |

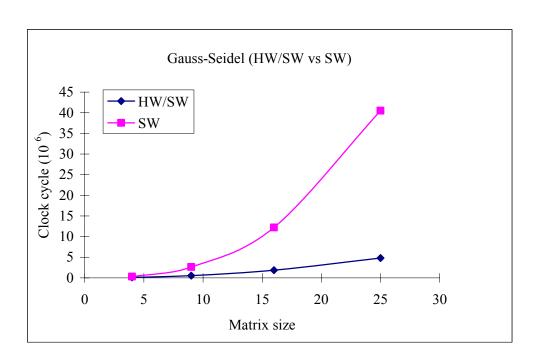

| Figure 5.9: Speed comparison of EDK SW design and HW/SW codesign of GS method             |

| Figure 5.10: Speed comparison of EDK SW design and HW/SW codesign of CG method  67        |

| Figure 5.11: Speed comparison of Jacobi, GS and CG method implemented in EDK SW           |

| and HW/SW codesign for different iteration until convergence                              |

| Figure 5.12: Speed comparison of Jacobi, GS and CG method implemented in EDK SW           |

| and HW/SW codesign for same iteration                                                     |

| Figure 5.13: Computation time for WZ and LU factorization, time difference between        |

| WZ and LU, and computation time for the update of $A_{n-2i}$ in WZ                        |

| Figure 5.14: Speed comparison of EDK based SW design and SW/HW codesign of WZ             |

| factorization                                                                             |

| Figure 6.1: General hardware architecture of LU factorization                             |

#### **List of Abbreviations**

BDB Bordered-Diagonal-Block

BRAM Block Random Access Memory

CG Conjugate Gradient

CGNR Conjugate Gradient on the Normal Equations

DED Diagonal Element Detector

EDK Embedded Development Kit

FIFO First in First out

FPGA Field Programmable Gate Array

FSL Fast Simplex Link

GE Gaussian Elimination

HDL Hardware Description Language

HERA Heterogeneous Reconfigurable Machine

HW/SW Software/Hardware

ISE Integrated Software Environment

JPU Jacobi Processor Unit

JTAG Joint Test Action Group

LNS Logarithmic Number System

LU Lower-Upper

MAC Multiplication and Accumulation

MGT Multi-Gigabit Transceiver

MIMD Multiple-Instruction, Multiple-Data

MMB Matrix Multiplication Block

MPI Message Passing Interface

M-SIMD Multiple-SIMD

NEWS North, East, West and South

OCM On-chip Memory

OPB On-the-Chip-Peripheral Bus

PCB Printed Circuit Board

PCI Peripheral Component Interconnect

PE Processing Element

PIE Parallel Implicit Elimination

PLB Processor Local Bus

PPC Power PC

QIF Quadrant Interlocking Factorization

SDK Software Development Kit

SIMD Single-Instruction, Multiple-Data

SOC System-on-a-Chip

SPICE Simulation Program with Integrated Circuit Emphasis

TMD Toronto Molecular Dynamic

UART Universal Asynchronous Receiver/Transmitter

WZ Matrices in W and Z shapes

XPS Xilinx Platform Studio

ZW Matrices in Z and W shapes

# Chapter 1

## Introduction

Many scientific and engineering problems, such as circuit simulation, applications in electric power networks, and structural analysis [1, 2, 3], involve solving large systems of simultaneous linear equations. Parallel implementations of these computation intensive processes were limited primarily to multiprocessor computers. However due to the exponentially increasing complexity of these applications, the high cost of supercomputing forces us to explore new, sustainable, and affordable high performance computing platforms. Configurable computing [4], where hardware resources are configured appropriately to match specific hardware designs, has recently demonstrated its ability to significantly improve performance for computing intensive applications. With steady advances in silicon technology, as predicted by Moore's Law, Field Programmable Gate Array (FPGA) technologies [5] have enabled the implementation of System-on-a-Chip (SOC) [6] computing platforms, which, in turn, have given a significant boost to the field of configurable computing.

#### 1.1 Motivation

Driven by the advanced fabrication technology of semiconductor and market demand, complexities of sub 200,000 logic gates on a single chip are now moving to 10 million-plus logic gates with 50 million logic gates in sight [7]. The productivity of semiconductor fabrication over the last twenty years has seen a 58% compounded annual growth; however the productivity of chip design has lagged behind, with only a 21% compounded annual rate. This clearly shows the widening productivity gap between design and fabrication. As product life time is decreasing form 3-5 years to 1-2 years, in many cases as short as a few months,

chip design cycles of months or years are no longer acceptable, since time-to-market is of critical importance in the semiconductor industry.

One of the major goals in semiconductor industry is to increase design productivity, which requires improvements in design methodology. Design methodology is a combination of design software, design flow and design techniques by which designers can follow step-by-step to produce a design that meets its functional specification. Functional verifications are very important steps during a design cycle. It is estimated that the functional verification of a design requires up to 70% of all design time [7]. Digital simulator is one of the verification tools which provide faster simulation results but do not guarantee the performance requirements because many of the essential features are not taken into account, for example: power consumption, non-linearity of load capacitors, parasitic feedbacks, and the influence of temperature. Additional steps and software tools are required for verifying these important effects of design, which increase the complexity of design methodology. Circuit simulation such as Simulation Program with Integrated Circuit Emphasis (SPICE) [8] is able to provide much more accurate results by taking those effects into account, but the existing circuit simulators are time consuming when dealing with large size circuits containing millions of components.

It is known that the most time-consuming task in computer simulation of large systems, such as electronic circuits and power systems, is solving large linear systems. Some efforts [9] have been made to exploit the power of parallel computers in speeding up matrix computations. However, case studies [6, 10, 11] showed hardware accelerator can be 1,000 to 10,000 faster than a software simulator core. The research results did not catch much attention mostly because the industry at that time did not have the design challenges as they are facing today. The motivation of this research is to build cost-effective high performance parallel systems using hardware in order to enable the solution of large linear systems, i.e. the solution of matrices.

Matrix solving methods contains two categories: iterative methods [17] and direct methods [16]. Gaussian elimination (GE) and Lower-Upper (LU) factorization [12, 13] are two of

direct methods used in SPICE simulation to solve matrices. Even though these matrix solving methods have been parallelized to run on parallel computers due to the advent of parallel computers, their performance is not satisfactory since both methods are essentially algorithms in which elimination and factorization are performed serially. Most iterative methods such as Jacobi and conjugate gradient (CG) aim at parallel processing, but accuracy is not guaranteed for limited iterations. Direct methods such as WZ factorization [14] and parallel elimination method (PIE) [15] are able to achieve exact solutions without considering rounding off error and solve matrices in parallel compared to LU and GE but mainly target on dense matrices. Since applications like circuit simulation and power systems produce large size sparse matrices, in order to extend parallel properties of these direct methods, reordering technique like minimum fill-in [16] should be used to transform the sparse matrices into bordered-diagonal-block (BDB) forms where submatrices are dense and can be factorized by multiprocessor in parallel.

One possible solution for improving the performance of matrix solving is to develop hardware friendly matrix solving algorithms which can be efficiently implemented in hardware. Hardware friendly algorithms are normally parallel in nature. The independent evaluation procedures of these algorithms are increased over methods like GE and LU, which makes them well suited for hardware design. The success of the proposed solution for matrix solving will simplify the design methodology, narrow the design productivity gap, and also reduce the design cost.

# 1.2 Thesis Overview and Objectives

This thesis focuses on the development of hardware friendly parallel processing algorithms and "sea-of-processor" architectures for the hardware accelerator to replace the software simulator core. The algorithms and architectures are verified by building a prototype using Matlab simulation and FPGA-based hardware device respectively. The detailed objectives are listed as follows:

#### I. Iterative methods

- a. Propose FPGA-based general hardware architectures of Jacobi, combined Jacobi and Gauss-Seidel, and CG methods.

- b. Compare the performance of three iterative methods based on the results of Matlab simulations and FPGA-based HW/SW codesigns.

- c. Convergence analysis of a logarithmic number system (LNS) [19, 20, 21, 22] based Jacobi processor: Due to the complexity of hardware designs of arithmetic units such as multiplier and divider, LNS provides an alternative to floating point with the possibility to simplify arithmetic operations. For matrix solvers, fast multiplication and division operations can be achieved by using addition and subtraction operations on the logarithms of the input data. It is interested to know how the simplified error correction circuit is related to the convergence of Jacobi method.

#### II. Direct methods

- a. Investigate other factorization algorithms, i.e., ZW factorization and X factorization, as alternatives to WZ factorization and PIE respectively.

- b. Propose FPGA-based general single unit and scalable hardware architectures of WZ factorization. Analyze the architectures under different constraints.

- c. Analyze the performance of WZ factorization based on the results of Matlab simulations and FPGA-based HW/SW codesigns. Extend the BDB form to WZ factorization for parallel processing.

#### 1.3 Thesis Outline

There are four primary topics of interest discussed in this thesis, including hardware implementation of iterative methods, hardware implementation of direct methods, performance analysis and suggestions for future work.

Chapter 2 describes the background of circuit simulation, selected iterative and direct methods (i.e., Jacobi, combined Jacobi and Gauss-Seidel, CG, PIE and WZ factorization) targeting on their parallel property for solving sparse and dense matrices, and several existing

hardware architectures for general applications. Chapter 3 discusses FPGA-based general hardware architectures and LNS-based hardware architectures of Jacobi, combined Jacobi and Gauss-Seidel, and CG, followed by HW/SW codesigns of three iterative methods by using Xilinx Embedded Development Kit (EDK) [18]. In Chapter 4, an implementation of WZ factorization is presented. Firstly, ZW factorization and X factorization are introduced as alternatives to WZ factorization and PIE respectively. Single unit and scalable hardware architectures of WZ factorization are proposed and analyzed under different constraints. Xilinx EDK HW/SW codesign of WZ factorization is also presented followed by reordering techniques [16] dealing with large size sparse matrices. This will lead into Chapter 5 where performance of design simulations is analyzed. Finally, the conclusion and suggestions for future work will be given in Chapter 6.

# Chapter 2

# **Background**

The algorithms used in SPICE define the traditional approach to circuit simulation. The goal of this chapter is to provide a brief background of basic concepts of SPICE and major matrix solving methods (i.e., GE and LU factorization) used in SPICE. Since evaluation procedures of GE and LU are not processed in parallel, selected iterative and direct methods (i.e., Jacobi, combined Jacobi and Gauss-Seidel, conjugate gradient, PIE and WZ factorization) which are parallel in nature are introduced for solving sparse and dense matrices. Several existing FPGA based hardware architectures targeting on general applications are also reviewed.

# 2.1 SPICE Algorithm Overview

SPICE [24, 25] is a general purpose analog electronic circuit simulator and is used to provide analysis of circuits containing active components such as bipolar transistors, field effect transistors, diodes and passive components such as resistors, capacitors and inductors. The program originates from the University of California, Berkeley. SPICE is a powerful program which allows designers to evaluate designs without actually building them.

Most of SPICE algorithms [25] can be explained by the following block diagram shown in Figure 2.1. The key of all algorithms inside SPICE is nodal analysis (blocks 3 and 4) including formulating the nodal matrix and solving the nodal matrix for the circuit voltages. The inner loop (blocks 2-6) finds the solution for nonlinear circuits where nonlinear devices are replaced by equivalent linear models. The solution process starts with an initial guess (block 1), goes through the inner loop (blocks 2-6), and repeats until it reaches convergence. The time domain solution is represented by the outer loop (blocks 7-9), together with the inner

Figure 2.1: Flow chart of SPICE algorithms

loop, it performs a transient analysis creating equivalent linear models for energy-storage components such as capacitors, inductors, etc.

SPICE begins an analysis by reading elements from the input file. Using matrix construction by inspection and a set of predefined element templates [25], system equations are described in a set of linear matrices. SPICE has two solution algorithms, one for linear circuits and one for nonlinear circuits. For linear circuits, only two of the blocks are needed: load the Nodal Matrix (block 3) using Kirchhoff's current law [26] and solve the nodal matrix (block 4) using GE or LU factorization. For Non-Linear circuits, SPICE needs to create equivalent linear models for the non-linear devices such as diode. The loop (blocks 1-6)

iteratively finds the exact solution as follows: guess an operating point, create equivalent linear models and solve the nodal matrix for the circuit voltages. Then, choose a new operating point (block 6) based on the new voltages and start the loop again until the voltage and current reach convergence.

### 2.2 Matrix Solving Methods Used in SPICE

#### 2.2.1 Gaussian Elimination (GE)

GE and LU factorization [12, 13] are two major methods used in SPICE to solve matrix. GE contains forward elimination and backward substitution. Forward elimination uses scaling of each equation followed by subtraction from the remaining equations in order to eliminate unknowns one by one until matrix A is reduced to an upper triangular matrix. The final solution can then be found by backward substitution which computes each element of x in reverse order. Using GE method, any linear system equation can be solved in at most cubic time. Consider the system of linear equations Ax = b shown in Equation 2.1.

$$\begin{bmatrix} a_{11} & a_{12} & \dots & a_{1n} \\ a_{21} & a_{22} & \dots & a_{2n} \\ \dots & \dots & \dots & \dots \\ a_{n1} & a_{n2} & \dots & a_{nn} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ \dots \\ x_n \end{bmatrix} = \begin{bmatrix} b_1 \\ b_2 \\ \dots \\ b_n \end{bmatrix}$$

$$(2.1)$$

Assume solution  $x = [x_1^k, x_2^k, ..., x_n^k]$ , which can be obtained in two steps:

First step: column elimination.

$$e_{i} = (a_{i1}, a_{i2}, ..., a_{in}),$$

$$e_{i}^{(j)} = e_{i} - (a_{ij} / a_{jj})e_{j},$$

$$b_{i}^{(j)} = b_{i} - (a_{ij} / a_{jj})b_{j},$$

(2.2)

where j = 1, 2,..., n-1 representing  $j_{th}$  column elimination stages and i = j+1, j+2,..., n representing  $i_{th}$  row of matrix A. The first step repeats for j = 1, 2,..., n-1 until the system is transformed into a right triangular matrix shown in Equation 2.3.

$$\begin{bmatrix} a_{11} & a_{12} & \dots & a_{1n} \\ 0 & a_{22}^{(1)} & \dots & a_{2n}^{(1)} \\ \dots & \dots & \dots & \dots \\ \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & \dots & a_{nn}^{(n-1)} \end{bmatrix} \begin{bmatrix} x_1 \\ x_2 \\ \vdots \\ x_n \end{bmatrix} = \begin{bmatrix} b_1 \\ b_2^{(1)} \\ \vdots \\ b_n^{(n-1)} \end{bmatrix}$$

$$(2.3)$$

Second step: back-substitution process. x is solved starting from  $x_n$  using Equation 2.4 upwards to  $x_1$  using Equation 2.5. The entire process is done serially.

$$x_n^k = \frac{b_n^{(n-1)}}{a_{nn}^{n-1}}. (2.4)$$

$$x_i^k = \frac{1}{a_{ii}^{(i-1)}} \left[ b_i^{(i-1)} - \sum_{j=i+1}^n a_{i,j}^{(i-1)} x_j^k \right]$$

for  $i = n-1, n-2,..., 1$ . (2.5)

#### 2.2.2 LU Factorization

The LU factorization decomposes matrix as the product of a lower and upper triangular matrices. There are several ways for LU factorization such as Doolittle's method and Crout's methods [12]. Doolittle's method has all 1's in the diagonal of lower triangular matrix as showed in Equations 2.6. The factorization process begins with the first row of upper triangular matrix U using Equation 2.7 followed by the first column of lower triangular matrix U using Equation 2.8. The evaluation process repeats with second row of matrix U followed by the second column of matrix U until the last row of matrix U and the last column of matrix U are found. The Crout's method is similar to Doolittle's except that  $U_{kk} = 1$  instead of  $U_{kk} = 1$  and the factorization process begins with first column of matrix U followed by the first row of matrix U.

$$\begin{bmatrix} a_{11} & a_{12} & \dots & a_{1n} \\ a_{21} & a_{22} & \dots & a_{2n} \\ \dots & \dots & \dots & \dots \\ a_{n1} & a_{n2} & \dots & a_{nn} \end{bmatrix} = \begin{bmatrix} 1 & 0 & \dots & 0 \\ L_{21} & 1 & & & 0 \\ \dots & \dots & \dots & \dots \\ \dots & \dots & \dots & \dots \\ L_{n1} & L_{n2} & \dots & 1 \end{bmatrix} \begin{bmatrix} U_{11} & U_{12} & \dots & U_{1n} \\ 0 & U_{22} & \dots & U_{2n} \\ \dots & \dots & \dots & \dots \\ \dots & \dots & \dots & \dots \\ 0 & 0 & \dots & \dots & \dots \end{bmatrix}$$

(2.6)

$$U_{ij} = a_{ij} - \sum_{k=1}^{i-1} L_{ik} U_{kj}$$

for  $i = 1, 2, ..., n$  and  $j = i, i+1, ..., n$ . (2.7)

$$L_{ij} = (a_{ij} - \sum_{k=1}^{j-1} L_{ik} U_{kj}) \frac{1}{U_{ji}} \quad \text{for } j = 1, 2, ..., n-1 \text{ and } i = j+1, j+2, ..., n.$$

(2.8)

After factorization of matrix A, Equation 2.1 can be rewritten as Ax = LUx = b. For given A and b, the solution x can be obtained in two steps: Firstly, solving the equation Ly = b for y; Secondly, solving Ux = y for x. In these two steps, y and x can be solved directly using forward and backward substitution due to factorized lower and upper triangular matrices. The algorithm description shows that LU factorization is more trivial and requires twice substitution in order to solve x, but it is computationally efficient when a matrix equation is solved for multiple times for different b as compared to GE.

GE and LU factorization have been modified for parallel processing due to the advent of parallel computing [9], their performance is still not satisfactory since both methods are essentially algorithms in which elimination and factorization are processed in serial, i.e., only one row or one column is solved at a time. In next section, selected matrix solving methods which are more suitable for parallel computation and aim at a parallel machine will be introduced.

# 2.3 Parallel Iterative Matrix Solving Methods

#### 2.3.1 Jacobi Iterative Method

The Jacobi method [12] is an algorithm in linear algebra for determining the solutions of linear systems with largest absolute values in each row and column dominated by the

diagonal elements. Each diagonal element is solved for, and an approximate value plugged in. The process is then iterated until it converges. The solution to set of linear equations, expressed in matrix terms as Equation 2.1, where A is an  $n \times n$  matrix, is obtained as follows: Let A = L + D + U, where L is the lower triangular matrix containing all elements of A below the diagonal, U is the upper triangular matrix containing all elements of A above the diagonal, and D is the diagonal matrix consisting of only the diagonal elements. Substituting A = L + D + U into Equation 2.1 yields

$$x = D^{-1} [b - (L + U)x]$$

(2.9)

The Jacobi method can be expressed as:

$$x_i^{k+1} = \frac{1}{a_{ii}} \left[ b_i - \sum_{j \neq i} a_{ij} x_j^k \right]$$

for  $i = 1, 2, ..., n$ . (2.10)

Initially guess  $x^0 = \left[x_1^0, x_2^0, ... x_n^0\right]$ , substitute  $x^0$  into the right-hand side of Equation 2.10 to calculate new, possibly more accurate, values of  $x_i$ . This evaluation process repeats until the convergence condition is met. Jacobi will always converge if the matrix A is strictly diagonally dominant, which means that for each row, the absolute value of the diagonal term is greater than the sum of absolute values of other terms shown in Equation 2.11.

$$\left|a_{ii}\right| > \sum_{i \neq j} \left|a_{ij}\right| \tag{2.11}$$

The Jacobi method sometimes converges even if this condition is not satisfied. It is necessary, however, that the diagonal terms in the matrix are greater (in magnitude) than the other terms. Furthermore, Jacobi is barely used as a stand-alone solver, but rather as a preconditioner to reduce the condition number, thus increase the rate of convergence for more advanced iterative methods like conjugate gradient [27].

#### 2.3.2 Combined Jacobi and Gauss-Seidel

Unlike Jacobi method, Gauss-Seidel method [12] uses new values of  $x_i$  as soon as they become available. For example, when calculating  $x_2^1$ , the new value  $x_1^1$  is used instead of the old value of  $x_1^0$ . The Gauss-Seidel can be expressed as:

$$x_i^{k+1} = \frac{1}{a_{ii}} \left[ b_i - \sum_{j < i} a_{ij} x_j^{(k+1)} - \sum_{j > i} a_{ij} x_j^{(k)} \right]$$

(2.12)

There are two important characteristics of the Gauss-Seidel method. Firstly, the computations are processed in serial. Since each component of the new iterate depends upon all previously computed components, the updates cannot be done simultaneously as in the Jacobi method. Secondly, the new iterate  $x^{k+1}$  depends upon the order in which the equations are examined. If this ordering is changed, the components of new iterates will also change. A more hardware friendly approach is to combine Jacobi and Gauss-Seidel methods. In this combined method, a number of variables, x, are calculated in parallel dependent upon available hardware resource. If the hardware resource allows maximum p variables to be calculated in parallel,  $x_1, x_2... x_p$  are calculated first. The new values are used for calculating the next p variables,  $x_{p+1}, x_{p+2}... x_{2p}$ , and so on.

# 2.3.3 Conjugate Gradient (CG)

Conjugate gradient (CG) [27, 28] is an algorithm for finding the nearest local minimum of a system of *n* variables which assumes that the gradient of the function can be computed. CG derives its name from the fact that it generates a sequence of conjugate (or orthogonal) vectors and uses conjugate vectors as search directions instead of the local gradient for going downhill until the final solution is reached. CG is effective for the numerical solution of particular linear systems, namely those whose matrix is symmetric and positive-definite, since storage for only a limited number of vectors is required [29, 30, 31].

CG proceeds by generating vector sequences  $x^{k+1}$  of iterates, i.e., successive approximations to the solution, residuals  $r^{k+1}$  corresponding to iterates, and search directions

```

%Start

%Begin with first iterate.

k = 0

%Set up initial values, where search direction

is equal to the residual for the first iterate.

d^0 = r^0 = b - Ax^0

\delta_{now} = (\mathbf{r}^0)^{\mathrm{T}} \mathbf{r}^0

while k < k_{max} do

\alpha^{k} = \frac{\delta_{new}}{(\mathbf{d}^{k})^{T} \mathbf{A} \mathbf{d}^{k}}

%Update new values of solution x.

\mathbf{x}^{k+1} = \mathbf{x}^k + \alpha^k \mathbf{d}^k

%Update new values of residual r.

\mathbf{r}^{k+1} = \mathbf{r}^k - \alpha^k \mathbf{A} \mathbf{d}^k

\delta_{old} = \delta_{new}

\delta_{new} = (\mathbf{r}^{k+1})^{\mathrm{T}} \mathbf{r}^{k+1}

\beta^{k} = \frac{\delta_{new}}{\delta_{st}}

%Update new values of search direction d.

\mathbf{d}^{k+1} = \mathbf{r}^{k+1} + \mathbf{\beta}^k \mathbf{d}^k

%Increase iterate.

k = k + 1

%End

```

Figure 2.2: Algorithm description of CG

$d^{k+1}$  used in updating iterates and residuals. Considering the linear system Ax = b in Equation 2.1, denote the initial guess for x by  $x^0$ . The resulting algorithm is summarized in Figure 2.2. The input vector  $x^0$  can be an approximate initial solution or zero.

CG method can also be applied to an arbitrary system where A is not symmetric, not positive-definite, and even not square by transforming A into normal equations  $A^{T}A$  and right-hand side vector b into  $A^{T}b$  shown in Equation 2.13, since  $A^{T}A$  is a symmetric positive

definite matrix for any A. The result is called conjugate gradient on the normal equations (CGNR).

$$A^T A x = A^T b, (2.13)$$

However, the downside of forming the normal equations is that the condition number  $\kappa(A^TA)$  is equal to  $\kappa(A)^2$  and so the rate of convergence of CGNR may be very slow.

# 2.4 Parallel Direct Matrix Solving Methods

#### 2.4.1 Parallel Implicit Elimination (PIE)

PIE method for the solution of linear system was introduced by Evans and Abdullah [14, 32]. This method simultaneously eliminates two matrix elements, in stead of just one in GE. Thus, PIE is suitable for parallel implementation. Considering the linear system Ax = b in Equation 2.1, the basis of PIE method is to transform matrix A into butterfly form Z as shown in Equation 2.14 by multiplying matrix A with transformation matrix W. This transformation process is called parallel elimination.

By combining WA=Z and Ax=b, WAx=Wb is obtained, which can be rewritten as Zx=b', where b'=Wb. Vector b is also updated once matrix Z is obtained. The solution process of PIE is similar to the solution procedure shown in WZ factorization. In this section, only the transformation process will be introduced, which is summarized as follows: Matrix A is denoted in shorthand form in Equation 2.15.

$$A = \begin{bmatrix} a_{11} & a_{1j} & a_{1n} \\ a_{i1} & A_{ij} & a_{in} \\ a_{n1} & a_{nj} & a_{nn} \end{bmatrix}$$

for  $i, j = 2, 3, ..., n-1$ . (2.15)

For the first evaluation stage, the transformation matrix W is shown in Equation 2.16.

$$W_{1} = \begin{bmatrix} 1 & 0 & 0 \\ -w_{i1} & I_{n-2} & -w_{in} \\ 0 & 0 & 1 \end{bmatrix}$$

(2.16)

where i = 2, 3, ..., n-1 and  $I_{n-2}$  is the unit matrix of order n-2. Elimination is achieved by taking product of  $W_1$  and A.

$$W_{1}A = \begin{bmatrix} 1 & 0 & 0 \\ -w_{i1} & I_{n-2} & -w_{in} \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} a_{11} & a_{1j} & a_{1n} \\ a_{i1} & A_{ij} & a_{in} \\ a_{n1} & a_{nj} & a_{nn} \end{bmatrix}$$

$$= \begin{bmatrix} a_{11} & a_{1j} & a_{1n} \\ -a_{11}w_{i1} + a_{i1}I_{n-2} - a_{n1}w_{in} & -w_{i1}a_{1j} + A_{ij} - w_{in}a_{nj} & -a_{1n}w_{i1} + a_{in}I_{n-2} - a_{nn}w_{in} \\ a_{n1} & a_{nj} & a_{nn} \end{bmatrix}$$

$$(2.17)$$

Referring to Equation 2.14, in order to meet  $W_1A = Z$ ,  $-a_{11}w_{i1} + a_{i1}I_{n-2} - a_{n1}w_{in}$  and  $a_{1n}w_{i1} + a_{in}I_{n-2} - a_{nn}w_{in}$  shown in Equation 2.17 need to be equal to zero. By solving n-2 sets of  $2\times 2$  equations, matrix  $Z_1$  can be obtained in the form of Equation 2.18.

$$Z_{1} = \begin{bmatrix} a_{11} & a_{1j} & a_{1n} \\ 0 & A'_{n-2} & 0 \\ a_{n1} & a_{nj} & a_{nn} \end{bmatrix}$$

for  $j = 2, 3 \dots n-1$ . (2.18)

$A_{n-2}$  is the remaining matrix of order n-2, which is updated by Equation 2.19.

$$A'_{n-2} = -w_{i1}a_{1j} + A_{n-2} - w_{in}a_{nj}$$

(2.19)

This evaluation process recursively repeats for (n-1)/2 stages. The final matrix Z is obtained in the form of Equation 2.14. An example of PIE is given in Appendix A.

#### 2.4.2 WZ Factorization

WZ factorization was introduced by Evans and Hatzopoulos in 1973 [15, 33]. A method using WZ factorization to solve matrix is called quadrant interlocking factorization (QIF) [14]. WZ method decomposes coefficient matrix A into two interlocking quadrant factors of butterfly form denoted by W and Z or as

$$A = WZ \tag{2.20}$$

where W and Z are shown in Equations 2.21 and 2.22,

and

$$Z = \begin{bmatrix} z_{11} & z_{12} & z_{13} & \cdots & z_{1,n-2} & z_{1,n-1} & z_{1n} \\ z_{22} & z_{23} & \cdots & z_{2,n-2} & z_{2,n-1} \\ & & & & & & & \\ & & z_{33} & \cdots & z_{3,n-2} \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & & \\ & & & & \\ & & &$$

Equation 2.20 can be rewritten as

$$\begin{bmatrix} a_{11} & a_{1i} & a_{1n} \\ a_{i1} & A_{n-2} & a_{in} \\ a_{n1} & a_{ni} & ann \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ w_{i1} & W_{n-2} & w_{in} \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} z_{11} & z_{1i} & z_{1n} \\ 0 & Z_{n-2} & 0 \\ z_{n1} & z_{ni} & z_{nn} \end{bmatrix}$$

(2.23)

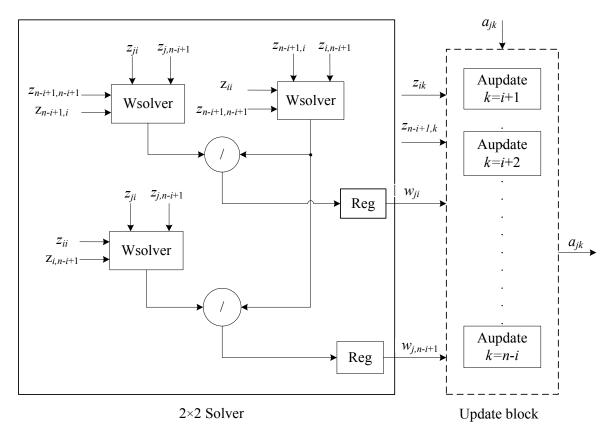

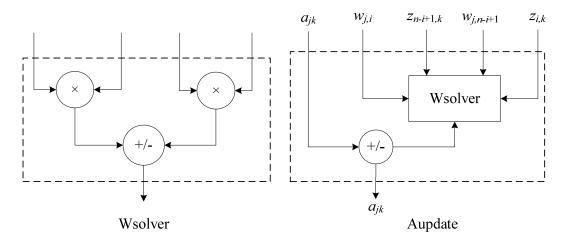

The elements of matrices W and A can be evaluated in (n-1)/2 distinct stages. The basic steps are summarized as follows.

At the first stage, it can be observed that the elements of first and last rows of the matrix Z are obtained by

$$a_{11} = z_{11}, \ a_{1i} = z_{1i}, \ a_{1n} = z_{1n}$$

$a_{n1} = z_{n1}, \ a_{ni} = z_{ni}, \ a_{nn} = z_{nn} \text{ for } i = 2, 3, ..., n-1.$  (2.24)

The elements of the first and last columns of the matrix W are evaluated by solving (n-2) sets of  $2\times 2$  linear systems given by

$$z_{11}w_{i1} + z_{n1}w_{in} = a_{i1}$$

$$z_{1n}w_{i1} + z_{nn}w_{in} = a_{in} \quad \text{for } i = 2, 3, ..., n-1.$$

(2.25)

In general, each 2×2 linear system is solved by Cramer's rule using Equation 2.26.

$$\begin{aligned}

x_{1} &= z_{ii} z_{n-i+1,n-i+1} - z_{n-i+1,i} z_{i,n-i+1}, \\

x_{2} &= a_{ji} z_{n-i+1,n-i+1} - z_{n-i+1,i} a_{j,n-i+1}, \\

x_{3} &= z_{ii} a_{j,n-i+1} - a_{ji} z_{i,n-i+1},

\end{aligned}$$

$$W_{ji} = \frac{x_{2}}{x_{1}}$$

$$W_{j,n-i+1} = \frac{x_{3}}{x_{1}}$$

(2.26)

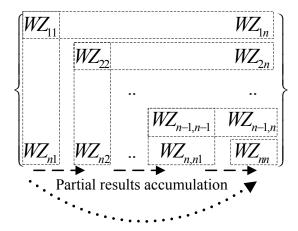

The remaining matrix  $A_{n-2}$  is then updated by Equation 2.27.

$$a_{ij} = a_{ij} - w_{i1}z_{1j} - w_{in}z_{nj}$$

for  $i, j = 2, 3...n-1$  (2.27)

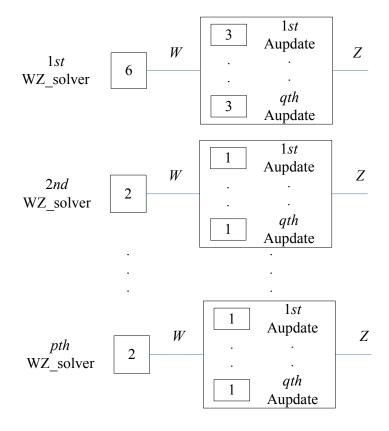

For the following evaluation stages, this evaluation process is recursively repeated for the remaining matrices  $A_{n-2i}$  (i.e.  $A_{n-2}$ ,  $A_{n-4}$ ...2 for n is even and  $A_{n-2}$ ,  $A_{n-4}$ ...1 for n is odd.).

In order to solve the system by the QIF method, Ax=b can be rewritten as (WZ)x = b. Only two related and simpler linear systems of forms Wy = b and Zx = y need to be solved. The solution procedure for y is carried out in pairs from top and bottom. In general, at  $i_{th}$  stage,

$$y_i = b_i \text{ and } y_{n-i+1} = b_{n-i+1}$$

(2.28)

Then update  $b_i$  using Equation 2.29.

$$b'_{i} = b_{i} - w_{ii}y_{i} - w_{i,n-i+1}y_{n-i+1}$$

for  $j = i+1, i+2 \dots n-i$ . (2.29)

The final solution x is computed from the middle of matrix Z. This process can be distinguished into two cases: n is odd and n is even. If n is odd,  $x_{(n+1)/2}$  is obtained by Equation 2.30.

$$x_{\frac{1}{2}(n+1)} = \frac{y_{\frac{1}{2}(n+1)}}{z_{\frac{1}{2}(n+1),\frac{1}{2}(n+1)}}$$

(2.30)

Update y for next stage,

$$y_{j}' = y_{j-} x_{\frac{1}{2}(n+1)} z_{\frac{1}{2}(n+1)}$$

for  $j = 1, 2...n, j \neq \frac{1}{2}(n+1)$  (2.31)

The remaining elements of x can be obtained in pairs by solving (n-1)/2 sets of  $2\times 2$  linear equations. If n is even, x can be evaluated directly by solving n/2 sets of  $2\times 2$  linear equations starting with  $x_{(n-1)/2}$  and  $x_{(n+1)/2}$ . In general, at  $i_{th}$  stage, solve Equation 2.32 to obtain the values of x,

$$z_{ii}x_i + z_{i,n-i+1}x_{n-i+1} = y_i$$

$$z_{n-i+1}x_{i+2n-i+1}x_{n-i+1} = y_{n-i+1}$$

(2.32)

and update  $y_i$  in Equation 2.33.

$$y_{j} = y_{j} - x_{i}z_{ji} - x_{n-i+1}z_{j,n-i+1}. (2.33)$$

An example of WZ factorization is given in Appendix A.

# 2.4.3 Comparison of Direct Methods

As LU factorization compared to GE, WZ factorization is more trivial and requires twice substitution in order to solve x, but is computationally efficient to solve a matrix equation multiple times for different b compared to PIE. According to the similarity of evaluation processes, the first type of comparison can be made between PIE and GE. During the elimination stage of PIE method, two columns of transformation matrix W are solved or two rows of matrix Z are eliminated simultaneously. The solution stage of PIE starts from the middle of vector x being completed bi-directionally in parallel resulting in increased stability. GE is only able to eliminate one column and solve one x at a time. In general, the timings on multiprocessor for PIE are better than GE. For the larger matrices the gains of speed up vary

from 6% for 1 processor to 10% for 10 processors [14]. These gains will increase for larger matrices and larger number of processors.

The second type of comparison can be made between WZ and LU. The WZ factorization solves W elements from left and right and Z elements from top and bottom bi-directionally which is similar as PIE method. The solution stage of WZ solves two values simultaneously from the top and bottom moving inwards bi-directionally for vector y and from the middle moving outwards bi-directionally for vector x. LU is only able to solve one row of U followed by one column of L at a time. The solution stage of LU is also processed in serial. The timings on the sequent multiprocessor show that the WZ factorization is faster than LU and for larger matrices, the gains appear to be 20% for all values of processor [33].

## 2.5 Hardware Architectures for General Applications

The flexibility, re-programmability and run-time reconfigurability of FPGAs have great potential to offer an alternative computing platform for high performance computing. Recent significant advances in FPGA technology and the inherent advantages of configurable logic have brought new research efforts in the configurable computing field: parallel processing on configurable chips [34, 35]. In this section, three FPGA based hardware architectures are reviewed for general applications.

# 2.5.1 Toronto Molecular Dynamic (TMD) Architecture

TMD was designed for molecular dynamics simulations [36, 37]. This architecture can also be used to solve other computing-intensive problems. The architecture is built entirely using FPGA computing nodes which are implemented by Virtex-II Pro XC2VP100 FPGAs [38]. The machine enables designers to implement large-scale computing applications using a heterogeneous combination of hardware accelerators and embedded microprocessors spread across many FPGAs, all interconnected by three levels communication networks.

The TMD architecture is divided into there hierarchical tiers shown in Figure 2.3, allowing it to scale up to reconfigurable machine containing many FPGAs. The lowest tier exists within

Figure 2.3: TMD architecture hierarchy [36].

FPGA, where different topologies can be specified for interconnecting computing engines and embedded processors. The middle tier is based on cluster printed circuit board (PCB) level which consists of 8 FPGAs for computing purpose and 1 FPGA for communicating with other clusters. The highest tier is the large network by interconnecting multiple clusters.

TMD communications networks can be divided into there levels. The first level is intra-FPGA communication which is implemented using point-to-point unidirectional FIFOs. The second level is inter-FPGA communication which uses multi-gigabit transceiver (MGT) [39] hardware to implement communication between FPGAs. The third level is inter-cluster communication by aggregating four MGT links, enabling the use of infiniband switches for implementing global interconnection between clusters.

# 2.5.2 Hardware/Software (HW/SW) Partitioned Computing System

Usually, a reconfigurable computing system has multiple nodes which can be implemented by processors, FPGAs, or both. This hybrid architecture [40] utilized both the processors and the FPGAs in the system for computing purpose, as shown in Figure 2.4. The design is based on Cray XD1 [41]. The basic unit is a computing blade, which consists of two AMD 2.2 GHz processors and one Xilinx Virtex-II Pro XC2VP50 [38]. Six computing blades fit into one chassis, interconnected by a non-blocking cross-bar switching fabric which provides two 2GB/s links to each node. The nodes communicate using Message Passing Interface (MPI) [42]. In this system, only the processors of the blades (nodes) are connected through communication network.

Figure 2.4: HW/SW partitioned system architecture [40].

For different applications, tasks capable of different functions need to be specified. The HW/SW partition is based on the workload of the task so that processor and FPGA are both fully utilized. In other word, the computation times of processor and FPGA need to be equal considering the data transfer time and communication costs. Other than workload partition, the coordination between processor and FPGA is also very important.

# 2.5.3 Mixed-Mode Heterogeneous Reconfigurable Machine (HERA) Architecture

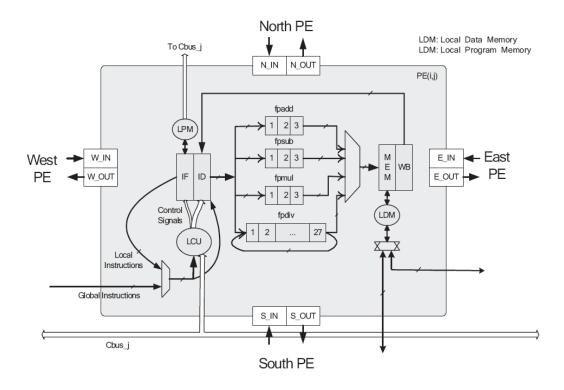

The HERA machine [43] is based on Xilinx Virtex-II and Virtex-II pro platform FPGAs. This machine can implement the single-instruction, multiple-data (SIMD), multiple-instruction, multiple-data (MIMD) and multiple-SIMD (M-SIMD) execution modes in one machine.

Figure 2.5 shows the general architecture of HERA machine with  $m \times n$  processing elements (PEs) interconnected by a 2-D mesh network. The architecture employs fast, direct North, East, West and South (NEWS) connections for communications between nearest neighbors. The global communication is achieved by the Cbus and column bus. Every column has a Cbus and all the Cbuses are connected to the column bus. Every PE is built on a single-precision IEEE 754 FPU [44, 45] with tightly-coupled local memory shown in Figure 2.6, and supports

Figure 2.5: HERA system architecture [43].

dynamic switching among SIMD, MIMD and M-SIMD at runtime. Most of the instruction decoding is carried out by the local control unit within PE. The computing process is controlled by a system sequencer that communicates with the host processor via the peripheral component interface (PCI) bus. The capabilities of each PE and the number of PEs can be reconfigured on the basis of the application's requirements and available resources in target FPGA devices respectively. The operating mode of each PE is configured dynamically by the host processor through the operating mode register of PE.

In this chapter, background related to SPICE, selected parallel matrix solving methods and the existing FPGA-based hardware architectures for general applications have been reviewed. GE and LU are two major direct matrix solving methods used in SPICE, which are processed in serial. To improve the performance of matrix solving process, FPGA-based hardware

Figure 2.6: HERA PE architecture [43]

implementations of parallel matrix solving methods are desired. Most iterative methods such as Jacobi and CG aim at parallel processing for solving large sparse matrices. In Chapter 3, FPGA-based general hardware architectures, LNS-based hardware designs and FPGA-based HW/SW codesigns of Jacobi, combined Jacobi and Gauss-Seidel, and CG are presented.

# Chapter 3

# General Hardware Architectures and HW/SW Codesigns

## of Iterative Methods

In computational mathematics, an iterative method attempts to solve a problem (for example an equation or a linear system) by using successive approximations to obtain more accurate solutions at each step starting from an initial guess. The goal of this chapter is to provide detailed approaches to FPGA-based hardware design including FPGA-based general hardware architectures, LNS based hardware designs and FPGA-based HW/SW codesigns to Jacobi, combined Jacobi and Gauss-Seidel, and CG for solving sparse matrices.

#### 3.1 FPGA-based Hardware Architectures

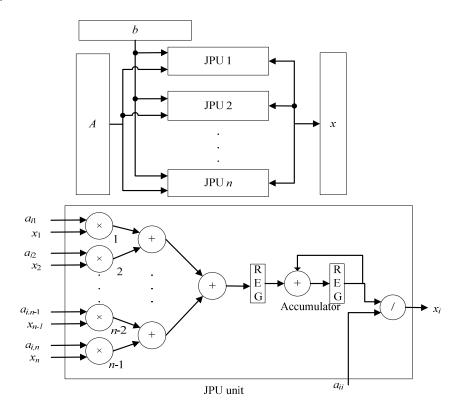

#### 3.1.1 Jacobi Iterative Method

Assume no memory constraint. An ideal hardware architecture for Jacobi method would consists of n Jacobi processor units (JPU) for n-vector x, where JPU is the basic unit of Jacobi hardware architecture. Within each JPU there are n-1 multipliers, 1 divider, and binary tree adders/subtractors as showed in Figure 3.1. This architecture requires  $n \times (n-1)$  multipliers in total. Multiplication of inputs  $a_{ij}$  and  $x_j$  are processed in parallel for each  $x_i$  and new n-vector x is updated in parallel as well, where i, j = 1, 2, ..., n and  $j \neq i$ . Considering the hardware resource, several other possible cases have been considered, where different case has different JPU.

1. n JPUs, 1 multiplier in each JPU: Multiplications of inputs  $a_{ij}$  and  $x_j$  are processed serially in each JPU. For each iteration, output for each x will be obtained and updated

in parallel which means new value for each x is updated once all the outputs new  $x_i$  are available.

- 2. 1 JPU and n-1 multipliers in the JPU: Multiplication of inputs  $a_{ij}$  and  $x_j$  are processed in parallel for each x. Output x's will be obtained and updated serially. This architecture is actually equivalent to an ideal architecture for Gauss-Seidel method.

- 3. p(p < n) JPUs and 1 multiplier in each JPU: A subset of n-vector x are processed in parallel at a time which requires  $\lceil n/p \rceil$  number of times to process the n-vector x, where  $\lceil \rceil$  is a ceiling function. Inside each JPU, multiplications of inputs  $a_{ij}$  and  $x_j$  are processed serially.

- 4. 1 JPU and l multipliers in each JPU: A subset of multiplications of inputs  $a_{ij}$  and  $x_j$  are processed in parallel at a time which requires  $\lceil (n-1)/l \rceil$  number of times to process one  $x_i$ .

Figure 3.1: Ideal hardware architecture for Jacobi method

Figure 3.2: Hardware architecture for Jacobi method (case 3)

Figure 3.3: Hardware architecture for Jacobi method (case 4)

Cases 1 and 2 are applicable to small linear systems which require less hardware resource for implementation. Cases 3 and 4 have scalable architectures and can be applied to large linear systems considering the available hardware resource in reality. Figure 3.2 shows a hardware architecture which implements case 3. For each iteration, a set of coefficients,  $a_{p+1,q}$ ,  $a_{p+2,q}$ ,...,  $a_{2p,q}$  from A and  $x_q$  from x are placed at the inputs of JPU 1 to p. After n clock cycles (i.e. for q = 1 to n), a total of p number of new  $x_i$  are generated and loaded into x. The first set of new  $x_i$  are  $x_1, x_2, ..., x_p$ , the second set of new  $x_i$  are  $x_{p+1}, x_{p+2}, ..., x_{2p}$ , and so on. The second iteration repeats from  $x_1, x_2, ..., x_p$  until convergence has been reached.

Figure 3.3 shows a hardware architecture which implements case 4. This architecture parallelizes multiplications inside each JPU instead of having multiple JPUs processed in parallel. For each iteration, a set of coefficients,  $a_{k,l+1}$ ,  $a_{k,l+2}$ ,..., $a_{k,2l}$  from A and  $x_{l+1}$ ,  $x_{l+2}$ ,..., $x_{2l}$  from x are placed at the inputs of multiplier 1 to x. After x and x are placed and loaded into x. All new x is generated and loaded into x. All new x is generated in serial. The second iteration again repeats from x until convergence has been reached.

One major difference between cases 3 and 4 is that how new values of  $x_i$  are updated. In case 3, a total of p new values of  $x_i$  can be updated at a time with inputs processed in serial, while in case 4 only one new value of  $x_i$  will be updated at time but at a faster rate of update of each new  $x_i$  compared to case 3. Also, case 3 requires one accumulator for the product of  $a_{ij}$  and  $x_j$  in each JPU, while case 4 requires additional binary tree adders/subtractors in order to take advantage of parallel multipliers [46].

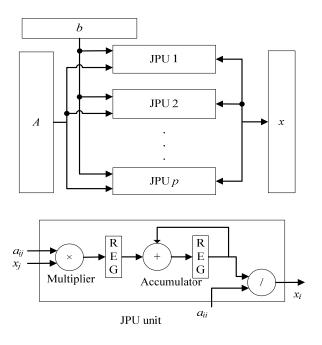

#### 3.1.2 Combined Jacobi and Gauss-Seidel Method

Assume no memory constraint. The ideal hardware architecture of Gauss-Seidel method is equivalent to case 2 of hardware architectures of Jacobi, which consists of 1 JPU for updating  $x_i$ . Within JPU, there are n-1 multipliers, 1 divider, and binary tree adders/subtractors. This architecture is able to process the multiplication of  $a_{ij}$  and  $x_j$  in parallel inside JPU, but only update one new  $x_i$  at a time. However, considering the hardware resource constraint, it is difficult to realize completely parallel multiplications inside JPU in particular for large linear

Figure 3.4: Hardware architecture for combined Jacobi and Gauss-Seidel method

systems. A more realistic approach is to combine Jacobi and Gauss-Seidel method which requires  $p \times q$  multipliers in total, where p is the number of JPUs and q is the number of multipliers inside each JPU. Given limited hardware resource, there is a trade off between the number of JPUs and multipliers (i.e. p and q). In this combined method, a subset of variables, x, are calculated in parallel dependent upon available hardware resource. If the hardware resource allows maximum p variables to be calculated in parallel,  $x_1, x_2, ..., x_p$  are calculated first. The new values are used for calculating the next p variables,  $x_{p+1}, x_{p+2}, ..., x_{2p}$ , and so on.

Figure 3.4 shows a hardware architecture which implements the combined Jacobi and Gauss-Seidel method. This architecture contains p JPUs processed in parallel and q multipliers inside each JPU. For each iteration, a set of coefficients,  $a_{i,q+1}, a_{i,q+2}, \ldots, a_{i,2q}$  from A and  $x_{q+1}, x_{q+2}, \ldots, x_{2q}$  from x are placed at the inputs of multiplier 1 to q inside JPU. After  $\lceil (n-1)/q \rceil$  clock cycles, a total of p number of new  $x_i$  are generated and loaded into x. The

first set of new  $x_i$  are  $x_1, x_2,...,x_p$ , the second set of new  $x_i$  are  $x_{p+1}, x_{p+2},...,x_{2p}$ , and so on. The second iteration again repeats from  $x_1, x_2,...,x_p$  until convergence has been reached.

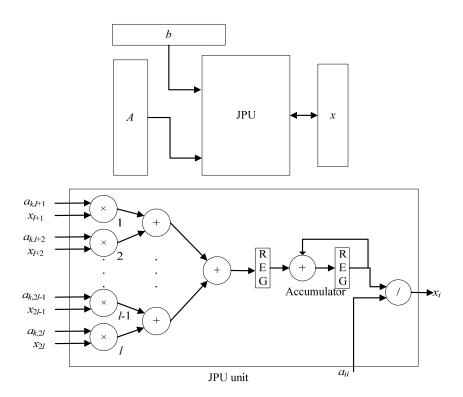

#### 3.1.3 Conjugate Gradient Method

As described in Chapter 2, CG used as iterative method is memory-efficient and runs quickly with sparse matrices. Figure 3.5 shows one way to implement CG in hardware. This architecture consists of four matrix-multiplication blocks (MMB), two dividers, and two adder/subtractors. Matrix-vector multiplication, vector-vector multiplication and scalar-vector multiplication are implemented in the same block, i.e., MMB. Scalar-vector multiplication is treated as matrix-vector multiplication by transforming the scalar into a diagonal matrix with all diagonal values equal to the scalar value, where a diagonal matrix is a square matrix in which the entries outside the main diagonal are all zero.

In this realization, there are five global signals. The first global signal,  $sel_{\_}r^0$ , is used to determine when to select b-Ax and  $r-\alpha Ad$  associated with  $r^0$  and  $r^k$ , where  $r^0$  is the initialized residual,  $r^k$  is the new residual and k is the number of current iteration. The second global signal,  $sel_{\_}d^0$ , is used to determine when to select  $d^0$  and  $d^k$ , where  $d^0$  is the initialized search direction and  $d^k$  is the current search direction. The third global signal,  $sel_{\_}accu$ , is used to accumulate multiplications to obtain  $d^TAd$ . The fourth global signal,  $sel_{\_}a\beta$ , is used to determine when to select  $x + \alpha d$  and  $r + \beta d$  associated with  $x^{k+1}$  and  $d^{k+1}$ , where  $x^{k+1}$  is the new approximation to solution x. The last global signal,  $sel_{\_}x^0$ , is used to determine when to select  $x^0$  and  $x^k$ . Divider\_1 and Divider\_2 perform scalar divisions to obtain  $\alpha$  and  $\beta$  respectively, where  $\alpha$  and  $\beta$  are associated with calculations of x, r and d.

This architecture can be divided into three blocks including BLOCK\_A, BLOCK\_B and BLOCK\_C shown in Figure 3.5. Only one block will be enabled at a time. For the first iteration, BLOCK\_A is enabled at the beginning, where  $sel_r^0$  selects b, A, and  $x^0$  to calculate the initial residual  $r^0$  which is also equal to the initial search direction  $d^0$ , and  $\delta new$  is obtained by multiplying  $r^0$  with  $(r^0)^T$ . Then BLOCK\_B is enabled, where  $sel_d^0$  selects  $d^0$ ,  $sel_accu$  is used to accumulate the multiplication results,  $(d^0)^T A d^0$ , and Divider\_1 performs a scalar division between  $\delta new$  and  $(d^0)^T A d^0$  to obtain  $\alpha^0$ . Then BLOCK\_C is enabled, where

$sel\_x^0$  selects  $x^0$  and  $sel\_a\beta$  selects  $x^0$  and  $\alpha^0$  to calculate  $x^1$ . After  $x^1$  is obtained, BLOCK\_A is enabled again, where  $sel\_r^0$  selects  $r^0$ ,  $\alpha^0$ , and  $Ad^0$  to calculate the second residual  $r^1$ ,  $\delta old$  is set to  $\delta new$ , and  $\delta new$  is renewed by multiplying  $r^1$  with  $(r^1)^T$ . Divider\_2 performs a scalar division between  $\delta new$  and  $\delta old$  to obtain  $\beta^0$ . At the end of this iteration, BLOCK\_C is enabled again, where  $sel\_\alpha\beta$  selects  $r^1$  and  $\beta^0$  to calculate  $d^1$ .

For second iteration, BLOCK\_B is enabled at the beginning, where  $sel\_d^0$  selects  $d^1$ ,  $sel\_accu$  is used to accumulate the multiplication results,  $(d^1)^T A d^1$  and Divider\_1 performs a scalar division between  $\delta new$  and  $(d^1)^T A d^1$  to obtain  $\alpha^1$ . Then BLOCK\_C is enabled, where  $sel\_x^0$  selects  $x^1$  and  $sel\_\alpha\beta$  selects  $x^1$  and  $\alpha^1$  to calculate  $x^2$ . After  $x^2$  is obtained, BLOCK\_A is enabled, where  $sel\_r^0$  selects  $r^1$ ,  $\alpha^1$ , and  $Ad^1$  to calculate the third residual  $r^2$ ,  $\delta old$  is set to  $\delta new$  and  $\delta new$  is renewed by multiplying  $r^2$  with  $(r^2)^T$ . Divider\_2 performs a scalar division between  $\delta new$  and  $\delta old$  to obtain  $\beta^1$ . At the end of this iteration, BLOCK\_C is enabled again, where  $sel\_\alpha\beta$  selects  $r^2$  and  $\beta^1$  to calculate  $d^2$ . For following iterations, the process repeats as second iteration until convergence has been reached.

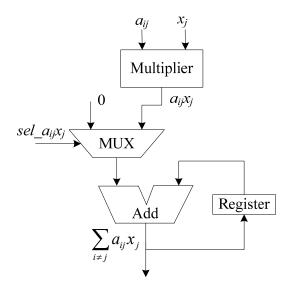

The above analysis shows that the key to a fast implementation of CG is a fast implementation of MMB. A simplified multiplication and accumulation (MAC) unit for matrix multiplication is shown in Figure 3.6. Assume  $a_{ij}$  and  $x_j$  can be available as inputs data simultaneously, the MAC unit computes  $a_{ij} \times x_j$ , and then adds  $a_{ij}x_j$  to the accumulate register, where accumulate register is initialized to zero. The MAC unit accumulates the products of inputs fed every cycle. After n (matrix size) cycles, one element of resulted vectors will be obtained and stored into memory until all of inputs are processed. CG is usually completed after n iterations. In practice, the recursive formula for the residual,  $r^{k+1} = r^k - \alpha^k A d^k$ , results in accumulated floating point round off error which will cause the residual r to gradually lose accuracy. The evaluation process will be terminated early due to this floating point round off error. This problem can be corrected by recalculating the exact residual,  $r^{k+1} = b - Ax^k$ , where global signal  $sel_r^0$  selects b, A, and  $x^k$  to calculate  $r^{k+1}$  in BLOCK\_A.

Figure 3.5: General hardware architecture for CG algorithm

Figure 3.6: Hardware architecture for multiplication unit

## 3.2 LNS-based Hardware Design of Jacobi Processor

Due to the complexity of hardware designs of arithmetic units such as multiplier and divider, LNS has been studied in an effect to simplify arithmetic computations for lower computation complexity, higher computation speed, and smaller counts size [19, 20, 21, 22]. In LNS, fast multiplication and division operations can be achieved by using addition and subtraction operations on the logarithms of the input data; i.e., the hardware cost of multiplications and divisions are similar in LNS. The reduced circuit size and possibly increased speed of multiplication and division make LNS becomes a viable solution to many computational intensive applications such as hardware implementation of matrix solving.

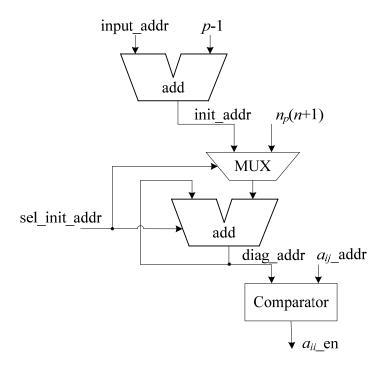

Figure 3.7 shows one way to implement LNS-based JPU unit [51] for case 3 described in Section 3.1.1, where logarithm and antilogarithm converters can be implemented according to [19, 21]. In this realization, two logarithm converters are used for the multiplications of  $a_{ij}$  and  $x_j$  as well as the division of  $b_i - \sum_{j \neq i} a_{ij} x_j^m$  and  $a_{ii}$ . The global signal,  $sel\_div$ , is used to determine when to select  $b_i - \sum_{j \neq i} a_{ij} x_j^m$  and  $a_{ii}$  to perform LNS-based division. A second global signal,  $sel\_b_i$ , is used to determine when the accumulator is used for executing additions and subtractions associated with  $\sum_{j \neq i} a_{ij} x_j^m$  and  $b_i - \sum_{j \neq i} a_{ij} x_j^m$ . An external signal,  $a_{ii}\_en$ , from a

Figure 3.7: Hardware architecture for LNS-based Jacobi processor

diagonal element detector (DED) (not shown in Figure 3.7), is used to pick and store the diagonal element,  $a_{ii}$  for individual JPUs. Each JPU has a DED as showed in Figure 3.8, where  $input\_addr$  is the base address of certain row corresponding to that JPU. An initial address denoted as  $init\_addr$  is obtained by  $input\_addr + (p-1)$ , where p is the sequence number of JPU. For first subset of  $x_i$ ,  $sel\_init\_addr$  is set to high and the diagonal element address  $diag\_addr$  is equal to  $init\_addr$ . For second subset of  $x_i$ , the  $sel\_init\_addr$  is set to low the  $diag\_addr$  is obtained by adding  $init\_addr$  with  $n_p(n+1)$ , where  $n_p$  is the total number of JPU, n is the size of matrix A, and  $n_p(n+1)$  is a pre-calculated number. For the following subsets of  $x_i$ ,  $sel\_init\_addr$  is set to low and the  $diag\_addr$  is obtained by adding the

Figure 3.8: Hardware architecture for DED

diag\_addr again with  $n_p(n+1)$ . This process repeats until the first iteration is done. The following iteration begins again by setting  $sel\_init\_addr$  to high, thus  $diag\_addr$  is reset to 0 and  $init\_addr$  is selected for the first subset of  $x_i$ . The obtained  $diag\_addr$  will be compared with  $a_{ij}\_addr$ , where  $a_{ij}\_addr$  is the address of matrix element. If  $diag\_addr$  is equal to  $a_{ij}\_addr$ , matrix element  $a_{ij}$  will be chosen and stored as diagonal element by  $a_{ii}\_en$ .

LNS-based combined Jacobi and Gauss-Seidel can be implemented in a similar way as LNS-based Jacobi Processor where multiplication and division are replaced with LNS-based design. For CG method, MMB takes up the major part of multiplication which can also be replaced with a LNS-based block.

# 3.3 Xilinx EDK HW/SW Codesign of Iterative Methods

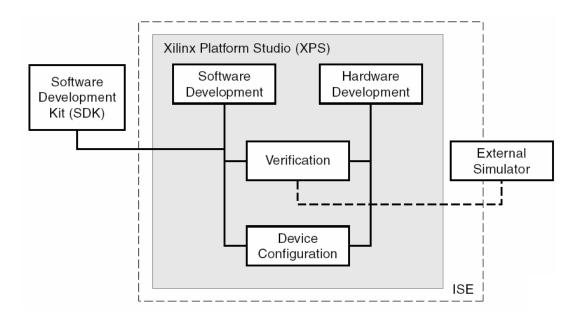

Xilinx EDK [18] is a suite of tools and IP blocks that designs a complete embedded processor system for implementation in a Xilinx FPGA device. The suite includes Xilinx platform studio (XPS), software development kit (SDK), hardware IP for the Xilinx

embedded processors, drivers and libraries for embedded software development, and GNU compiler and debugger for C/C++ software development. XPS is the development environment used for designing the hardware portion of embedded processor system and SDK is an integrated development environment, complimentary to XPS, that is used for C/C++ embedded software application creation and verification. Xilinx EDK tools are able to design a system using embedded MicroBlaze<sup>TM</sup> soft processor cores implemented using FPGA fabric, and/or PowerPC<sup>TM</sup> (PPC) hard processor cores, i.e., the fixed CPU cores incorporated into FPGA fabric. The MicroBlaze soft processor core has access to a high-speed serial interface called the Fast Simplex Link (FSL) which is an on-chip interconnect that provides a high-performance data channel between the MicroBlaze processor and the surrounding FPGA fabric. Similarly, the PowerPC hard processor core provides high-performance communication channels through the processor local bus (PLB) and on-chip memory (OCM) interfaces.

To use EDK, integrated software environment (ISE) [52] must be installed as well. ISE is the foundation for Xilinx FPGA logic design, which includes tools related to embedded processor systems and their design. Because FPGA design can be an involved process, Xilinx has provided ISE that allow the designer to circumvent some of this complexity such as constraints entry, timing analysis, logic placement and routing, and device programming have all been integrated into ISE.

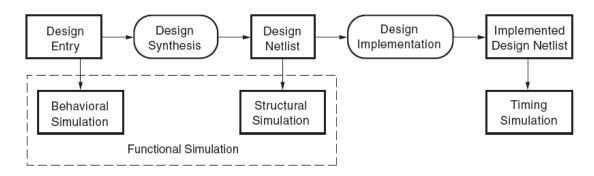

A simplified design flow for an embedded design using Xilinx EDK tools is showed in Figure 3.9 [18]. The design enables the integration of both hardware and software components of an embedded system. Typically, the ISE FPGA development software runs behind the scene. The XPS tools make function calls to the utilities provided by the ISE software. XPS is used primarily for embedded processor hardware system development, where specification of the microprocessor, peripherals, and the interconnection of these components, along with their respective property assignments takes place. Simple software development can also be accomplished from within XPS, but for more complex application development and debug, Xilinx recommends using the SDK tool. Verifying the correct functionality of hardware platform can be accomplished by running the design through a

Figure 3.9: Basic embedded design process flow [18].

Figure 3.10: EDK design simulation stages [18].

hardware description language (HDL) simulator. XPS facilitates three types of simulation including behavioral, structural and timing-accurate. Verification through behavioral, structural, and timing simulation can be performed at specific points in design process, as illustrated in Figure 3.10 [18]. After completing the design, FPGA bitstream along with the software executable and linkable format file (ELF) are downloaded into target board to configure the target device.

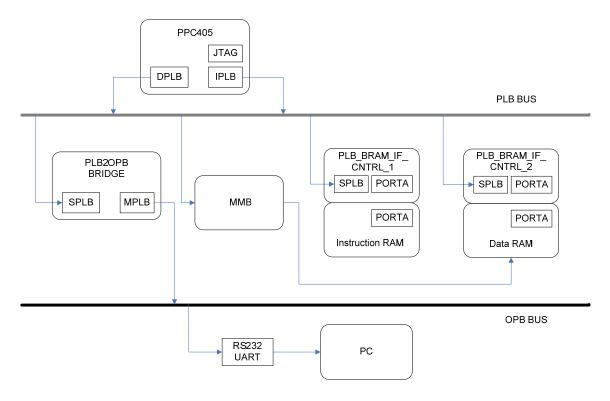

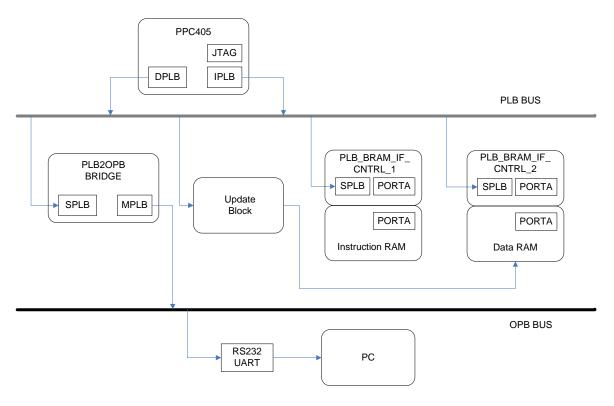

The Xilinx EDK design is implemented in Xilinx Virtex-II Pro XC2VP30 based platform FPGA. The HW/SW codesign architecture for Jacobi, Gauss-Seidel and CG is shown in Figure 3.11. This architecture includes the following hardware components:

- PPC 405: The brain of the system, the microprocessor.

- PLB\_BUS: The processor local bus. PLB\_BUS is the higher hierarchy bus, the one closer to the processor. Primary instruction and data memory are transferred through this bus.

- OPB\_BUS: The on-chip-peripheral bus. Slow and non-critical peripheral is attached to this bus.

- MMB: The matrix multiplication block, which implements matrix multiplications of three iterative methods in FPGA.

- PLB\_BRAM\_IF\_CNTRL: The controller for the memory which is attached to the PLB bus.

- PLB BRAM: Memories for storing data and instructions.

- PLB2OPB\_BRIDGE: This bridge connects the PLB and the OPB bus in a master-slave (PLB-OPB) schema. This is a one-way bridge. Therefore, as an OPB-PLB schema is needed an opb2plb\_bridge will be required.

- OPB\_UART: Universal asynchronous receiver/transmitter, this is attached to the OPB bus and allows the design system to display information on PC.

- DDR\_CLOCK\_MODULE\_REF: The design system requires several different clocks, for the bus, for the CPU, for peripherals, etc.

- PROC\_SYS\_RESET: The system has different types of resets (i.e. chip reset, system reset, core reset, etc).

Figure 3.11: EDK design architecture of Jacobi, Gauss-Seidel, and CG.

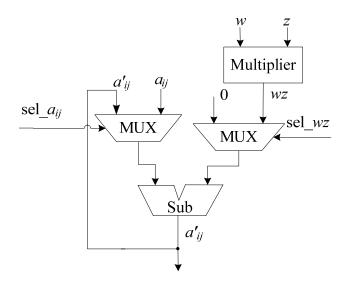

Figure 3.12: Hardware architecture of MMB